March 2008

# **USB1T11A** — Universal Serial Bus Transceiver

#### **Features**

- Complies with Universal Serial Bus Specification 1.1

- Utilizes Digital Inputs and Outputs to Transmit and Receive USB Cable Data

- Supports 12Mbit/s "Full Speed" and 1.5Mbit/s "Low Speed" Serial Data Transmission

- Compatible with the VHDL "Serial Interface Engine" from USB Implementers' Forum

- Supports Single-ended Data Interface

- Single 3.3V Supply

- ESD Performance: Human Body Model

>9.5kV on D-, D+ pins only

>4kV on all other pins

- 16-lead, Space-Saving, MLP Package

### **Description**

The USB1T11A is a one-chip, generic USB transceiver. It is designed to allow 5.0V or 3.3V programmable and standard logic to interface with the physical layer of the Universal Serial Bus. It is capable of transmitting and receiving serial data at both full-speed (12Mbit/s) and low-speed (1.5Mbit/s) data rates.

The input and output signals of the USB1T11A conform with the "Serial Interface Engine." Implementation of the serial interface engine allows designers to make USB-compatible devices with off-the-shelf logic to modify and update the application.

### **Ordering Information**

| Part Number  | Operating<br>Temperature<br>Range | Package                                                                           | Packing<br>Method |

|--------------|-----------------------------------|-----------------------------------------------------------------------------------|-------------------|

| USB1T11AM    | -40 to +85°C                      | 14-Lead, Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150-Inch Narrow | Tube              |

| USB1T11AMX   | -40 to +85°C                      | 14-Lead, Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150-Inch Narrow | Tape and Reel     |

| USB1T11ABQX  | -40 to +85°C                      | 16-Terminal, Molded Leadless Package (MLP), JEDEC MO-220, 3mm Square              | Tape and Reel     |

| USB1T11AMTC  | -40 to +85°C                      | 14-Lead, Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mmWide       | Tube              |

| USB1T11AMTCX | -40 to +85°C                      | 14-Lead, Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide      | Tape and Reel     |

All packages are lead free per JEDEC: J-STD-020B standard.

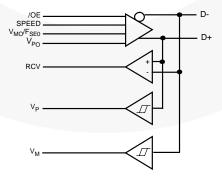

Figure 1. Logic Diagram

# **Pin Configuration**

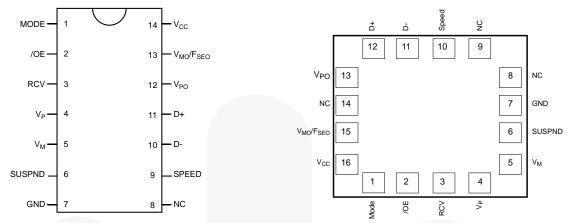

Figure 2. TSSOP and SOIC Pin Assignments

Figure 3. MLP Pin Assignments

# **Pin Descriptions**

| Pin Names        | 1/0  | Description                                                                                                          |                                                                                                                                      |                                   |                                                |  |  |

|------------------|------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------|--|--|

| RVC              | 0    | Receive Data. CMOS                                                                                                   | Receive Data. CMOS level output for USB differential input.                                                                          |                                   |                                                |  |  |

| /OE              | 1    |                                                                                                                      | Output Enable. Active LOW, enables the transceiver to transmit data on the bus. When not active, the transceiver is in receive mode. |                                   |                                                |  |  |

| Mode             | 1    | Mode. When left und GND, the V <sub>MO</sub> /F <sub>SEO</sub> p                                                     |                                                                                                                                      |                                   | Is it to $V_{CC}$ and, in this D).             |  |  |

|                  |      | Inputs to differential of                                                                                            | driver. (Outputs fro                                                                                                                 | om SIE.)                          |                                                |  |  |

|                  |      | Mode                                                                                                                 | V <sub>PO</sub>                                                                                                                      | V <sub>MO</sub> /F <sub>SEO</sub> | RESULT                                         |  |  |

|                  |      | 0                                                                                                                    | 0                                                                                                                                    |                                   | Logic "0"                                      |  |  |

|                  |      |                                                                                                                      | 0                                                                                                                                    |                                   | /SEO                                           |  |  |

| Vpo.Vmo/Fseo     |      |                                                                                                                      | 1                                                                                                                                    |                                   | Logic "1"                                      |  |  |

| V PO, V MO/T SEO |      |                                                                                                                      | 1                                                                                                                                    |                                   | /SEO                                           |  |  |

|                  |      | 1                                                                                                                    | 0                                                                                                                                    | 0                                 | /SEO                                           |  |  |

|                  |      |                                                                                                                      | 0                                                                                                                                    | 1                                 | Logic "0"                                      |  |  |

|                  |      |                                                                                                                      | 1                                                                                                                                    | 0                                 | Logic "1"                                      |  |  |

|                  |      |                                                                                                                      | 1                                                                                                                                    | 1                                 | Illegal Code                                   |  |  |

|                  |      | Gated version of D- a ended zero (/SEO), e                                                                           |                                                                                                                                      |                                   | "1." Used to detect singleed. (Input to SIE).  |  |  |

|                  |      | V <sub>P</sub>                                                                                                       |                                                                                                                                      | V <sub>M</sub>                    | RESULT                                         |  |  |

| $V_P, V_M$       | 0    | 0                                                                                                                    |                                                                                                                                      | 0                                 | /SEO                                           |  |  |

|                  |      | 0                                                                                                                    |                                                                                                                                      | 1                                 | Low Speed                                      |  |  |

|                  |      | 1                                                                                                                    |                                                                                                                                      | 0                                 | Full Speed                                     |  |  |

|                  |      | 0                                                                                                                    |                                                                                                                                      | 1                                 | Error                                          |  |  |

| D+, D-           | AI/O | Data+, Data Differe                                                                                                  | Data+, Data Differential data bus conforming to the Universal Serial Bus standard.                                                   |                                   |                                                |  |  |

| SUSPND           | I    | <b>Suspend</b> . Enables a suspend pin is active STATE.                                                              |                                                                                                                                      |                                   | nactive. While the<br>te. Both D+ and D- are 3 |  |  |

| Speed            | I    | Edge Rate Control. Logic "1" operates at edge rates for "full speed." Logic "0" operates edge rates for "low speed." |                                                                                                                                      |                                   |                                                |  |  |

| V <sub>CC</sub>  |      | 3.0 to 3.6 power supp                                                                                                | oly.                                                                                                                                 |                                   |                                                |  |  |

| GND              |      | Ground reference.                                                                                                    |                                                                                                                                      |                                   |                                                |  |  |

# **Functional Truth Table**

|               | Input         |                                   |     | I/     | 0       |         | Outp               | uts                |                    |                 |

|---------------|---------------|-----------------------------------|-----|--------|---------|---------|--------------------|--------------------|--------------------|-----------------|

| Mode          | $V_{PO}$      | V <sub>MO</sub> /F <sub>SEO</sub> | /OE | SUSPND | D+      | D-      | RCV                | V <sub>P</sub>     | V <sub>M</sub>     | Result          |

| 0             | 0             | 0                                 | 0   | 0      | 0       | 1       | 0                  | 0                  | 1                  | Logic "0"       |

| 0             | 0             | 1                                 | 0   | 0      | 0       | 0       | Undefined<br>State | 0                  | 0                  | /SEO            |

| 0             | 1             | 0                                 | 0   | 0      | 1       | 0       | 1                  | 1                  | 0                  | Logic "1"       |

| 0             | 1             | 1                                 | 0   | 0      | 0       | 0       | Undefined<br>State | 0                  | 0                  | /SEO            |

| 1             | 0             | 0                                 | 0   | 0      | 0       | 0       | Undefined<br>State | 0                  | 0                  | /SEO            |

| 1             | 0             | 1                                 | 0   | 0      | 0       | 1       | 0                  | 0                  | 1                  | Logic "0"       |

| 1             | 1             | 0                                 | 0   | 0      | 1       | 0       | 1                  | 1                  | 0                  | Logic "1"       |

| 1             | 1             | 1                                 | 0   | 0      | 1       | 1       | Undefined<br>State | Undefined<br>State | Undefined<br>State | Illegal<br>Code |

| Don't<br>Care | Don't<br>Care | Don't Care                        | 1   | 0      | 3-State | 3-State | Undefined<br>State | Undefined<br>State | Undefined<br>State | D+/D-<br>Hi-Z   |

| Don't<br>Care | Don't<br>Care | Don't Care                        | 1   | 1      | 3-State | 3-State | Undefined<br>State | Undefined<br>State | Undefined<br>State | D+/D-<br>Hi-Z   |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                             | Paramete                                    | Parameter                                  |      |                       | Unit |

|------------------------------------|---------------------------------------------|--------------------------------------------|------|-----------------------|------|

| V <sub>CC</sub>                    | DC Supply Voltage                           |                                            | 0.5  | 7.0                   | V    |

| I <sub>IK</sub>                    | DC Input Diode Current, V <sub>IN</sub> <0V | ,                                          |      | -50                   | mA   |

| $V_{IN}$                           | Input Voltage <sup>(1)</sup>                |                                            | 0.5  | 5.5                   | V    |

| V <sub>I/O</sub>                   | Input Voltage                               |                                            | 0.5  | V <sub>CC</sub> + 0.5 | V    |

| lok                                | Output Diode Current, Vo>Vcc o              | or V <sub>O</sub> <0                       |      | ±50                   | mA   |

| Vo                                 | Output Voltage                              |                                            | 0.5  | V <sub>CC</sub> + 0.5 | V    |

| Io                                 | Output Source or Sink Current               | V <sub>P</sub> , V <sub>M</sub> , RCV Pins |      | ±15                   | mA   |

| 10                                 | $(V_O = 0 \text{ to } V_{CC})$              | D+/D- Pins                                 |      | ±50                   | ША   |

| I <sub>CC</sub> / I <sub>GND</sub> | V <sub>CC</sub> / GND Current               |                                            | ±100 | mA                    |      |

| T <sub>STG</sub>                   | Storage Temperature Range                   |                                            | -60  | +150                  | °C   |

#### Note:

The input and output negative voltage ratings may be exceeded if the input and output diode current ratings are

observed.

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol            | Parameter                               | Min. | Max.     | Unit |

|-------------------|-----------------------------------------|------|----------|------|

| Vcc               | Power Supply Operating                  | 3.0  | 3.6      | V    |

| V <sub>IN</sub>   | Input Voltage                           | 0    | 5.5      | V    |

| V <sub>AI/O</sub> | Input Range for AI/0                    | 0    | Vcc      | V    |

| Vo                | Output Voltage                          |      | $V_{CC}$ | V    |

| T <sub>A</sub>    | Operating Ambient Temperature, Free Air | -40  | +85      | °C   |

## **DC Electrical Characteristics Digital Pins**

Over recommended range of supply voltage and operating free air temperature unless otherwise noted.  $V_{CC} = 3.0V$  to 3.6V.

| Cumahaal          | Dovernator                               | Conditions                                          | T <sub>A</sub> =-    | T <sub>A</sub> =-40 to +85°C |      |       |  |

|-------------------|------------------------------------------|-----------------------------------------------------|----------------------|------------------------------|------|-------|--|

| Symbol            | Parameter                                | Conditions                                          | Min.                 | Тур.                         | Max. | Units |  |

| Input Leve        | ls                                       |                                                     |                      |                              |      |       |  |

| V <sub>IL</sub>   | Low-Level Input Voltage                  |                                                     |                      |                              | 0.8  | V     |  |

| V <sub>IH</sub>   | High-Level Input Voltage                 |                                                     | 2                    |                              |      | V     |  |

| Output Lev        | vels                                     |                                                     |                      |                              |      |       |  |

| V                 | V <sub>OL</sub> Low-Level Output Voltage | I <sub>OL</sub> =4mA                                |                      |                              | 0.4  | V     |  |

| VOL               |                                          | I <sub>OL</sub> =20µA                               |                      |                              | 0.1  | V     |  |

| \/                | V Lligh Lovel Output Voltage             | I <sub>OH</sub> =4mA                                | 2.5                  |                              |      | V     |  |

| $V_{OH}$          | High-Level Output Voltage                | I <sub>OH</sub> =20μA                               | V <sub>CC</sub> -0.1 |                              |      | ]     |  |

| Leakage C         | urrent                                   |                                                     |                      |                              |      |       |  |

| I <sub>IN</sub>   | Input Leakage Current                    | V <sub>CC</sub> =3.0 to 3.6                         |                      |                              | ±5   | μΑ    |  |

| I <sub>CCFS</sub> | Supply Current, Full Speed               | V <sub>CC</sub> =3.0 to 3.6                         |                      |                              | 5    | mA    |  |

| I <sub>CCLS</sub> | Supply Current, Low Speed                | V <sub>CC</sub> =3.0 to 3.6                         |                      |                              | 5    | mA    |  |

| I <sub>CCQ</sub>  | Quiescent Supply Current                 | $V_{CC}$ =3.0 to 3.6, $V_{IN}$ = $V_{CC}$ or GND    |                      |                              | 5    | mA    |  |

| Iccs              | Supply Current in Suspend                | V <sub>CC</sub> =3.0 to 3.6<br>Mode=V <sub>CC</sub> |                      |                              | 10   | μΑ    |  |

### DC Electrical Characteristics D+/D- Pins

Over recommended range of supply voltage and operating free air temperature unless otherwise noted.  $V_{CC} = 3.0V$  to 3.6V.

| Symbol                         | Parameter                                 | Conditions                      | T <sub>A</sub> =- | Units |      |        |  |

|--------------------------------|-------------------------------------------|---------------------------------|-------------------|-------|------|--------|--|

| Symbol                         | Parameter                                 | Conditions                      | Min.              | Тур.  | Max. | Uillis |  |

| Input Leve                     | ls                                        |                                 |                   |       |      |        |  |

| $V_{DI}$                       | Differential Input Sensitivity            | (D+) - (D-)                     | 0.2               |       |      | V      |  |

| $V_{CM}$                       | Differential Common-Mode Range            | Includes V <sub>DI</sub> Range  | 0.8               |       | 2.5  | V      |  |

| V <sub>SE</sub>                | Single-Ended Receiver Threshold           |                                 | 0.8               | /     | 2.0  | V      |  |

| Output Lev                     | vels                                      | •                               | 7                 |       |      |        |  |

| V <sub>OL</sub>                | Static Output Low-Voltage                 |                                 |                   |       | 0.3  | V      |  |

| V <sub>OH</sub>                | Static Output High-Voltage                | $R_L$ of $1.5k\Omega$ to $3.6V$ | 2.8               |       | 3.6  | V      |  |

| V <sub>CR</sub>                | Differential Crossover                    | $R_L$ of 1.5k $\Omega$ to GND   | 1.3               |       | 2.0  | V      |  |

| Leakage C                      | urrent                                    |                                 |                   | •     |      |        |  |

| l <sub>oz</sub>                | High Z-State Data Line Leakage<br>Current | 0V <v<sub>IN&lt;3.3V</v<sub>    |                   |       | ±5   | μΑ     |  |

| Capacitan                      | ce                                        | <u> </u>                        |                   |       |      |        |  |

| C <sub>IN</sub> <sup>(2)</sup> | Transceiver Capacitance                   | Pin to GND                      |                   |       | 10   | pF     |  |

| CIN                            | Capacitance Match                         |                                 |                   |       | 10   | %      |  |

| Output Re                      | sistance                                  |                                 |                   |       |      |        |  |

| $Z_{DRV}^{(3)}$                | Driver Output Resistance                  | Steady-State Drive              | 4                 |       | 20   | Ω      |  |

| ∠DRV ′                         | Resistance Match                          |                                 |                   |       | 10   | %      |  |

#### Notes:

- 2. This specification is guaranteed by design and statistical process distribution.

- 3. Excludes external resistor. To comply with USB specification 1.1, external series resistors of 24W ±1% each on D+ and D- are recommended.

## AC Electrical Characteristics D+/D- Pins, Full Speed

Over recommended range of supply voltage and operating free air temperature unless otherwise noted.  $V_{CC}$  = 3.0V to 3.6V,  $C_L$  = 50Pf;  $R_L$  =  $k\Omega$  on D+ to  $V_{CC}$ .

| Cymbal                              | Parameter                                                                             | Canditions           | T <sub>A</sub> =- | 40 to +8 | 5°C  | l lasita |

|-------------------------------------|---------------------------------------------------------------------------------------|----------------------|-------------------|----------|------|----------|

| Symbol                              | Parameter                                                                             | Conditions           | Min.              | Тур.     | Max. | Units    |

| Driver Cha                          | racteristics                                                                          |                      |                   |          |      |          |

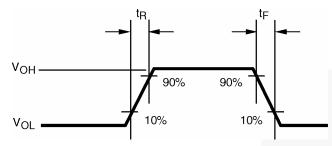

| t <sub>R,</sub> t <sub>F</sub>      | Rise and Fall Time                                                                    | 10 and 90%, Figure 4 | 4                 |          | 20   | ns       |

| t <sub>RFM</sub>                    | Rise/Fall Time Matching                                                               | $t_r / t_f$          | 90                |          | 110  | %        |

| V <sub>CRS</sub>                    | Output Signal Crossover Voltage                                                       |                      | 1.3               |          | 2.0  | V        |

| Driver Tim                          | ings                                                                                  |                      |                   |          |      |          |

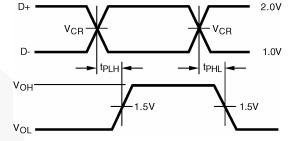

| t <sub>PLH</sub>                    | Driver Propagation Delay (V <sub>PO</sub> ,V <sub>MO</sub> /F <sub>SEO</sub> to D+D-) | Figure 5             |                   |          | 18   | ns       |

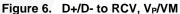

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Driver Disable Delay (/OE to D+/D-)                                                   | Figure 7             |                   |          | 13   | ns       |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Driver Enable Delay (/OE to D+/D-)                                                    | Figure 7             |                   |          | 17   | ns       |

| Receiver T                          | imings                                                                                |                      |                   |          |      |          |

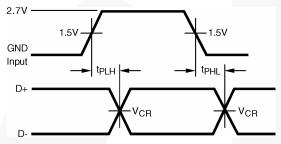

| t <sub>PLH</sub>                    | Receiver Propagation Delay                                                            | Figure 6             |                   |          | 16   | ns       |

| t <sub>PHL</sub>                    | D+/D- to RVC                                                                          | Figure 6             |                   |          | 19   | ns       |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Single-ended Receiver Delay (D+,D- to V <sub>P</sub> , V <sub>M</sub> )               | Figure 6             |                   |          | 8    | ns       |

# AC Electrical Characteristics D+/D- Pins, Low Speed

Over recommended range of supply voltage and operating free air temperature unless otherwise noted.  $V_{CC}$  = 3.0V to 3.6V,  $C_L$  = 200pF to 600pF;  $R_L$  = 1.5k $\Omega$  on D- to  $V_{CC}$ .

| Cumahal                             | Doromotor                                                                             | O a w aliti a w a               | T <sub>A</sub> =- |      |      |       |

|-------------------------------------|---------------------------------------------------------------------------------------|---------------------------------|-------------------|------|------|-------|

| Symbol                              | Parameter                                                                             | Conditions                      | Min.              | Тур. | Max. | Units |

| Driver Cha                          | racteristics                                                                          |                                 |                   |      |      |       |

| t <sub>LR</sub> , t <sub>LF</sub>   | Rise and Fall Time                                                                    | 10 and 90%, Figure 4            | 75                |      | 300  | ns    |

| t <sub>RFM</sub>                    | Rise/Fall Time Matching                                                               | t <sub>r</sub> / t <sub>f</sub> | 80                | /    | 120  | %     |

| V <sub>CRS</sub>                    | Output Signal Crossover Voltage                                                       |                                 | 1.3               |      | 2.0  | V     |

| Driver Tim                          | ings                                                                                  |                                 |                   |      | ý    |       |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Driver Propagation Delay (V <sub>PO</sub> ,V <sub>MO</sub> /F <sub>SEO</sub> to D+D-) | Figure 5                        |                   |      | 300  | ns    |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Driver Disable Delay (/OE to D+/D-)                                                   | Figure 7                        |                   |      | 13   | ns    |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Driver Enable Delay (/OE to D+/D-)                                                    | Figure 7                        |                   |      | 205  | ns    |

| Receiver T                          | imings                                                                                |                                 |                   |      |      |       |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Receiver Propagation Delay (D+/D- to RVC)                                             | Figure 6                        |                   |      | 18   | ns    |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Single-ended Receiver Delay (D+,D- to V <sub>P</sub> , V <sub>M</sub> )               | Figure 6                        |                   |      | 28   | ns    |

## **AC Loadings and Waveforms**

$V_{OL}$  and  $V_{OH}$  are the typical output voltage drops that occur with the output load.  $V_{CC}$  never goes below 3.0V.

Figure 4. Rise and Fall Times

Figure 5. V<sub>PO</sub>, V<sub>MO</sub>/F<sub>SEO</sub> to D+/D-

Figure 7. /OE to D+/D-

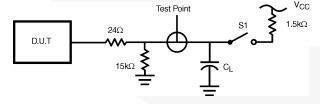

Test Point

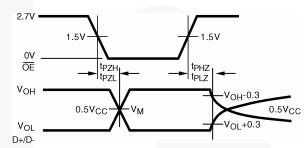

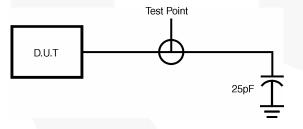

### **Test Circuits and Waveforms**

$500\Omega$  $24\Omega$ D.U.T 50pF

Figure 8. Load for V<sub>M</sub>/V<sub>P</sub> and RCV

Figure 9. Load for Enable and Disable Times

| Test  | <b>S</b> 1 |

|-------|------------|

| D-/LS | Close      |

| D+/LS | Open       |

| D-/FS | Open       |

| D+/FS | Close      |

C<sub>L</sub>=50pF, Full Speed

C<sub>L</sub>=200pF, Full Speed (Minimum Timing) C<sub>L</sub>=600pF, Full Speed (Maximum Timing)

$1.5k\Omega$  on D-(Low Speed) or D+ (Full Speed) only.

Figure 10. Load for D+/D-

## **Physical Dimensions**

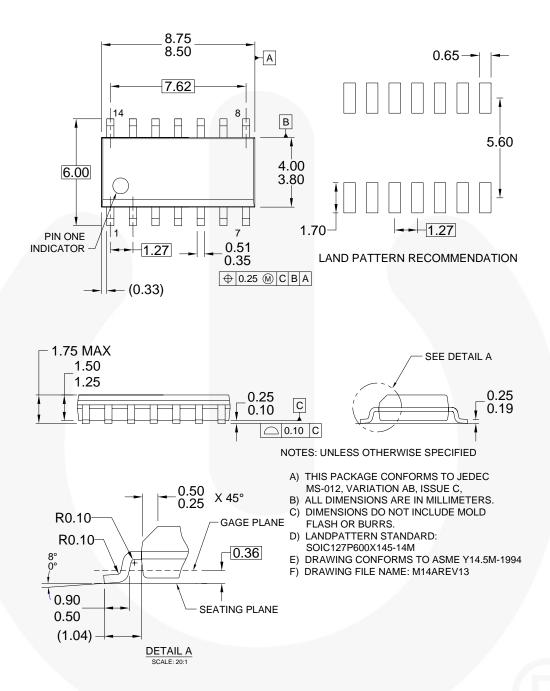

Figure 11. 14-Lead, Small Outline Integrated Circuit (SOIC) MO-012, 0.150-inch Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>

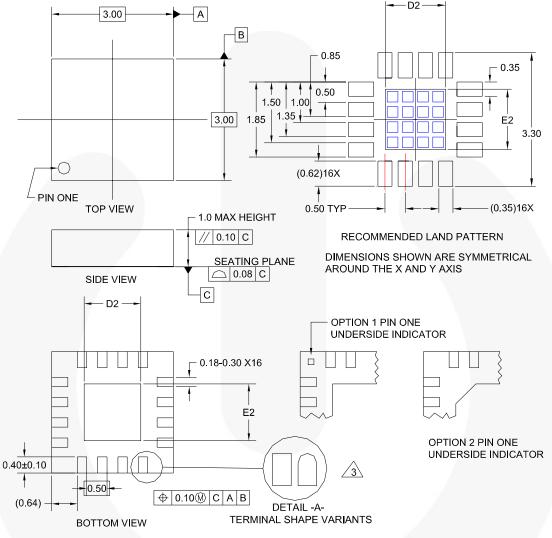

## **Physical Dimensions**

NOTES

- A. Package conforms to JEDEC MO-220

- B. DIMENSIONS ARE IN MILLIMETERS

- C. TERMINAL SHAPE MAY VARY ACCORDING TO PACKAGE SUPPLIER, SEE DETAIL A

MLP016CrevB

Figure 12. 16-Terminal, Molded Leadless Package (MLP), JEDEC MO-220, 3mm Square

Click here for tape and reel specifications, available at:

http://www.fairchildsemi.com/products/analog/pdf/MLP6\_3x3\_TNR.pdf

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

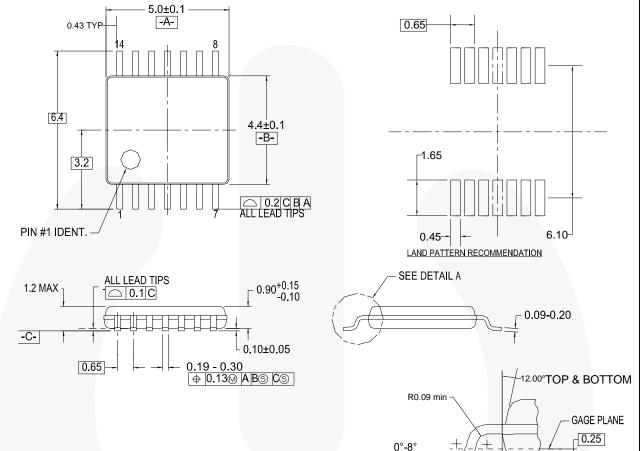

### **Physical Dimensions**

$0.6 \pm 0.1$

-1 00

NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-153, VARIATION AB, REF NOTE 6

- **B. DIMENSIONS ARE IN MILLIMETERS**

- C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS

- D. DIMENSIONING AND TOLERANCES PER ANSI Y14.5M, 1982

- E. LANDPATTERN STANDARD: SOP65P640X110-14M

- F. DRAWING FILE NAME: MTC14REV6

Figure 13. 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>

SEATING PLANE

R0.09min

**DETAIL** A

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks

ACEx<sup>®</sup> Build it Now™ CorePLUS™ CorePOWER™ CROSSVOLT™

CTL TM Current Transfer Logic™ EcoSPARK<sup>©</sup> EfficentMax™ EZSWITCH™ \*

Fairchild<sup>®</sup>

Fairchild Semiconductor® FACT Quiet Series™ FACT\_

FAST® FastvCore™ FlashWriter®\* FPS™ F-PFS™ FRFET®

Global Power Resources Green FPS™

Green FPS™ e-Series™ GTO™ IntelliMAX™

ISOPLANAR™ MegaBuck™

MICROCOUPLER™ MicroFET™

MicroPak™ MillerDrive™ MotionMax™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR® PDP SPM™ Power-SPM™ PowerTrench®

Programmable Active Droop™ QFET®

QSTM

Quiet Series™ RapidConfigure™

Saving our world, 1mW at a time™

SmartMax™ SMART START™

SPM® STEALTH™ SuperFET™ SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS™ SyncFET\*\*

The Power Franchise® p wer

TinyBoost™ TinyBuck™ TinyLogic<sup>®</sup> TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ μSerDes™

UHC Ultra FRFET™ UniFET™

VCX™ VisualMax™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification                 | Product Status        | Definition                                                                                                                                                                                               |

|------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information                      | Formative / In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary                              | First Production      | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed Full Production |                       | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                                 | Not In Production     | This datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. 134

<sup>\*</sup> EZSWITCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor.