## MG84FL54B

## Full-Speed USB micro-controller

| 1.  | General Description                            | 4   |

|-----|------------------------------------------------|-----|

| 2.  | Features                                       | 5   |

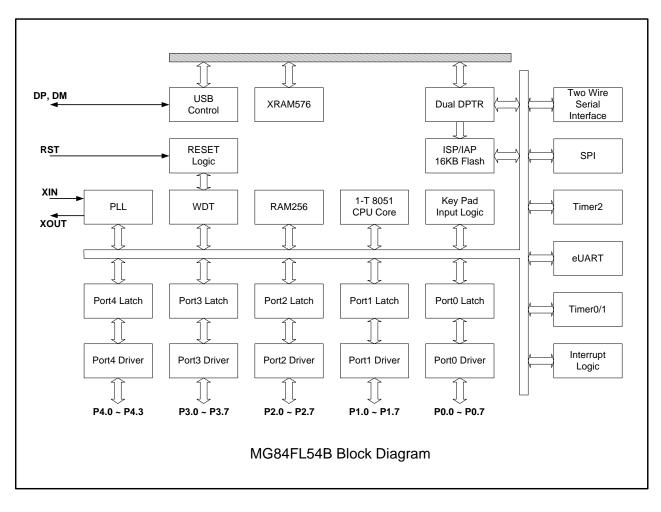

| 3.  | Block Diagram                                  | 6   |

| 4.  | Pin Configurations                             |     |

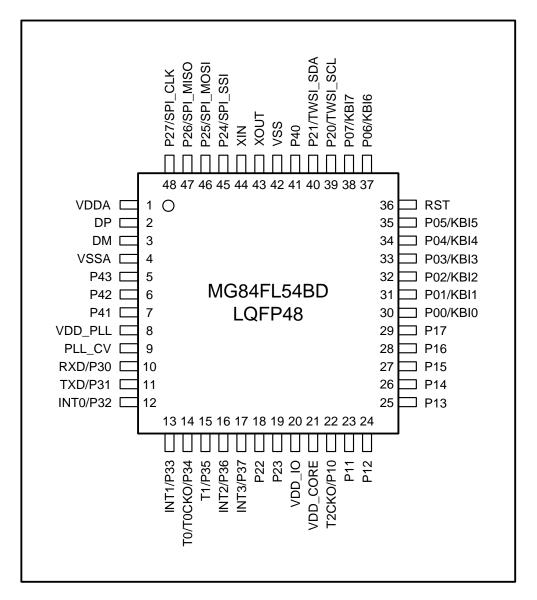

|     | 4.1. Pin-out for 48-pin Package                | 7   |

|     | 4.2. Pin Description                           | 8   |

| 5.  | Special Function Registers (SFRs)              | 10  |

|     | 5.1. SFR Mapping                               | 10  |

|     | 5.2. The Standard 8051 SFRs                    | 11  |

|     | 5.3. The Auxiliary SFRs                        | 12  |

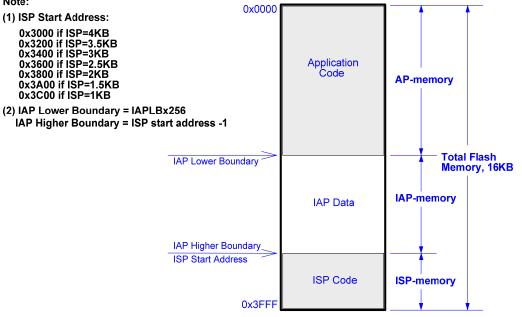

| 6.  | Flash Memory Configuration                     | 14  |

| 7.  | On-chip expanded RAM (XRAM)                    | 15  |

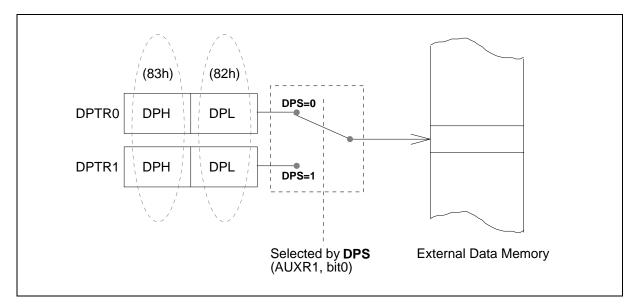

| 8.  | Dual Data Pointer Register (DPTR)              | 16  |

| 9.  | Configurable I/O Ports                         | 17  |

|     | 9.1. Port Configurations                       | 17  |

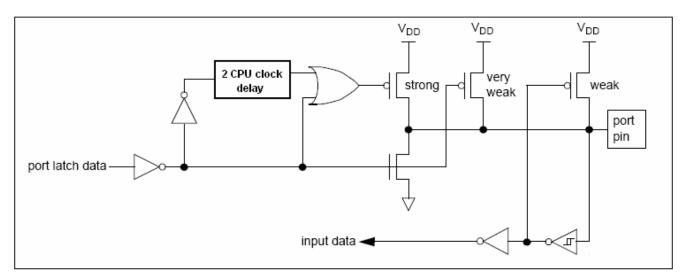

|     | 9.1.1. Quasi-bidirectional                     | .18 |

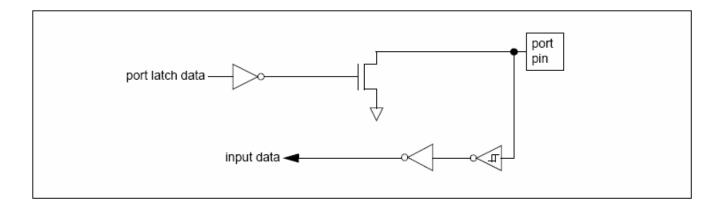

|     | 9.1.2. Open-Drain Output                       |     |

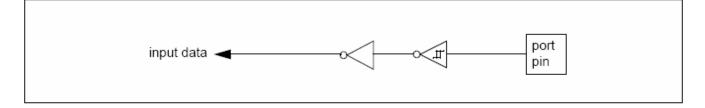

|     | 9.1.3. Input-Only (Hi-Z)                       | .19 |

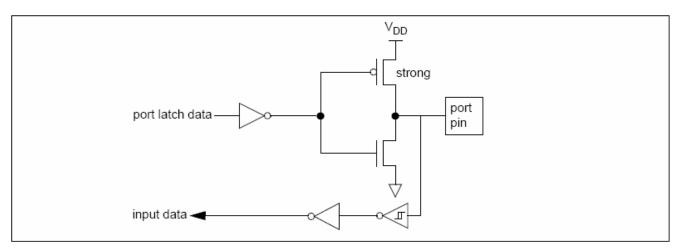

|     | 9.1.4. Push-Pull Output                        |     |

|     | 9.2. Maximum Ratings for Port Outputs          |     |

| 10. | Three 16-bit Timers                            |     |

|     | 10.1. Timer 0 and Timer 1                      |     |

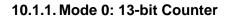

|     | 10.1.1. Mode 0: 13-bit Counter                 |     |

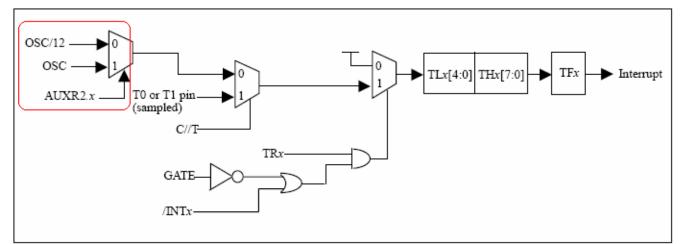

|     | 10.1.2. Mode 1: 16-bit Counter                 |     |

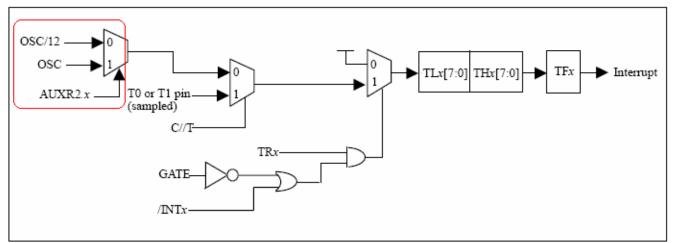

|     | 10.1.3. Mode 2: 8-bit Auto-reload              |     |

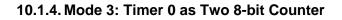

|     | 10.1.4. Mode 3: Timer 0 as Two 8-bit Counter   |     |

|     | 10.1.5. Programmable Clock Output from Timer 0 |     |

|     | 10.2. Timer 2                                  |     |

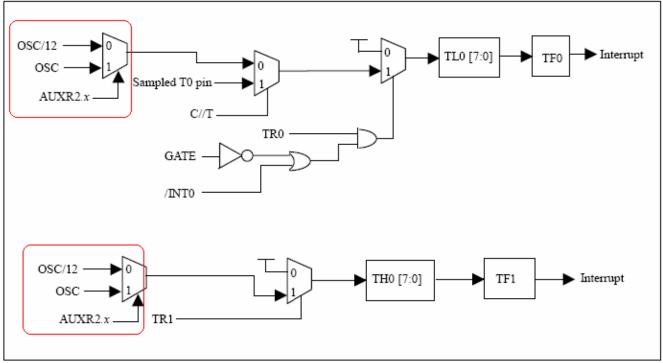

|     | 10.2.1. Capture Mode (CP)                      |     |

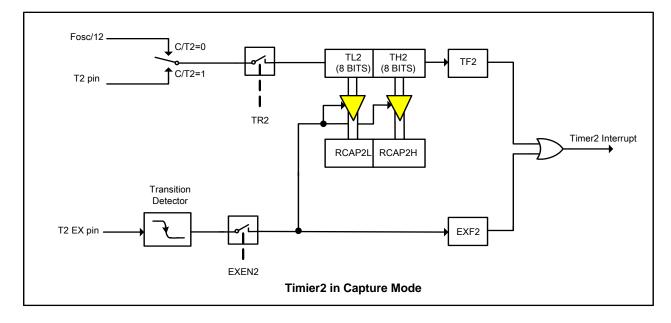

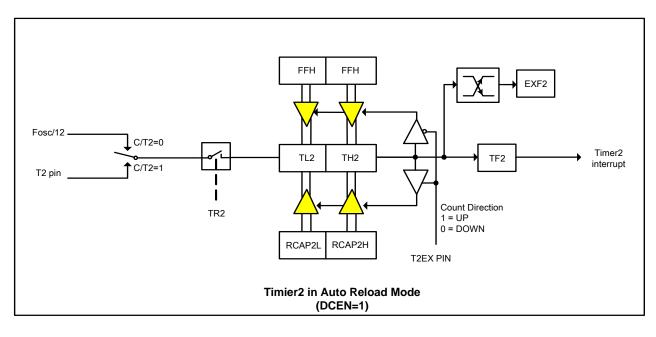

|     | 10.2.2. Auto-Reload Mode (AR)                  |     |

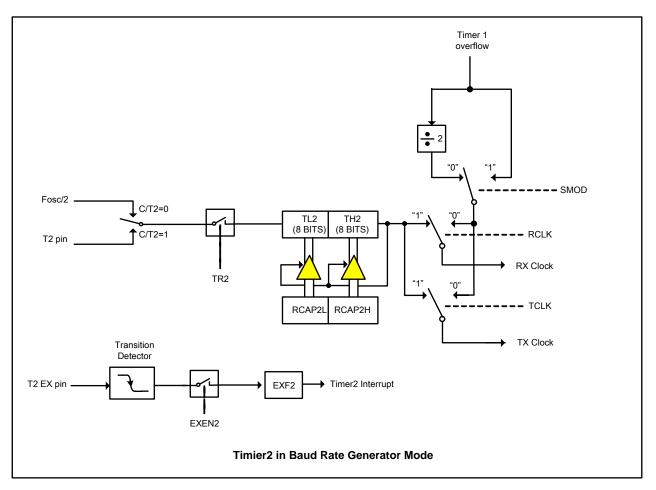

|     | 10.2.3. Baud-Rate Generator Mode (BRG)         |     |

|     | 10.2.4. Programmable Clock Output from Timer 2 |     |

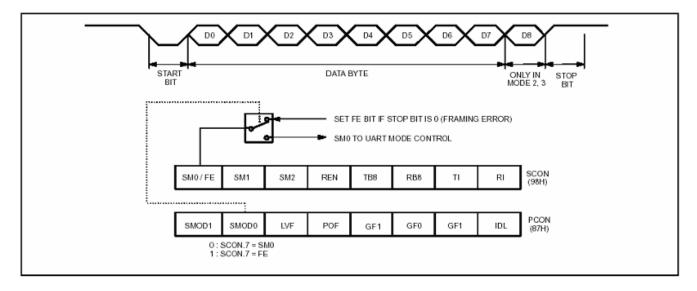

| 11. | Enhanced UART                                  |     |

|     | 11.1. Frame Error Detection                    |     |

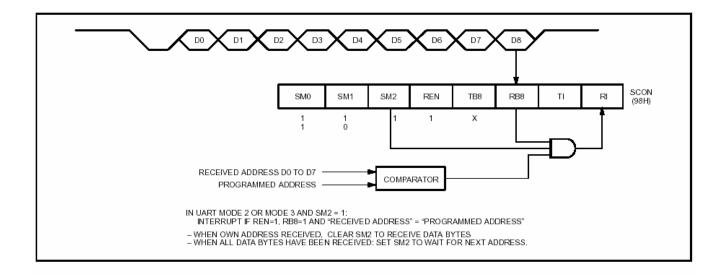

|     | 11.2. Automatic Address Recognition            |     |

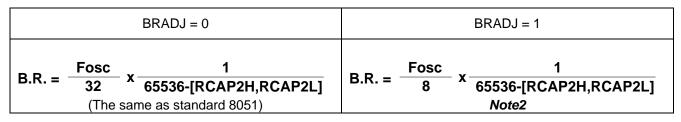

|     | 11.3. Baud Rate Setting                        |     |

| 12. | Interrupt                                      |     |

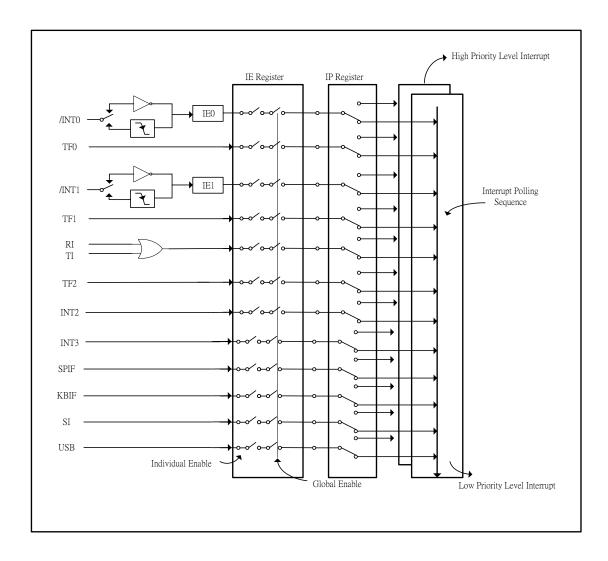

|     | 12.1. Two Priority Levels                      |     |

|     | 12.2. Interrupt System                         |     |

|     | 12.3. Note on Interrupt during ISP/IAP         |     |

| 13. | Additional External Interrupts (INT2 and INT3) | 39  |

This document contains information on a new product under development by Megawin. Megawin reserves the right to change or discontinue this product Without notice.

Megawin Technology Co., Ltd. 2008 All rights reserved.

|     | Keypad Interrupt                                             |     |

|-----|--------------------------------------------------------------|-----|

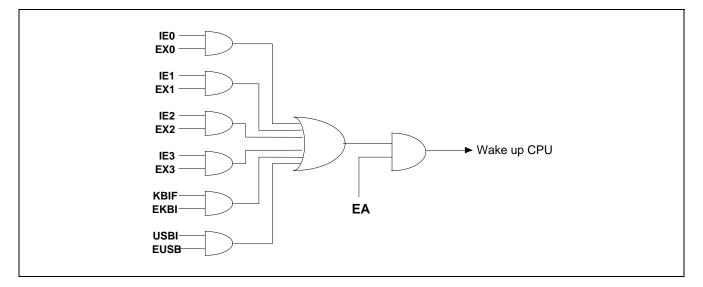

| 15. | Wake-up from Power-down Mode                                 |     |

|     | 15.1. Power-down Wake-up Sources                             |     |

|     | 15.2. Sample Code for Wake-up from Power-down                |     |

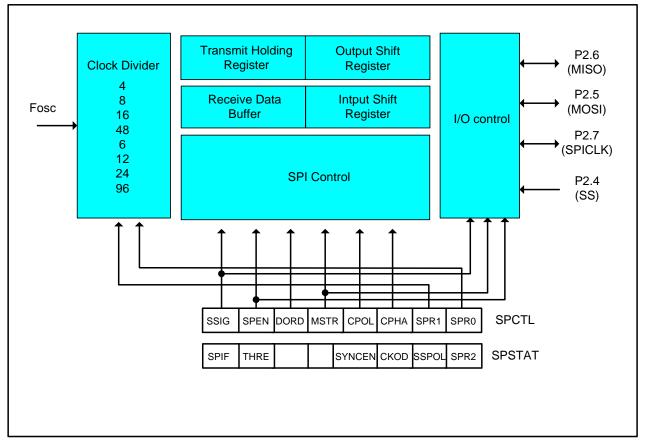

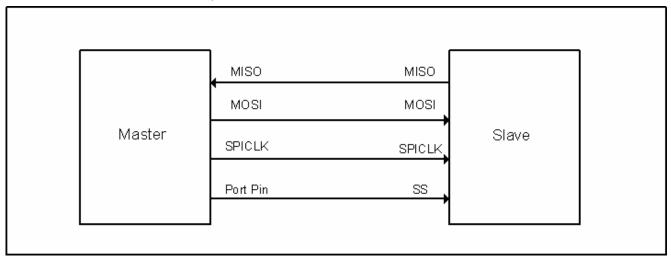

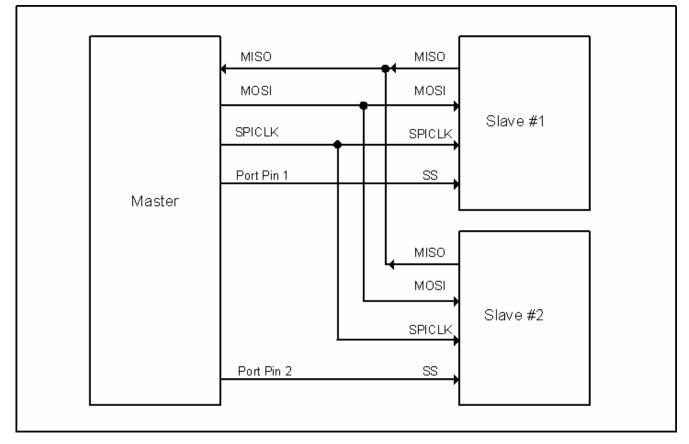

| 16. | Serial Peripheral Interface (SPI)                            |     |

|     | 16.1. Typical SPI Configurations                             |     |

|     | 16.1.1. Single Master & Single Slave                         |     |

|     | 16.1.2. Dual Device, where either can be a Master or a Slave |     |

|     | 16.1.3. Single Master & Multiple Slaves                      |     |

|     | 16.2. Configuring the SPI                                    |     |

|     | 16.2.1. Additional Considerations for a Slave                |     |

|     | 16.2.2. Additional Considerations for a Master               |     |

|     | 16.2.3. Mode Change on /SS-pin                               |     |

|     | 16.2.4. No Write Collision                                   |     |

|     | 16.2.5. SPI Clock Rate Select                                | .48 |

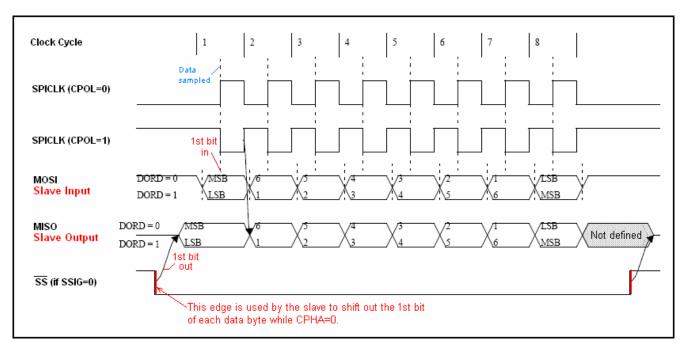

|     | 16.3. Data Mode                                              |     |

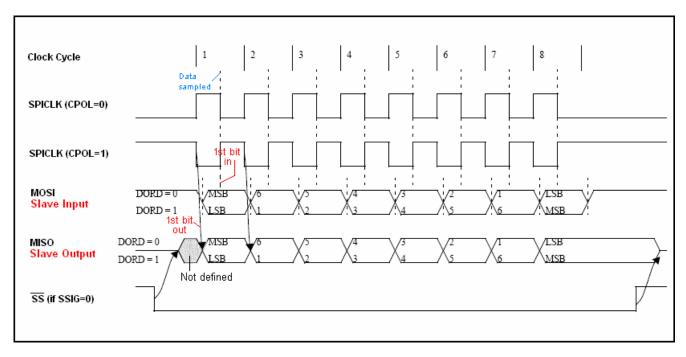

|     | 16.3.1. SPI Slave Transfer Format with CPHA=0                |     |

|     | 16.3.2. SPI Slave Transfer Format with CPHA=1                |     |

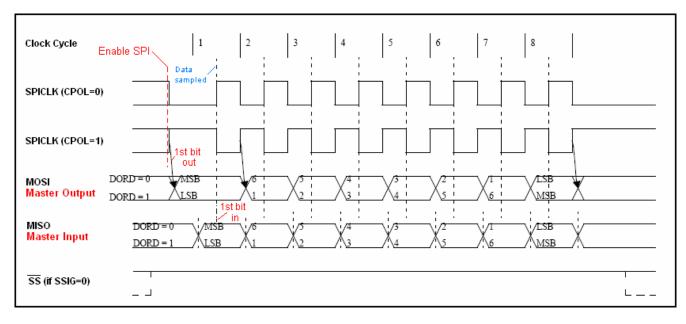

|     | 16.3.3. SPI Master Transfer Format with CPHA=0               | .50 |

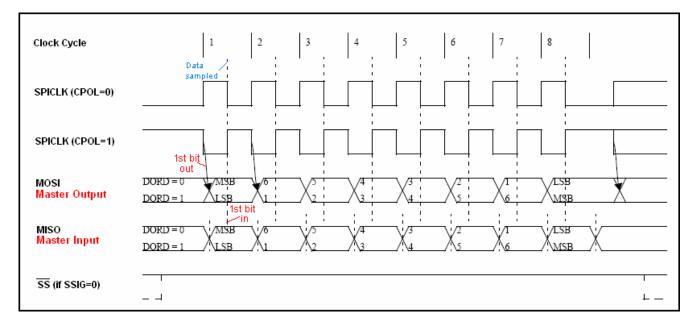

|     | 16.3.4. SPI Master Transfer Format with CPHA=1               | .50 |

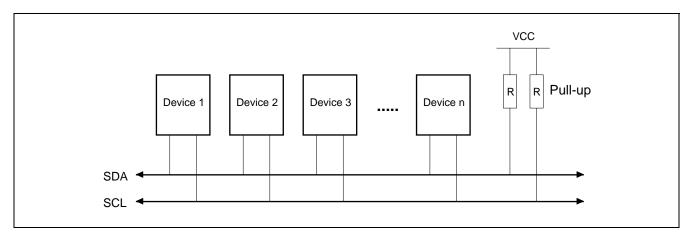

| 17. | 2-wire Serial Interface (TWSI)                               | 51  |

|     | 17.1. The Special Function Registers for TWSI                |     |

|     | 17.2. Operating Modes                                        |     |

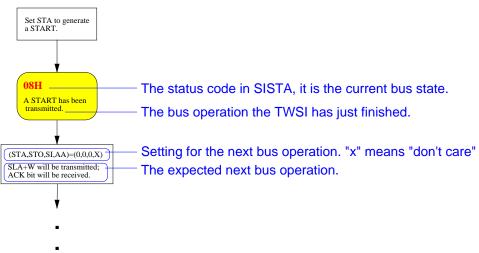

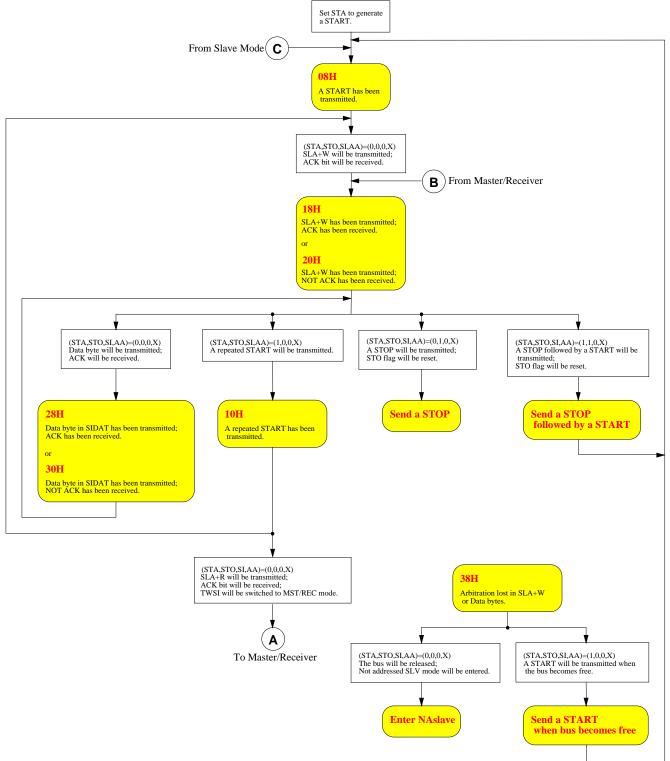

|     | 17.2.1. Master Transmitter Mode                              | .54 |

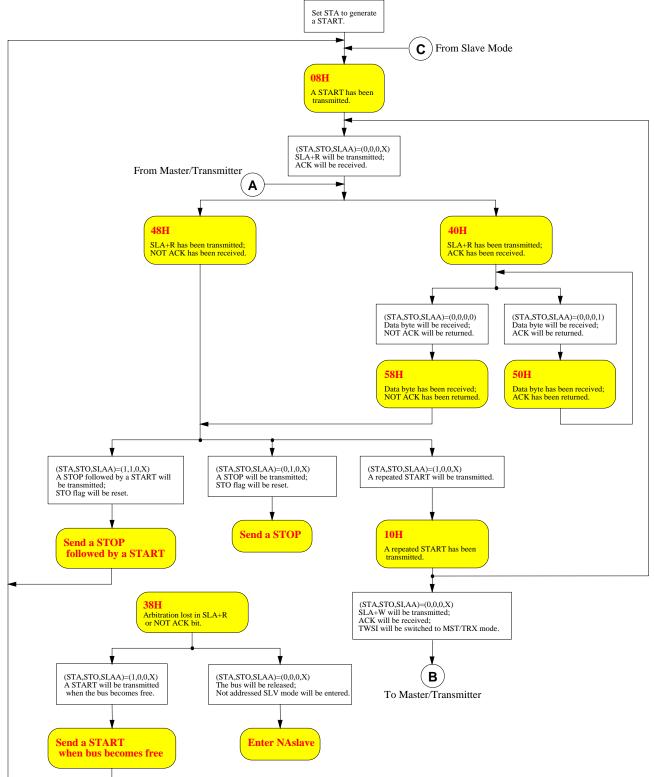

|     | 17.2.2. Master Receiver Mode                                 | .55 |

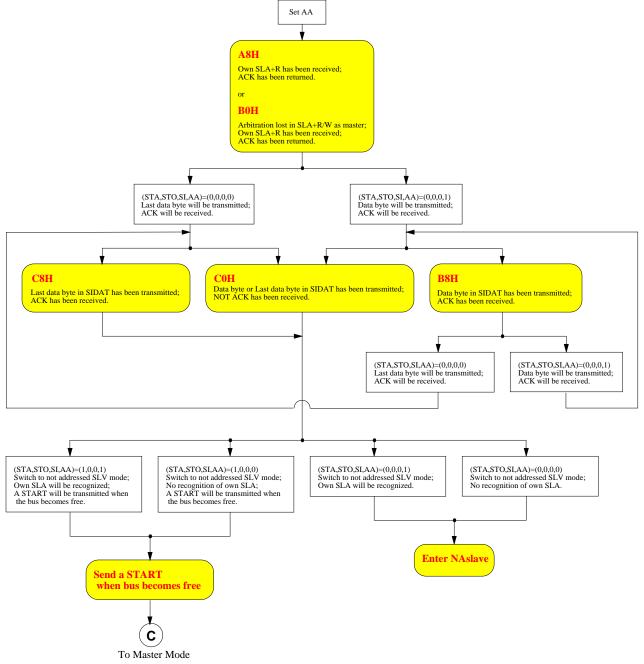

|     | 17.2.3. Slave Transmitter Mode                               |     |

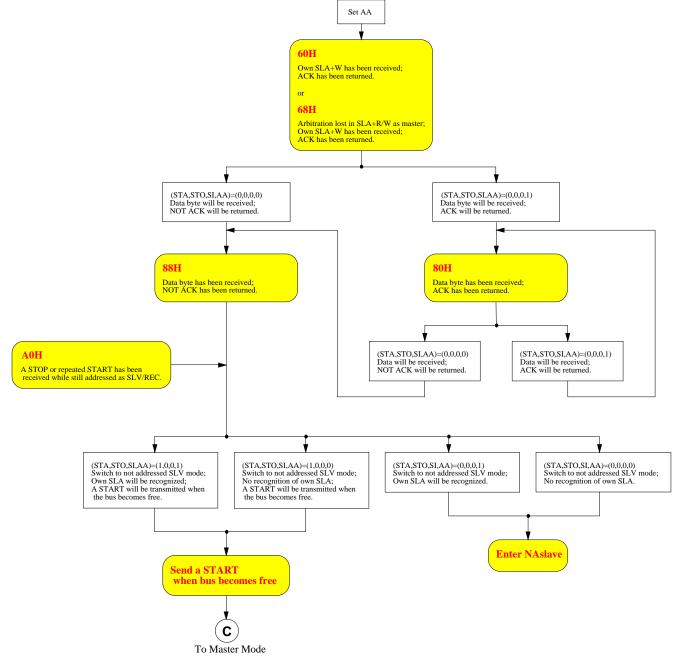

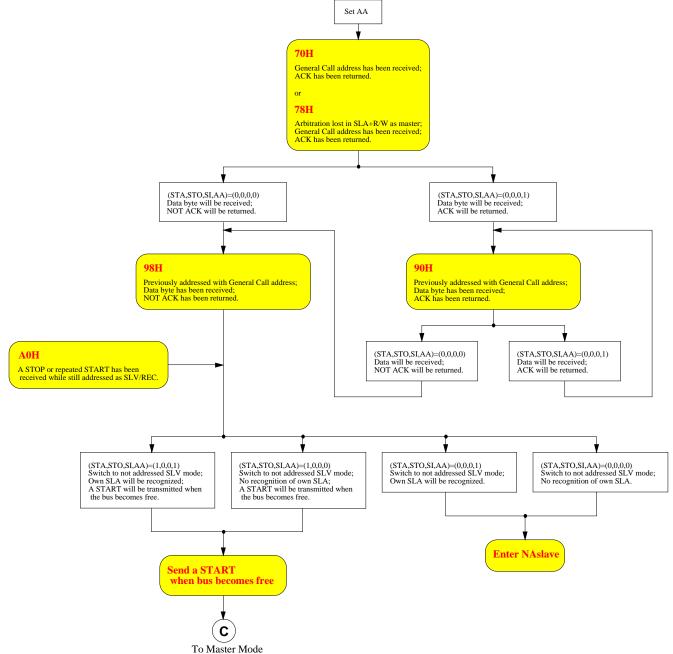

|     | 17.2.4. Slave Receiver Mode                                  |     |

|     | 17.3. Miscellaneous States                                   | .57 |

|     | 17.4. Using the TWSI                                         | .58 |

| 18. | One-Time-Enabled Watchdog Timer (WDT)                        |     |

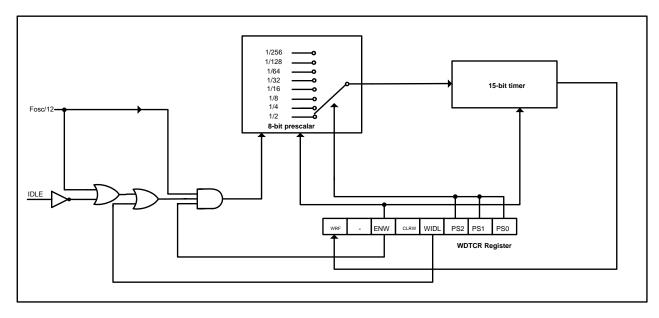

|     | 18.1. WDT Block Diagram                                      |     |

|     | 18.2. WDT During Idle and Power Down                         |     |

|     | 18.3. WDT Automatically Enabled by Hardware                  |     |

|     | 18.4. WDT Overflow Period                                    |     |

|     | 18.5. Sample Code for WDT                                    |     |

| 19. | Universal Serial Bus (USB)                                   |     |

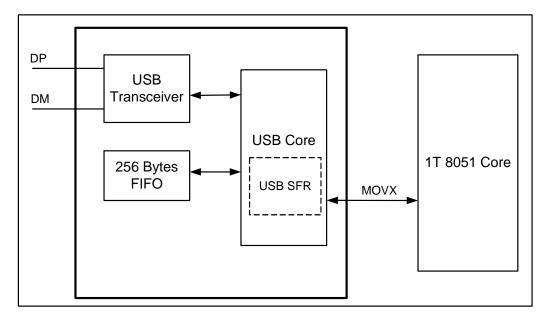

|     | 19.1. USB Block Diagram                                      |     |

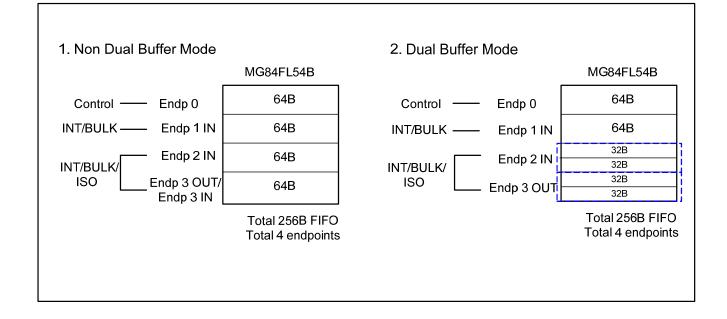

|     | 19.2. USB FIFO Management                                    |     |

|     | 19.3. USB Special Function Registers                         |     |

|     | 19.3.1. USB SFR Memory Mapping                               |     |

|     | 19.3.2. USB SFR Description                                  |     |

| 20. | In-System-Programming (ISP)                                  |     |

|     | 20.1. Description for ISP Operation                          |     |

|     | 20.2. Demo Program for ISP                                   |     |

| 21. | In-Application-Programming (IAP)                             |     |

|     | 21.1. IAP-memory Boundary/Range                              |     |

|     | 21.2. Update the data in the IAP-memory                      |     |

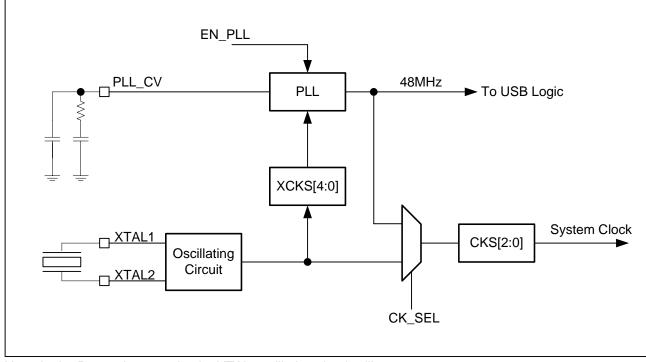

| 22  | System Clock                                                 |     |

|     | 22.1. Programmable System Clock                              |     |

|     | 22.2. On-chip XTAL Oscillating Driving Control               |     |

| 23. | Power-On Reset                                               |     |

|     |                                                              |     |

| 24. | Hardware Option                                  | 83 |

|-----|--------------------------------------------------|----|

| 25. | Hardware Option<br>Instruction Set               | 85 |

|     | 25.1. Arithmetic Operations                      | 86 |

|     | 25.2. Logic Operations                           | 87 |

|     | 25.3. Data Transfer                              | 88 |

|     | 25.4. Boolean Variable Manipulation              | 89 |

|     | 25.5. Program and Machine Control                |    |

| 26. | Absolute Maximum Rating                          |    |

|     | Electrical Characteristics                       |    |

|     | 27.1. Global DC Electrical Characteristics       | 91 |

|     | 27.2. USB Transceiver Electrical Characteristics | 92 |

| 28. | Field Applications                               | 93 |

|     | Order Information                                |    |

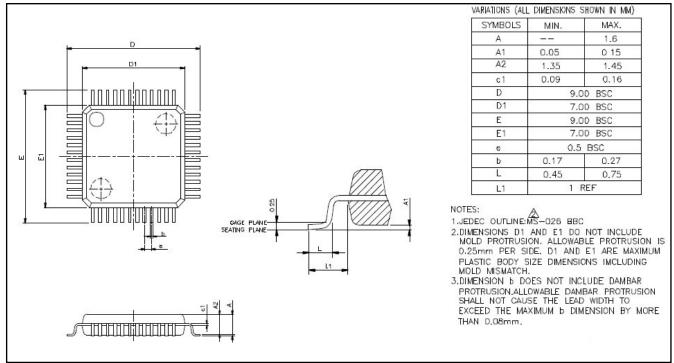

| 30. | Package Dimension                                | 93 |

|     | Revision History                                 |    |

|     |                                                  |    |

## 1. General Description

MG84FL54B is an enhanced single-chip 8-bit microcontroller manufactured in an advanced Embedded-Flash process. The instruction set is fully compatible with that of the 8051. With the enhanced CPU core, the device needs only 1 to 7 clock cycles to complete an instruction, and thus provides much higher performance than the standard 8051, which needs 12 to 48 clock cycles to complete an instruction. So, at the same performance as the standard 8051, the device can operate at a much lower speed and thereby greatly reduce the power consumption.

The device has on-chip 16KB Flash memory that is parallel programmable (via a universal programmer), In-System Programmable (via USB DFU). ISP allows the device to alter its own program memory without being removed from the actual end product under software control. This opens up a range of applications that need the ability to field update the application firmware. The other important and useful feature, In-Application-Programming (IAP), provides the device with the ability to save non-volatile data in its Flash memory.

And in addition to the 256 bytes of internal scratch-pad RAM, the device has 576 bytes of on-chip expanded RAM (XRAM) for the applications that require extra memory. The device has also four 8-bit I/O ports and one 4-bit I/O ports, three 16-bit timers/counters, a multi-source/two-priority-level/nested interrupt structure, an enhanced UART input. More important, the added features such as KBI, SPI, TWSI bus and USB1.1 make it a powerful microcontroller and suitable for wide field applications.

## 2. Features

- 1-T 8051 CPU Core

- 16K bytes of on-chip Flash program memory with ISP/IAP function

- 256 bytes internal scratch-pad RAM and 576 bytes on-chip expanded RAM (XRAM)

- Dual DPTR (Data Pointer register)

- Four and half configurable I/O ports

- Three 16-bits Timers

- Enhanced UART

- Two-priority-level interrupt structure

- Additional external interrupts, INT2 and INT3

- Keypad interrupt (P0)

- Wake-up from power-down mode

- Serial Peripheral Interface (SPI)

- 2-wire Serial Interface (TWSI)

- One-time-enabled Watch-dog Timer (WDT)

- Programmable system clock

- USB specification 2.0 and 1.1 compliant

- Built in full speed (12Mbps) USB transceiver

- Intel 8X931 like USB control flow

- One 256 bytes FIFO for USB endpoint-shared buffer

- Maximum 64 bytes data for EP0 control-in/out buffer

- Maximum 64 bytes data for EP1 bulk/interrupt-in buffer

- Maximum 64 bytes data for EP2 bulk/interrupt/isochronous-in buffer, it could be configured to two 32 bytes dual-buffer-mode in bulk and isochronous operating.

- Maximum 64 bytes data for EP3 bulk/interrupt/isochronous-out buffer, it could be configured to two 32 bytes dual-buffer-mode in bulk and isochronous operating. Additionally, it also can be configured to an interrupt-in buffer on EP3 function.

- Supports USB suspend/resume and remote wake-up event

- Software-controlled USB connection/disconnection mechanism

- Support USB DFU (Device Firmware Update)

- Power saving modes

- Idle mode

- Power-down mode

- Operating voltage

- 2.4 ~ 5.5V on VDD\_IO, 2.7V ~ 3.6V on VDD\_CORE and VDD\_PLL, 3.0V~3.6V on VDDA.

- Built-in Low-Voltage Reset circuit.

- Operating temperature

- Industrial (-40°C to +85°C)\*

- Maximum operating frequency

- Up to 24MHz, Industrial range

- Flash Quality criterion:

- Flash data endurance: 20K erase/write cycles

- Flash data retention: 100 years under room temperature

- 2-level code protection: SB (code scrambled) & LOCK (code locked)

- Package: LQFP-48

- \*: Tested by sampling.

## 3. Block Diagram

## 4. Pin Configurations

### 4.1. Pin-out for 48-pin Package

## 4.2. Pin Description

| Pin No. | Name                  | Туре | Description                                          |

|---------|-----------------------|------|------------------------------------------------------|

| 1       | VDDA                  | Р    | 3.3V Analog Power                                    |

| 2       | DP                    | I/O  | USB DP I/O.                                          |

| 3       | DM                    | I/O  | USB DM I/O.                                          |

| 4       | VSSA                  | Р    | Analog Ground.                                       |

| 5       | P4.3                  | I/O  | P4.3                                                 |

| 6       | P4.2                  | I/O  | P4.2                                                 |

| 7       | P4.1                  | I/O  | P4.1                                                 |

| 8       | VDD_PLL               | Р    | Power input of PLL.                                  |

| 9       | PLL_CV                | I/O  | Reference for internal PLL.                          |

| 10      | P3.0<br>/RXD          | I/O  | P3.0 & Serial port RXD.                              |

| 11      | P3.1<br>/TXD          | I/O  | P3.1 & Serial port TXD.                              |

| 12      | P3.2<br>/INT0         | I/O  | P3.2 & External interrupt 0.                         |

| 13      | P3.3<br>/INT1         | I/O  | P3.3 & External interrupt 1.                         |

| 14      | P3.4<br>/T0<br>/T0CKO | I/O  | P3.4, Timer 0 external input & Timer 0 clock output. |

| 15      | P3.5<br>/T1           | I/O  | P3.5 & Timer 1 external input.                       |

| 16      | P3.6<br>/INT2         | I/O  | P3.6 & External interrupt 2.                         |

| 17      | P3.7<br>/INT3         | I/O  | P3.7 & External interrupt 3.                         |

| 18      | P2.2                  | I/O  | P2.2.                                                |

| 19      | P2.3                  | I/O  | P2.3.                                                |

| 20      | VDD_IO                | Р    | Digital power for I/O pads.                          |

| 21      | VDD_CORE              | Р    | Digital power for I/O internal core logic.           |

| 22      | P1.0<br>/T2CKO        | I/O  | P1.0 & Timer 2 clock output.                         |

| 23      | P1.1                  | I/O  | P1.1                                                 |

| 24      | P1.2                  | I/O  | P1.2.                                                |

| 25      | P1.3                  | I/O  | P1.3.                                                |

| 26      | P1.4                  | I/O  | P1.4.                                                |

| 27      | P1.5                  | I/O  | P1.5.                                                |

| 28      | P1.6                  | I/O  | P1.6.                                                |

| 29      | P1.7                  | I/O  | P1.7.                                                |

| 30      | P0.0                  | I/O  | P0.0 & Keypad input 0.                               |

| 31      | P0.1                  | I/O  | P0.1 & Keypad input 1.                               |

| 32      | P0.2                  | I/O  | P0.2 & Keypad input 2.                               |

| 33      | P0.3                  | I/O  | P0.3 & Keypad input 3.                               |

| 34 | P0.4              | I/O | P0.4 & Keypad input 4.           |

|----|-------------------|-----|----------------------------------|

| 35 | P0.5              | I/O | P0.5 & Keypad input 5.           |

| 36 | RST               | I   | System reset input, high active. |

| 37 | P0.6              | I/O | P0.6 & Keypad input 6.           |

| 38 | P0.7              | I/O | P0.7 & Keypad input 7.           |

| 39 | P2.0<br>/TWSI_SCL | I/O | P2.0 & TWSI_SCL.                 |

| 40 | P2.1<br>/TWSI_SDA | I/O | P2.1 & TWSI_SDA.                 |

| 41 | P4.0              | I/O | P4.0                             |

| 42 | VSS               | Р   | Digital ground.                  |

| 43 | XOUT              | 0   | Crystal output pad.              |

| 44 | XIN               | Ι   | Crystal input pad.               |

| 45 | P2.4<br>/SPI_SSI  | I/O | P2.4 & SPI_ SSI.                 |

| 46 | P2.5<br>/SPI_MOSI | I/O | P2.5 & SPI_MOSI.                 |

| 47 | P2.6<br>/SPI_MISO | I/O | P2.6 & SPI_MISO.                 |

| 48 | P2.7<br>/SPI_CLK  | I/O | P2.7 & SPI_CLK.                  |

## 5. Special Function Registers (SFRs)

## 5.1. SFR Mapping

|     | 0/8   | 1/9   | 2/A    | 3/B    | 4/C    | 5/D    | 6/E   | 7/F    | _        |

|-----|-------|-------|--------|--------|--------|--------|-------|--------|----------|

| F8H | SICON |       |        |        |        |        |       |        | FFH      |

| F0H | В     |       |        |        |        |        |       |        | F7H      |

| E8H | P4    |       |        |        |        |        |       |        | EFH      |

| E0H | ACC   | WDTCR | IFD    | IFADRH | IFADRL |        | SCMD  | ISPCR  | E7H      |

| D8H |       |       |        |        |        |        |       |        | DFH      |

| D0H | PSW   | SIADR | SIDAT  | SISTA  |        | KBPATN | KBCON | KBMASK | D7H      |

| C8H | T2CON | T2MOD | RCAP2L | RCAP2H | TL2    | TH2    |       |        | CFH      |

| C0H | XICON |       |        |        |        |        |       | CKCON  | C7H      |

| B8H | IP    | SADEN |        |        |        |        |       | CKCON2 | BFH      |

| B0H | P3    | P3M0  | P3M1   | P4M0   | P4M1   |        |       |        | B7H      |

| A8H | IE    | SADDR |        |        |        | AUXIE  | AUXIP |        | AFH      |

| A0H | P2    |       |        |        |        |        | AUXR2 | TSTWD  | A7H      |

| 98H | SCON  | SBUF  |        |        |        |        |       |        | 9FH      |

| 90H | P1    | P1M0  | P1M1   | P0M0   | P0M1   | P2M0   | P2M1  |        | 97H      |

| 88H | TCON  | TMOD  | TL0    | TL1    | TH0    | TH1    | AUXR  |        | 8FH      |

| 80H | P0    | SP    | DPL    | DPH    | SPSTAT | SPCTL  | SPDAT | PCON   | 87H      |

| 1   | 0/8   | 1/9   | 2/A    | 3/B    | 4/C    | 5/D    | 6/E   | 7/F    | <b>_</b> |

## 5.2. The Standard 8051 SFRs

| SYMBOL          | DESCRIPTION           | ADDR |                            |                            | BIT                        | ADDRES                     | S & SYMB                    | OL                          |                            |                            | RESET |

|-----------------|-----------------------|------|----------------------------|----------------------------|----------------------------|----------------------------|-----------------------------|-----------------------------|----------------------------|----------------------------|-------|

| STWIBOL         | DESCRIPTION           | ADDK | Bit-7                      | Bit-6                      | Bit-5                      | Bit-4                      | Bit-3                       | Bit-2                       | Bit-1                      | Bit-0                      | VALUE |

| ACC*            | Accumulator           | E0H  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| в*              | B Register            | F0H  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| PSW*            | Program Status Word   | D0H  | D7H<br>CY                  | D6H<br>AC                  | <b>D5H</b><br>F0           | <b>D4H</b><br>RS1          | D3H<br>RS0                  | <b>D2H</b><br>OV            | D1H                        | D0H<br>P                   | 00H   |

| SP              | Stack Pointer         | 81H  |                            |                            |                            |                            |                             |                             |                            |                            | 07H   |

| DPH             | Data Pointer High     | 83H  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| DPL             | Data Pointer Low      | 82H  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| P0 <sup>*</sup> | Port 0                | 80H  | <b>87H</b><br>P0.7<br>KBI7 | <b>86H</b><br>P0.6<br>KBl6 | <b>85H</b><br>P0.5<br>KBI5 | <b>84H</b><br>P0.4<br>KBI4 | <b>83H</b><br>P0.3<br>KBI3  | <b>82H</b><br>P0.2<br>KBI2  | <b>81H</b><br>P0.1<br>KBI1 | <b>80H</b><br>P0.0<br>KBI0 | FFH   |

| P1*             | Port 1                | 90H  | 97H<br>P1.7                | <b>96H</b><br>P1.6         | <b>95H</b><br>P1.5         | <b>94H</b><br>P1.4         | <b>93H</b><br>P1.3          | <b>92H</b><br>P1.2          | 91H<br>P1.1                | <b>90H</b><br>P1.0         | FFH   |

| P2*             | Port 2                | АОН  | A7H<br>P2.7<br>SPICLK      | <b>A6H</b><br>P2.6<br>MISO | A5H<br>P2.5<br>MOSI        | <b>A4H</b><br>P2.4<br>/SS  | <b>A3H</b><br>P2.3          | <b>A2H</b><br>P2.2          | <b>A1H</b><br>P2.1<br>SDA  | A0H<br>P2.0<br>SCL         | FFH   |

| P3 <sup>*</sup> | Port 3                | B0H  | <b>B7H</b><br>P3.7<br>INT3 | <b>B6H</b><br>P3.6<br>INT2 | <b>B5H</b><br>P3.5<br>T1   | <b>B4H</b><br>P3.4<br>T0   | <b>B3H</b><br>P3.3<br>/INT1 | <b>B2H</b><br>P3.2<br>/INT0 | <b>B1H</b><br>P3.1<br>TXD  | <b>B0H</b><br>P3.0<br>RXD  | FFH   |

| IP*             | Interrupt Priority    | B8H  | BFH<br>PX3                 | BEH<br>PX2                 | BDH<br>PT2                 | BCH<br>PS                  | BBH<br>PT1                  | BAH<br>PX1                  | <b>B9H</b><br>PT0          | <b>B8H</b><br>PX0          | 00H   |

| IE*             | Interrupt Enable      | A8H  | AFH<br>EA                  | AEH                        | ADH<br>ET2                 | ACH<br>ES                  | ABH<br>ET1                  | AAH<br>EX1                  | <b>A9H</b><br>ET0          | A8H<br>EX0                 | 00H   |

| TMOD            | Timer Mode            | 89H  | GATE                       | C/-T                       | M1                         | M0                         | GATE                        | C/-T                        | M1                         | MO                         | 00H   |

| TCON*           | Timer Control         | 88H  | <b>8FH</b><br>TF1          | <b>8EH</b><br>TR1          | <b>8DH</b><br>TF0          | <b>8CH</b><br>TR0          | 8BH<br>IE1                  | <b>8AH</b><br>IT1           | <b>89H</b><br>IE0          | <b>88H</b><br>IT0          | 00H   |

| T2CON*          | Timer 2 Control       | C8H  | CFH<br>TF2                 | CEH<br>EXF2                | <b>CDH</b><br>RCLK         | CCH<br>TCLK                | CBH<br>EXEN2                | CAH<br>TR2                  | <b>С9Н</b><br>С/-Т2        | C8H<br>CP/-RL2             | 00H   |

| TH0             | Timer 0, High-byte    | 8CH  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| TL0             | Timer 0, Low-byte     | 8AH  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| TH1             | Timer 1, High-byte    | 8DH  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| TL1             | Timer 1, Low-byte     | 8BH  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| TH2             | Timer 2, High-byte    | CDH  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| TL2             | Timer 2, Low-byte     | ССН  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| RCAP2H          | Timer 2 Capture, High | СВН  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| RCAP2L          | Timer 2 Capture, Low  | CAH  |                            |                            |                            |                            |                             |                             |                            |                            | 00H   |

| SCON*           | Serial Port Control   | 98H  | 9FH<br>SM0/FE              | <b>9EH</b><br>SM1          | 9DH<br>SM2                 | 9CH<br>REN                 | <b>9BH</b><br>TB8           | <b>9AH</b><br>RB8           | 99H<br>TI                  | 98H<br>RI                  | 00H   |

| SBUF            | Serial Data Buffer    | 99H  |                            |                            |                            |                            |                             |                             |                            |                            | ххН   |

| PCON            | Power Control         | 87H  | SMOD                       | SMOD0                      | -                          | POF                        | GF1                         | GF0                         | PD                         | IDL                        | 00H   |

Notes:

\*: bit addressable

-: reserved bit

## 5.3. The Auxiliary SFRs

| SYMBOL         DESCRIPTION         ADDR         Bit-7         Bit-6         Bit-5         Bit-4           Interrupt         Bit-7         Bit-6         Bit-5         Bit-4         Bit-4           Interrupt         Control         Interrupt         CoH         C7H         Bit-6         Bit-5         Bit-4           AUXIE         Auxiliary<br>Interrupt Enable         ADH         EUSB         ETWSI         EKB         -           AUXIP         Auxiliary<br>Interrupt Priority         AEH         PUSB         PTWSI         PKB         -           //O Port         Auxiliary<br>Interrupt Priority         AEH         PUSB         PTWSI         PKB         -           P0M0         Port 0         Mode Register 0         93H         P0M0.7         P0M0.6         P0M1.5         P0M1.4           P1M0         Port 1         Mode Register 0         91H         P1M0.7         P1M0.6         P1M0.5         P1M1.4           P1M0         Port 1         Mode Register 1         92H         P1M1.7         P1M1.6         P1M1.5         P1M1.4           P2M0         Port 2         Mode Register 1         92H         P2M1.7         P2M0.6         P2M0.5         P2M0.4           P3M1         Po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit-3  C3H IL2  -  -  EBH P4.3  P0M0.3  P0M1.3  P1M0.3  P1M0.3  P2M0.3  P2M1.3  P3M0.3  P3M0.3  P3M1.3  P4M0.3  P4M0.3  P4M0.3                                                                              | Bit-2<br>C2H<br>EX2<br>-<br>-<br>POM0.2<br>P0M0.2<br>P0M0.2<br>P0M1.2<br>P1M0.2<br>P1M1.2<br>P2M0.2<br>P1M1.2<br>P2M0.2<br>P1M1.2<br>P2M0.2<br>P1M1.2<br>P2M1.2<br>P3M0.2<br>P3M1.2<br>P4M0.2<br>P4M0.2 | Bit-1<br>IE2<br>-<br>-<br>E9H<br>P4.1<br>P0M0.1<br>P0M0.1<br>P1M0.1<br>P1M0.1<br>P1M1.1<br>P2M0.1<br>P2M0.1<br>P3M0.1<br>P3M0.1<br>P3M0.1<br>P3M0.1<br>P3M0.1<br>P3M0.1<br>P3M0.1<br>P3M0.1                            | Bit-0<br>IT2<br>ESPI<br>PSPI<br>PSPI<br>P0M0.0<br>P0M0.0<br>P0M1.0<br>P1M0.0<br>P1M1.0<br>P2M0.0<br>P2M1.0<br>P3M0.0<br>P3M1.0<br>P3M1.0<br>P3M1.0<br>P3M1.0 | VALUE 00H 00H 00H 00H 00H 00H 00H 00H 00H 00                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| XICON*External<br>ControlInterrupt<br>ControlCOHC7H<br>IL3C6H<br>EX3C5H<br>IE3C4H<br>IT3AUXIEAuxiliary<br>Interrupt EnableADHEUSBETWSIEKB-AUXIPAuxiliary<br>Interrupt PriorityAEHPUSBPTWSIPKB-//O Port//O Port//O PortP4*Port 4E8HEFHEEHEDHECHP0M0Port 0 Mode Register 093HP0M0.7P0M0.6P0M0.5P0M0.4P0M1Port 0 Mode Register 194HP0M1.7P0M1.6P0M1.5P0M1.4P1M0Port 1 Mode Register 091HP1M0.7P1M0.6P1M0.5P1M0.4P1M1Port 1 Mode Register 192HP1M1.7P1M1.6P1M1.5P1M1.4P2M0Port 2 Mode Register 095HP2M0.7P2M0.6P2M0.5P2M0.4P2M1Port 2 Mode Register 196HP2M1.7P2M1.6P2M1.5P2M1.4P3M0Port 3 Mode Register 196HP3M1.7P3M0.6P3M0.5P3M0.4P3M1Port 4 Mode Register 1B2HP3M1.7P3M1.6P3M1.5P3M1.4P4M0Port 4 Mode Register 1B4HP4M1Port 4 Mode Register 1B4HP4M1Port 4 Mode Register 1B4HP4M1Port 4 Mode Register 1B4HP4M1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IL2         -         -         P0M0.3         P0M1.3         P1M0.3         P1M0.3         P1M0.3         P2M0.3         P2M0.3         P3M0.3         P3M0.3         P4M0.3         P4M0.3         P4M1.3 | EX2<br>-<br>-<br>P0M0.2<br>P0M0.2<br>P0M1.2<br>P1M0.2<br>P1M1.2<br>P2M0.2<br>P2M1.2<br>P3M0.2<br>P3M0.2<br>P3M1.2<br>P4M0.2                                                                             | IE2           -           -           P0M0.1           P0M0.1           P1M0.1           P1M0.1           P1M0.1           P2M0.1           P2M0.1           P3M0.1           P3M0.1           P4M0.1           P4M0.1 | IT2<br>ESPI<br>PSPI<br>P4.0<br>P0M0.0<br>P0M1.0<br>P1M0.0<br>P1M0.0<br>P1M1.0<br>P2M0.0<br>P3M0.0<br>P3M1.0<br>P3M1.0<br>P4M0.0                              | 00H<br>00H<br>FFH<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H |

| XICON         Control         CON         IL3         EX3         IE3         IT3           AUXIE         Auxiliary<br>Interrupt Enable         ADH         EUSB         ETWSI         EKB         -           AUXIP         Auxiliary<br>Interrupt Priority         AEH         PUSB         PTWSI         PKB         -           I/O Port         Auxiliary<br>Interrupt Priority         AEH         PUSB         PTWSI         PKB         -           I/O Port         Auxiliary<br>Interrupt Priority         AEH         PUSB         PTWSI         PKB         -           I/O Port         Port 4         E8H         EFH         EEH         EDH         ECH           P0M0         Port 0 Mode Register 0         93H         P0M0.7         P0M0.6         P0M0.5         P0M0.4           P1M0         Port 1 Mode Register 0         91H         P1M0.7         P1M0.6         P1M0.5         P1M0.4           P1M0         Port 1 Mode Register 0         95H         P2M0.7         P2M0.6         P2M0.5         P2M0.4           P2M1         Port 2 Mode Register 1         96H         P2M1.7         P2M1.6         P2M1.5         P3M1.4           P3M1         Port 3 Mode Register 1         B2H         P3M1.7 <t< th=""><th>IL2         -         -         P0M0.3         P0M1.3         P1M0.3         P1M0.3         P1M0.3         P2M0.3         P2M0.3         P3M0.3         P3M0.3         P4M0.3         P4M0.3         P4M1.3</th><th>EX2<br/>-<br/>-<br/>P0M0.2<br/>P0M0.2<br/>P0M1.2<br/>P1M0.2<br/>P1M1.2<br/>P2M0.2<br/>P2M1.2<br/>P3M0.2<br/>P3M0.2<br/>P3M1.2<br/>P4M0.2</th><th>IE2           -           -           P0M0.1           P0M0.1           P1M0.1           P1M0.1           P1M0.1           P2M0.1           P2M0.1           P3M0.1           P3M0.1           P4M0.1           P4M0.1</th><th>IT2<br/>ESPI<br/>PSPI<br/>P4.0<br/>P0M0.0<br/>P0M1.0<br/>P1M0.0<br/>P1M0.0<br/>P1M1.0<br/>P2M0.0<br/>P3M0.0<br/>P3M1.0<br/>P3M1.0<br/>P4M0.0</th><th>00H<br/>00H<br/>FFH<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H</th></t<> | IL2         -         -         P0M0.3         P0M1.3         P1M0.3         P1M0.3         P1M0.3         P2M0.3         P2M0.3         P3M0.3         P3M0.3         P4M0.3         P4M0.3         P4M1.3 | EX2<br>-<br>-<br>P0M0.2<br>P0M0.2<br>P0M1.2<br>P1M0.2<br>P1M1.2<br>P2M0.2<br>P2M1.2<br>P3M0.2<br>P3M0.2<br>P3M1.2<br>P4M0.2                                                                             | IE2           -           -           P0M0.1           P0M0.1           P1M0.1           P1M0.1           P1M0.1           P2M0.1           P2M0.1           P3M0.1           P3M0.1           P4M0.1           P4M0.1 | IT2<br>ESPI<br>PSPI<br>P4.0<br>P0M0.0<br>P0M1.0<br>P1M0.0<br>P1M0.0<br>P1M1.0<br>P2M0.0<br>P3M0.0<br>P3M1.0<br>P3M1.0<br>P4M0.0                              | 00H<br>00H<br>FFH<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H |

| AUXIE         Interrupt Enable         AUH         EUSB         ETWSI         EKB         -           AUXIP         Auxiliary<br>Interrupt Priority         AEH         PUSB         PTWSI         PKB         -           P4*         Port 4         E8H         EFH         EEH         EDH         ECH         -         -           P0M0         Port 0 Mode Register 0         93H         P0M0.7         P0M0.6         P0M0.5         P0M0.4           P0M1         Port 0 Mode Register 1         94H         P0M1.7         P0M1.6         P0M1.5         P0M0.4           P1M0         Port 1 Mode Register 0         91H         P1M0.7         P1M0.6         P1M1.5         P1M1.4           P2M0         Port 2 Mode Register 0         95H         P2M0.7         P2M0.6         P2M0.5         P2M0.4           P2M1         Port 2 Mode Register 0         95H         P2M0.7         P2M0.6         P2M1.5         P2M1.4           P3M0         Port 3 Mode Register 0         B1H         P3M0.7         P3M0.6         P3M1.5         P3M1.4           P4M0         Port 4 Mode Register 0         B3H         -         -         -         -           P4M1         Port 4 Mode Register 1         B4H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -<br><b>EBH</b><br>P4.3<br>P0M0.3<br>P0M1.3<br>P1M0.3<br>P1M0.3<br>P1M1.3<br>P2M0.3<br>P2M1.3<br>P3M0.3<br>P3M0.3<br>P4M0.3<br>P4M1.3                                                                       | -<br>P0M0.2<br>P0M1.2<br>P1M0.2<br>P1M1.2<br>P2M0.2<br>P2M1.2<br>P3M0.2<br>P3M1.2<br>P4M0.2<br>P4M1.2                                                                                                   | -<br><b>E9H</b><br>P4.1<br>P0M0.1<br>P1M0.1<br>P1M0.1<br>P1M1.1<br>P2M0.1<br>P2M1.1<br>P3M0.1<br>P3M0.1<br>P4M0.1<br>P4M1.1                                                                                            | PSPI<br>P0M0.0<br>P0M1.0<br>P1M0.0<br>P1M1.0<br>P2M0.0<br>P2M1.0<br>P3M0.0<br>P3M1.0<br>P4M0.0<br>P4M1.0                                                     | 00H<br>FFH<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H |

| AUXIP         Interrupt Priority         AEA         POSB         PTWSI         PKB         -           I/O Port         Port 4         E8H         EFH         EEH         EDH         ECH           P0M0         Port 0 Mode Register 0         93H         P0M0.7         P0M0.6         P0M0.5         P0M0.4           P0M1         Port 0 Mode Register 0         93H         P0M1.7         P0M1.6         P0M1.5         P0M1.4           P1M0         Port 1 Mode Register 0         91H         P1M0.7         P0M0.6         P1M0.5         P1M0.4           P1M1         Port 1 Mode Register 1         92H         P1M1.7         P1M1.6         P1M1.5         P1M1.4           P2M0         Port 2 Mode Register 0         95H         P2M0.7         P2M0.6         P2M0.5         P2M0.4           P2M1         Port 2 Mode Register 0         96H         P2M1.7         P2M1.6         P2M1.5         P2M1.4           P3M0         Port 3 Mode Register 0         B1H         P3M0.7         P3M0.6         P3M0.5         P3M0.4           P3M1         Port 4 Mode Register 1         B2H         P3M1.7         P3M1.6         P3M1.5         P3M1.4           P4M0         Port 4 Mode Register 1         B4H <t< td=""><td>P4.3         P0M0.3         P0M1.3         P1M0.3         P1M0.3         P2M0.3         P2M0.3         P3M0.3         P3M1.3         P4M0.3         P4M1.3</td><td>EAH<br/>P4.2<br/>P0M0.2<br/>P0M1.2<br/>P1M0.2<br/>P1M1.2<br/>P2M0.2<br/>P2M1.2<br/>P3M0.2<br/>P3M1.2<br/>P4M0.2<br/>P4M1.2</td><td>E9H<br/>P4.1<br/>P0M0.1<br/>P0M1.1<br/>P1M0.1<br/>P1M1.1<br/>P2M0.1<br/>P2M1.1<br/>P3M0.1<br/>P3M1.1<br/>P4M0.1<br/>P4M1.1</td><td>E8H<br/>P4.0<br/>P0M0.0<br/>P0M1.0<br/>P1M0.0<br/>P1M1.0<br/>P2M0.0<br/>P2M1.0<br/>P3M0.0<br/>P3M1.0<br/>P4M0.0<br/>P4M1.0</td><td>FFH<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H</td></t<>                                                                                                                                                                                 | P4.3         P0M0.3         P0M1.3         P1M0.3         P1M0.3         P2M0.3         P2M0.3         P3M0.3         P3M1.3         P4M0.3         P4M1.3                                                  | EAH<br>P4.2<br>P0M0.2<br>P0M1.2<br>P1M0.2<br>P1M1.2<br>P2M0.2<br>P2M1.2<br>P3M0.2<br>P3M1.2<br>P4M0.2<br>P4M1.2                                                                                         | E9H<br>P4.1<br>P0M0.1<br>P0M1.1<br>P1M0.1<br>P1M1.1<br>P2M0.1<br>P2M1.1<br>P3M0.1<br>P3M1.1<br>P4M0.1<br>P4M1.1                                                                                                        | E8H<br>P4.0<br>P0M0.0<br>P0M1.0<br>P1M0.0<br>P1M1.0<br>P2M0.0<br>P2M1.0<br>P3M0.0<br>P3M1.0<br>P4M0.0<br>P4M1.0                                              | FFH<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H |

| P4*Port 4E8HEFHEEHEDHECHP0M0Port 0 Mode Register 093HP0M0.7P0M0.6P0M0.5P0M0.4P0M1Port 0 Mode Register 194HP0M1.7P0M1.6P0M1.5P0M1.4P1M0Port 1 Mode Register 091HP1M0.7P1M0.6P1M0.5P1M0.4P1M1Port 1 Mode Register 192HP1M1.7P1M0.6P1M0.5P1M0.4P2M0Port 2 Mode Register 095HP2M0.7P2M0.6P2M0.5P2M0.4P2M1Port 2 Mode Register 196HP2M1.7P2M1.6P2M1.5P2M1.4P3M0Port 3 Mode Register 0B1HP3M0.7P3M0.6P3M0.5P3M0.4P3M1Port 3 Mode Register 1B2HP3M1.7P3M1.6P3M1.5P3M1.4P4M0Port 4 Mode Register 0B3HP4M1Port 4 Mode Register 1B4HP4M1Port 4 Mode Register 1B4HP4M1Port 4 Mode Register 1B4HF4M1Port 4 Mode Register 1B4HF4M1Port 4 Mode Register 1B4HF4M1Port 4 Mode Register 1D5HKBCONKeypad ControlD6HKBMASKKeypad MaskD7H <td>P4.3         P0M0.3         P0M1.3         P1M0.3         P1M0.3         P2M0.3         P2M0.3         P3M0.3         P3M1.3         P4M0.3         P4M1.3</td> <td>P4.2<br/>P0M0.2<br/>P0M1.2<br/>P1M0.2<br/>P1M1.2<br/>P2M0.2<br/>P2M1.2<br/>P3M0.2<br/>P3M0.2<br/>P3M1.2<br/>P4M0.2</td> <td>P4.1           P0M0.1           P0M1.1           P1M0.1           P1M0.1           P2M0.1           P2M0.1           P3M0.1           P3M0.1           P4M0.1           P4M0.1</td> <td>P4.0<br/>P0M0.0<br/>P0M1.0<br/>P1M0.0<br/>P1M1.0<br/>P2M0.0<br/>P2M1.0<br/>P3M0.0<br/>P3M1.0<br/>P4M0.0<br/>P4M1.0</td> <td>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H<br/>00H</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P4.3         P0M0.3         P0M1.3         P1M0.3         P1M0.3         P2M0.3         P2M0.3         P3M0.3         P3M1.3         P4M0.3         P4M1.3                                                  | P4.2<br>P0M0.2<br>P0M1.2<br>P1M0.2<br>P1M1.2<br>P2M0.2<br>P2M1.2<br>P3M0.2<br>P3M0.2<br>P3M1.2<br>P4M0.2                                                                                                | P4.1           P0M0.1           P0M1.1           P1M0.1           P1M0.1           P2M0.1           P2M0.1           P3M0.1           P3M0.1           P4M0.1           P4M0.1                                         | P4.0<br>P0M0.0<br>P0M1.0<br>P1M0.0<br>P1M1.0<br>P2M0.0<br>P2M1.0<br>P3M0.0<br>P3M1.0<br>P4M0.0<br>P4M1.0                                                     | 00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H |

| P4*         Port 4         E8H         Port 0         Port 1         Port 2         Port 3         Port 4         Port 4         Port 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P4.3         P0M0.3         P0M1.3         P1M0.3         P1M0.3         P2M0.3         P2M0.3         P3M0.3         P3M1.3         P4M0.3         P4M1.3                                                  | P4.2<br>P0M0.2<br>P0M1.2<br>P1M0.2<br>P1M1.2<br>P2M0.2<br>P2M1.2<br>P3M0.2<br>P3M0.2<br>P3M1.2<br>P4M0.2                                                                                                | P4.1           P0M0.1           P0M1.1           P1M0.1           P1M0.1           P2M0.1           P2M0.1           P3M0.1           P3M0.1           P4M0.1           P4M0.1                                         | P4.0<br>P0M0.0<br>P0M1.0<br>P1M0.0<br>P1M1.0<br>P2M0.0<br>P2M1.0<br>P3M0.0<br>P3M1.0<br>P4M0.0<br>P4M1.0                                                     | 00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H |

| P0M1         Port 0 Mode Register 1         94H         P0M1.7         P0M1.6         P0M1.5         P0M1.4           P1M0         Port 1 Mode Register 0         91H         P1M0.7         P1M0.6         P1M0.5         P1M0.4           P1M1         Port 1 Mode Register 0         92H         P1M1.7         P1M1.6         P1M1.5         P1M1.4           P2M0         Port 2 Mode Register 0         95H         P2M0.7         P2M0.6         P2M0.5         P2M0.4           P2M1         Port 2 Mode Register 0         95H         P2M0.7         P2M0.6         P2M0.5         P2M0.4           P2M1         Port 2 Mode Register 0         95H         P2M0.7         P2M0.6         P2M0.5         P2M0.4           P3M0         Port 3 Mode Register 0         B1H         P3M0.7         P3M0.6         P3M0.5         P3M0.4           P3M1         Port 3 Mode Register 1         B2H         P3M1.7         P3M1.6         P3M1.5         P3M1.4           P4M0         Port 4 Mode Register 1         B2H         P3M1.7         P3M1.6         P3M1.5         P3M1.4           P4M1         Port 4 Mode Register 1         B4H         -         -         -         -           KBCON         Keypad Pattern         D5H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P0M1.3<br>P1M0.3<br>P1M1.3<br>P2M0.3<br>P2M1.3<br>P3M0.3<br>P3M1.3<br>P4M0.3<br>P4M1.3                                                                                                                      | P0M1.2<br>P1M0.2<br>P1M1.2<br>P2M0.2<br>P2M1.2<br>P3M0.2<br>P3M1.2<br>P4M0.2<br>P4M1.2                                                                                                                  | P0M1.1<br>P1M0.1<br>P1M1.1<br>P2M0.1<br>P2M1.1<br>P3M0.1<br>P3M1.1<br>P4M0.1<br>P4M1.1                                                                                                                                 | P0M1.0<br>P1M0.0<br>P1M1.0<br>P2M0.0<br>P2M1.0<br>P3M0.0<br>P3M1.0<br>P4M0.0<br>P4M1.0                                                                       | 00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H |

| P1M0         Port 1 Mode Register 0         91H         P1M0.7         P1M0.6         P1M0.5         P1M0.4           P1M1         Port 1 Mode Register 1         92H         P1M1.7         P1M1.6         P1M1.5         P1M1.4           P2M0         Port 2 Mode Register 0         95H         P2M0.7         P2M0.6         P2M0.5         P2M0.4           P2M1         Port 2 Mode Register 0         96H         P2M1.7         P2M1.6         P2M1.5         P2M1.4           P3M0         Port 3 Mode Register 0         B1H         P3M0.7         P3M0.6         P3M0.5         P3M0.4           P3M1         Port 3 Mode Register 1         B2H         P3M1.7         P3M1.6         P3M1.5         P3M1.4           P4M0         Port 4 Mode Register 1         B4H         -         -         -         -           P4M1         Port 4 Mode Register 1         B4H         -         -         -         -           F4M1         Port 4 Mode Register 1         B4H         -         -         -         -           F4M1         Port 4 Mode Register 1         B4H         -         -         -         -           KBCON         Keypad Pattern         D5H         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P1M0.3<br>P1M1.3<br>P2M0.3<br>P2M1.3<br>P3M0.3<br>P3M1.3<br>P4M0.3<br>P4M1.3                                                                                                                                | P1M0.2<br>P1M1.2<br>P2M0.2<br>P2M1.2<br>P3M0.2<br>P3M1.2<br>P4M0.2<br>P4M1.2                                                                                                                            | P1M0.1<br>P1M1.1<br>P2M0.1<br>P2M1.1<br>P3M0.1<br>P3M1.1<br>P4M0.1<br>P4M1.1                                                                                                                                           | P1M0.0<br>P1M1.0<br>P2M0.0<br>P2M1.0<br>P3M0.0<br>P3M1.0<br>P4M0.0<br>P4M1.0                                                                                 | 00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>FFH        |

| P1M1         Port 1 Mode Register 1         92H         P1M1.7         P1M1.6         P1M1.5         P1M1.4           P2M0         Port 2 Mode Register 0         95H         P2M0.7         P2M0.6         P2M0.5         P2M0.4           P2M1         Port 2 Mode Register 0         96H         P2M1.7         P2M1.6         P2M1.5         P2M1.4           P3M0         Port 3 Mode Register 0         B1H         P3M0.7         P3M0.6         P3M0.5         P3M0.4           P3M1         Port 3 Mode Register 0         B1H         P3M0.7         P3M1.6         P3M1.5         P3M1.4           P4M0         Port 4 Mode Register 0         B3H         -         -         -         -           P4M1         Port 4 Mode Register 1         B4H         -         -         -         -           P4M1         Port 4 Mode Register 1         B4H         -         -         -         -           F4M1         Port 4 Mode Register 1         B4H         -         -         -         -           F4M1         Port 4 Mode Register 1         D6H         -         -         -         -           KBCON         Keypad Control         D6H         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P1M1.3<br>P2M0.3<br>P2M1.3<br>P3M0.3<br>P3M1.3<br>P4M0.3<br>P4M1.3                                                                                                                                          | P1M1.2<br>P2M0.2<br>P2M1.2<br>P3M0.2<br>P3M1.2<br>P4M0.2<br>P4M1.2                                                                                                                                      | P1M1.1<br>P2M0.1<br>P2M1.1<br>P3M0.1<br>P3M1.1<br>P4M0.1<br>P4M1.1                                                                                                                                                     | P1M1.0<br>P2M0.0<br>P2M1.0<br>P3M0.0<br>P3M1.0<br>P4M0.0<br>P4M1.0                                                                                           | 00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>FFH        |

| P2M0         Port 2 Mode Register 0         95H         P2M0.7         P2M0.6         P2M0.5         P2M0.4           P2M1         Port 2 Mode Register 1         96H         P2M1.7         P2M1.6         P2M1.5         P2M1.4           P3M0         Port 3 Mode Register 0         B1H         P3M0.7         P3M0.6         P3M0.5         P3M0.4           P3M1         Port 3 Mode Register 0         B1H         P3M0.7         P3M1.6         P3M1.5         P3M1.4           P4M0         Port 4 Mode Register 0         B3H         -         -         -         -           P4M1         Port 4 Mode Register 1         B4H         -         -         -         -         -           P4M1         Port 4 Mode Register 1         B4H         -         -         -         -         -           P4M1         Port 4 Mode Register 1         B4H         -         -         -         -         -         -         -           KBCON         Keypad Control         D6H         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P2M0.3<br>P2M1.3<br>P3M0.3<br>P3M1.3<br>P4M0.3<br>P4M1.3                                                                                                                                                    | P2M0.2<br>P2M1.2<br>P3M0.2<br>P3M1.2<br>P4M0.2<br>P4M1.2                                                                                                                                                | P2M0.1<br>P2M1.1<br>P3M0.1<br>P3M1.1<br>P4M0.1<br>P4M1.1                                                                                                                                                               | P2M0.0<br>P2M1.0<br>P3M0.0<br>P3M1.0<br>P4M0.0<br>P4M1.0                                                                                                     | 00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>FFH               |

| P2M1Port 2 Mode Register 196HP2M1.7P2M1.6P2M1.5P2M1.4P3M0Port 3 Mode Register 0B1HP3M0.7P3M0.6P3M0.5P3M0.4P3M1Port 3 Mode Register 1B2HP3M1.7P3M1.6P3M1.5P3M1.4P4M0Port 4 Mode Register 0B3HP4M1Port 4 Mode Register 1B4HP4M1Port 4 Mode Register 1B4HKeypad InterruptB4HKBCONKeypad ControlD6HKBMASKKeypad MaskD7HSADENSlave Address MaskB9HSADDRSlave AddressA9HSICON*TWSI Control RegisterF8HCR2ENSISTASTOSIADRTWSI AddressD1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P2M1.3<br>P3M0.3<br>P3M1.3<br>P4M0.3<br>P4M1.3                                                                                                                                                              | P2M1.2<br>P3M0.2<br>P3M1.2<br>P4M0.2<br>P4M1.2                                                                                                                                                          | P2M1.1<br>P3M0.1<br>P3M1.1<br>P4M0.1<br>P4M1.1                                                                                                                                                                         | P2M1.0<br>P3M0.0<br>P3M1.0<br>P4M0.0<br>P4M1.0                                                                                                               | 00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>FFH                      |

| P3M0Port 3 Mode Register 0B1HP3M0.7P3M0.6P3M0.5P3M0.4P3M1Port 3 Mode Register 1B2HP3M1.7P3M1.6P3M1.5P3M1.4P4M0Port 4 Mode Register 0B3HP4M1Port 4 Mode Register 1B4HP4M1Port 4 Mode Register 1B4HKeypad InterruptB4HKBCONKeypad ControlD6HKBPATNKeypad PatternD5HKBMASKKeypad MaskD7HSADENSlave Address MaskB9HSICON*TWSI Control RegisterF8HCR2ENSISTASTOSIADRTWSI AddressD1H(Own Slave AddressAddress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P3M0.3<br>P3M1.3<br>P4M0.3<br>P4M1.3                                                                                                                                                                        | P3M0.2<br>P3M1.2<br>P4M0.2<br>P4M1.2                                                                                                                                                                    | P3M0.1<br>P3M1.1<br>P4M0.1<br>P4M1.1                                                                                                                                                                                   | P3M0.0<br>P3M1.0<br>P4M0.0<br>P4M1.0                                                                                                                         | 00H<br>00H<br>00H<br>00H<br>00H<br>FFH                             |

| P3M1Port 3 Mode Register 1B2HP3M1.7P3M1.6P3M1.5P3M1.4P4M0Port 4 Mode Register 0B3HP4M1Port 4 Mode Register 1B4HP4M1Port 4 Mode Register 1B4HKeypad InterruptKBCONKeypad ControlD6HKBPATNKeypad PatternD5HKBMASKKeypad MaskD7HSADENSlave Address MaskB9HSADDRSlave AddressA9HSICON*TWSI Control RegisterF8HCR2ENSISTASTOSIADRTWSI AddressD1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P3M1.3<br>P4M0.3<br>P4M1.3                                                                                                                                                                                  | P3M1.2<br>P4M0.2<br>P4M1.2                                                                                                                                                                              | P3M1.1<br>P4M0.1<br>P4M1.1                                                                                                                                                                                             | P3M1.0<br>P4M0.0<br>P4M1.0                                                                                                                                   | 00H<br>00H<br>00H<br>00H<br>FFH                                    |

| P4M0       Port 4 Mode Register 0       B3H       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P4M0.3<br>P4M1.3                                                                                                                                                                                            | P4M0.2<br>P4M1.2                                                                                                                                                                                        | P4M0.1<br>P4M1.1                                                                                                                                                                                                       | P4M0.0<br>P4M1.0                                                                                                                                             | 00H<br>00H<br>00H<br>FFH                                           |

| P4M1       Port 4 Mode Register 1       B4H       -       -       -       -         Keypad Interrupt       KBCON       Keypad Control       D6H       -       -       -       -         KBCON       Keypad Control       D6H       -       -       -       -         KBCN       Keypad Control       D6H       -       -       -       -         KBASK       Keypad Pattern       D5H       -       -       -       -         KBMASK       Keypad Mask       D7H       -       -       -       -         Serial Port       -       -       -       -       -       -         SADEN       Slave Address Mask       B9H       -       -       -       -         SADDR       Slave Address       A9H       -       -       -       -         SICON*       TWSI Control Register       F8H       CR2       ENSI       STA       STO         SIADR       TWSI Address       D1H       (Own Slave Address)       Control Register       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P4M1.3                                                                                                                                                                                                      | P4M1.2                                                                                                                                                                                                  | P4M1.1                                                                                                                                                                                                                 | P4M1.0                                                                                                                                                       | 00H<br>00H<br>FFH                                                  |

| Keypad Interrupt         KBCON       Keypad Control       D6H       -       -       -         KBPATN       Keypad Pattern       D5H       -       -       -         KBMASK       Keypad Pattern       D5H       -       -       -         KBMASK       Keypad Pattern       D5H       -       -       -         KBMASK       Keypad Mask       D7H       -       -       -         Serial Port       Saden       Slave Address Mask       B9H       -       -       -         SADEN       Slave Address       A9H       -       -       -       -       -         SICON*       TWSI Control Register       F8H       CR2       ENSI       STA       STO         SIADR       TWSI Address<br>Register       D1H       (Own Slave Address)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                             |                                                                                                                                                                                                         |                                                                                                                                                                                                                        |                                                                                                                                                              | 00H<br>FFH                                                         |