### **General Description**

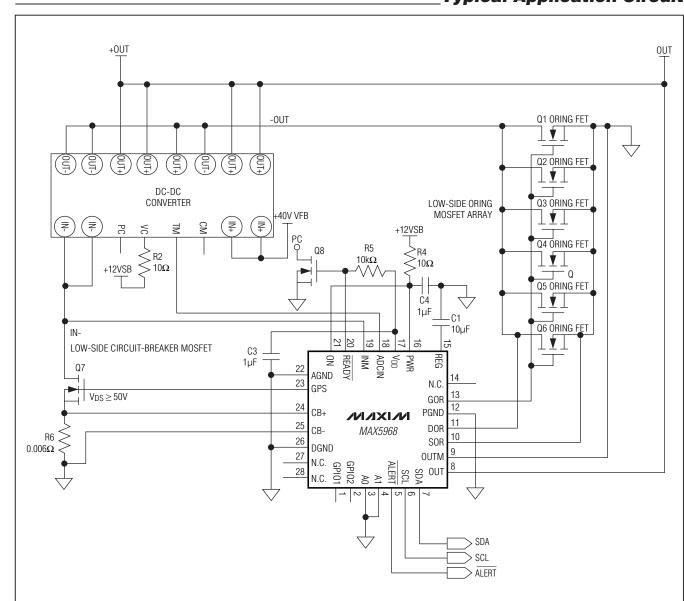

The MAX5968 soft-switch and ideal diode controller protects systems with redundant DC-DC converter modules against failure of the converter by controlling external n-channel MOSFETs at the input and output of the converter. Input short-circuit and overload current protection is provided by means of a current-sense amplifier connected to a sense resistor that resides at the source of the external protection MOSFET. If a failure occurs at the input of the associated converter, the MAX5968 protects the input supply by pulling the gate of the input protection MOSFET low and disconnecting the failed converter. Similarly, if there is a failure at the output of the redundant converter. the MAX5968 detects the reverse potential across the output MOSFET and pulls the gate low to disconnect the failed converter from the load. The MAX5968 features VariableSpeed/BiLevel<sup>™</sup> input circuit-breaker protection.

The MAX5968 also integrates a 10-bit ADC that monitors converter input current, load voltage, and output MOSFET forward voltage. An analog input (ADCIN) is provided to monitor a temperature signal from the associated converter. The MAX5968 features two 10-bit circular buffers that contain a history of the 50 most recent input current and output load voltage digital conversion results. This data helps to diagnose and troubleshoot converter failures. All ADC results, including circular buffers and several configuration registers are accessible through a 400kHz I<sup>2</sup>C interface.

Digital limits for overvoltage and undervoltage warning are user programmable. An ALERT output notifies the system controller of any failure condition that arises or requires attention. When any of the measured signals violates digitally programmable limits, the ALERT output is asserted.

A precision ON comparator input can be used to implement programmable undervoltage lockout for the input and output MOSFET drivers.

An open-drain READY output can be used to enable the associated DC-DC converter by releasing the converter's enable input when both the input and output MOSFETs are fully enhanced.

Two general-purpose I/Os can be fully configured through the I<sup>2</sup>C interface to provide external indications or to control additional peripheral devices.

The MAX5968 is available in a 28-pin thin QFN package and operates over the -40°C to +125°C temperature range.

### \_Features

- 10-Bit ADC for Temperature, Voltage, Output MOSFET Forward Voltage, and Input Current Monitoring

- Circular Buffers Store 50 Most Recent Voltage and Current Values for Fault Transient Analysis

- Input Circuit-Breaker Controller Drives External Low-Side n-Channel MOSFET

- Output Reverse-Current Protection Controller Drives Parallel External n-Channel MOSFETs

- Programmable VariableSpeed/BiLevel Fault Protection Provides Electronic Circuit-Breaker Function

- Internal 4A Pulldown Current for Fast Shutdown of the Circuit Breaker

- + Internal 600m $\Omega$  Gate Drive for Fast On-Off Control of the ORing FETs

- Minimum- and Maximum-Value Detection Registers for All Digitized Signals

- Two GPIO Pins

- ♦ 400kHz I<sup>2</sup>C Interface

- Small, 5mm x 5mm, 28-Pin TQFN Package

### Applications

Redundant DC-DC Converter Protection Servers High-Reliability Systems

### **Ordering Information**

| -           |                 |             |

|-------------|-----------------|-------------|

| PART        | TEMP RANGE      | PIN-PACKAGE |

| MAX5968ATI+ | -40°C to +125°C | 28 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

VariableSpeed/BiLevel is a trademark of Maxim Integrated Products, Inc.

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| ADCIN, INM to AGND           | 0.3V to +60V                     |

|------------------------------|----------------------------------|

| PWR to AGND                  |                                  |

| READY, ALERT to AGND         | 0.3V to (V <sub>DD</sub> + 0.3V) |

| VDD, REG, SCL, SDA to AGND   | -0.3V to +6V                     |

| GOR to AGND                  | 0.3V to (VREG + 0.3V)            |

| ON, GPS to AGND              | 0.3V to (VPWR + 0.3V)            |

| OUT, DOR, SOR, CB+, CB-, A1, | A0,                              |

| GPIO1, GPIO2 to AGND         | 0.3V to (V <sub>DD</sub> + 0.3V) |

| CB+ to CB                    | 1V to +1V                        |

| GPS to CB+0.3                | 3V to +8V (internally clamped)   |

| DOR to SOR                   | 0.3V to +3.3V                    |

| PGND, DGND, OUTM to AGND     | 0.3V to +0.3V                    |

SDA,  $\overline{\text{ALERT}}$ ,  $\overline{\text{READY}}$ ,  $\overline{\text{GPIO1}}$ ,  $\overline{\text{GPIO2}}$  Current ..-1mA to +100mA Input/Output Current (all other pins).....+20mA (Note 1) Continuous Power Dissipation (T<sub>A</sub> = +70°C)

| C)2758.6mW     |

|----------------|

| 29°C/W         |

| 2°C/W          |

| 10°C to +125°C |

| +150°C         |

| 65°C to +150°C |

| +300°C         |

| +260°C         |

|                |

**Note 1:** During GPS/GOR pulldown, GPS, GOR, REG, AGND, and PGND could carry 1.5A to 7A transient current for several microseconds.

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

(VPWR = 12V, TA = TJ = -40°C to +125°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 3)

| PARAMETER                                 | SYMBOL     | CONDITIONS                                                                       | MIN | TYP | MAX | UNITS |

|-------------------------------------------|------------|----------------------------------------------------------------------------------|-----|-----|-----|-------|

| Operating Voltage Range                   | VPWR       |                                                                                  | 9   |     | 14  | V     |

| Undervoltage Lockout                      | Vuvlo      | Minimum voltage on V <sub>PWR</sub> to ensure operation, V <sub>PWR</sub> rising | 7.9 | 8.4 | 8.9 | V     |

| Undervoltage Lockout<br>Hysteresis        | VUVLO_HYS  | VPWR falling                                                                     |     | 500 |     | mV    |

| Supply Current                            | IPWR       | fSCL = 400kHz                                                                    |     | 3.5 | 6   | mA    |

| REG Regulator Output Voltage              | VREG       | With 5mA load                                                                    | 4.5 | 4.8 | 5.0 | V     |

| REG Undervoltage Lockout                  | VREGUV     |                                                                                  |     | 3.5 |     | V     |

| REG Undervoltage Lockout<br>Hysteresis    | VREGUV_HYS |                                                                                  |     | 500 |     | mV    |

| V <sub>DD</sub> Regulator Output Voltage  | VDD        | With 5mA load                                                                    | 4.5 | 5   | 5.5 | V     |

| VDD Power-On Reset                        | VPOR       |                                                                                  |     | 3.5 |     | V     |

| V <sub>DD</sub> Power-On Reset Hysteresis | VPOR_HYS   |                                                                                  |     | 500 |     | mV    |

| Internal Oscillator Frequency             | fint       |                                                                                  | 3.6 | 4.0 | 4.4 | MHz   |

| ANALOG-TO-DIGITAL CONVER                  | TER        |                                                                                  |     |     |     |       |

| Resolution                                |            |                                                                                  |     | 10  |     | Bits  |

| Total Unadjusted Error                    |            |                                                                                  |     |     | 1   | %FS   |

| Integral Nonlinearity                     | INL        |                                                                                  |     | 1   |     | LSB   |

| Differential Nonlinearity                 | DNL        |                                                                                  |     | 1   |     | LSB   |

| Offset Error                              |            |                                                                                  | -5  |     | +5  | LSB   |

| DC Gain Error                             |            |                                                                                  | -7  |     | +7  | LSB   |

# **ELECTRICAL CHARACTERISTICS (continued)**

(VPWR = 12V, TA = TJ = -40°C to +125°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 3)

| PARAMETER                            | SYMBOL   | CONDITIONS                                                                           | MIN  | ΤΥΡ  | MAX  | UNITS |  |

|--------------------------------------|----------|--------------------------------------------------------------------------------------|------|------|------|-------|--|

| ADC Total Monitoring Cycle Time      |          |                                                                                      |      | 100  |      | μs    |  |

| ADCIN Input Full-Scale Voltage       |          | Conversion = 1023, LSB = 4.88mV                                                      |      | 5    |      | V     |  |

| ADCIN Measurement Accuracy           |          |                                                                                      | -7   |      | +7   | LSB   |  |

| ADCIN Input Resistance               |          | ADCIN to INM                                                                         | 300  | 500  | 700  | kΩ    |  |

|                                      |          | LV_range = 0, conversion = 1023,<br>LSB = 1.955mV                                    |      | 2    |      | V     |  |

| OUT Full-Scale Voltage               |          | LV_range = 1, conversion = 1023,<br>LSB = 3.910mV                                    |      | 4    |      | V     |  |

|                                      |          | Vout = 2.0V                                                                          | 10   | 25   | 40   |       |  |

| OUT Leakage Current                  | IOUT     | V <sub>OUT</sub> = 4.0V                                                              | 50   | 100  | 150  | μΑ    |  |

|                                      |          | V <sub>OUT</sub> = 4.0V, V <sub>OUTM</sub> = 0V                                      | -150 | -100 | -50  |       |  |

| OUTM Leakage Current                 | IOUTM    | V <sub>OUT</sub> = 2.0V, V <sub>OUTM</sub> = 0V                                      | -40  | -25  | -10  | μΑ    |  |

|                                      |          | LV_range = 0                                                                         | -7   |      | +7   |       |  |

| OUT Measurement Accuracy             |          | LV_range = 1                                                                         | -7   |      | +7   | LSB   |  |

|                                      |          | At code = 1023                                                                       |      | 40   |      | mV    |  |

| VCB+ - VCB- Full-Scale Voltage       |          | At code = 0                                                                          |      | -10  |      |       |  |

|                                      | ICB+     | $V_{CB+} = 40 \text{mV}, V_{CB-} = 0 \text{V}$                                       |      | 5    | 2    | ^     |  |

| Input Bias Current                   | ICB-     | $V_{CB+} = 40 \text{mV}, V_{CB-} = 0 \text{V}$                                       |      | 5    | 2    | μA    |  |

|                                      |          | $V_{CB+} = 0V, V_{CB-} = 0V, T_A = -40^{\circ}C \text{ to } +25^{\circ}C$            | -1.2 |      | +1.2 |       |  |

| Input Current Measurement            |          | $V_{CB+} = 0V, V_{CB-} = 0V, T_A = +25^{\circ}C \text{ to } +125^{\circ}C$           | -0.6 |      | +0.6 |       |  |

| Accuracy                             |          | $V_{CB-} = 0V, V_{CB+} = 5mV$                                                        | -1.2 |      | +1.2 | mV    |  |

|                                      |          | $V_{CB-} = 0V, V_{CB+} = 20mV$                                                       | -1.2 |      | +1.2 |       |  |

|                                      |          | At code = 1023                                                                       |      | -40  |      | mV    |  |

| VDOR - VSOR Range Voltage            |          | At code = 0                                                                          |      | 10   |      | IIIV  |  |

| VDOR - VSOR Measurement              |          | VSOR = 0V, VDOR = -20mV                                                              | -1.2 |      | +1.2 | mV    |  |

| Accuracy                             |          | $V_{SOR} = 0V, V_{DOR} = -5mV$                                                       | -1.2 |      | +1.2 | IIIV  |  |

| SOR Input Bias Current               | ISOR     | V <sub>SOR</sub> = 0mV, V <sub>DOR</sub> = -40mV                                     |      | 2    | 5    | μΑ    |  |

| DOR Input Bias Current               | IDOR     | $V_{SOR} = 0mV, V_{DOR} = -40mV$                                                     |      | 2    | 5    | μΑ    |  |

| INPUT CIRCUIT-BREAKER PRO            | TECTION  |                                                                                      |      |      |      |       |  |

| Fast Comparator Threshold Full Scale |          | Code = 255                                                                           |      | 40   |      | mV    |  |

| Circuit-Breaker Accuracy             |          | V <sub>CB-</sub> = 0V, code = 191 or 15mV (typ) input<br>referred, full scale = 200% | -2.7 |      | +2.7 | mV    |  |

| (Slow Comparator)                    | Vos,cb_s | V <sub>CB-</sub> = 0V, code = 102 or 8mV (typ) input<br>referred, full scale = 200%  | -2.7 |      | +2.7 | ſŤĬV  |  |

|                                      |          |                                                                                      |      |      |      |       |  |

**ELECTRICAL CHARACTERISTICS (continued)** (VPWR = 12V, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 3)

|                                                       |                                        |                                                                                      |       | ,     |       |       |

|-------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Circuit-Breaker Accuracy                              |                                        | V <sub>CB-</sub> = 0V, code = 191 or 30mV (typ) input<br>referred, full scale = 200% | -1.5  |       | +1.5  | mV    |

| (Fast Comparator)                                     | VOS,CB_F                               | V <sub>CB-</sub> = 0V, code = 102 or 16mV (typ) input<br>referred, full scale = 200% |       |       | +1.0  |       |

| PARAMETER                                             | SYMBOL                                 | CONDITIONS                                                                           | MIN   | TYP   | MAX   | UNITS |

| Fast Comparator Threshold<br>Programming Resolution   |                                        | DAC resolution                                                                       |       | 8     |       | Bits  |

| Slow Circuit-Breaker Response                         | toop                                   | $V_{CB+} - V_{CB-} = V_{TH,SC} + 2mV$                                                |       | 2.4   |       |       |

| Time                                                  | tSCD                                   | $V_{CB+} - V_{CB-} = V_{TH,SC} + 4mV$                                                |       | 1.2   |       | ms    |

| Fast Circuit-Breaker Response<br>Time                 | tFCD                                   | V <sub>CB+</sub> - V <sub>CB-</sub> = V <sub>TH,FC</sub> + 10mV                      |       | 0.1   |       | μs    |

| OUTPUT REVERSE-CURRENT F                              | ROTECTION                              |                                                                                      |       |       |       |       |

| Reverse-Current Detection<br>Threshold                | VRCD                                   | V <sub>DOR</sub> relative to V <sub>SOR</sub> (when GOR turns off)                   | 2.9   | 4     | 4.9   | mV    |

| Forward-Current Detection<br>Threshold                | VFCD                                   | $V_{\mbox{DOR}}$ relative to $V_{\mbox{SOR}}$ (when GOR turns on)                    | 1     | 2     | 3.5   | mV    |

| GOR Off Threshold Hysteresis                          | VHCD                                   |                                                                                      |       | 2     |       | mV    |

| Reverse-Current Blocking                              | trcd                                   | VDOR - VSOR = VRCD + 1mV, CGOR = 10nF                                                |       | 2     |       | μs    |

| Response Time                                         | VDOR - VSOR = VRCD + 10mV, CGOR = 10nF |                                                                                      |       | 100   |       | ns    |

| OUTPUT UNDERVOLTAGE FAS                               | T COMPARA                              |                                                                                      | 1     |       |       |       |

| OUT UV Comparator Threshold                           | Vthuvdac                               | LV_range = 0, code = 127                                                             | 0.79  | 0.8   | 0.81  | v     |

|                                                       |                                        | LV_range = 1, code = 127                                                             | 1.58  | 1.6   | 1.62  |       |

| OUT UV Comparator Threshold<br>Programming Resolution |                                        | DAC resolution 8                                                                     |       |       | Bits  |       |

| OUT UV Comparator<br>Propagation Delay                | tout                                   | With 10mV overdrive                                                                  | 100   |       | ns    |       |

| ON COMPARATOR INPUT (ON)                              |                                        |                                                                                      |       |       |       |       |

| ON Input Threshold                                    | VTHON                                  | Rising                                                                               | 1.209 | 1.228 | 1.246 | V     |

| ON Input Hysteresis                                   |                                        | Falling                                                                              |       | 62.5  |       | mV    |

| ON Input Current                                      | ION                                    |                                                                                      | -1    |       | +1    | μA    |

| INPUT MOSFET GATE DRIVE (G                            | iPS)                                   | 1                                                                                    | 1     |       |       | 1     |

| GPS High Voltage                                      | VGPSH                                  | Relative to AGND                                                                     | 6.5   | 8     | 9.6   | V     |

| GPS High Comparator Threshold                         | VTHGPS                                 | V <sub>GPS</sub> - V <sub>CB+</sub>                                                  | 4.9   | 5     | 5.1   | V     |

| GPS Pullup Current                                    | IGPSUP                                 | VGPS is 1V below VGPSH                                                               | 45    | 50    | 55    | μA    |

| GPS Pulldown Current                                  | IGPSDN                                 | V <sub>GPS</sub> = 2V                                                                |       | 1.5   |       | A     |

| GPS Pulldown Resistance                               | RDGPS                                  |                                                                                      |       |       | 2.5   | Ω     |

| OUTPUT MOSFET GATE DRIVE                              | (GOR)                                  | 1                                                                                    |       |       |       |       |

| GOR High Voltage                                      | VGORH                                  | Relative to AGND                                                                     | 4.5   | 4.8   | 5.0   | V     |

| GOR High Comparator<br>Threshold                      | Vthgor                                 | Vgor - Vsor                                                                          | 2.9   | 3.0   | 3.1   | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(VPWR = 12V, TA = TJ = -40°C to +125°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 3)

| GOR Pullup Resistance                          | RUGOR            |                                                |     |     | 5   | Ω     |

|------------------------------------------------|------------------|------------------------------------------------|-----|-----|-----|-------|

| GOR Pulldown Resistance                        | RDGOR            |                                                |     |     | 2.5 | Ω     |

| GOR Pullup Current                             | IGORUP           | V <sub>GOR</sub> is 1V below V <sub>GORH</sub> |     | 2.5 |     | А     |

| GOR Pulldown Current                           | IGORDN           | VGOR = 2V                                      |     | 7   |     | А     |

| PARAMETER                                      | SYMBOL           | CONDITIONS                                     | MIN | TYP | MAX | UNITS |

| OUTPUTS (ALERT, READY, GR                      | PIO_)            |                                                |     |     |     |       |

| ALERT Voltage Low                              |                  | I <sub>SINK</sub> = 5mA                        |     |     | 0.4 | V     |

| ALERT Output Leakage (Open Drain)              |                  | VALERT = VDD                                   | -1  |     | +1  | μA    |

| READY Voltage Low                              |                  | ISINK = 5mA                                    |     |     | 0.4 | V     |

| READY Output Leakage<br>(Open Drain)           |                  | VREADY = VDD                                   | -1  |     | +1  | μA    |

| GPIO_ Input Logic-High<br>Threshold            |                  |                                                |     |     | 1.4 | V     |

| GPIO_ Input Logic-Low<br>Threshold             |                  |                                                | 0.4 |     |     | V     |

| GPIO_ Voltage Low                              |                  | ISINK = 5mA                                    |     |     | 0.4 | V     |

| GPIO_ Weak Pullup Current                      | Iwkpu            | $V_{GPIO} = 2V$                                | -5  | -10 | -20 | μA    |

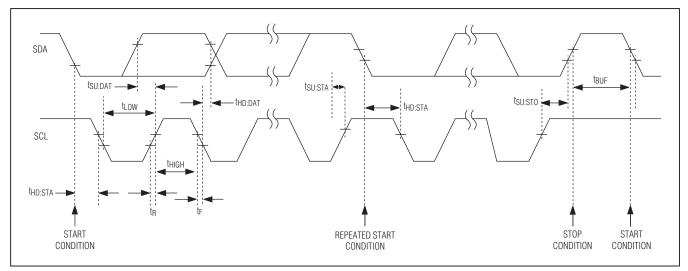

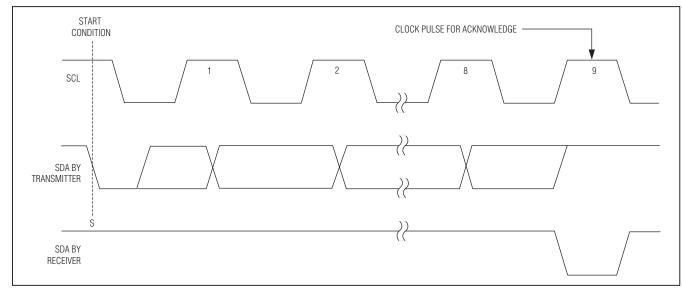

| I <sup>2</sup> C INTERFACE (SCL, SDA, A0       | , A1) (Figure 3  | 3)                                             |     |     |     |       |

| Serial-Clock Frequency                         | fSCL             |                                                |     |     | 400 | kHz   |

| Bus Free Time Between STOP and START Condition | <sup>t</sup> BUF |                                                | 1.3 |     |     | μs    |

| START Condition Setup Time                     | tsu:sta          |                                                | 0.6 |     |     | μs    |

| START Condition Hold Time                      | thd:sta          |                                                | 0.6 |     |     | μs    |

| STOP Condition Setup Time                      | tsu:sto          |                                                | 0.6 |     |     | μs    |

| Clock Low Period                               | tLOW             |                                                | 1.3 |     |     | μs    |

| Clock High Period                              | thigh            |                                                | 0.6 |     |     | μs    |

| Data Setup Time                                | tsu:dat          |                                                | 100 |     |     | ns    |

| Data Hold Time                                 | thd:dat          |                                                | 0   |     |     | ns    |

| Pulse Width of Spike<br>Suppressed             | tSP              |                                                | 50  |     |     | ns    |

| SDA, SCL Input Current                         |                  | SDA is not in pulldown, VSCL = VSDA = 5.5V     | -1  |     | +1  | μA    |

| SDA, SCL Logic-Low                             |                  |                                                |     |     | 0.8 | V     |

| SDA, SCL Logic-High                            |                  |                                                | 1.6 |     |     | V     |

| SDA, SCL Input Capacitance                     |                  |                                                |     | 15  |     | pF    |

| SDA Voltage Low                                |                  | ISINK = 5mA                                    |     |     | 0.4 | V     |

| A0, A1 Low Voltage                             |                  |                                                |     |     | 0.4 | V     |

| A0, A1 High Voltage                            |                  |                                                | 1.4 |     |     | V     |

| A0, A1 Input Current                           |                  | $V_{A0} = V_{A1} = V_{DD}$                     | -1  |     | +1  | μA    |

**Note 3:** All devices 100% production tested at  $T_A = +25^{\circ}C$  and  $T_A = +125^{\circ}C$ . Limits at  $T_A = -40^{\circ}C$  are guaranteed by design.

**MAX5968**

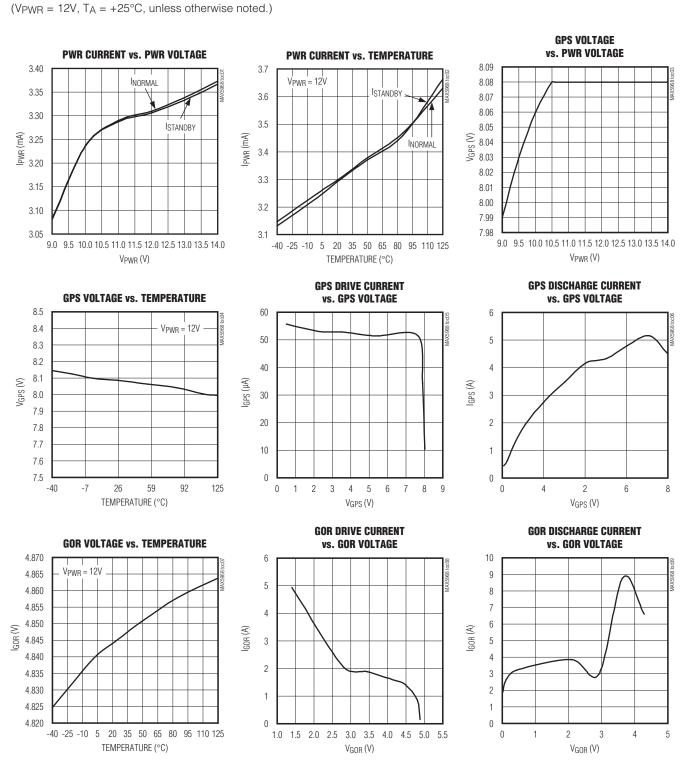

**Typical Operating Characteristics**

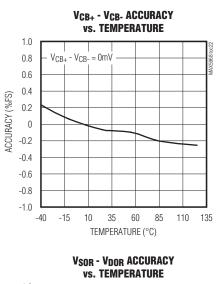

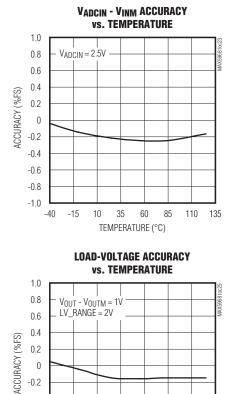

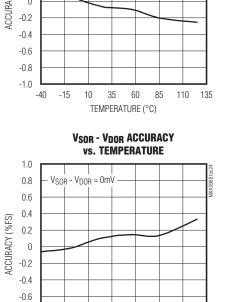

# **Typical Operating Characteristics (continued)**

$(V_{PWB} = 12V, T_A = +25^{\circ}C, unless otherwise noted.)$ **SLOW COMPARATOR THRESHOLD ON INPUT THRESHOLD VOLTAGE** vs. TEMPERATURE **VOLTAGE ERROR vs. TEMPERATURE** SLOW COMPARATOR THRESHOLD VOLTAGE ERROR (%) 10 1.240 VON RISING () 1.230 1.220 1.210 1.210 1.210 1.210 1.200 1.190 1.180 1.170 8 6 20mV THRESHOLD 4 VON FALLING 2 1.170 32mV THRESHOLD 0 1.160 -40 -25 -10 5 20 35 50 65 80 95 110 125 -40 -25 -10 5 20 35 50 65 80 95 110 125 TEMPERATURE (°C) TEMPERATURE (°C) **OUT FAST COMPARATOR THRESHOLD OUT FAST COMPARATOR THRESHOLD** vs. TEMPERATURE vs. LV DAC CODE 1.800 3.3 LV DAC = 127 LV\_RANGE = OUT FAST COMPARATOR THRESHOLD (V) OUT FAST COMPARATOR THRESHOLD (V) 1.600 LV RANGE = 1 1.400 2.2 1.200 1.000 1.1 LV\_RANGE = 0 0.800 0.600 0 -40 -25 -10 5 20 35 50 65 80 95 110 125 0 50 150 250 100 200 TEMPERATURE (°C) LV\_DAC CODE **STARTUP WAVEFORM STARTUP WAVEFORM** (ON FROM LOW TO HIGH) (PWR FROM OV TO 16V)  $\begin{array}{l} CH1 = V_{GPS} \\ CH2 = V_{GOR} \end{array}$ CH1 = VGPS CH2 = VGOR CH3 = VREADY CH3 = VREADY CH4 = VALERTCH4 = VALERT5V/div 5V/div 5V/div 5V/div 20ms/div 1ms/div

**MAX5968**

**Typical Operating Characteristics (continued)**

#### (VPWR = 12V, $T_A = +25^{\circ}C$ , unless otherwise noted.) **TURN-OFF WAVFORM TURN-OFF WAVFORM** (SLOW COMPARATOR FAULT) (FAST COMPARATOR FAULT) CH1 = VGPS CH1 = VGPS íí CH2 = VGORCH3 = VREADYCH2 = VGOR CH3 = VREADY $CH4 = V_{ALERT}$ CH4 = VALERT5V/div 5V/div 5V/div 5V/div 5V/div 5V/div 5V/div 5V/div 1ms/div 1ms/div **ORING FET OFF WAVEFORM CURRENT BUFFER vs. TIME** 5 Ö CH1 = VGPS CIRCULAR BUFFER CH2 = VGOR CONTENT AT SLOW 4 $CH3 = V_{READY}$ TRIP FAULT $CH4 = V_{ALERT}$ 5V/div CURRENT BUFFER (A) 3 5V/div 2 1 5V/div 0 5V/div -1 1ms/div -250-200-150-100-50 0 50 100 150 200 250 TIME (µs) **REVERSE LOAD-VOLTAGE BUFFER** LOAD-VOLTAGE BUFFER vs. TIME vs. TIME 1.4 1.4 CIRCULAR BUFFER 1.2 CONTENT AT SLOW 1.2 TRIP FAULT -OAD-VOLTAGE BUFFER (V) -OAD-VOLTAGE BUFFER (V) 1.0 1.0 0.8 0.8 0.6 0.6 0.4 0.4 0.2 0.2 0 0 -250 -200 -150 -100 -50 0 50 100 150 200 250 -250-200-150-100-50 0 50 100 150 200 250 TIME (µs) TIME (µs)

# **Typical Operating Characteristics (continued)**

$(V_{PWB} = 12V, T_A = +25^{\circ}C, unless otherwise noted.)$

-0.8

-1.0

-40 -15 10

0

-0.2 -0.4

-0.6

-0.8

-1.0

-40 -15 10 35 60 85 110 135

TEMPERATURE (°C)

35

60 85 110 135

TEMPERATURE (°C)

#### **Pin Configuration** ON READY TOP VIEW INM ADCIN V<sub>DD</sub> PWR REG 21 20 19 18 17 16 15 14 N.C AGND 22 13 GOR GPS 23 12 PGND CB+ 24 M/XI/M 11 DOR CB-25 MAX5968 DGND SOR 26 10 OUTM N.C 27 9 \*EP 8 OUT N.C 28 2 3 4 5 6 7 11 GPI01 GPI02 AO A1 ALERT SCL SDA TQFN \*CONNECT EXPOSED PAD TO GROUND.

### **\_Pin Description**

| PIN        | NAME            | FUNCTION                                                                                                                                                                    |  |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | GPIO1           | General-Purpose Input/Output 1. Configured by internal registers.                                                                                                           |  |

| 2          | GPIO2           | General-Purpose Input/Output 2. Configured by internal registers.                                                                                                           |  |

| 3          | A0              | I <sup>2</sup> C Address Selection Input 1                                                                                                                                  |  |

| 4          | A1              | I <sup>2</sup> C Address Selection Input 2                                                                                                                                  |  |

| 5          | ALERT           | Active-Low Fault Status Open-Drain Output. Driven low if a failure condition is detected.                                                                                   |  |

| 6          | SCL             | I <sup>2</sup> C Clock Input                                                                                                                                                |  |

| 7          | SDA             | I <sup>2</sup> C Serial-Data Input/Output                                                                                                                                   |  |

| 8          | OUT             | Load-Voltage ADC Monitor Positive Input                                                                                                                                     |  |

| 9          | OUTM            | Load-Voltage ADC Monitor Negative Input. Connect to the load ground.                                                                                                        |  |

| 10         | SOR             | Reverse-Current Protection External MOSFET Source Connection. Connect to the source of the output reverse-current protection n-channel MOSFETs and the load ground.         |  |

| 11         | DOR             | Reverse-Current Protection External MOSFET Drain Connection. Connect to the drain of the reverse-current protection n-channel MOSFETs and to the converter negative output. |  |

| 12         | PGND            | Power Ground                                                                                                                                                                |  |

| 13         | GOR             | Reverse-Current Protection External MOSFET Gate-Drive Output. Connect to gate of the reverse-<br>current protection n-channel MOSFETs.                                      |  |

| 14, 27, 28 | N.C.            | No Connection. Not internally connected.                                                                                                                                    |  |

| 15         | REG             | Internal Regulator Output External Bypass Capacitor Connection. Bypass to ground with a 10µF ceramic capacitor.                                                             |  |

| 16         | PWR             | Device Power Input                                                                                                                                                          |  |

| 17         | V <sub>DD</sub> | Digital Supply. Bypass VDD to DGND with a 1 $\mu$ F capacitor.                                                                                                              |  |

| 18         | ADCIN           | Converter Temperature and Fault Monitoring Input. Connect to converter temperature output nal. This input is multiplexed to the internal ADC for temperature monitoring.    |  |

# Pin Description (continued)

| PIN | NAME  | FUNCTION                                                                                                                                                   |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19  | INM   | ADCIN Differential Amplifier Reference Input. Connect to the drain of the input protection low-side MOSFET to remove ground bias from the signal at ADCIN. |

| 20  | READY | Active-Low Converter Enable Open-Drain Output. READY goes low when both GPS and GOR output voltages are high (or enhanced).                                |

| 21  | ON    | Enable Input. Precision enable input to adjust undervoltage lockout. Connect to PWR for enabled operation.                                                 |

| 22  | AGND  | Analog Ground                                                                                                                                              |

| 23  | GPS   | Converter Input Power MOSFET Gate Drive. Connect to the gate of the external n-channel low-side power MOSFET.                                              |

| 24  | CB+   | Converter Input Current-Sense Amplifier Positive Input                                                                                                     |

| 25  | CB-   | Converter Input Current-Sense Amplifier Negative Input                                                                                                     |

| 26  | DGND  | Digital Ground                                                                                                                                             |

|     | EP    | Exposed Pad. Connect to the ground plane.                                                                                                                  |

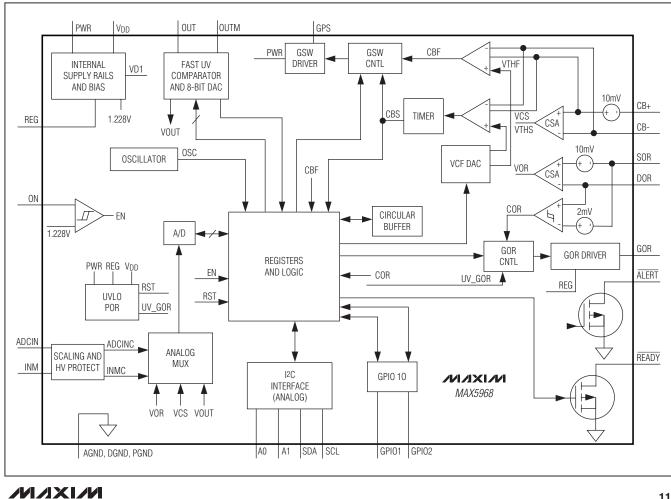

# **Functional Diagram**

**MAX5968**

**MAX5968**

### **Detailed Description**

The MAX5968 is a soft-switch and ideal diode controller that protects systems with redundant DC-DC converter modules by isolating failed modules from the common input and output power. During normal operation, both the input and output MOSFET switches are fully enhanced. The gate of the high-voltage MOSFET at GPS is driven to +8V (typ) to ensure low on-resistance and high-efficiency operation. The gate of the reverse-current blocking MOSFET at GOR is driven to 4.8V (typ) for fast on-off response, low on-resistance, and to stay within the gate-to-source voltage rating of the low-voltage MOSFETs used in this application.

The MAX5968 provides input protection by means of a current-sense amplifier connected to a sense resistor that resides at the source of the input protection MOSFET. The current-sense signal is supplied to two precision analog comparators to implement circuit-breaker protection. One comparator has a lower threshold and a slow response time, while the other comparator has a higher threshold and a fast response. This provides good rejection of noise and brief load-current transients, while still protecting the system against slow-onset and short-circuit failures. If either the slow-comparator or fastcomparator threshold is exceeded for sufficient duration, the gate of the input protection MOSFET is pulled low with 1.5A peak current and latched off, disconnecting the converter input from the power supply bus. The fasttrip threshold is programmed through the I<sup>2</sup>C interface to a value from 0 to 40mV with an 8-bit DAC, and the slowtrip threshold can be set to 50%, 57%, 67%, or 80% of the fast-trip threshold.

Converter output protection consists of a precision amplifier and comparator circuit that compares the voltage between the source and drain of an external MOSFET. If the drain rises above the source by 2mV (typ), a reverse-current condition is detected and the gate of the MOSFET immediately pulls low with 7A peak current, blocking the flow of current from the output bus back into the failed converter. As soon as the drain falls to within 1mV (typ) of source potential, the gate of the MOSFET pulls high again with 2.5A peak current to allow forward current flow. This fast, unlatched driver allows the converter module to quickly return to normal operation after a reverse-current transient.

A 10-bit ADC is multiplexed to monitor the DC-DC converter input current, the voltage at an auxiliary input, the output MOSFET forward voltage drop, and the load voltage. All ADC results, including circular buffers and the

configuration registers, are accessible through a 400kHz I<sup>2</sup>C interface. The auxiliary ADC input can be connected to a 0 to 5V signal from the converter, typically a combined temperature and fault signal.

Two 10-bit circular buffers that contain a history of the 50 most recent input switching current and output load-voltage digital conversion results help diagnose DC-DC converter faults.

A precision on-comparator input can be used to enable or disable the input and output MOSFET drivers by connecting to an external voltage signal, allowing ON to be used as a programmable undervoltage threshold.

All inputs are equipped with programmable warning comparators. If an input signal falls outside its digital thresholds, a warning condition is registered, and the ALERT output can be programmed to assert for any or all of these conditions. All monitored signals are equipped with resettable peak-detection registers that store the minimum and maximum values measured since they were last cleared. This peak-detection system reduces or eliminates the need for continuous polling of conversion results. A fast analog comparator continuously monitors OUT voltage and latches the UV\_warn register that asserts ALERT.

An open-drain  $\overline{\text{READY}}$  output can be used to enable the associated DC-DC converter by driving the converter enable input when the input and output MOSFET drivers are fully enhanced, or it can be programmed through the l<sup>2</sup>C interface to arbitrarily disable the converter at any time.

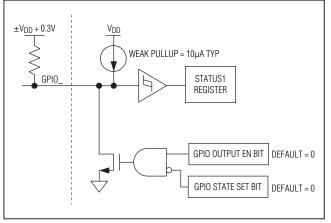

Two general-purpose I/Os can be fully configured through the I<sup>2</sup>C interface to provide external indications or to control additional peripheral devices. These outputs have sufficient sink-current capability to drive LED indicators. These pins have internal 10 $\mu$ A pullups and sufficient sink-current capability to directly drive LED indicators.

#### **SOR/DOR Comparator**

The SOR/DOR comparator monitors the VDS voltage of the external low-side ORing FET. When VDOR - VSOR exceeds the trip point (+4mV), this comparator trips and commands the ORing FET gate driver to pull GOR to ground, turning off the FET and blocking reverse current. When VDOR - VSOR falls below +2mV, the GOR driver immediately drives GOR high again.

During normal operation, transient conditions cause temporary reversal of potential across the ORing FET. The MAX5968 ORing function is intended to block any

reverse current that could occur in this condition, while quickly returning the FET to the on state, immediately after the reverse potential condition is gone. There is a user-selectable timeout period for reverse-current blocking notification. If the GOR output remains low for longer than this timer period, a fault status indicator flag is set in bit 2 of register 0x27. This feature is intended to alert the system to a persistent reverse potential at the ORing FET that is indicative of a failure at the output of the associated converter module. The time delay can be programmed to 192µs, 128µs, 64µs, or 32µs by writing to the two bits of register 0x39. The default timer value is 192µs.

#### **SOR/DOR Voltage Amplifier**

The MAX5968 measures the ORing MOSFET forward voltage ( $V_{SOR} - V_{DOR}$ ) and sends this value to the ADC for conversion and communication through the I<sup>2</sup>C bus. The total ADC conversion range is 50mV: full-scale input voltage is -40mV, and there is an offset added to the signal to allow ADC measurement of reverse potential as high as 10mV.

#### **GOR Gate Driver**

The GOR gate driver includes a  $5\Omega$  MOSFET driver that pulls up to +4.8V (typ) and pulls down to ground to allow forward current and block reverse current, respectively. The GOR driver is capable of 2.5A peak pullup and 7A peak pulldown currents. A coarse 3V comparator is used to indicate FET full enhancement and sets a GOR gatedrive good flag in register 0x29.

#### **ON Comparator**

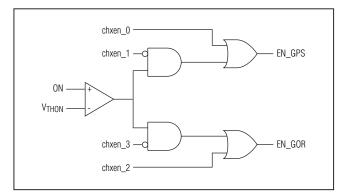

The ON input enables and disables the MAX5968 GPS and GOR outputs. A comparator compares the ON voltage against the internal bandgap voltage with 62.5mV hysteresis. Upon system fault, the input FET pulls low and is latched off. In this situation, the user can toggle the ON input to reset the fault latch and reenable the FETs. In addition, the ON enabling/disabling functionality can be masked or overridden by the chxen register bits. See Figure 2.

#### **PWR UVLO and VDD Power-On Reset**

If the voltage at PWR is below 8.9V or V<sub>DD</sub> voltage is below +3.5V (typ), the MAX5968 enters power-on reset and all the registers are restored to their default states. For normal operation, the PWR input must be greater than or equal to +9V and V<sub>DD</sub> must be greater than or equal to +4.5V. A flag is set in register 0x27 whenever the MAX5968 exits the reset state to indicate that all registers are in their default states.

#### **CB+/CB- Current-Sense Amplifier**

The CB+/CB- current-sense amplifier feeds the differential voltage across a current-sense resistor to the internal ADC. The total conversion range is 50mV: the full-scale input voltage is 40mV, and there is an input offset added to allow measurement of reverse current as high as -10mV.

#### **GPS Fast Comparator**

The fast circuit-breaker comparator compares the output of the CB+/CB- current-sense amplifier to the threshold voltage generated by the 8-bit fast circuit-breaker threshold DAC. The DAC voltage is set by writing to register 0x25. This fast comparator commands a quick turn off of the GPS output as soon as its threshold is exceeded, and the fast-trip shutdown flag is set in register 0x27.

#### **GPS Slow Comparator**

The slow circuit-breaker comparator compares the output of the CB+/CB- current-sense amplifier to a threshold voltage generated by the combination of the fast circuitbreaker threshold DAC and the fast-to-slow threshold ratio setting in register 0x26; see Table 1. When the slow circuit-breaker threshold is exceeded, it starts an analog timer designed so that the timer duration is proportional to comparator overdrive voltage. When the timer expires, the GPS output is driven low and the slow-trip shutdown flag is set in register 0x27.

### Table 1. Fast and Slow Circuit-Breaker Comparator Threshold Ranges

| FAST-TRIP COMPARATOR<br>8-BIT DAC RANGE<br>(REGISTER 0x25) (mV) | F2S_RATIO[1:0]<br>(REGISTER 0x26) | FAST-TRIP TO SLOW-<br>TRIP RATIO (%) | VALID SLOW-TRIP<br>THRESHOLD RANGE<br>(mV) | SPECIFIED SLOW-TRIP<br>THRESHOLD RANGE<br>(mV) |

|-----------------------------------------------------------------|-----------------------------------|--------------------------------------|--------------------------------------------|------------------------------------------------|

|                                                                 | 00                                | 125                                  | 0 to 32                                    | 12.8 to 32                                     |

| 0 to 40                                                         | 01                                | 150                                  | 0 to 26.67                                 | 10.67 to 26.67                                 |

| 0 to 40                                                         | 10                                | 175                                  | 0 to 22.86                                 | 9.14 to 22.86                                  |

|                                                                 | 11                                | 200                                  | 0 to 20                                    | 8 to 20                                        |

Figure 1. GPIO Driver

#### **GPS Gate Driver**

The GPS output is designed to drive the gate of a lowside external n-channel MOSFET. When commanded high, GPS is pulled up to an internal 8V rail with a 50µA current source. A 5V comparator is used to indicate full enhancement and set a gate-drive good flag in register 0x29. Upon turn-off, GPS is driven to ground with peak current of 1.5A.

#### OUT Undervoltage Fast Comparator and ADC Full-Scale Range

The output load voltage is monitored by the ADC. The load voltage is measured differentially between OUT and OUTM. The full-scale conversion voltage is set to either 2V or 4V by writing to the 1-bit register at address 0x18. See Table 2.

The load-voltage monitoring amplifier is also connected to a precision fast comparator. The reference for this comparator is generated by an 8-bit DAC, programmed by register 0x24. This sets an undervoltage value from 0 to 1.6V for the 2V OUT range, or 3.2V for the 4V OUT range as shown in Table 2. If VOUT - VOUTM falls below the programmed comparator threshold, the UV warning register bit asserts in register 0x2A. This feature detects load-voltage glitches during fault-protection events that can occur when one of several redundant converters is disabled, causing the load to shift to the other converters. This analog comparator allows detection of fast glitches that are asynchronous to the ADC sample cycle.

### GPIO1, GPIO2

Two general-purpose open-drain I/Os can be independently configured by output-enable register 0x37 and output-state register 0x38. The actual voltage state of these I/Os can be read through status register 0x28, regardless of whether they are configured as inputs or outputs. Upon power-on reset, both GPIOs are configured as inputs with 10µA weak pullups. When configured as outputs, both GPIOs have sufficient pulldown strength to directly drive LED indicators (Figure 1).

### ALERT Output

ALERT is an active-low, open-drain output. The ALERT output defaults to only indicate a failure condition that includes either a circuit-breaker or reverse-current shutdown. A bit can be cleared to unmask the digital and analog warning (UV, OV, or OC) comparator inputs, allowing these conditions to also assert the ALERT output, if desired. ALERT has sufficient pulldown strength to directly drive an LED indicator.

### **READY** Output

An open-drain READY pin goes low after the input and output protection MOSFETs are fully enhanced, and remains low until a circuit-breaker fault occurs or until READY is set high impedance by writing to a register. READY can be used to provide an active-high enable signal to the associated converter by driving an external n-channel transistor, thus allowing high-voltage operation. READY has sufficient pulldown strength to directly drive an LED indicator.

### Table 2. OUT Undervoltage Fast Comparator

| LV_RANGE[0] VALUE | LOAD-VOLTAGE ADC CONVERSION RANGE<br>(OUT RANGE) (V) | LOAD-VOLTAGE FAST UNDERVOLTAGE<br>COMPARATOR DAC RANGE (V) |

|-------------------|------------------------------------------------------|------------------------------------------------------------|

| 0                 | $0 \le V_{OUT} \le 2.0$                              | $0 \le V_{THUVDAC} \le 1.6$                                |

| 1                 | $0 \le V_{OUT} \le 4.0$                              | $0 \le VTHUVDAC \le 3.2$                                   |

### **Register Map**

If a register is less than 8 bits wide and writable, the nonexistent bits are ignored during a write operation. During a read operation they are read back as 0. Because the I<sup>2</sup>C protocol uses 8-bit data, the master must write 2 bytes to sequential registers to program the 10-bit settings of the MAX5968. To read 10-bit data, the master should perform a 2-byte burst read, starting on the MSB byte address. See Table 3 for the register address map.

### Table 3. Register Address Map

| NAME          | ADDR | ACCESS | BIT<br>RANGE | RESET<br>VALUE | DESCRIPTION                                                        |

|---------------|------|--------|--------------|----------------|--------------------------------------------------------------------|

| CS_MSB        | 0x00 | R      | [7:0]        | 0x00           | Latest ADC results of CB- amplifier output, bits [9:2]             |

| CS_LSB        | 0x01 | R      | [1:0]        | 0x00           | Latest ADC results of CB- amplifier output, bits [1:0]             |

| ADCIN_MSB     | 0x02 | R      | [7:0]        | 0x00           | Latest ADC results of ADCIN, bits [9:2]                            |

| ADCIN_LSB     | 0x03 | R      | [1:0]        | 0x00           | Latest ADC results of ADCIN, bits [1:0]                            |

| ORFET_MSB     | 0x04 | R      | [7:0]        | 0x00           | Latest ADC results of output-MOSFET forward voltage, bits [9:2]    |

| ORFET_LSB     | 0x05 | R      | [1:0]        | 0x00           | Latest ADC results of output-MOSFET forward voltage, bits [1:0]    |

| LV_MSB        | 0x06 | R      | [7:0]        | 0x00           | Latest ADC results of load voltage, bits [9:2]                     |

| LV_LSB        | 0x07 | R      | [1:0]        | 0x00           | Latest ADC results of load voltage, bits [1:0]                     |

| min_CS_MSB    | 0x08 | R      | [7:0]        | 0xFF           | Minimum value of CS amplifier output, bits [9:2]                   |

| min_CS_LSB    | 0x09 | R      | [1:0]        | 0x03           | Minimum value of CS amplifier output, bits [1:0]                   |

| max_CS_MSB    | 0x0A | R      | [7:0]        | 0x00           | Maximum value of CS amplifier output, bits [9:2]                   |

| max_CS_LSB    | 0x0B | R      | [1:0]        | 0x00           | Maximum value of CS amplifier output, bits [1:0]                   |

| min_ADCIN_MSB | 0x0C | R      | [7:0]        | 0xFF           | Minimum value of ADCIN, bits [9:2]                                 |

| min_ADCIN_LSB | 0x0D | R      | [1:0]        | 0x03           | Minimum value of ADCIN, bits [1:0]                                 |

| max_ADCIN_MSB | 0x0E | R      | [7:0]        | 0x00           | Maximum value of ADCIN, bits [9:2]                                 |

| max_ADCIN_LSB | 0x0F | R      | [1:0]        | 0x00           | Maximum value of ADCIN, bits [1:0]                                 |

| min_ORFET_MSB | 0x10 | R      | [7:0]        | 0xFF           | Minimum value of output-MOSFET forward voltage, bits [9:2]         |

| min_ORFET_LSB | 0x11 | R      | [1:0]        | 0x03           | Minimum value of output-MOSFET forward voltage, bits [1:0]         |

| max_ORFET_MSB | 0x12 | R      | [7:0]        | 0x00           | Maximum value of output-MOSFET forward voltage, bits [9:2]         |

| max_ORFET_LSB | 0x13 | R      | [1:0]        | 0x00           | Maximum value of output-MOSFET forward voltage, bits [1:0]         |

| min_LV_MSB    | 0x14 | R      | [7:0]        | 0xFF           | Minimum value of load voltage, bits [9:2]                          |

| min_LV_LSB    | 0x15 | R      | [1:0]        | 0x03           | Minimum value of load voltage, bits [1:0]                          |

| max_LV_MSB    | 0x16 | R      | [7:0]        | 0x00           | Maximum value of load voltage, bits [9:2]                          |

| max_LV_LSB    | 0x17 | R      | [1:0]        | 0x00           | Maximum value of load voltage, bits [1:0]                          |

| LV_range      | 0x18 | R/W    | [0]          | 0x00           | Load voltage ADC input range setting: 0 = 2V, 1 = 4V               |

| buf_enable    | 0x19 | R/W    | [2:0]        | 0x05           | Selective enabling of circular buffer blocks                       |

|               |      |        | [0]          | 1              | Current-sense buffer enable bit                                    |

|               |      |        | [1]          | 1              | Load-voltage buffer enable bit                                     |

|               |      |        | [2]          | 1              | Load-voltage buffer stop upon persistent reverse-current fault     |

| ocw_CS_MSB    | 0x1A | R/W    | [7:0]        | 0xFF           | Digital warning threshold value for overcurrent, bits [9:2]        |

| ocw_CS_LSB    | 0x1B | R/W    | [1:0]        | 0x03           | Digital warning threshold value for overcurrent, bits [1:0]        |

| uvw_ADCIN_MSB | 0x1C | R.W    | [7:0]        | 0x00           | Digital warning undervoltage threshold value for ADCIN, bits [9:2] |

### Table 3. Register Address Map (continued)

| NAME          | ADDR | ACCESS | BIT<br>RANGE | RESET<br>VALUE | DESCRIPTION                                                                                                                                                               |

|---------------|------|--------|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uvw_ADCIN_LSB | 0x1D | R/W    | [1:0]        | 0x00           | Digital warning undervoltage threshold value for ADCIN, bits [1:0]                                                                                                        |

| ovw_ADCIN_MSB | 0x1E | R/W    | [7:0]        | 0xFF           | Digital warning overvoltage threshold value for ADCIN, bits [9:2]                                                                                                         |

| ovw_ADCIN_LSB | 0x1F | R/W    | [1:0]        | 0x03           | Digital warning overvoltage threshold value for ADCIN, bits [1:0]                                                                                                         |

| ovw_ORFET_MSB | 0x20 | R/W    | [7:0]        | 0xFF           | Digital warning overvoltage threshold value for output-<br>MOSFET voltage, bits [9:2]                                                                                     |

| ovw_ORFET_LSB | 0x21 | R/W    | [1:0]        | 0x03           | Digital warning overvoltage threshold value for output-<br>MOSFET voltage, bits [1:0]                                                                                     |

| ovw_LV_MSB    | 0x22 | R/W    | [7:0]        | 0xFF           | Digital warning overvoltage threshold value for load voltage, bits [9:2]                                                                                                  |

| ovw_LV_LSB    | 0x23 | R/W    | [1:0]        | 0x03           | Digital warning overvoltage threshold value for load voltage, bits [1:0]                                                                                                  |

| DAC_LV_fc     | 0x24 | R/W    | [7:0]        | 0x00           | DAC setting for the load-voltage fast undervoltage detection comparator                                                                                                   |

| DAC_CS_fc     | 0x25 | R/W    | [7:0]        | 0xBF           | DAC setting for the circuit-breaker fast-trip comparator                                                                                                                  |

| f2s_ratio     | 0x26 | R/W    | [1:0]        | 0x03           | Settings for circuit-breaker fast comparator to slow compara-<br>tor ratio                                                                                                |

|               |      |        | [0]          | 1              | f2s_ratio[0]                                                                                                                                                              |

|               |      |        | [1]          | 1              | f2s_ratio[1]                                                                                                                                                              |

| fault         | 0x27 | R      | [3:0]        | 0x08           | Fault shutdown event logging                                                                                                                                              |

|               |      |        | [0]          |                | Fast-trip shutdown flag                                                                                                                                                   |

|               |      |        | [1]          |                | Slow-trip shutdown flag                                                                                                                                                   |

|               |      |        | [2]          | —              | Persistent reverse-current fault flag                                                                                                                                     |

|               |      |        | [3]          | _              | Default state indicator flag. This bit is set to 1 on initialization (coming out of UVLO). This bit clears to 0 after an I <sup>2</sup> C write to any writable register. |

| status1       | 0x28 | R      | [2:0]        |                | External input status                                                                                                                                                     |

|               |      |        | [0]          |                | ON state                                                                                                                                                                  |

|               |      |        | [1]          |                | GPIO1 state                                                                                                                                                               |

|               |      |        | [2]          |                | GPIO2 state                                                                                                                                                               |

| status2       | 0x29 | R      | [3:0]        |                | External output status                                                                                                                                                    |

|               |      |        | [0]          |                | READY state                                                                                                                                                               |

|               |      |        | [1]          |                | ALERT flag                                                                                                                                                                |

|               |      |        | [2]          |                | GPS-GOOD state                                                                                                                                                            |

|               |      |        | [3]          |                | GOR-GOOD state                                                                                                                                                            |

| UV_warn       | 0x2A |        | [2:0]        | 0x00           | Undervoltage warning comparators status                                                                                                                                   |

|               |      | R      | [0]          | 0              | ADCIN undervoltage warning flag                                                                                                                                           |

|               |      | R      | [1]          | 0              | Load-voltage fast undervoltage comparator warning flag                                                                                                                    |

|               |      | R/W    | [2]          | 0              | Undervoltage warning flag ALERT unmask bit; 1 to unmask ALERT                                                                                                             |

# Table 3. Register Address Map (continued)

| NAME          | ADDR | ACCESS | BIT<br>RANGE | RESET<br>VALUE | DESCRIPTION                                                                 |

|---------------|------|--------|--------------|----------------|-----------------------------------------------------------------------------|

| OV_warn       | 0x2B |        | [3:0]        | 0x00           | Digital overvoltage warning comparators status                              |

|               |      | R      | [0]          | 0              | ADCIN overvoltage warning flag                                              |

|               |      | R      | [1]          | 0              | ORing FET forward overvoltage warning flag                                  |

|               |      | R      | [2]          | 0              | Load-voltage overvoltage warning flag                                       |

|               |      | R/W    | [3]          | 0              | Overvoltage warning flag ALERT unmask bit; 1 to unmask ALERT                |

| OC_warn       | 0x2C |        | [1:0]        | 0x00           | Digital overcurrent warning comparator status                               |

|               |      | R      | [0]          | 0              | Overcurrent warning flag                                                    |

|               |      | R/W    | [1]          | 0              | Overcurrent warning flag ALERT unmask bit;1 to unmask ALERT                 |

| fokey         | 0x2D | R/W    | [7:0]        | 0x00           | Key to allow force on function                                              |

| foset         | 0x2E | R/W    | [2:0]        | 0x00           | Force-on activation (valid only when fokey = 0xA5)                          |

|               |      |        | [0]          | 0              | Force-on for input switch (GPS output)                                      |

|               |      |        | [1]          | 0              | Force-on for reverse-current protection switch (GOR output)                 |

|               |      |        | [2]          | 0              | Force reset on all registers, also resets itself                            |

| chxen         | 0x2F | R/W    | [3:0]        | 0x00           | Channel activation bits (combinational functioning with ON comparator)      |

|               |      |        | [0]          | 0              | GPS master enable                                                           |

|               |      |        | [1]          | 0              | GPS ON-enabling mask bit; 1 to mask ON-enabling                             |

|               |      |        | [2]          | 0              | GOR master enable                                                           |

|               |      |        | [3]          | 0              | GOR ON-enabling mask bit; 1 to mask ON-enabling                             |

| dgl_i         | 0x30 | R/W    | [0]          | 0x00           | Input overcurrent warning comparator deglitch on/off                        |

| dgl_uv        | 0x31 | R/W    | [0:0]        | 0x00           | Deglitch setting bit for ADCIN undervoltage comparator                      |

| dgl_ov        | 0x32 | R/W    | [1:0]        | 0x00           | Deglitch setting bits for overvoltage comparators                           |

|               |      |        | [0]          | 0              | ADCIN overvoltage warning deglitch on/off                                   |

|               |      |        | [1]          | 0              | ORing FET forward overvoltage warning deglitch on/off                       |

|               |      |        | [2]          | 0              | Load-voltage overvoltage warning deglitch on/off                            |

| buf_read_8bit | 0x33 | R/W    | [1:0]        | 0x00           | Select 10-bit or 8-bit read-out from circular buffers                       |

|               |      |        | [0]          | 0              | Set to 1 for 8-bit read-out mode on current-sense buffer                    |

|               |      |        | [1]          | 0              | Set to 1 for 8-bit read-out mode on load-voltage buffer                     |

| buf_stp_dly   | 0x34 | R/W    | [5:0]        | 0x19           | Number of samples to be stored before stopping buffers (valid 0 to 63)      |

| peak_log_rst  | 0x35 | R/W    | [3:0]        | 0x00           | When a bit is 1 the related signal peak detection is cleared startup values |

|               |      |        | [0]          | 0              | Input current min/max clear                                                 |

|               |      |        | [1]          | 0              | ADCIN min/max clear                                                         |

|               |      |        | [2]          | 0              | ORing switch voltage min/max clear                                          |

|               |      |        | [3]          | 0              | Load voltage min/max clear                                                  |

| NAME           | ADDR | ACCESS | BIT<br>RANGE | RESET<br>VALUE | DESCRIPTION                                                                                                                 |

|----------------|------|--------|--------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| peak_log_hold  | 0x36 | R/W    | [3:0]        | 0x00           | When a bit is 1 the related signal peak detection is held (no change allowed)                                               |

|                |      |        | [0]          | 0              | Input current min/max hold                                                                                                  |

|                |      |        | [1]          | 0              | ADCIN min/max hold                                                                                                          |

|                |      |        | [2]          | 0              | ORing switch voltage min/max hold                                                                                           |

|                |      |        | [3]          | 0              | Load voltage min/max hold                                                                                                   |

| GPIO_out_en    | 0x37 | R/W    | [1:0]        | 0x00           | GPIO output enable                                                                                                          |

|                |      |        | [0]          | 0              | Set to 1 to enable GPIO1 as open-drain output (0 for CMOS input with weak pullup)                                           |

|                |      |        | [1]          | 0              | Set to 1 to enable GPIO2 as open-drain output (0 for CMOS input with weak pullup)                                           |

| GPIO_state_set | 0x38 | R/W    | [1:0]        | 0x00           | GPIO output state                                                                                                           |

|                |      |        | [0]          | 0              | Set to 0 to pull down GPIO1 when in output mode; set to 1 allow GPIO1 to go high (internal weak pullup to V <sub>DD</sub> ) |

|                |      |        | [1]          | 0              | Set to 0 to pull down GPIO2 when in output mode; set to 1 allow GPIO2 to go high (internal weak pullup to V <sub>DD</sub> ) |

| or_fault_timer | 0x39 | R/W    | [1:0]        | 0x03           | ORing fault flag time delay setting. Default is 192µs.                                                                      |

|                |      |        | [0]          | 1              | 00 = 32µs<br>01 = 64µs                                                                                                      |

|                |      |        | [1]          | 1              | 10 = 128µs<br>11 = 192µs                                                                                                    |

| buf_base_CS    | 0x3A | R      | [7:0]        |                | Base address for the input current circular buffer                                                                          |

| buf_base_LV    | 0x3B | R      | [7:0]        |                | Base address for the load-voltage circular buffer                                                                           |

### Table 3. Register Address Map (continued)

### **Setting Circuit-Breaker Thresholds**

To select and set the MAX5968 slow-trip and fast-trip comparator thresholds, use the following procedure:

- 1) Select one of four ratios between the fast-trip threshold and the slow-trip threshold: 200%, 175%, 150%, or 125%. The ratio is set by writing to the f2s\_ratio register (the default setting on power-up is 200%).

- 2) Determine the slow-trip threshold VTH,ST based on the anticipated maximum continuous module input current during normal operation, and the value of the current-sense resistor. The slow-trip threshold should include some margin above the maximum input current to prevent spurious circuit-breaker shutdown and to accommodate passive component tolerances:

VTH,ST = RSENSE × IINPUT,MAX × 120%

3) Calculate the necessary fast-trip threshold V<sub>TH,FT</sub> based on the ratio set in step 1:

VTH,FT = VTH,ST x (fast-to-slow threshold ratio)

4) Program the fast-trip and slow-trip thresholds by writing an 8-bit value to the DAC\_CS\_fc register. This 8-bit value is determined from the desired VTH,ST value that was calculated in step 2, the threshold ratio from step 1, and the current-sense range of +40mV:

Table 1 shows the specified ranges for the fast-trip and slow-trip thresholds for all selections of the fast-to-slow threshold ratio. The fast-trip DAC can be programmed to values below 0x26 (40% of the current-sense range), but accuracy is not specified for operation below 40%.

### Force-On Bit

When the force-on bit is set to 1, the input and output switches are enabled and do not shut down. The overcurrent and reverse current comparator outputs are ignored. The power-on reset value of this bit is 0. There is a Force-On Key register that must be set to 0xA5 for the force-on function to become active. If this register

contains any value other than 0xA5, setting the force-on bit to 1 has no effect. The power-on default value of the Force-On Key register is 0x00.

### **ADC Result Registers**

Result registers contain the most recent ADC values. Because the ADC is multiplexed to four different channels sequentially, at any time the result registers can contain values from the current ADC cycle and the previous cycle. For example, if the conversion for channel 2 was just stored in the ADC Result register, registers for channels 0, 1, and 2 would contain values from the present scan and the registers for channel 3 would contain the values from the previous scan. The registers can be read at any time through the I<sup>2</sup>C interface. The registers are buffered so that reading any ADC result register does not interrupt or delay the ADC cycle, nor does it cause missed readings.

#### **Min/Max Registers**

Each ADC channel features a min and a max register; there are four min registers and four max registers. In each ADC cycle for each signal, the ADC reading is compared to the contents of the min register. If the current value is less than min register value, the current value is stored in the min register. If the current value is greater than the value in the max register, the current value is stored in the max register. The input current and load-voltage min/max registers do not update when the circular buffers are stopped because of a fault condition or shutdown.

The power-on reset value of the min registers is 0x3FF. To reset a min register, write 0x3FF.

The power-on reset value of the max registers is 0x000. To reset a max register, write 0x000.

Control registers are provided to hold and clear the min and max registers independently for each signal.

#### **Digital Warning Comparators**

Each monitored signal is equipped with one or more programmable digital warning comparators. If the most recent conversion result exceeds the programmed overvoltage or overcurrent value, or is less than the undervoltage value, the warning flag registers are set. Each group of warning flag registers has a mask bit that masks or unmasks ALERT bit response to these warning flags.

The default value of the overvoltage and overcurrent thresholds is 0x3FF, and the default value for the undervoltage threshold is 0x000. These default values disable the associated digital comparator. When the values are programmed to some value other than the default, the comparator is active.

Reading the under/over warning flag registers automatically clears the contents of the registers, eliminating the need for a second  $I^2C$  write operation to clear the flags. See Table 4.

#### **Circular Buffer**

The circular buffer includes two banks—one for the voltage measurement across the input current-sense resistor, and another for the load-voltage measurement; each comprises 50 10-bit samples.

A block read is triggered by the I<sup>2</sup>C interface when a read operation is attempted from one of the circular buffer block base addresses. Readings can be either of the whole 10-bit samples or of the 8-bit upper bytes, according to the buf\_read\_8bit register.

Internal writing to either or both of the buffers can be inhibited directly by the user through a dedicated register at 0x19. Writing to the buffers also stops when the input switch is shut down. When a buffer block is read through the  $I^2C$  interface, new load voltage and input current measurements are not written into the circular buffer.