# EM77950

## **BB** Controller

# Product Specification

DOC. VERSION 1.0

ELAN MICROELECTRONICS CORP. October 2007

### **Trademark Acknowledgments:**

IBM is a registered trademark and PS/2 is a trademark of IBM. Windows is a trademark of Microsoft Corporation.

ELAN and ELAN logo

### Copyright © 2007 by ELAN Microelectronics Corporation All Rights Reserved

Printed in Taiwan

The contents of this specification are subject to change without further notice. ELAN Microelectronics assumes no responsibility concerning the accuracy, adequacy, or completeness of this specification. ELAN Microelectronics makes no commitment to update, or to keep current the information and material contained in this specification. Such information and material may change to conform to each confirmed order.

In no event shall ELAN Microelectronics be made responsible for any claims attributed to errors, omissions, or other inaccuracies in the information or material contained in this specification. ELAN Microelectronics shall not be liable for direct, indirect, special incidental, or consequential damages arising from the use of such information or material.

The software (if any) described in this specification is furnished under a license or nondisclosure agreement, and may be used or copied only in accordance with the terms of such agreement.

ELAN Microelectronics products are not intended for use in life support appliances, devices, or systems. Use of ELAN Microelectronics product in such applications is not supported and is prohibited. NO PART OF THIS SPECIFICATION MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS WITHOUT THE EXPRESSED WRITTEN PERMISSION OF ELAN MICROELECTRONICS.

## ELAN

### Headquarters: No. 12, Innovation Road 1 Hsinchu Science Park Hsinchu, Taiwan 308 Tel: +886 3 563-9977 Fax: +886 3 563-9966 http://www.emc.com.tw

Hong Kong: Elan (HK) Microelectronics Corporation, Ltd. Flat A, 19F., World Tech Centre 95 How Ming Street, Kwun Tong Kowloon, HONG KONG Tel: +852 2723-3376 Fax: +852 2723-7780 elanhk@emc.com.hk

#### Shenzhen:

ELAN MICROELECTRONICS CORPORATION

#### Elan Microelectronics Shenzhen, Ltd.

3F, SSMEC Bldg., Gaoxin S. Ave. I Shenzhen Hi-tech Industrial Park (South Area), Shenzhen CHINA 518057 Tel: +86 755 2601-0565 Fax: +86 755 2601-0500

## USA: Elan Information Technology Group (USA)

P.O. Box 601 Cupertino, CA 95015 USA Tel: +1 408 366-8225 Fax: +1 408 366-8225

#### Shanghai: Elan Microelectronics Shanghai, Ltd.

#23, Zone 115, Lane 572, Bibo Rd. Zhangjiang Hi-Tech Park Shanghai, CHINA 201203 Tel: +86 21 5080-3866 Fax: +86 21 5080-4600

# Contents

| 1      | Gen  | eral Description                                                     | .1   |  |  |  |  |  |  |  |  |

|--------|------|----------------------------------------------------------------------|------|--|--|--|--|--|--|--|--|

| 2      | Feat | ures                                                                 | res1 |  |  |  |  |  |  |  |  |

|        | 2.1  | Core                                                                 | .1   |  |  |  |  |  |  |  |  |

|        | 2.2  | Oscillators/System Clocks                                            | .2   |  |  |  |  |  |  |  |  |

|        | 2.3  | Input and Output (I/O) Pins                                          | .2   |  |  |  |  |  |  |  |  |

|        | 2.4  | Timers and Counters                                                  | .2   |  |  |  |  |  |  |  |  |

|        | 2.5  | Interrupt Sources and Features                                       |      |  |  |  |  |  |  |  |  |

|        | 2.6  | Baseband (BB)                                                        |      |  |  |  |  |  |  |  |  |

|        | 2.7  | Serial Peripheral Interface (SPI)                                    |      |  |  |  |  |  |  |  |  |

|        | 2.8  | Pulse Width Modulation (PWM)                                         |      |  |  |  |  |  |  |  |  |

|        | 2.0  | Analog to Digital Converter (ADC)                                    |      |  |  |  |  |  |  |  |  |

| •      |      |                                                                      |      |  |  |  |  |  |  |  |  |

| 3      |      | Assignment                                                           |      |  |  |  |  |  |  |  |  |

| 4<br>5 |      | Description<br>k Diagram                                             |      |  |  |  |  |  |  |  |  |

| -      |      | •                                                                    |      |  |  |  |  |  |  |  |  |

| 6      |      | Nory                                                                 |      |  |  |  |  |  |  |  |  |

|        | 6.1  | Program Memory                                                       |      |  |  |  |  |  |  |  |  |

|        | 6.2  | RAM–Register                                                         |      |  |  |  |  |  |  |  |  |

| 7      |      | ction Description                                                    |      |  |  |  |  |  |  |  |  |

|        | 7.1  | Special Purpose Registers                                            |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.1 Accumulator – ACC                                              |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.2 Indirect Addressing Contents – IAC0 and IAC1                   |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.3 High Byte Program Counter HPC and Low Byte Program Counter LPC |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.4 Status Register – SR                                           |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.5 RAM Bank Selector – RAMBS0 and RAMBS1                          |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.6 ROM Page Selector – ROMPS                                      |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.7 Indirect Addressing Pointers – IAP0 and IAP1                   |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.8 Indirect Address Pointer Direction Control Register – IAPDR    |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.9 Table Look-up Pointer – LTBL and HTBL                          |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.10 Stack Pointer – STKPTR                                        |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.11 Repeat Counter – RPTC                                         |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.12 Prescaler Counter – PRC                                       |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.13 Real Time Clock Counter – RTCC                                |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.14 Interrupt Flag Register – INTF                                |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.15 Key Wake-up Flag Register – KWUAIF & KWUBIF                   |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.16 I/O Port Registers – PTA ~ PTF                                |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.17 16-bit Free Run Counter (FRC) – LFRC HFRC & LFRCB             |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.18 Serial Peripheral Interface Read Register – SPIRB             |      |  |  |  |  |  |  |  |  |

|        |      | 7.1.19 Serial Peripheral Interface Write Register – SPIWB            | 29   |  |  |  |  |  |  |  |  |

Product Specification (V1.0) 10.09.2007

• iii

|      | 7.1.20  | ADC Converting Value – ADDATA                                  | .29 |

|------|---------|----------------------------------------------------------------|-----|

|      | 7.1.21  | PWM Duty – DT0L/DT0H & DT1L/DT1H                               | .29 |

|      | 7.1.22  | PWM Period – PRD0L/PRD0H & PRD1L/PRD1H                         | .29 |

|      | 7.1.23  | PWM Duty Latch – DL0L/DL0H & DL1L/DL1H                         | .30 |

|      | 7.1.24  | BB Address Register – RFAAR                                    | .30 |

|      | 7.1.25  | BB Data Buffer Register – RFDB                                 | .30 |

|      | 7.1.26  | BB Data Read/Write Control Register – RFACR                    | .30 |

|      | 7.1.27  | BB Interrupt Flag Register – RFINTF                            | .30 |

| 7.2  | Dual P  | ort Register                                                   | 31  |

| 7.3  | Systen  | n Status, Control and Configuration Registers                  | 31  |

|      | 7.3.1   | Peripherals Enable Control – PRIE                              | .31 |

|      | 7.3.2   | Interrupts Enable Control – INTE                               | .31 |

|      | 7.3.3   | Key Wake-up Enable Control – KWUAIE & KWUBIE                   | .32 |

|      | 7.3.4   | External Interrupts Edge Control – EINTED                      |     |

|      | 7.3.5   | Serial Peripheral Serial (SPI) Enable Control Register - SPIC  | .33 |

|      | 7.3.6   | I/O Control Registers – IOCA~IOCF                              | .33 |

|      | 7.3.7   | Pull-up Resistance Control Registers for Ports A~F – PUCA~PUCF | .34 |

|      | 7.3.8   | Open Drain Control Registers of Port B/Port C – ODCB/ODCC      | .34 |

|      | 7.3.9   | Timer Clock Counter Controller – TCCC                          | .34 |

|      | 7.3.10  | Free Run Counter Controller – FRCC                             | .35 |

|      | 7.3.11  | Watchdog Timer Controller – WDTC                               | .35 |

|      | 7.3.12  | ADC Analog Input Pin Select – ADCAIS                           | .36 |

|      | 7.3.13  | ADC Configuration Register – ADCCR                             | .36 |

|      | 7.3.14  | PWM Control Register – PWMCR                                   | .37 |

|      | 7.3.15  | BB Interrupt Control Register – RFINTE                         | .37 |

| 7.4  | Code (  | Option (ROM-0x2FFF)                                            | 38  |

| Base | eband ( | ВВ)                                                            | 39  |

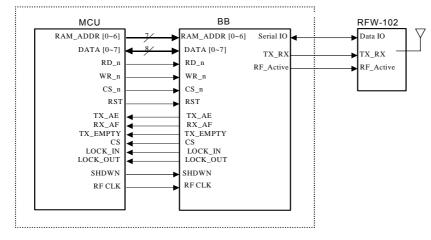

| 8.1  | BB: Sta | andard Interface for the RFW102 Series                         | 39  |

|      | 8.1.1   | Features                                                       | .39 |

|      | 8.1.2   | Description                                                    | .39 |

|      | 8.1.3   | I/O and Package Description                                    | .40 |

|      | 8.1.4   | BB Architecture                                                | .42 |

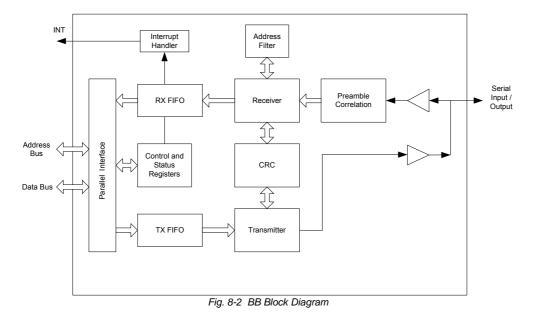

| 8.2  | BB De   | scription                                                      | 42  |

|      | 8.2.1   | Reset                                                          | .42 |

|      | 8.2.2   | Power Saving Modes                                             | .42 |

|      |         | 8.2.2.1 Power-Down Mode                                        | .42 |

|      |         | 8.2.2.2 Idle Mode                                              | .43 |

|      | 8.2.3   | Preamble Correlation                                           | .43 |

|      | 8.2.4   | Refresh Bit                                                    | .44 |

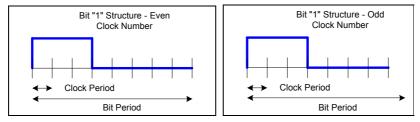

|      | 8.2.5   | Bit Structure                                                  | .44 |

|      | 8.2.6   | CRC                                                            | .45 |

|      |         |                                                                |     |

Product Specification (V1.0) 10.09.2007

CLAN

8

|   |       | 8.2.7    | RX FIFO                                  | 46   |

|---|-------|----------|------------------------------------------|------|

|   |       | 8.2.8    | TX FIFO                                  | 47   |

|   |       | 8.2.9    | Interrupt Driver                         | 47   |

|   |       | 8.2.10   | Packet Size                              | 49   |

|   |       | 8.2.11   | NET_ID and NODE_ID Filters               | 49   |

|   |       | 8.2.12   | Carrier-Sense                            | 50   |

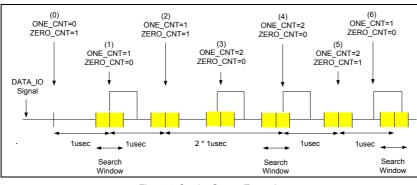

|   |       |          | 8.2.12.1 RFWaves Carrier-Sense Algorithm | 50   |

|   |       | 8.2.13   | Receiver Reference Capacitor Discharge   | 51   |

|   |       | 8.2.14   | Changing BB Configuration                | 52   |

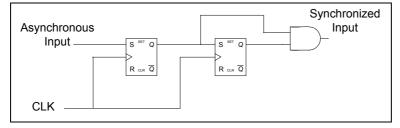

|   |       | 8.2.15   | Input Synchronizer                       | 52   |

|   | 8.3   | Registe  | er Description                           | . 52 |

|   |       | 8.3.1    | Bit Length Register (BLR)                | 53   |

|   |       | 8.3.2    | Preamble Low Register (PRE-L)            | 53   |

|   |       | 8.3.3    | Preamble High Register (PRE-H)           | 53   |

|   |       | 8.3.4    | Packet Parameter Register (PPR)          | 53   |

|   |       | 8.3.5    | System Control Register1 (SCR1)          | 55   |

|   |       | 8.3.6    | System Control Register 2 (SCR2)         | 55   |

|   |       | 8.3.7    | System Control Register 3 (SCR3)         |      |

|   |       | 8.3.8    | System Control Register 4 (SCR4)         | 58   |

|   |       | 8.3.9    | Transmit FIFO Status Register (TFSR)     | 59   |

|   |       |          | Receive FIFO Status Register (RFSR)      |      |

|   |       | 8.3.11   | Location Control Register (LCR)          | 59   |

|   |       |          | Node Identity Register (BIR)             |      |

|   |       | 8.3.13   | Net Identity Register (NIR)              | 60   |

|   |       |          | System Status Register (SSR)             |      |

|   |       |          | Packet Size Register (PSR)               |      |

|   |       |          | Carrier Sense Register (CSR)             |      |

|   | 8.4   | Interru  | pt Registers                             |      |

|   |       | 8.4.1    | Interrupt Enable Register (IER)          |      |

|   |       | 8.4.2    | Interrupt Identification Register (IIR)  | 64   |

|   | 8.5   | List of  | BB Register Mapping                      | .65  |

|   | 8.6   | MCU E    | 3B Control Registers                     | .65  |

|   |       | 8.6.1    | Control Registers List                   | 65   |

|   |       | 8.6.2    | BB Control Example                       | 66   |

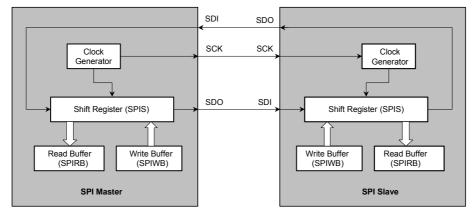

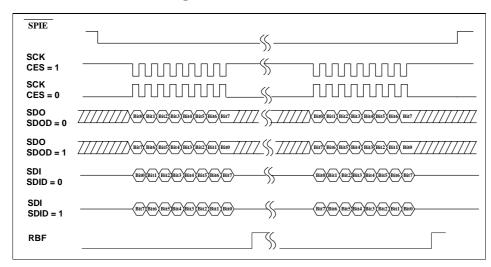

| 9 | Direc | ction Se | erial Peripheral Interface (SPI)         | . 68 |

|   | 9.1   | Introdu  | lction                                   | .68  |

|   | 9.2   | Featur   | es                                       | .68  |

|   | 9.3   | Block [  | Diagram                                  | .68  |

|   | 9.4   |          | eiver Timing                             |      |

|   | 9.5   |          | d Registers with SPI                     |      |

|   |       |          | U                                        |      |

Product Specification (V1.0) 10.09.2007

• v

Contents

|    | 9.6 Function Description                                | 70 |

|----|---------------------------------------------------------|----|

|    | 9.6.1 Block Diagram Description                         | 70 |

|    | 9.6.2 Signal & Pin Description                          |    |

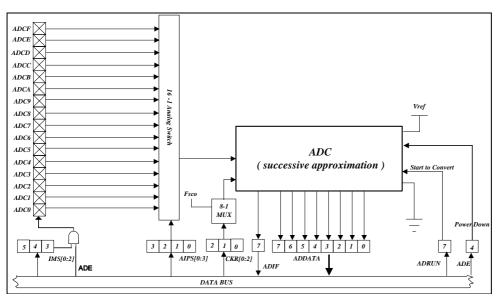

| 10 | Analog to Digital Converter (ADC)                       | 71 |

|    | 10.1 ADC Control Registers                              | 72 |

|    | 10.2 Programming Steps/Considerations                   | 74 |

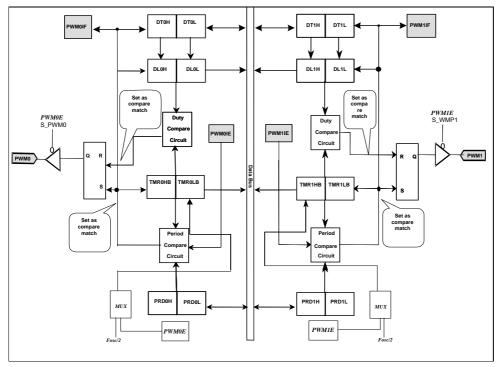

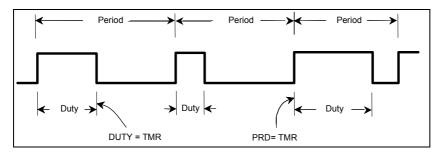

| 11 | Dual Pulse Width Modulations (PWM0 and PWM1)            | 75 |

|    | 11.1 Overview                                           | 75 |

|    | 11.2 PWM Control Registers                              | 76 |

|    | 11.3 PWM Programming Procedures/Steps                   | 78 |

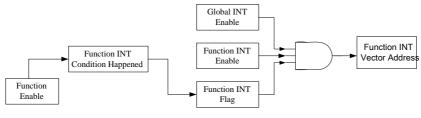

| 12 | Interrupts                                              | 78 |

|    | 12.1 Introduction                                       | 78 |

| 13 | Circuitry of Input and Output Pins                      | 80 |

|    | 13.1 Introduction                                       | 80 |

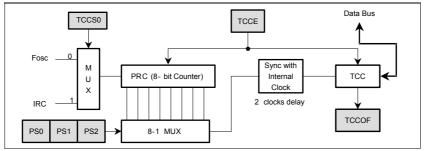

| 14 | Timer/Counter System                                    | 80 |

|    | 14.1 Introduction                                       | 80 |

|    | 14.2 Time Clock Counter (TCC)                           | 80 |

|    | 14.2.1 Block Diagram of TCC                             | 80 |

|    | 14.2.2 TCC Control Registers                            |    |

|    | 14.2.3 TCC Programming Procedures/Steps                 |    |

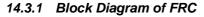

|    | 14.3 Free Run Counter                                   |    |

|    | 14.3.1 Block Diagram of FRC                             |    |

|    | 14.3.2 FRC Control Registers                            |    |

|    | 14.3.3 FRC Programming Procedures/Steps                 |    |

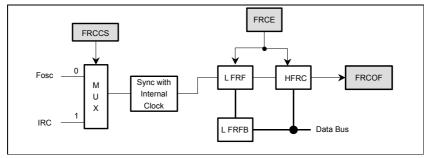

| 15 | Reset and Wake up                                       |    |

|    | 15.1 Reset                                              |    |

|    | 15.2 The Status of RST, T, and P of the STATUS Register |    |

|    | 15.3 System Set-up Time (SST)                           |    |

|    | 15.4 Wake-up Procedure on Power-on Reset                |    |

| 16 | Oscillators                                             |    |

|    | 16.1 Introduction                                       |    |

|    | 16.2 Clock Signal Distribution                          |    |

|    | 16.3 PLL Oscillator                                     |    |

|    | 16.4 Selected PLL Oscillation out                       |    |

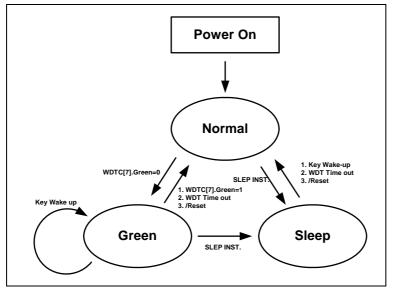

| 17 | Low-Power Mode                                          |    |

|    | 17.1 Introduction                                       |    |

|    | 17.2 Green Mode                                         | 87 |

|    | 17.3 Sleep Mode                                         |    |

|    |                                                         |    |

Product Specification (V1.0) 10.09.2007

CLAN

| 18 | Instruction Description                         |  |

|----|-------------------------------------------------|--|

|    | 18.1 Instruction Set Summary                    |  |

| 19 | Electrical Specification                        |  |

|    | 19.1 Absolute Maximum Ratings                   |  |

|    | 19.2 DC Electrical Characteristic               |  |

|    | 19.3 Voltage Detector Electrical Characteristic |  |

|    | 19.4 AC Electrical Characteristic               |  |

|    | 19.4.1 MCU                                      |  |

|    | 19.4.2 BB                                       |  |

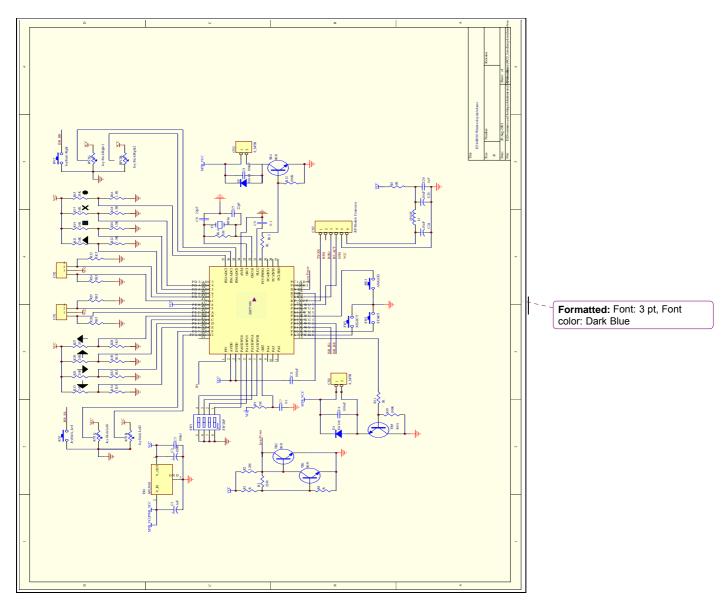

| 20 | Application Circuit                             |  |

## APPENDIX

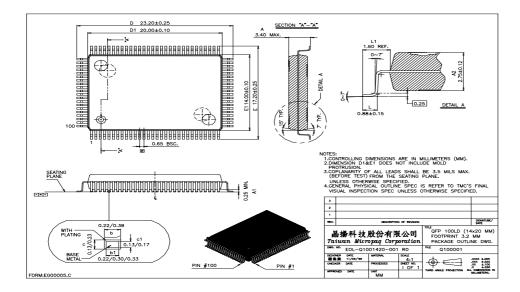

| Α | Package Type        | . 94 |

|---|---------------------|------|

|   | Package Information |      |

## **Specification Revision History**

| Doc. Version | Revision Description     | Date       |

|--------------|--------------------------|------------|

| 1.0          | Initial released version | 2007/10/09 |

• vii

Product Specification (V1.0) 10.09.2007

## **1** General Description

The EM77950 from ELAN Electronics is a low-cost and high performance 8-bit CMOS advance RISC architecture microcontroller device. It has an on-chip 1-Mbps RF driver module/Base Band (BB), Serial Peripheral Interface (SPI), dual Pulse Width Modulation (PWM) with 16-bit resolution, an 8-bit Timer Clock Counter (TCC) and a 16-bit Free Run Timer, multi-channel Analog to Digital Converter (ADC) with 8-bit resolution, Key Wake-up function (KWU), Power-on Reset (POR), Watchdog Timer (WDT), and power saving Sleep Mode. All these features combine to ensure applications require the least external components, hence, not only reduce system cost, but also have the advantage of low power consumption and enhanced device reliability.

The 52-pin EM77950 is available in a very cost-effective version that provides a single chip solution in designing wireless products.

## 2 Features

## 2.1 Core

- Operating Voltage Range: 2.2V ~ 3.6V DC (ADC reference volt 3V)

- Operating Temperature Range: 0°C ~ 70°C

- Operating Frequency Range: DC ~ 48MHz (1 clock/cycle)

- 6MHz external clock source

- 6/12/24/48 MHz to Core clock

- 6/12/24/48 MHz to clock

- Internal Memory

- 12K x 16 bits of on-chip Program ROM

- 896 x 8 bits of on-chip Register (SRAM)

- Watchdog Timer (WDT)

- 32 level stacks for both CALL and interrupt subroutine

- Internal Power-on Reset (POR) function

- Code protection function available

- All single cycle (1 clock) instruction except for conditional branches which are two or three cycles.

- Direct, indirect and relative addressing modes

- Low power, high speed CMOS technology

- Power consumption:

- < 4 mA @ 3.3V, 6 MHz

- < 60 µA @ 3.0V, (RC = 32.768 kHz)

- < 1 µA standby current

- 52/44-pin QFP package

## 2.2 Oscillators/System Clocks

- Three oscillator options:

- Crystal/Resonate oscillator of high frequency

- PLL oscillator: 6MHz, 12 MHz, 24 MHz, and 48 MHz (External crystal should be 6 MHz)

- External RC oscillator

- Three modes of system clocks:

- Sleep mode

- Green mode

- Normal mode

- Internal RC oscillator for Power-on Reset (POR) and Watchdog Timer (WDT)

## 2.3 Input and Output (I/O) Pins

- 40 I/O pins max.

- Pull-up resistor options

- Key Wake-up function

- Open drain output options

## 2.4 Timers and Counters

- Programmable 8-bit real Time Clock/Counter (TCC) with prescaler and overflow interrupt

- 16-bit Free Run Counter (FRC) with overflow interrupt

## 2.5 Interrupt Sources and Features

- Hardware priority check

- Different interrupt vectors

- Interrupts

- Key Wake-up function

- External pin interrupt

- 16-bit Free Run Counter Overflow

- TCC (time-base) overflow;

- Read Buffer Full Interrupt in Serial Peripheral Interface (SPI)

- · An analog to digital converting (ADC) complete

- One period of Pulse Width Modulation (PWM) complete

- Base Band (BB) function interrupts:

- CSD: carrier sense detection

- TX\_AE: TX\_FIFO almost full

- RX\_AF: RX\_FIFO almost full

- TX\_EMPTY: finish a transmitting a package

- RX\_OF: RX\_FIFO overflow

- LINK\_DIS: zero counter capacitor discharge mechanism

- LOCK\_OUT: finish receiving a package

- LOCK\_IN: start receiving a package

## 2.6 Baseband (BB)

- Serial to Parallel conversion of RFW102 interface

- Parallel interface to RFW102 modem

- Serial to Parallel conversion of RFW102 interface

- Input FIFO (RX\_FIFO)

- Output FIFO (TX\_FIFO)

- Preamble Correlation

- Packet Address Filter (Network and unique)

- CRC calculation

- Inter-RFWAVES networks Carrier-sense

- Discharge of RFW-102 reference capacitor

- Compensate for clock drifts between the transmitting EM77950 and the receiving EM77950 up to 1000ppm. Hence, the EM77950 requires low performance crystal.

- Interrupt Driver connected to the EM77950's internal interrupt and informs the EM77950 about BB events.

## 2.7 Serial Peripheral Interface (SPI)

- Either MSB or LBS can be transmitted/received first

- Both Master and Slave modes available

## 2.8 Pulse Width Modulation (PWM)

Dual Pulse Width Modulation (PWM) with 16-bit resolution

## 2.9 Analog to Digital Converter (ADC)

• 16 multi-channel Analog to Digital Converter with 8-bit resolution

## 3 Pins Assignment

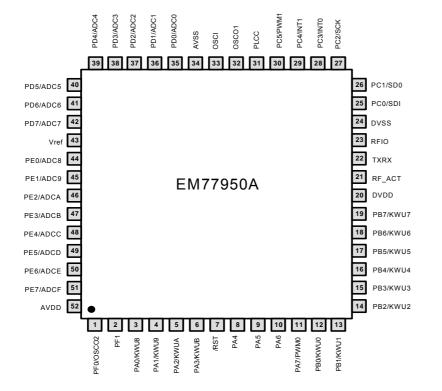

Fig. 3-1 Pin Configuration of EM77950A

Product Specification (V1.0) 10.09.2007 (This specification is subject to change without further notice)

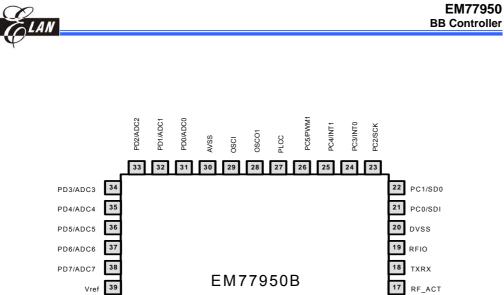

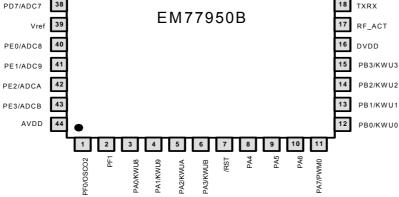

Fig. 3-2 Pins Configuration of EM77950B

Product Specification (V1.0) 10.09.2007 (This specification is subject to change without further notice)

## 4 Pin Description

The Table below shows the corresponding relationship between the pad and pins of EM77950A

| Pin # | Symbol           | Туре | Schmitt<br>Trigger | Pull High<br>/50KΩ | Open<br>Drain | Function Description                                                                                          |

|-------|------------------|------|--------------------|--------------------|---------------|---------------------------------------------------------------------------------------------------------------|

| 1     | PTF0/OSCO2       | I/O  | -                  | $\checkmark$       | _             | Pin 0 of Port F<br>Selected PLL clock out                                                                     |

| 2     | PF1              | I/O  | -                  | $\checkmark$       | -             | Pin 1 of Port F                                                                                               |

| 3~6   | KWU8~B,<br>PA0~3 | I/O  | -                  | $\checkmark$       | -             | Pins 0~3 of Port A (default).<br>Key Wake-up 8~B                                                              |

| 7     | /RST             | Ι    | $\checkmark$       | -                  | Ι             | Reset pin                                                                                                     |

| 8~10  | PTA4~6           | I/O  | -                  | $\checkmark$       | I             | Pins 4~6 of Port A.                                                                                           |

| 11    | PWM0/PTA7        | I/O  | -                  | $\checkmark$       | _             | Pin 7 of Port A.<br>PWM0 output                                                                               |

| 12~19 | PB0 ~ PB7        | I/O  | -                  | $\checkmark$       | $\checkmark$  | Pins 0~7 of Port B (default).<br>Key Wake-up 0~7                                                              |

| 20    | DVDD             | -    | -                  | -                  | -             | Power supply for digital circuit. The power source value should be within the range of the operating voltage. |

| 21    | RF_ACT           | 0    | -                  | -                  | -             | BB/RF Active                                                                                                  |

| 22    | TXRX             | 0    | -                  | -                  | -             | Transceiver modes control                                                                                     |

| 23    | RFIO             | I/O  | -                  | -                  | -             | Transceiver to/from RF modem                                                                                  |

| 24    | DVSS             | I    | -                  | 1                  | -             | Ground Pin for Digital circuit                                                                                |

| 25    | SDI/PTC0         | I/O  | $\checkmark$       | $\checkmark$       | $\checkmark$  | Data in of SPI<br>Pin 0 of Port C                                                                             |

| 26    | SDO/PTC1         | I/O  | $\checkmark$       | $\checkmark$       | $\checkmark$  | Data out of SPI<br>Pin 1 of Port C                                                                            |

| 27    | SCK/PTC2         | I/O  | $\checkmark$       | $\checkmark$       | $\checkmark$  | Clock of SPI<br>Pin 2 of Port C                                                                               |

| 28    | EINT0/ PTC3      | I/O  | _                  | $\checkmark$       | $\checkmark$  | External interrupt Pin 0<br>Pin 3 of Port C                                                                   |

| 29    | EINT1/ PTC4      | I/O  | -                  | $\checkmark$       | $\checkmark$  | External interrupt Pin 1<br>Pin 4 of Port C                                                                   |

| 30    | PWM1/PTC5        | I/O  | _                  | $\checkmark$       | $\checkmark$  | Pin 5 of Port C.<br>PWM1 output                                                                               |

| 31    | PLLC             | -    | -                  | -                  | -             | External capacitor for PLL circuit                                                                            |

| 32    | OSCO1            | 0    | -                  | -                  | -             | Output of crystal oscillator                                                                                  |

| 33    | OSCI             | Ι    | _                  | -                  | I             | Input of crystal oscillator                                                                                   |

| 34    | AVSS             | -    | -                  | -                  | -             | Ground Pin for Analog circuit                                                                                 |

6•

| Pin # | Symbol            | Туре | Schmitt<br>Trigger | Pull High<br>/50KΩ | Open<br>Drain | Function Description                                                                                         |

|-------|-------------------|------|--------------------|--------------------|---------------|--------------------------------------------------------------------------------------------------------------|

| 35~42 | PTD0~7,<br>ADC0~7 | I/O  | -                  | $\checkmark$       | -             | Pins 0~7 of Port D<br>Inputs 0~7 of ADC                                                                      |

| 43    | VREF              | I    | -                  | -                  | -             | Reference voltage for ADC                                                                                    |

| 44~51 | PTE0~7,<br>ADC8~F | I/O  | -                  | $\checkmark$       | -             | Pins 0~7 of Port E<br>Inputs 8~F of ADC                                                                      |

| 52    | AVDD              | -    | -                  | -                  | -             | Power supply for analog circuit. The power source value should be within the range of the operating voltage. |

The Table below shows the corresponding relationship between the pad and pins of EM77950B

| Pin # | Symbol           | Туре | Schmitt<br>Trigger | Pull High<br>/50KΩ | Open<br>Drain | Function Description                                                                                          |

|-------|------------------|------|--------------------|--------------------|---------------|---------------------------------------------------------------------------------------------------------------|

| 1     | PTF0/OSCO2       | I/O  | _                  | $\checkmark$       | _             | Pin 0 of Port F                                                                                               |

|       |                  |      |                    |                    |               | Selected PLL clock out                                                                                        |

| 2     | PF1              | I/O  | -                  | $\checkmark$       | -             | Pin 1 of Port F                                                                                               |

| 3~6   | KWU8~B,<br>PA0~3 | I/O  | -                  | $\checkmark$       | -             | Pins 0~3 of Port A (default)<br>Key Wake-up 8~B                                                               |

| 7     | /RST             | Ι    | $\checkmark$       | Ι                  | I             | Reset pin                                                                                                     |

| 8~10  | PTA4~6           | I/O  | -                  | $\checkmark$       | Ι             | Pins 4~6 of Port A                                                                                            |

| 11    | PWM0/PTA7        | 1/0  | -                  |                    | -             | Pin 7 of Port A.                                                                                              |

|       |                  |      |                    |                    |               | PWM0 output                                                                                                   |

| 12~15 | PB0 ~ PB3        | I/O  |                    |                    |               | Pins 0~3 of Port B (default)                                                                                  |

| 12.10 | F 60 % F 65      | 1/0  | _                  | v                  | v             | Key Wake-up 0~7                                                                                               |

| 16    | DVDD             | _    | _                  | _                  | _             | Power supply for digital circuit. The power source value should be within the range of the operating voltage. |

| 17    | RF_ACT           | 0    | _                  | -                  | _             | BB/RF Active                                                                                                  |

| 18    | TXRX             | 0    | -                  | -                  | _             | Transceiver modes control                                                                                     |

| 19    | RFIO             | I/O  | -                  | -                  | _             | Transceiver to/from RF modem                                                                                  |

| 20    | DVSS             | -    | -                  | -                  | -             | Ground Pin for Digital circuit                                                                                |

| 04    |                  | 1/0  | .1                 | .1                 | .1            | Data in of SPI                                                                                                |

| 21    | SDI/PTC0         | I/O  | $\checkmark$       | $\checkmark$       | $\checkmark$  | Pin 0 of Port C                                                                                               |

| 22    | SDO/PTC1         | 1/0  |                    |                    |               | Data out of SPI                                                                                               |

| ~~~   | 3D0/F101         | 1/0  | N                  | N                  | N             | Pin 1 of Port C                                                                                               |

| Pin # | Symbol            | Туре | Schmitt<br>Trigger | Pull High<br>/50KΩ | Open<br>Drain | Function Description                                                                                         |

|-------|-------------------|------|--------------------|--------------------|---------------|--------------------------------------------------------------------------------------------------------------|

| 23    | SCK/PTC2          | I/O  | $\checkmark$       | $\checkmark$       | $\checkmark$  | Clock of SPI<br>Pin 2 of Port C                                                                              |

| 24    | EINT0/ PTC3       | I/O  | -                  | $\checkmark$       | $\checkmark$  | External interrupt Pin 0<br>Pin 3 of Port C                                                                  |

| 25    | EINT1/ PTC4       | I/O  | _                  | $\checkmark$       | $\checkmark$  | External interrupt Pin 1<br>Pin 4 of Port C                                                                  |

| 26    | PWM1/PTC5         | I/O  | _                  | $\checkmark$       | $\checkmark$  | Pin 5 of Port C<br>PWM1 output                                                                               |

| 27    | PLLC              | -    | -                  | -                  | -             | External capacitor for PLL circuit                                                                           |

| 28    | OSCO1             | 0    | -                  | -                  | -             | Output of crystal oscillator                                                                                 |

| 29    | OSCI              | I    | -                  | -                  | -             | Input of crystal oscillator                                                                                  |

| 31~38 | PTD0~7,<br>ADC0~7 | I/O  | _                  | $\checkmark$       | _             | Pins 0~7 of Port D<br>Inputs 0~7 of ADC                                                                      |

| 39    | VREF              | I    | -                  | -                  | -             | Reference voltage for ADC                                                                                    |

| 40~43 | PTE0~3,<br>ADC8~B | I/O  | _                  | $\checkmark$       | -             | Pins 0~3 of Port E<br>Inputs 8~B of ADC                                                                      |

| 44    | AVDD              | -    | -                  | -                  | _             | Power supply for analog circuit. The power source value should be within the range of the operating voltage. |

Product Specification (V1.0) 10.09.2007 (This specification is subject to change without further notice)

LAN

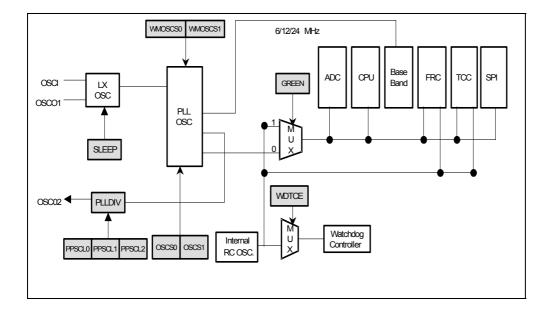

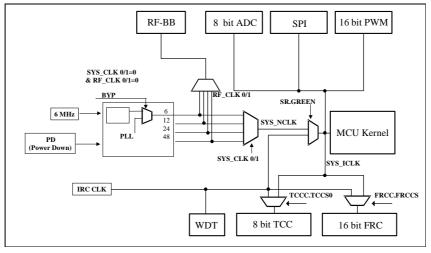

## 5 Block Diagram

Product Specification (V1.0) 10.09.2007 (This specification is subject to change without further notice)

## 6 Memory

## 6.1 Program Memory

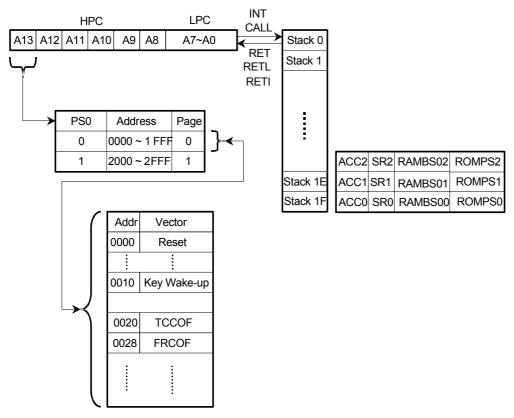

The EM77950 has a 14-bit program counter (PC). The space of program memory, which is partitioned into 2 pages can address up to 12K. One page has 8K in length, and the other is 4K. Fig. 6-1 depicts the profile of the program memory and stack. The initial address is 0x0000. The table of interrupt-vectors starts from 0x10 to 0x80 with every other eight-address space.

Fig. 6-1 Configuration of Program Memory (ROM) for EM77950

Product Specification (V1.0) 10.09.2007 (This specification is subject to change without further notice)

## 6.2 RAM-Register

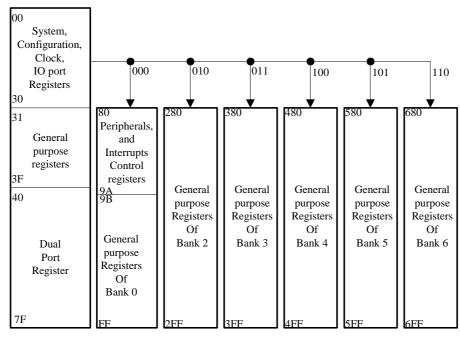

A total of 896 accessible bytes of data memory are available for the EM77950. By function, they are classified into general purpose registers, system control/configuration registers, specific purpose registers, Baseband (BB) control/status registers, SPI control/status registers, timer/counter registers, and IO port status/control registers. All of the mentioned registers except I/O ports and their related control registers are implemented as static RAM. The RAM configurations are shown in Fig. 6-2.

Fig. 6-2 of Data Memory (RAM) Configuration

EM77950 BB Controller

The table is a summary of all registers except general purpose registers.

| Addr  | Name  | Reset Type         | Bit 7      | Bit 6       | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1       | Bit 0     |

|-------|-------|--------------------|------------|-------------|------------|------------|------------|------------|-------------|-----------|

|       |       | Full Name          |            | Inc         | lirect Add | Iressing F | Register c | ontents    |             |           |

|       |       | Bit Name           | IAC07      | IAC06       | IAC05      | IAC04      | IAC03      | IAC02      | IAC01       | IAC00     |

| 0x00  | IAC0  | Read / Write (R/W) | R/W        | R/W         | R/W        | R/W        | R/W        | R/W        | R/W         | R/W       |

| 0x00  | IACU  | Power-on           | 0          | 0           | 0          | 0          | 0          | 0          | 0           | 0         |

|       |       | /RESET and WDT     | 0          | 0           | 0          | 0          | 0          | 0          | 0           | 0         |

|       |       | Wake-up from Int   | Р          | Р           | Р          | Р          | Р          | Р          | Р           | Р         |

|       |       | Full Name          |            | Most S      | ignificant | Byte of F  | rogramm    | ning Cour  | nter        |           |

|       |       | Bit Name           | PC7        | PC6         | PC5        | PC4        | PC3        | PC2        | PC1         | PC0       |

| 0x01  | HPC   | Read / Write (R/W) | R          | R           | R          | R          | R          | R          | R           | R         |

| 0x01  |       | Power-on           | 0          | 0           | 0          | 0          | 0          | 0          | 0           | 0         |

|       |       | /RESET and WDT     | 0          | 0           | 0          | 0          | 0          | 0          | 0           | 0         |

|       |       | Wake-up from Int   | Jump to co | rresponding | g interrup | t vector o | r continue | e to execu | ute next ir | struction |

|       |       | Full Name          |            | Least S     | ignificant | Byte of F  | Programn   | ning Cour  | nter        |           |

|       |       | Bit Name           | PCF        | PCE         | PCD        | PCC        | PCB        | PCA        | PC9         | PC8       |

| 0x02  | LPC   | Read / Write (R/W) | R/W        | R/W         | R/W        | R/W        | R/W        | R/W        | R/W         | R/W       |

| 0x02  | LPC   | Power-on           | 0          | 0           | 0          | 0          | 0          | 0          | 0           | 0         |

|       |       | /RESET and WDT     | 0          | 0           | 0          | 0          | 0          | 0          | 0           | 0         |

|       |       | Wake-up from Int   | Jump to co | rresponding | g interrup | t vector o | r continue | e to execu | ute next ir | struction |

|       |       | Full Name          |            |             | 5          | Status Re  | gister     |            |             |           |

|       |       | Bit Name           | -          | -           | RST        | Т          | Р          | Z          | DC          | С         |

| 0x03  | SR    | Read / Write (R/W) | -          | -           | R/W        | R/W        | R/W        | R/W        | R/W         | R/W       |

| 0.005 | SK -  | Power-on           | -          | -           | 0          | 1          | 1          | U          | U           | U         |

|       |       | /RESET and WDT     | -          | -           | Р          | Т          | Т          | Р          | Р           | Р         |

|       |       | Wake-up from Int   | -          | -           | Р          | Т          | Т          | Р          | Р           | Р         |

|       |       | Full Name          |            |             | RAM        | VI Bank S  | elector 0  |            |             |           |

|       |       | Bit Name           | -          | -           | -          | -          | -          | RBS02      | RBS01       | RBS00     |

| 0x04  | RAMBS | Read / Write (R/W) | -          | -           | -          | -          | -          | R          | R           | R         |

| 0x04  | 0     | Power-on           | -          | -           | -          | -          | -          | 0          | 0           | 0         |

|       |       | /RESET and WDT     | -          | -           | -          | -          | -          | 0          | 0           | 0         |

|       |       | Wake-up from Int   | -          | -           | -          | -          | -          | Р          | Р           | Р         |

|       |       | Full Name          |            |             | RC         | M Page     | Selector   |            |             |           |

|       |       | Bit Name           | -          | -           | -          | -          | -          | -          | -           | RPS0      |

| 0205  | ROMPS | Read / Write (R/W) | -          | -           | -          | -          | -          | -          | -           | R/W       |

| 0x05  | RUNPS | Power-on           | -          | -           | -          | -          | -          | -          | -           | 0         |

|       |       | /RESET and WDT     | -          | -           | -          | -          | -          | -          | -           | 0         |

|       |       | Wake-up from Int   | -          | -           | -          | -          | -          | -          | -           | Р         |

| Addr | Name      | Reset Type         | Bit 7 | Bit 6   | Bit 5      | Bit 4       | Bit 3      | Bit 2     | Bit 1    | Bit 0    |

|------|-----------|--------------------|-------|---------|------------|-------------|------------|-----------|----------|----------|

|      |           | Full Name          |       |         | Indire     | ect Addres  | ssing Poir | nter 0    |          |          |

|      |           | Bit Name           | IAP07 | IAP06   | IAP05      | IAP04       | IAP03      | IAP02     | IAP01    | IAP00    |

| 0x06 | IAP0      | Read / Write (R/W) | R/W   | R/W     | R/W        | R/W         | R/W        | R/W       | R/W      | R/W      |

| 0,00 | IAFU      | Power-on           | 0     | 0       | 0          | 0           | 0          | 0         | 0        | 0        |

|      |           | /RESET and WDT     | 0     | 0       | 0          | 0           | 0          | 0         | 0        | 0        |

|      |           | Wake-up from Int   | Р     | Р       | Р          | Р           | Р          | Р         | Р        | Р        |

|      |           | Full Name          |       |         | F          | RAM Bank    | Selector   | 1         |          |          |

|      |           | Bit Name           | -     | -       | -          | -           | -          | RBS12     | RBS11    | RBS10    |

| 0x07 | RAMBS1    | Read / Write (R/W) | -     | -       | -          | -           | -          | R/W       | R/W      | R/W      |

| 0.07 | RAIVIDS I | Power-on           | -     | -       | -          | -           | -          | 0         | 0        | 0        |

|      |           | /RESET and WDT     | -     | -       | -          | -           | -          | 0         | 0        | 0        |

|      |           | Wake-up from Int   | -     | -       | -          | -           | -          | Р         | Р        | Р        |

|      |           | Full Name          |       |         | Indire     | ect Addres  | ssing Poir | nter 1    |          |          |

|      |           | Bit Name           | IAP17 | IAP16   | IAP15      | IAP14       | IAP13      | IAP12     | IAP11    | IAP10    |

| 0x08 | IAP1      | Read / Write (R/W) | R/W   | R/W     | R/W        | R/W         | R/W        | R/W       | R/W      | R/W      |

| 0,00 |           | Power-on           | 0     | 0       | 0          | 0           | 0          | 0         | 0        | 0        |

|      |           | /RESET and WDT     | 0     | 0       | 0          | 0           | 0          | 0         | 0        | 0        |

|      |           | Wake-up from Int   | Р     | Р       | Р          | Р           | Р          | Р         | Р        | Р        |

|      |           | Full Name          |       |         | Indire     | ct Addres   | sing Cont  | ents 1    |          |          |

|      |           | Bit Name           | IAC17 | IAC16   | IAC15      | IAC14       | IAC13      | IAC12     | IAC11    | IAC10    |

| 0x09 | IAC1      | Read / Write (R/W) | R/W   | R/W     | R/W        | R/W         | R/W        | R/W       | R/W      | R/W      |

| 0,09 | IACT      | Power-on           | 0     | 0       | 0          | 0           | 0          | 0         | 0        | 0        |

|      |           | /RESET and WDT     | 0     | 0       | 0          | 0           | 0          | 0         | 0        | 0        |

|      |           | Wake-up from Int   | Р     | Р       | Р          | Р           | Р          | Р         | Р        | Р        |

|      |           | Full Name          |       | Indired | ct Address | s Pointer I | Direction  | Control R | egister  |          |

|      |           | Bit Name           | -     | -       | -          | -           | IAP1_D     | IAP0_D    | IAP1_D_E | IAP0_D_E |

| 0x0A | IAPDR     | Read / Write (R/W) | -     | -       | -          | -           | R/W        | R/W       | R/W      | R/W      |

| 0,07 |           | Power-on           | -     | -       | -          | -           | 0          | 0         | 0        | 0        |

|      |           | /RESET and WDT     | -     | -       | -          | -           | 0          | 0         | 0        | 0        |

|      |           | Wake-up from Int   | -     | -       | -          | -           | Р          | Р         | Р        | Р        |

|      |           | Full Name          |       | I       | _east Sigr | nificant By | te of Tabl | e Look-u  | C        |          |

|      |           | Bit Name           | TBL7  | TBL6    | TBL5       | TBL4        | TBL3       | TBL2      | TBL1     | TBL0     |

| 0x0B | LTBL      | Read / Write (R/W) | R/W   | R/W     | R/W        | R/W         | R/W        | R/W       | R/W      | R/W      |

| UXUB | LIBL      | Power-on           | 0     | 0       | 0          | 0           | 0          | 0         | 0        | 0        |

|      |           | /RESET and WDT     | 0     | 0       | 0          | 0           | 0          | 0         | 0        | 0        |

|      |           | Wake-up from Int   | Р     | Р       | Р          | Р           | Р          | Р         | Р        | Р        |

LAN

| Addr | Name   | Reset Type         | Bit 7  | Bit 6  | Bit 5  | Bit 4       | Bit 3     | Bit 2  | Bit 1     | Bit 0  |

|------|--------|--------------------|--------|--------|--------|-------------|-----------|--------|-----------|--------|

| Addi | Name   | Full Name          | Bit i  |        |        | nificant By |           |        |           | Bit V  |

|      |        | Bit Name           | TBLF   | TBLE   | TBLD   | TBLC        | TBLB      | TBLA   | ,<br>TBL9 | TBL8   |

|      |        | Read / Write (R/W) | R/W    | R/W    | R/W    | R/W         | R/W       | R/W    | R/W       | R/W    |

| 0x0C | HTBL   | Power-on           | 0      | 0      | 0      | 0           | 0         | 0      | 0         | 0      |

|      |        | /RESET and WDT     | 0      | 0      | 0      | 0           | 0         | 0      | 0         | 0      |

|      |        | Wake-up from Int   | P      | P      | P      | P           | P         | P      | P         | P      |

|      |        | Full Name          |        | •      | ·      |             | Pointer   |        |           | •      |

|      |        | Bit Name           | STKPT7 | STKPT6 | STKPT5 | STKPT4      |           | STKPT2 | STKPT1    | STKPT0 |

|      |        | Read / Write (R/W) | R      | R      | R      | R           | R         | R      | R         | R      |

| 0x0D | STKPTR | Power-on           | 1      | 1      | 1      | 1           | 1         | 1      | 1         | 1      |

|      |        | /RESET and WDT     | 1      | 1      | 1      | 1           | 1         | 1      | 1         | 1      |

|      |        | Wake-up from Int   | P      | P      | P      | P           | P         | P      | P         | P      |

|      |        | Full Name          | r      | I      | Г      |             | Pointer   |        | F         | r      |

|      |        | Bit Name           | RPTC7  | RPTC6  | RPTC5  | RPTC4       | RPTC3     | RPTC2  | RPTC1     | RPTC0  |

|      |        | Read / Write (R/W) | R/W    | R/W    | R/W    | R/W         | R/W       | R/W    | R/W       | R/W    |

| 0x0E | RPTC   | Power-on           | 0      | 0      | 0      | 0           | 0         | 0      | 0         | 0      |

|      |        | /RESET and WDT     | 0      | 0      | 0      | 0           | 0         | 0      | 0         | 0      |

|      |        | Wake-up from Int   | P      | P      | P      | P           | P         | P      | P         | P      |

|      |        | Full Name          | 1      |        | 1      | -           | r Counter | 1      | 1         | 1      |

|      |        | Bit Name           | PRC7   | PRC6   | PRC5   | PRC4        | PRC3      | PRC2   | PRC1      | PRC0   |

|      |        | Read / Write (R/W) | R/W    | R/W    | R/W    | R/W         | R/W       | R/W    | R/W       | R/W    |

| 0x0F | PRC    | Power-on           | 0      | 0      | 0      | 0           | 0         | 0      | 0         | 0      |

|      |        | /RESET and WDT     | 0      | 0      | 0      | 0           | 0         | 0      | 0         | 0      |

|      |        |                    | 0      | 0      | 0      | 0           | 0         | 0      | 0         | 0      |

|      |        | Wake-up from Int   | 0      | 0      | -      | -           | ũ         | -      | 0         | U      |

|      |        | Full Name          | T007   | TOOO   | 1      |             |           |        | TOOL      | TOOD   |

|      |        | Bit Name           | TCC7   | TCC6   | TCC5   | TCC4        | TCC3      | TCC2   | TCC1      | TCC0   |

| 0x10 | тсс    | Read / Write (R/W) | R/W    | R/W    | R/W    | R/W         | R/W       | R/W    | R/W       | R/W    |

|      |        | Power-on           | 0      | 0      | 0      | 0           | 0         | 0      | 0         | 0      |

|      |        | /RESET and WDT     | 0      | 0      | 0      | 0           | 0         | 0      | 0         | -      |

|      |        | Wake-up from Int   | 0      | 0      | 0      | -           | -         | 0      | 0         | 0      |

|      |        | Full Name          |        | DDEIE  |        | 1           | pt Flag   |        | TOOOF     | FDOOF  |

|      |        | Bit Name           | ADIF   | RBFIF  |        | PWM0IF      |           | EINTOF | TCCOF     | FRCOF  |

| 0x11 | INTF   | Read / Write (R/W) | R/W    | R/W    | R/W    | R/W         | R/W       | R/W    | R/W       | R/W    |

|      |        | Power-on           | 0      | 0      | 0      | 0           | 0         | 0      | 0         | 0      |

|      |        | /RESET and WDT     | 0      | 0      | 0      | 0           | 0         | 0      | 0         | 0      |

|      |        | Wake-up from Int   | Р      | Р      | Р      | Р           | Р         | Р      | Р         | Р      |

Bit 0

R/W

0

0

Ρ

R/W

0

0

Ρ

Bit 1

R/W

0

0

Ρ

R/W

0

0

Ρ

KWUBIF KWUAIF KWU9IF KWU8IF

KWU3IF KWU2IF KWU1IF KWU0IF

| 1 | E    | )<br>LAN |                    |        |        |          |           |               |          |

|---|------|----------|--------------------|--------|--------|----------|-----------|---------------|----------|

|   | Ψ    |          |                    |        |        |          |           |               |          |

|   | Addr | Name     | Reset Type         | Bit 7  | Bit 6  | Bit 5    | Bit 4     | Bit 3         | Bit 2    |

|   |      |          | Full Name          |        |        | Port A I | Key Wake  | up Interr     | upt Flag |

|   |      |          | Bit Name           | -      | -      | -        | -         | KWUBIF        | KWUAIF   |

|   | 0x12 | KWUAIF   | Read / Write (R/W) | -      | -      | -        | -         | R/W           | R/W      |

|   | 0.12 | NWOAII   | Power-on           | -      | -      | -        | -         | 0             | 0        |

|   |      |          | /RESET and WDT     | -      | -      | -        | -         | 0             | 0        |

|   |      |          | Wake-up from Int   | -      | -      | -        | -         | Р             | Р        |

|   |      |          | Full Name          |        |        | Port B I | Key Wake  | up Interr     | upt Flag |

|   |      |          | Bit Name           | KWU7IF | KWU6IF | KWU5IF   | KWU4IF    | <b>KWU3IF</b> | KWU2IF   |

|   | 0x13 | KWUBIF   | Read / Write (R/W) | R/W    | R/W    | R/W      | R/W       | R/W           | R/W      |

|   | 0.15 | RWOBI    | Power-on           | 0      | 0      | 0        | 0         | 0             | 0        |

|   |      |          | /RESET and WDT     | 0      | 0      | 0        | 0         | 0             | 0        |

|   |      |          | Wake-up from Int   | Р      | Р      | Р        | Р         | Р             | Р        |

|   |      |          | Full Name          |        |        | Genera   | al Purpos | e I/O port,   | Port A   |

|   |      |          | Bit Name           | PTA7   | PTA6   | PTA5     | PTA4      | PTA3          | PTA2     |

|   | 0x14 | РТА      | Read / Write (R/W) | R/W    | R/W    | R/W      | R/W       | R/W           | R/W      |

|   | 0,14 |          | Power-on           | U      | U      | U        | U         | U             | U        |

|   |      |          | /RESET and WDT     | U      | U      | U        | U         | U             | U        |

|   |      |          | Wake-up from Int   | Р      | Р      | Р        | Р         | Р             | Р        |

|   |      |          | Full Name          |        |        | Genera   | al Purpos | e I/O port,   | Port B   |

|   |      |          | Bit Name           | PTB7   | PTB6   | PTB5     | PTB4      | PTB3          | PTB2     |

~

|       |     | Bit Name           | PTA7 | PTA6 | PTA5   | PTA4       | PTA3        | PTA2   | PTA1 | PTA0 |

|-------|-----|--------------------|------|------|--------|------------|-------------|--------|------|------|

| 0x14  | ΡΤΑ | Read / Write (R/W) | R/W  | R/W  | R/W    | R/W        | R/W         | R/W    | R/W  | R/W  |

| UX 14 | PIA | Power-on           | U    | U    | U      | U          | U           | U      | U    | U    |

|       |     | /RESET and WDT     | U    | U    | U      | U          | U           | U      | U    | U    |

|       |     | Wake-up from Int   | Р    | Р    | Р      | Р          | Р           | Р      | Р    | Р    |

|       |     | Full Name          |      |      | Genera | al Purpose | e I/O port, | Port B |      |      |

|       |     | Bit Name           | PTB7 | PTB6 | PTB5   | PTB4       | PTB3        | PTB2   | PTB1 | PTB0 |

| 0x15  | РТВ | Read / Write (R/W) | R/W  | R/W  | R/W    | R/W        | R/W         | R/W    | R/W  | R/W  |

| 0x15  | PID | Power-on           | U    | U    | U      | U          | U           | U      | U    | U    |

|       |     | /RESET and WDT     | U    | U    | U      | U          | U           | U      | U    | U    |

|       |     | Wake-up from Int   | Р    | Р    | Р      | Р          | Р           | Р      | Р    | Р    |

|       |     | Full Name          |      |      | Genera | al Purpose | e I/O port, | Port C |      |      |

|       |     | Bit Name           | -    | -    | PTC5   | PTC4       | PTC3        | PTC2   | PTC1 | PTC0 |

| 0x16  | PTC | Read / Write (R/W) | -    | -    | R/W    | R/W        | R/W         | R/W    | R/W  | R/W  |

| 0210  | PIC | Power-on           | -    | -    | U      | U          | U           | U      | U    | U    |

|       |     | /RESET and WDT     | -    | -    | U      | U          | U           | U      | U    | U    |

|       |     | Wake-up from Int   | -    | -    | Р      | Р          | Р           | Р      | Р    | Р    |

|       |     | Full Name          |      |      | Genera | al Purpose | e I/O port, | Port D |      |      |

|       |     | Bit Name           | PTD7 | PTD6 | PTD5   | PTD4       | PTD3        | PTD2   | PTD1 | PTD0 |

| 0.17  | PTD | Read / Write (R/W) | R/W  | R/W  | R/W    | R/W        | R/W         | R/W    | R/W  | R/W  |

| 0x17  | PID | Power-on           | U    | U    | U      | U          | U           | U      | U    | U    |

|       |     | /RESET and WDT     | U    | U    | U      | U          | U           | U      | U    | U    |

|       |     | Wake-up from Int   | Р    | Р    | Р      | Р          | Р           | Р      | Р    | Р    |

| Addr | Name  | Reset Type         | Bit 7 | Bit 6       | Bit 5      | Bit 4      | Bit 3       | Bit 2     | Bit 1   | Bit 0 |

|------|-------|--------------------|-------|-------------|------------|------------|-------------|-----------|---------|-------|

|      |       | Full Name          | ·     |             | General    | Purpose    | I/O port,   | Port E    |         |       |

|      |       | Bit Name           | PTE7  | PTE6        | PTE5       | PTE4       | PTE3        | PTE2      | PTE1    | PTE0  |

| 0.40 | DTE   | Read / Write (R/W) | R/W   | R/W         | R/W        | R/W        | R/W         | R/W       | R/W     | R/W   |

| 0x18 | PTE   | Power-on           | U     | U           | U          | U          | U           | U         | U       | U     |

|      |       | /RESET and WDT     | U     | U           | U          | U          | U           | U         | U       | U     |

|      |       | Wake-up from Int   | Р     | Р           | Р          | Р          | Р           | Р         | Р       | Р     |

|      |       | Full Name          |       |             | General    | Purpose    | I/O port,   | Port F    |         |       |

|      |       | Bit Name           | -     | -           | -          | -          | -           | -         | PTF1    | PTF0  |

| 010  | DTE   | Read / Write (R/W) | -     | -           | -          | -          | -           | -         | R/W     | R/W   |

| 0x19 | PTF   | Power-on           | -     | -           | -          | -          | -           | -         | U       | U     |

|      |       | /RESET and WDT     | -     | -           | -          | -          | -           | -         | U       | U     |

|      |       | Wake-up from Int   | -     | -           | -          | -          | -           | -         | Р       | Р     |

|      |       | Full Name          |       | Least si    | ignificant | Byte of 1  | 6-bit Free  | Run Co    | unter   |       |

|      |       | Bit Name           | FRC7  | FRC6        | FRC5       | FRC4       | FRC3        | FRC2      | FRC1    | FRC0  |

| 0x1A | LFRC  | Read / Write (R/W) | R     | R           | R          | R          | R           | R         | R       | R     |

| UXIA | LFRG  | Power-on           | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | /RESET and WDT     | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | Wake-up from Int   | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | Full Name          |       | Most si     | gnificant  | Byte of 16 | 6-bit Free  | Run Cou   | unter   |       |

|      |       | Bit Name           | FRCF  | FRCE        | FRCD       | FRCC       | FRCB        | FRCA      | FRC9    | FRC8  |

| 0x1B | HFRC  | Read / Write (R/W) | R/W   | R/W         | R/W        | R/W        | R/W         | R/W       | R/W     | R/W   |

| UNID |       | Power-on           | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | /RESET and WDT     | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | Wake-up from Int   | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | Full Name          |       | Least signi | ficant Byt | e Buffer o | of 16-bit F | ree Run   | Counter |       |

|      |       | Bit Name           | FRCB7 | FRCB6       | FRCB5      | FRCB4      | FRCB3       | FRCB2     | FRCB1   | FRCB0 |

| 0x1C | LFRCB | Read / Write (R/W) | R/W   | R/W         | R/W        | R/W        | R/W         | R/W       | R/W     | R/W   |

| 0,10 | LINOD | Power-on           | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | /RESET and WDT     | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | Wake-up from Int   | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | Full Name          |       | Seri        | ial Periph | eral Inter | face Rea    | d Registe | er      |       |

|      |       | Bit Name           | SPIR7 | SPIR6       | SPIR5      | SPIR4      | SPIR3       | SPIR2     | SPIR1   | SPIR0 |

| 0x1D | SPIRB | Read / Write (R/W) | R/W   | R/W         | R/W        | R/W        | R/W         | R/W       | R/W     | R/W   |

| 0,10 |       | Power-on           | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | /RESET and WDT     | 0     | 0           | 0          | 0          | 0           | 0         | 0       | 0     |

|      |       | Wake-up from Int   | Р     | Р           | Р          | Р          | Р           | Р         | Р       | Р     |

| Addr   | Name   | Reset Type         | Bit 7 | Bit 6 | Bit 5      | Bit 4       | Bit 3      | Bit 2       | Bit 1 | Bit 0 |

|--------|--------|--------------------|-------|-------|------------|-------------|------------|-------------|-------|-------|

|        |        | Full Name          |       | S     | erial Peri | pheral Inte | erface Wr  | ite Registe | er    |       |

|        |        | Bit Name           | SPIW7 | SPIW6 | SPIW5      | SPIW4       | SPIW3      | SPIW2       | SPIW1 | SPIW0 |

| 0x1E   | SPIWB  | Read / Write (R/W) | R/W   | R/W   | R/W        | R/W         | R/W        | R/W         | R/W   | R/W   |

| UXIE   | SFIND  | Power-on           | 0     | 0     | 0          | 0           | 0          | 0           | 0     | 0     |

|        |        | /RESET and WDT     | 0     | 0     | 0          | 0           | 0          | 0           | 0     | 0     |

|        |        | Wake-up from Int   | Р     | Р     | Р          | Р           | Р          | Р           | Р     | Р     |

|        |        | Full Name          |       |       | Co         | nverting \  | /alue of A | DC          |       |       |

|        |        | Bit Name           | ADD7  | ADD6  | ADD5       | ADD4        | ADD3       | ADD2        | ADD1  | ADD0  |

| 0v1E   | ADDATA | Read / Write (R/W) | R/W   | R/W   | R/W        | R/W         | R/W        | R/W         | R/W   | R/W   |

| UXIF   | ADDATA | Power-on           | 0     | 0     | 0          | 0           | 0          | 0           | 0     | 0     |

|        |        | /RESET and WDT     | 0     | 0     | 0          | 0           | 0          | 0           | 0     | 0     |

|        |        | Wake-up from Int   | Р     | Р     | Р          | Р           | Р          | Р           | Р     | Р     |

|        |        | Full Name          |       |       |            |             |            |             |       |       |

|        |        | Bit Name           |       |       | -          | -           | -          | -           | -     | -     |

| 0x20   | NC     | Read / Write (R/W) | -     | -     | -          | -           | -          | -           | -     | -     |

| 0,20   | NC     | Power-on           | -     | -     | -          | -           | -          | -           | -     | -     |

|        |        | /RESET and WDT     | -     | -     | -          | -           | -          | -           | -     | -     |

|        |        | Wake-up from Int   | -     | -     | -          | -           | -          | -           | -     | -     |

|        |        | Full Name          |       |       | Du         | ity of PWI  | M0-Low B   | yte         |       |       |

|        |        | Bit Name           | DT07  | DT06  | DT05       | DT04        | DT03       | DT02        | DT01  | DT00  |

| 0x21   | DT0L   | Read / Write (R/W) | R     | R     | R          | R           | R          | R           | R     | R     |

| 0,72,1 | DIOL   | Power-on           | 0     | 0     | 0          | 0           | 0          | 0           | 0     | 0     |

|        |        | /RESET and WDT     | 0     | 0     | 0          | 0           | 0          | 0           | 0     | 0     |

|        |        | Wake-up from Int   | Р     | Р     | Р          | Р           | Р          | Р           | Р     | Р     |

|        |        | Full Name          |       |       | Du         | ty of PWN   | /10-High B | yte         |       |       |

|        |        | Bit Name           | DT0F  | DT0E  | DT0D       | DT0C        | DT0B       | DT0A        | DT09  | DT08  |

| 0x22   | DT0H   | Read / Write (R/W) | R     | R     | R          | R           | R          | R           | R     | R     |

| 0,22   | DIGH   | Power-on           | 0     | 0     | 0          | 0           | 0          | 0           | 0     | 0     |

|        |        | /RESET and WDT     | 0     | 0     | 0          | 0           | 0          | 0           | 0     | 0     |

|        |        | Wake-up from Int   | Р     | Р     | Р          | Р           | Р          | Р           | Р     | Р     |

|        |        | Full Name          |       |       | Peri       | od of PW    | M0- Low    | Byte        |       |       |

|        |        | Bit Name           | PRD07 | PRD06 | PRD05      | PRD04       | PRD03      | PRD02       | PRD01 | PRD00 |

| 0x23   | PRD0L  | Read / Write (R/W) | R/W   | R/W   | R/W        | R/W         | R/W        | R/W         | R/W   | R/W   |

| 0723   | PROUL  | Power-on           | 0     | 0     | 0          | 0           | 0          | 0           | 0     | 0     |

|        |        | /RESET and WDT     | 0     | 0     | 0          | 0           | 0          | 0           | 0     | 0     |

|        |        | Wake-up from Int   | Р     | Р     | Р          | Р           | Р          | Р           | Р     | Р     |

LAN

| Addr | Name  | Posot Typo                 | Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3             | Bit 2 | Bit 1 | Bit 0 |

|------|-------|----------------------------|-------|-------|-------|-----------|-------------------|-------|-------|-------|

| Addi | Name  | Reset Type                 | BIL 7 | ыго   |       |           |                   |       | ып т  | ыго   |

|      |       | Bit Name                   | PRD0F | PRD0E | PRD0D | PRD0C     | M0- High<br>PRD0B | -     | PRD09 | PRD08 |

|      |       |                            | R/W   | R/W   | R/W   | R/W       | R/W               | R/W   | R/W   | R/W   |

| 0x24 | PRD0H | Read / Write (R/W)         | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | Power-on<br>/RESET and WDT | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | Wake-up from Int           | P     | P     | P     | P         | P                 | P     | P     | P     |

|      |       | Full Name                  | Г     | Г     | -     |           |                   |       | Г     | Г     |

|      |       |                            |       |       | -     |           | WM0-Lov           | -     |       |       |

|      |       | Bit Name                   | DL07  | DL06  | DL05  | DL04      | DL03              | DL02  | DL01  | DL00  |

| 0x25 | DLOL  | Read / Write (R/W)         | R/W   | R/W   | R/W   | R/W       | R/W               | R/W   | R/W   | R/W   |

|      |       | Power-on                   | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | /RESET and WDT             | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | Wake-up from Int           | Р     | Р     | Р     | P         | Р                 | Р     | Р     | Р     |

|      |       | Full Name                  |       |       | -     |           | WM0-Hig           | -     |       |       |

|      |       | Bit Name                   | DL0F  | DL0E  | DL0D  | DL0C      | DL0B              | DL0A  | DL019 | DL08  |

| 0x26 | DL0H  | Read / Write (R/W)         | R/W   | R/W   | R/W   | R/W       | R/W               | R/W   | R/W   | R/W   |

|      |       | Power-on                   | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | /RESET and WDT             | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | Wake-up from Int           | Р     | Р     | Р     | Р         | Р                 | Р     | Р     | Р     |

|      |       | Full Name                  |       | 1     |       | -         | M1-Low B          |       |       |       |

|      |       | Bit Name                   | DT17  | DT16  | DT15  | DT14      | DT13              | DT12  | DT11  | DT10  |

| 0x27 | DT1L  | Read / Write (R/W)         | R     | R     | R     | R         | R                 | R     | R     | R     |

|      |       | Power-on                   | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | /RESET and WDT             | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | Wake-up from Int           | Р     | Р     | Р     | Р         | Р                 | Р     | Р     | Р     |

|      |       | Full Name                  |       | 1     | Du    | ty of PWN | /11-High B        | yte   |       |       |

|      |       | Bit Name                   | DT1F  | DT1E  | DT1D  | DT1C      | DT1B              | DT1A  | DT19  | DT18  |

| 0x28 | DT1H  | Read / Write (R/W)         | R     | R/    | R     | R         | R                 | R     | R     | R     |

| 0120 | Dim   | Power-on                   | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | /RESET and WDT             | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | Wake-up from Int           | Р     | Р     | Р     | Р         | Р                 | Р     | Р     | Р     |

|      |       | Full Name                  |       |       | Per   | iod of PW | M1- Low I         | Byte  |       |       |

|      |       | Bit Name                   | PRD17 | PRD16 | PRD15 | PRD14     | PRD13             | PRD12 | PRD1  | PRD10 |

| 0x29 | PRD1L | Read / Write (R/W)         | R/W   | R/W   | R/W   | R/W       | R/W               | R/W   | R/W   | R/W   |

| 0,29 |       | Power-on                   | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | /RESET and WDT             | 0     | 0     | 0     | 0         | 0                 | 0     | 0     | 0     |

|      |       | Wake-up from Int           | Р     | Р     | Р     | Р         | Р                 | Р     | Р     | Р     |

18 •

| Addr | Name  | Reset Type         | Bit 7 | Bit 6               | Bit 5   | Bit 4      | Bit 3      | Bit 2    | Bit 1 | Bit 0 |

|------|-------|--------------------|-------|---------------------|---------|------------|------------|----------|-------|-------|

|      |       | Full Name          |       |                     | Peri    | od of PWI  | M1- High   | Byte     |       |       |

|      |       | Bit Name           | PRD1F | PRD1E               | PRD1D   | PRD1C      | PRD1B      | PRD1A    | PRD19 | PRD18 |

| 0x2A | PRD1H | Read / Write (R/W) | R/W   | R/W                 | R/W     | R/W        | R/W        | R/W      | R/W   | R/W   |

| UXZA | FRDIN | Power-on           | 0     | 0                   | 0       | 0          | 0          | 0        | 0     | 0     |

|      |       | /RESET and WDT     | 0     | 0                   | 0       | 0          | 0          | 0        | 0     | 0     |

|      |       | Wake-up from Int   | Р     | Р                   | Р       | Р          | Р          | Р        | Р     | Р     |

|      |       | Full Name          |       |                     | Duty I  | Latch of P | WM1-Lov    | v Byte   |       |       |

|      |       | Bit Name           | DL17  | DL16                | DL15    | DL14       | DL13       | DL12     | DL11  | DL10  |

| 0x2B | DL1L  | Read / Write (R/W) | R/W   | R/W                 | R/W     | R/W        | R/W        | R/W      | R/W   | R/W   |

| UXZD | DLIL  | Power-on           | 0     | 0                   | 0       | 0          | 0          | 0        | 0     | 0     |

|      |       | /RESET and WDT     | 0     | 0                   | 0       | 0          | 0          | 0        | 0     | 0     |

|      |       | Wake-up from Int   | Р     | Р                   | Р       | Р          | Р          | Р        | Р     | Р     |

|      |       | Full Name          |       |                     | Duty L  | atch of P  | WM1-Hig    | h Byte   |       |       |

|      |       | Bit Name           | DL1F  | DL1E                | DL1D    | DL1C       | DL1B       | DL1A     | DL19  | DL18  |

| 0x2C | DL1H  | Read / Write (R/W) | R/W   | R/W                 | R/W     | R/W        | R/W        | R/W      | R/W   | R/W   |

| 0,20 | DLIII | Power-on           | 0     | 0                   | 0       | 0          | 0          | 0        | 0     | 0     |

|      |       | /RESET and WDT     | 0     | 0                   | 0       | 0          | 0          | 0        | 0     | 0     |