The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# SH7125 Group, SH7124 Group

Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family

> SH7125 R5F7125 SH7124 R5F7124

RenesasTechnology www.renesas.com

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com )

- Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below: (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

RENESAS

Rev. 3.00 Sep. 27, 2007 Page iii of xx

#### **General Precautions on Handling of Product**

- 1. Treatment of NC Pins

- Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

- 2. Treatment of Unused Input Pins

- Note: Fix all unused input pins to high or low level. Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a passthrough current flows internally, and a malfunction may occur.

- 3. Processing before Initialization

- Note: When power is first supplied, the product's state is undefined. The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

- 4. Prohibition of Access to Undefined or Reserved Addresses

- Note: Access to undefined or reserved addresses is prohibited. The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

## Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

## Preface

The SH7125 Group and SH7124 Group RISC (Reduced Instruction Set Computer) microcomputer include a Renesas Technology-original RISC CPU as its core, and the peripheral functions required to configure a system.

- Target Users: This manual was written for users who will be using the SH7125 Group and SH7124 Group in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

- Objective: This manual was written to explain the hardware functions and electrical characteristics of the SH7125 Group and SH7124 Group to the target users. Refer to the SH-1/SH-2/SH-DSP Software Manual for a detailed description of the instruction set.

Notes on reading this manual:

- In order to understand the overall functions of the chip Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions and electrical characteristics.

- In order to understand the details of the CPU's functions Read the SH-1/SH-2/SH-DSP Software Manual.

- In order to understand the details of a register when its name is known Read the index that is the final part of the manual to find the page number of the entry on the register. The addresses, bits, and initial values of the registers are summarized in section 20, List of Registers.

| Examples: | Register name:   | The following notation is used for cases when the same or a similar function, e.g. serial communication interface, is implemented on more than one channel:<br>XXX_N (XXX is the register name and N is the channel number) |

|-----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

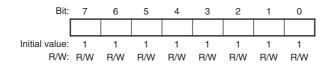

|           | Bit order:       | The MSB is on the left and the LSB is on the right.                                                                                                                                                                         |

|           | Number notation: | Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.                                                                                                                                                                   |

|           | Signal notation: | An overbar is added to a low-active signal: $\overline{xxxx}$                                                                                                                                                               |

Related Manuals: The latest versions of all related manuals are available from our web site. Please ensure you have the latest versions of all documents you require. http://www.renesas.com/

Rev. 3.00 Sep. 27, 2007 Page vi of xx

SH7125 Group and SH7124 Group manuals:

| Document Title                             | Document No. |

|--------------------------------------------|--------------|

| SH7125 Group, SH7124 Group Hardware Manual | This manual  |

| SH-1/SH-2/SH-DSP Software Manual           | REJ09B0171   |

User's manuals for development tools:

| Document Title                                                                                                                | Document No. |

|-------------------------------------------------------------------------------------------------------------------------------|--------------|

| SuperH <sup>™</sup> RISC engine C/C++ Compiler, Assembler,<br>Optimizing Linkage Editor Compiler Package V.9.00 User's Manual | REJ10B0152   |

| SuperH <sup>™</sup> RISC engine High-performance Embedded Workshop 3<br>User's Manual                                         | REJ10B0025   |

| SuperH RISC engine High-Performance Embedded Workshop 3 Tutorial                                                              | REJ10B0023   |

|                                                                                                                               |              |

Application note:

| Document Title                                             | Document No. |

|------------------------------------------------------------|--------------|

| SuperH RISC engine C/C++ Compiler Package Application Note | REJ05B0463   |

All trademarks and registered trademarks are the property of their respective owners.

Rev. 3.00 Sep. 27, 2007 Page viii of xx

## Contents

| Sect | ion 1   | Overview                          | 1  |

|------|---------|-----------------------------------|----|

| 1.1  | Featur  | res of SH7125 and SH7124          | 1  |

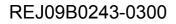

| 1.2  | Block   | Diagram                           | 6  |

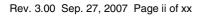

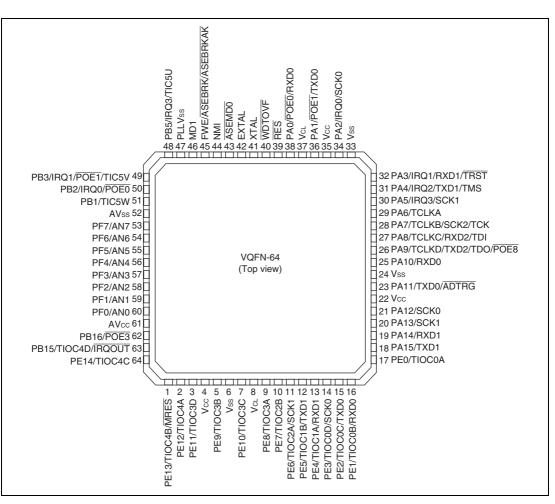

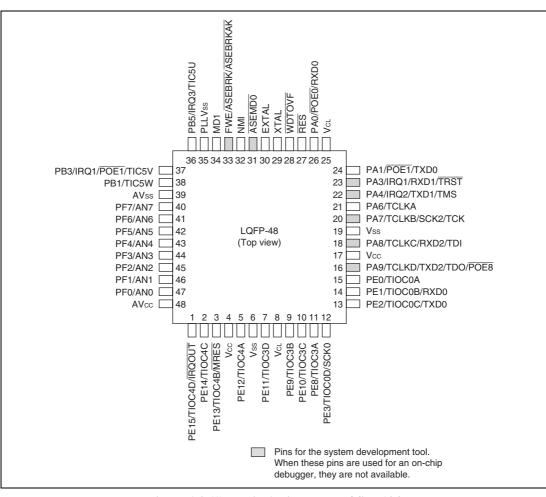

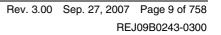

| 1.3  | Pin As  | ssignments                        | 7  |

| 1.4  | Pin Fu  | unctions                          |    |

| Sect | ion 2   | CPU                               | 17 |

| 2.1  | Featur  | 'es                               | 17 |

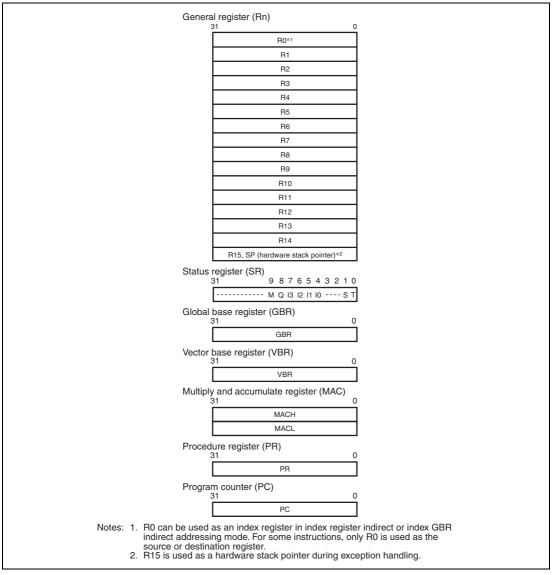

| 2.2  | Regist  | er Configuration                  |    |

|      | 2.2.1   | General Registers (Rn)            |    |

|      | 2.2.2   | Control Registers                 |    |

|      | 2.2.3   | System Registers                  |    |

|      | 2.2.4   | Initial Values of Registers       |    |

| 2.3  | Data F  | Formats                           |    |

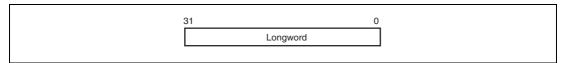

|      | 2.3.1   | Register Data Format              |    |

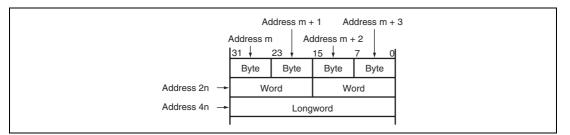

|      | 2.3.2   | Memory Data Formats               |    |

|      | 2.3.3   | Immediate Data Formats            |    |

| 2.4  | Featur  | es of Instructions                |    |

|      | 2.4.1   | RISC Type                         |    |

|      | 2.4.2   | Addressing Modes                  |    |

|      | 2.4.3   | Instruction Formats               |    |

| 2.5  | Instruc | ction Set                         |    |

|      | 2.5.1   | Instruction Set by Type           |    |

|      | 2.5.2   | Data Transfer Instructions        |    |

|      | 2.5.3   | Arithmetic Operation Instructions |    |

|      | 2.5.4   | Logic Operation Instructions      |    |

|      | 2.5.5   | Shift Instructions                |    |

|      | 2.5.6   | Branch Instructions               |    |

|      | 2.5.7   | System Control Instructions       |    |

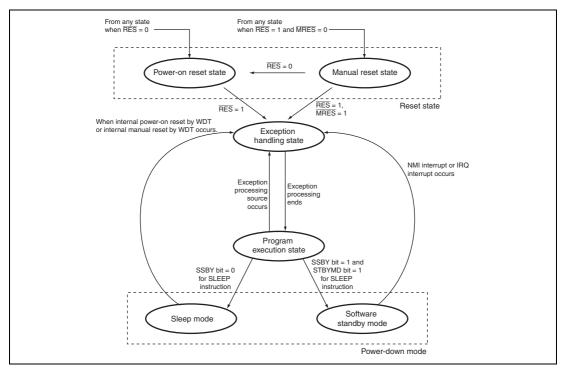

| 2.6  | Proces  | ssing States                      |    |

| Sect | ion 3   | MCU Operating Modes               | 49 |

| 3.1  |         | ion of Operating Modes            |    |

| 3.2  |         | Output Pins                       |    |

| 3.3  | -       | ting Modes                        |    |

|      | -       | Mode 3 (Single Chip Mode)         |    |

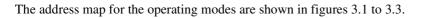

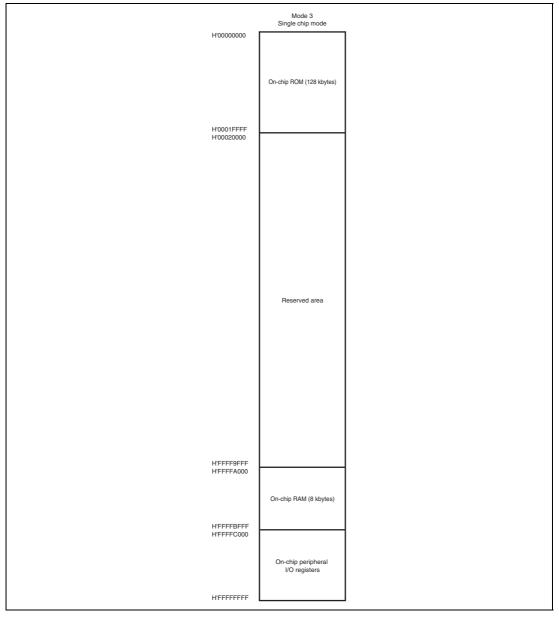

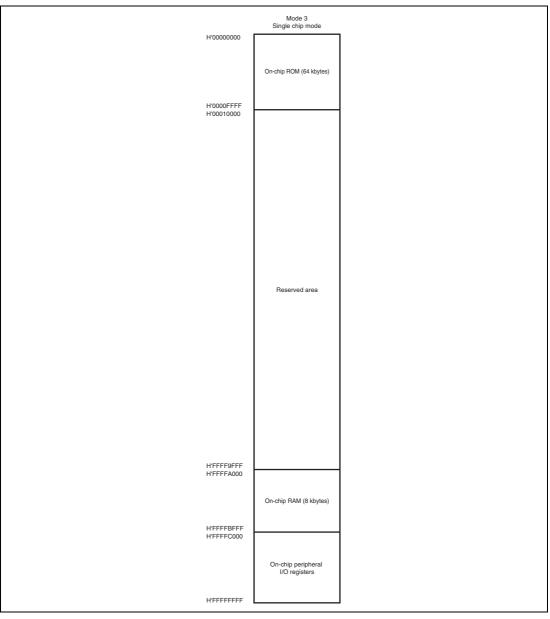

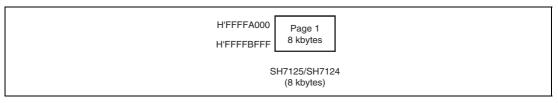

| 3.4   | Address  | 5 Map                                               | . 51 |

|-------|----------|-----------------------------------------------------|------|

| 3.5   |          | tate in This LSI                                    |      |

| 3.6   | Note on  | Changing Operating Mode                             | . 54 |

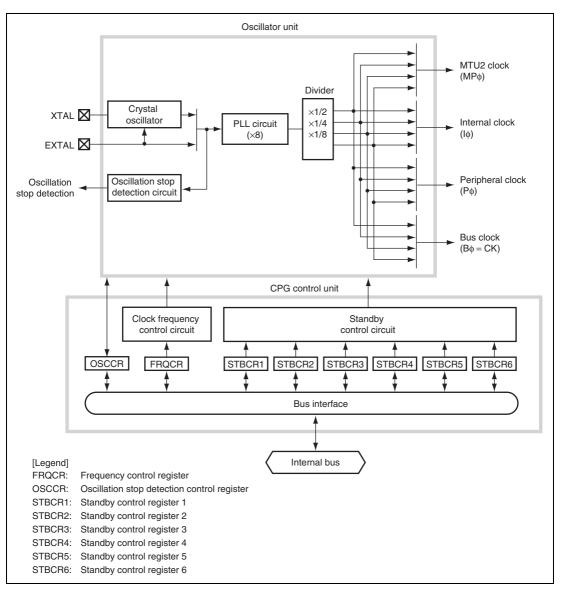

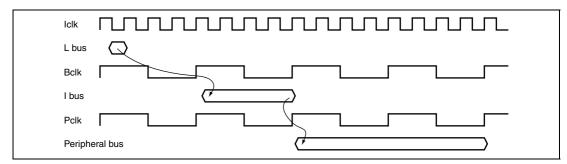

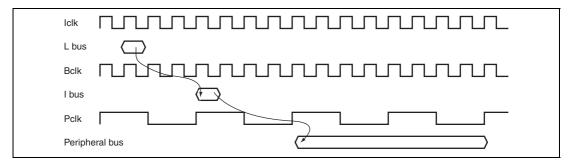

| Secti | on 4 C   | Clock Pulse Generator (CPG)                         | 55   |

| 4.1   | Feature  | S                                                   | . 55 |

| 4.2   | Input/O  | utput Pins                                          | . 58 |

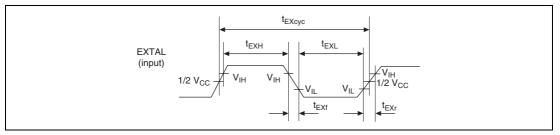

| 4.3   | Clock C  | Derating Mode                                       | . 59 |

| 4.4   | Register | r Descriptions                                      | . 61 |

|       | 4.4.1    | Frequency Control Register (FRQCR)                  | . 61 |

|       | 4.4.2    | Oscillation Stop Detection Control Register (OSCCR) | . 64 |

| 4.5   | Changir  | ng Frequency                                        | . 65 |

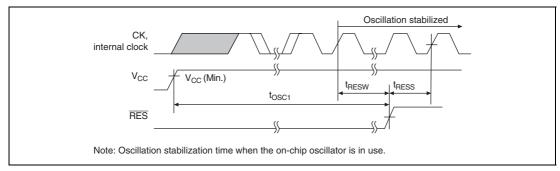

| 4.6   | Oscillat | or                                                  | . 66 |

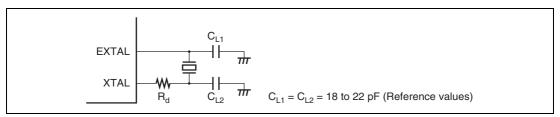

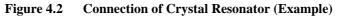

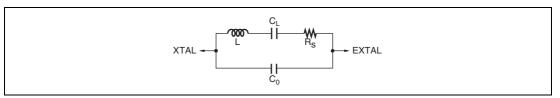

|       | 4.6.1    | Connecting Crystal Resonator                        | . 66 |

|       | 4.6.2    | External Clock Input Method                         | . 67 |

| 4.7   |          | n for Detecting Oscillator Stop                     |      |

| 4.8   | Usage N  | Notes                                               | . 69 |

|       | 4.8.1    | Note on Crystal Resonator                           | . 69 |

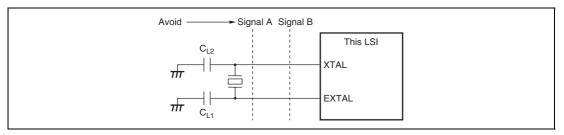

|       | 4.8.2    | Notes on Board Design                               | . 69 |

|       |          |                                                     |      |

| Secti |          | Exception Handling                                  |      |

| 5.1   |          | W                                                   |      |

|       | 5.1.1    | Types of Exception Handling and Priority            |      |

|       | 5.1.2    | Exception Handling Operations                       |      |

|       | 5.1.3    | Exception Handling Vector Table                     |      |

| 5.2   |          |                                                     |      |

|       | 5.2.1    | Types of Resets                                     |      |

|       | 5.2.2    | Power-On Reset                                      |      |

|       | 5.2.3    | Manual Reset                                        |      |

| 5.3   |          | s Errors                                            |      |

|       | 5.3.1    | Address Error Sources                               |      |

|       | 5.3.2    | Address Error Exception Source                      |      |

| 5.4   | -        | ts                                                  |      |

|       | 5.4.1    | Interrupt Sources                                   |      |

|       | 5.4.2    | Interrupt Priority                                  |      |

|       | 5.4.3    | Interrupt Exception Handling                        |      |

| 5.5   | -        | ons Triggered by Instructions                       |      |

|       | 5.5.1    | Types of Exceptions Triggered by Instructions       |      |

|       | 5.5.2    | Trap Instructions                                   |      |

|       | 5.5.3    | Illegal Slot Instructions                           | . 82 |

|      | 5.5.4   | General Illegal Instructions                                           | 82  |

|------|---------|------------------------------------------------------------------------|-----|

| 5.6  | Cases   | when Exceptions are Accepted                                           | 83  |

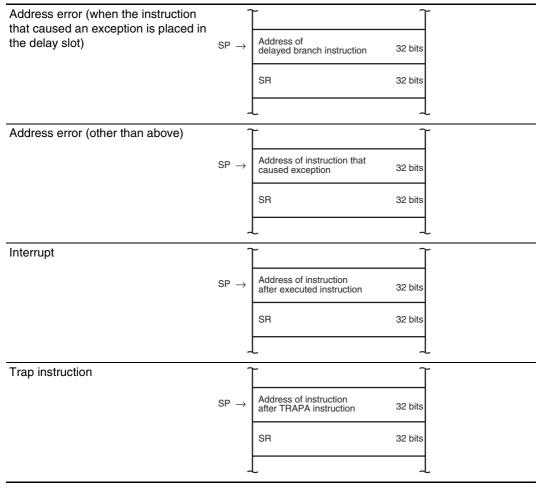

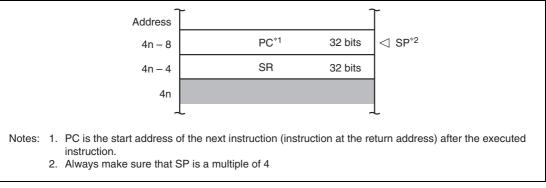

| 5.7  | Stack   | States after Exception Handling Ends                                   | 84  |

| 5.8  | Usage   | Notes                                                                  | 86  |

|      | 5.8.1   | Value of Stack Pointer (SP)                                            | 86  |

|      | 5.8.2   | Value of Vector Base Register (VBR)                                    | 86  |

|      | 5.8.3   | Address Errors Caused by Stacking for Address Error Exception Handling | 86  |

|      | 5.8.4   | Notes on Slot Illegal Instruction Exception Handling                   | 87  |

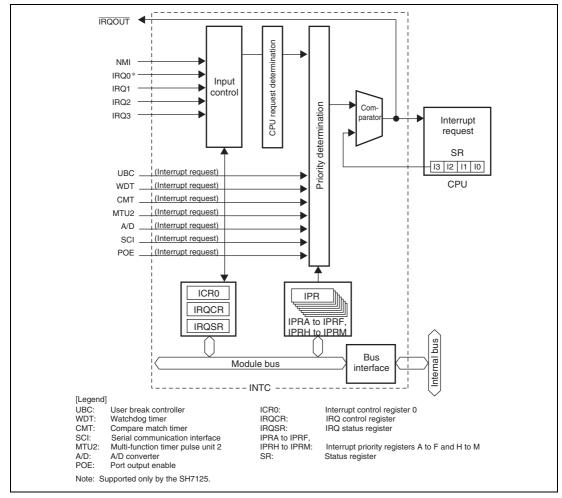

| Sect | ion 6   | Interrupt Controller (INTC)                                            | 89  |

| 6.1  | Featur  | 'es                                                                    |     |

| 6.2  | Input/  | Output Pins                                                            | 91  |

| 6.3  | Regist  | er Descriptions                                                        | 92  |

|      | 6.3.1   | Interrupt Control Register 0 (ICR0)                                    | 93  |

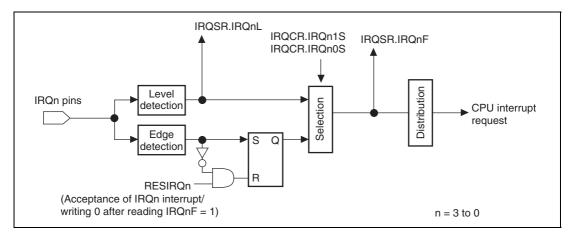

|      | 6.3.2   | IRQ Control Register (IRQCR)                                           | 94  |

|      | 6.3.3   | IRQ Status register (IRQSR)                                            | 96  |

|      | 6.3.4   | Interrupt Priority Registers A to F and H to M                         |     |

|      |         | (IPRA to IPRF and IPRH to IPRM)                                        | 99  |

| 6.4  | Interru | ıpt Sources                                                            | 102 |

|      | 6.4.1   | External Interrupts                                                    | 102 |

|      | 6.4.2   | On-Chip Peripheral Module Interrupts                                   | 103 |

|      | 6.4.3   | User Break Interrupt                                                   | 103 |

| 6.5  | Interru | pt Exception Handling Vector Table                                     | 104 |

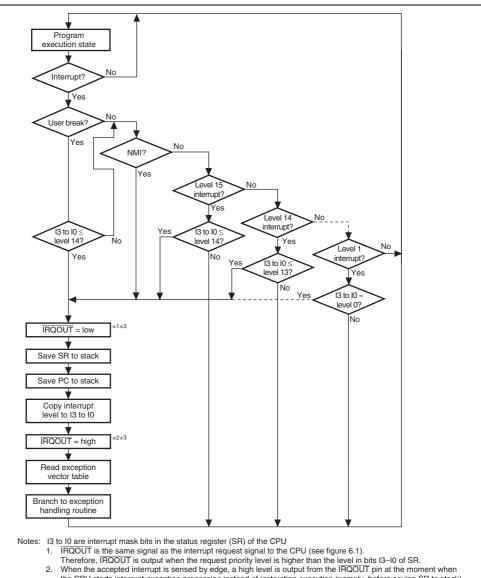

| 6.6  | Interru | pt Operation                                                           | 107 |

|      | 6.6.1   | Interrupt Sequence                                                     | 107 |

|      | 6.6.2   | Stack after Interrupt Exception Handling                               | 110 |

| 6.7  | Interru | pt Response Time                                                       | 110 |

| 6.8  | Usage   | Note                                                                   | 112 |

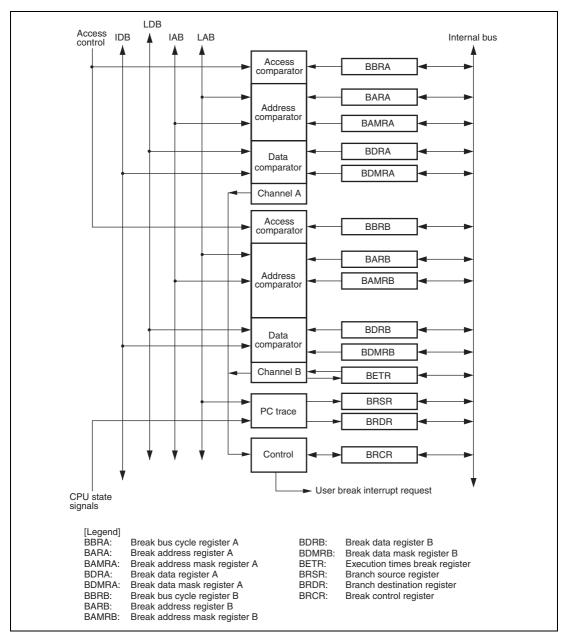

| Sect | ion 7   | User Break Controller (UBC)                                            | 113 |

| 7.1  |         | 'es                                                                    |     |

| 7.2  | Regist  | er Descriptions                                                        | 115 |

|      | 7.2.1   | Break Address Register A (BARA)                                        | 116 |

|      | 7.2.2   | Break Address Mask Register A (BAMRA)                                  | 116 |

|      | 7.2.3   | Break Bus Cycle Register A (BBRA)                                      | 117 |

|      | 7.2.4   | Break Data Register A (BDRA)                                           |     |

|      | 7.2.5   | Break Data Mask Register A (BDMRA)                                     |     |

|      | 7.2.6   | Break Address Register B (BARB)                                        | 121 |

|      | 7.2.7   | Break Address Mask Register B (BAMRB)                                  |     |

|      | 7.2.8   | Break Data Register B (BDRB)                                           | 123 |

|      |         |                                                                        |     |

|                                                               | 7.2.9                                                                                                                                   | Break Data Mask Register B (BDMRB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                                               | 7.2.10                                                                                                                                  | Break Bus Cycle Register B (BBRB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |

|                                                               | 7.2.11                                                                                                                                  | Break Control Register (BRCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

|                                                               | 7.2.12                                                                                                                                  | Execution Times Break Register (BETR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

|                                                               | 7.2.13                                                                                                                                  | Branch Source Register (BRSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

|                                                               | 7.2.14                                                                                                                                  | Branch Destination Register (BRDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| 7.3                                                           | Operati                                                                                                                                 | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

|                                                               | 7.3.1                                                                                                                                   | Flow of the User Break Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

|                                                               | 7.3.2                                                                                                                                   | Break on Instruction Fetch Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

|                                                               | 7.3.3                                                                                                                                   | Break on Data Access Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |

|                                                               | 7.3.4                                                                                                                                   | Sequential Break                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

|                                                               | 7.3.5                                                                                                                                   | Value of Saved Program Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

|                                                               | 7.3.6                                                                                                                                   | PC Trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                       |

|                                                               | 7.3.7                                                                                                                                   | Usage Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| 7.4                                                           | Usage                                                                                                                                   | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

| Secti                                                         | on 8                                                                                                                                    | Bus State Controller (BSC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 147                                                                                                   |

| 8.1                                                           |                                                                                                                                         | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |

| 8.2                                                           |                                                                                                                                         | s Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

|                                                               |                                                                                                                                         | to on-chip FLASH and on-chip RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

| 8.3                                                           | ALLOS                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                       |

| 8.3<br>8.4                                                    |                                                                                                                                         | to on-chip Peripheral I/O Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| 8.4                                                           | Access                                                                                                                                  | to on-chip Peripheral I/O Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| 8.4<br>Secti                                                  | Access                                                                                                                                  | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| 8.4<br>Secti<br>9.1                                           | Access<br>on 9                                                                                                                          | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| 8.4<br>Secti                                                  | Access<br>on 9                                                                                                                          | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)<br>s<br>Dutput Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9 D<br>Feature<br>Input/C<br>Registe                                                                                       | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)<br>s<br>Dutput Pins<br>r Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9<br>Feature<br>Input/C<br>Registe<br>9.3.1                                                                                | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)<br>s<br>Dutput Pins<br>r Descriptions<br>Timer Control Register (TCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9 D<br>Feature<br>Input/C<br>Registe                                                                                       | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)<br>s<br>Dutput Pins<br>r Descriptions<br>Timer Control Register (TCR)<br>Timer Mode Register (TMDR)                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9<br>Feature<br>Input/C<br>Registe<br>9.3.1<br>9.3.2                                                                       | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)<br>s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 148<br>151<br>151<br>157<br>158<br>162<br>166<br>169                                                  |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9<br>Feature<br>Input/C<br>Registe<br>9.3.1<br>9.3.2<br>9.3.3                                                              | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)<br>s<br>Dutput Pins<br>r Descriptions<br>Timer Control Register (TCR)<br>Timer Mode Register (TMDR)                                                                                                                                                                                                                                                                                                                                                                                                                               | 148<br>151<br>151<br>157<br>158<br>162<br>166<br>169<br>188                                           |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9<br>Feature<br>Input/C<br>Registe<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4                                                     | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)<br>ss<br>Dutput Pins<br>r Descriptions<br>Timer Control Register (TCR)<br>Timer Mode Register (TMDR)<br>Timer I/O Control Register (TIOR)<br>Timer Compare Match Clear Register (TCNTCMPCLR)                                                                                                                                                                                                                                                                                                                                      | 148<br>151<br>151<br>157<br>158<br>162<br>166<br>169<br>188<br>189                                    |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9 1<br>Feature<br>Input/C<br>Registe<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5                                          | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)<br>Support Pins<br>r Descriptions<br>Timer Control Register (TCR)<br>Timer Mode Register (TMDR)<br>Timer I/O Control Register (TIOR)<br>Timer Compare Match Clear Register (TCNTCMPCLR)<br>Timer Interrupt Enable Register (TIER)                                                                                                                                                                                                                                                                                                 | 148<br>151<br>151<br>157<br>158<br>162<br>166<br>169<br>188<br>189<br>194                             |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9<br>Feature<br>Input/C<br>Registe<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6                                   | to on-chip Peripheral I/O Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 148<br>151<br>151<br>157<br>158<br>162<br>166<br>166<br>169<br>188<br>189<br>194<br>202               |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9<br>Feature<br>Input/C<br>Registe<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>9.3.7                          | to on-chip Peripheral I/O Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 148<br>151<br>151<br>157<br>158<br>162<br>166<br>169<br>188<br>189<br>194<br>202<br>203               |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9 Feature<br>Input/C<br>Registe<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>9.3.7<br>9.3.8                    | to on-chip Peripheral I/O Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 148<br>151<br>151<br>157<br>158<br>162<br>166<br>169<br>188<br>189<br>194<br>202<br>203               |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9 E<br>Feature<br>Input/C<br>Registe<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>9.3.7<br>9.3.8<br>9.3.9      | to on-chip Peripheral I/O Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 148<br>151<br>151<br>157<br>158<br>162<br>166<br>169<br>188<br>189<br>194<br>202<br>203<br>205        |

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9 E<br>Feature<br>Input/C<br>Registe<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>9.3.7<br>9.3.8<br>9.3.9      | to on-chip Peripheral I/O Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 148<br>151<br>151<br>157<br>158<br>162<br>166<br>169<br>188<br>189<br>194<br>202<br>203<br>205        |

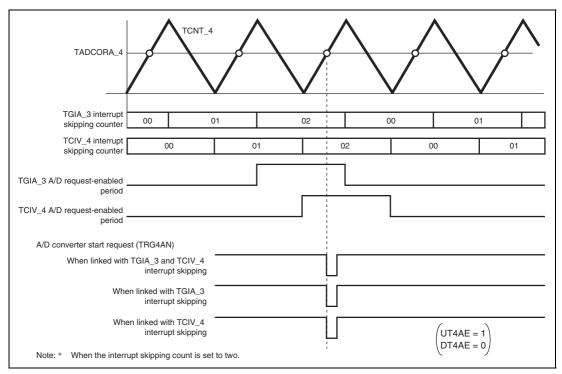

| <ul><li>8.4</li><li>Section</li><li>9.1</li><li>9.2</li></ul> | Access<br>on 9 Feature<br>Input/C<br>Registe<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>9.3.7<br>9.3.8<br>9.3.9<br>9.3.10 | to on-chip Peripheral I/O Register<br>Multi-Function Timer Pulse Unit 2 (MTU2)<br>ss<br>Dutput Pins<br>r Descriptions<br>Timer Control Register (TCR)<br>Timer Mode Register (TMDR)<br>Timer I/O Control Register (TIOR)<br>Timer Compare Match Clear Register (TCNTCMPCLR)<br>Timer Interrupt Enable Register (TIER)<br>Timer Status Register (TSR)<br>Timer Buffer Operation Transfer Mode Register (TBTM)<br>Timer Input Capture Control Register (TICCR)<br>Timer A/D Converter Start Request Control Register (TADCR)<br>Timer A/D CONVERTER Start Request Cycle Set Registers<br>(TADCORA_4 and TADCORB_4) | 148<br>151<br>151<br>157<br>158<br>162<br>166<br>169<br>188<br>189<br>194<br>202<br>203<br>205<br>208 |

|     | 9.3.13  | Timer General Register (TGR)                                       | 209 |

|-----|---------|--------------------------------------------------------------------|-----|

|     | 9.3.14  | Timer Start Register (TSTR)                                        | 210 |

|     | 9.3.15  | Timer Synchronous Register (TSYR)                                  | 212 |

|     | 9.3.16  | Timer Counter Synchronous Start Register (TCSYSTR)                 | 214 |

|     | 9.3.17  | Timer Read/Write Enable Register (TRWER)                           | 216 |

|     | 9.3.18  | Timer Output Master Enable Register (TOER)                         | 217 |

|     | 9.3.19  | Timer Output Control Register 1 (TOCR1)                            | 218 |

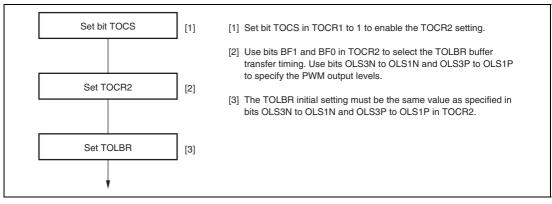

|     | 9.3.20  | Timer Output Control Register 2 (TOCR2)                            | 221 |

|     | 9.3.21  | Timer Output Level Buffer Register (TOLBR)                         | 224 |

|     | 9.3.22  | Timer Gate Control Register (TGCR)                                 | 225 |

|     | 9.3.23  | Timer Subcounter (TCNTS)                                           | 227 |

|     | 9.3.24  | Timer Dead Time Data Register (TDDR)                               | 228 |

|     | 9.3.25  | Timer Cycle Data Register (TCDR)                                   | 228 |

|     | 9.3.26  | Timer Cycle Buffer Register (TCBR)                                 | 229 |

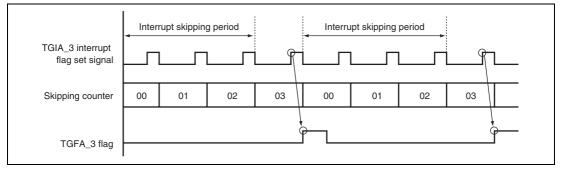

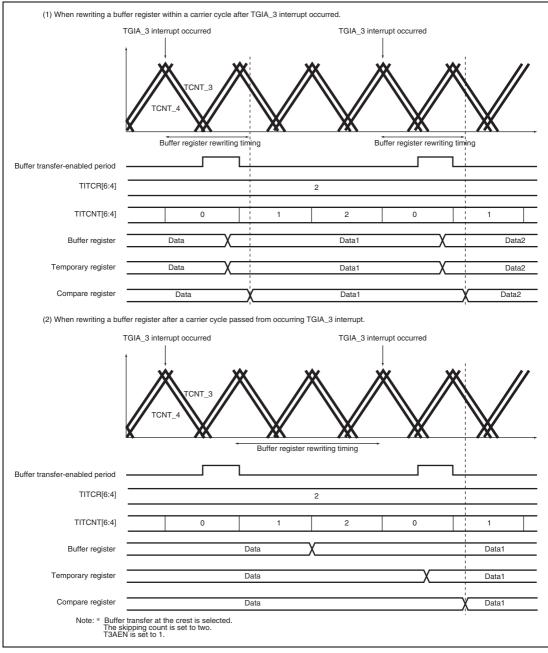

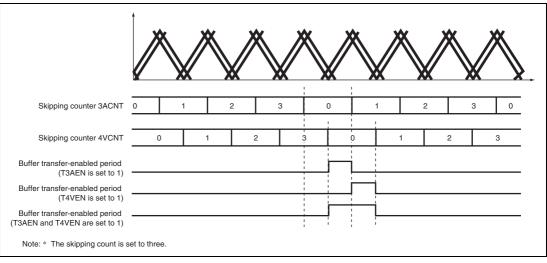

|     | 9.3.27  | Timer Interrupt Skipping Set Register (TITCR)                      | 229 |

|     | 9.3.28  | Timer Interrupt Skipping Counter (TITCNT)                          | 231 |

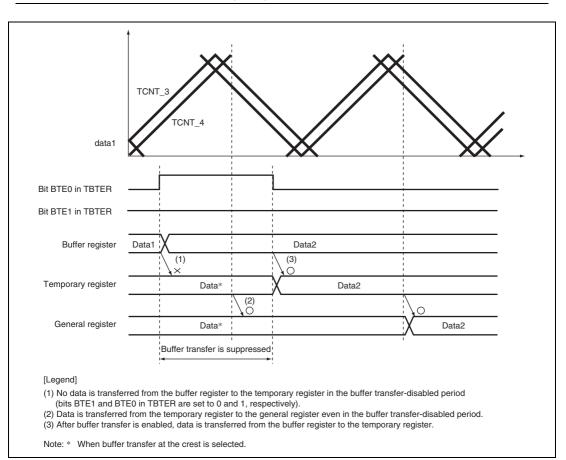

|     | 9.3.29  | Timer Buffer Transfer Set Register (TBTER)                         | 232 |

|     | 9.3.30  | Timer Dead Time Enable Register (TDER)                             | 234 |

|     | 9.3.31  | Timer Waveform Control Register (TWCR)                             | 235 |

|     | 9.3.32  | Bus Master Interface                                               | 236 |

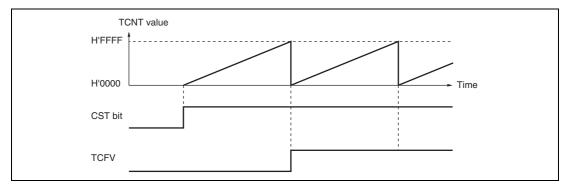

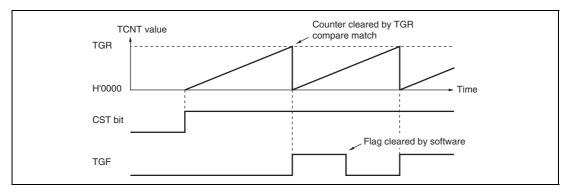

| 9.4 | Operati | ion                                                                | 237 |

|     | 9.4.1   | Basic Functions                                                    | 237 |

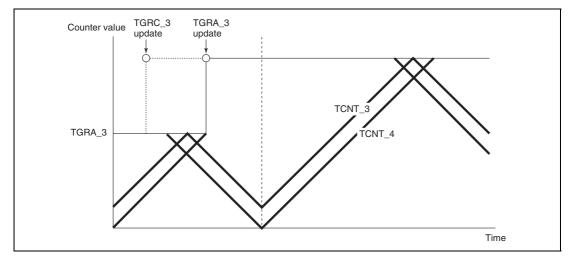

|     | 9.4.2   | Synchronous Operation                                              | 243 |

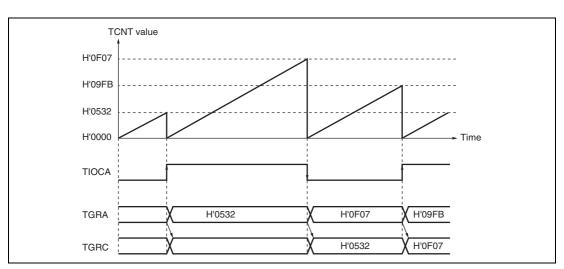

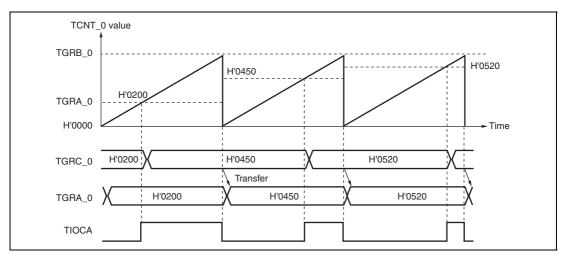

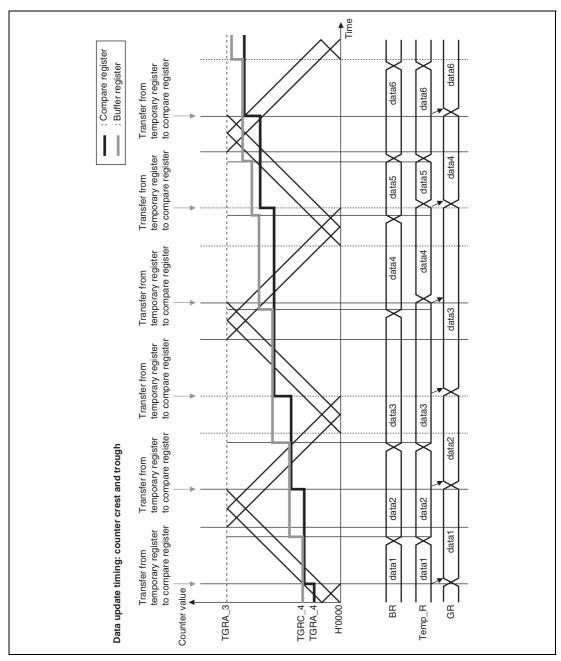

|     | 9.4.3   | Buffer Operation                                                   | 245 |

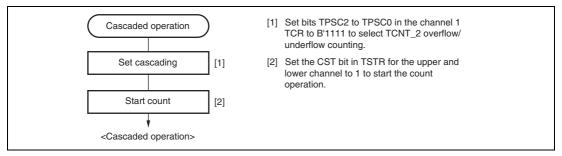

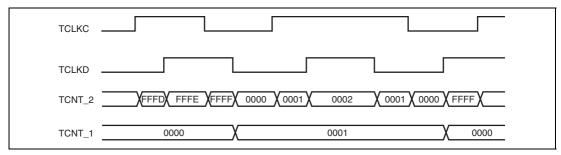

|     | 9.4.4   | Cascaded Operation                                                 | 249 |

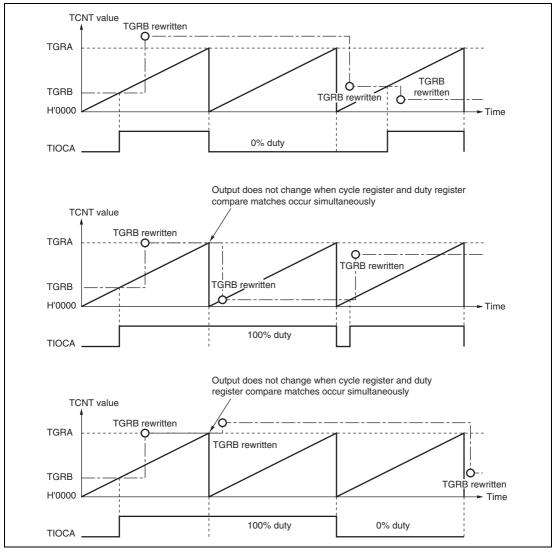

|     | 9.4.5   | PWM Modes                                                          | 254 |

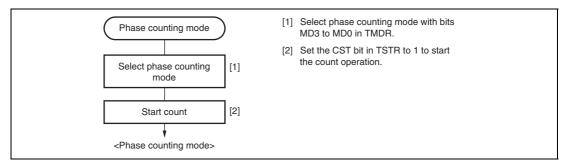

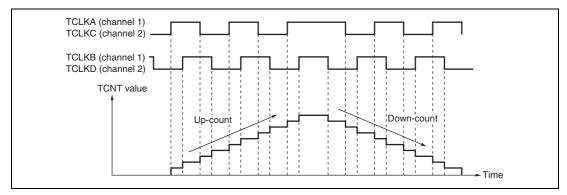

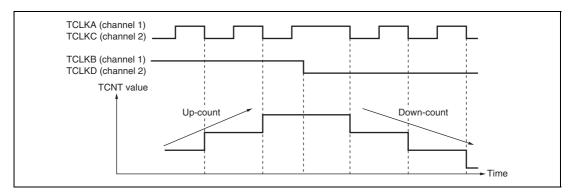

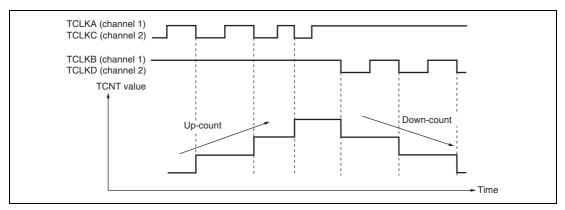

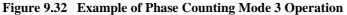

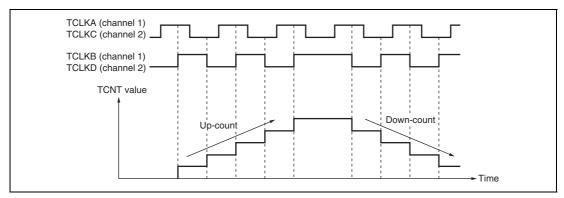

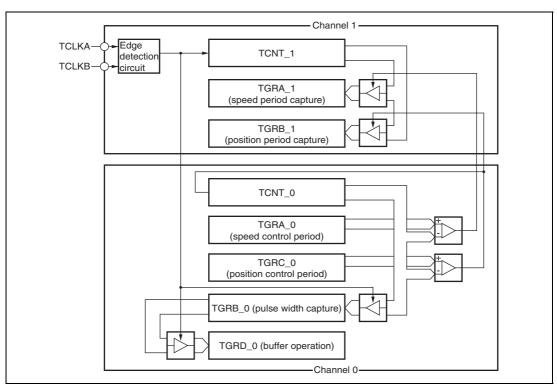

|     | 9.4.6   | Phase Counting Mode                                                | 259 |

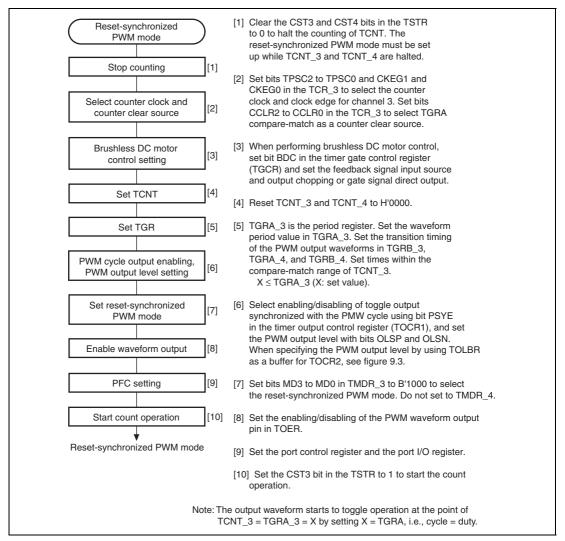

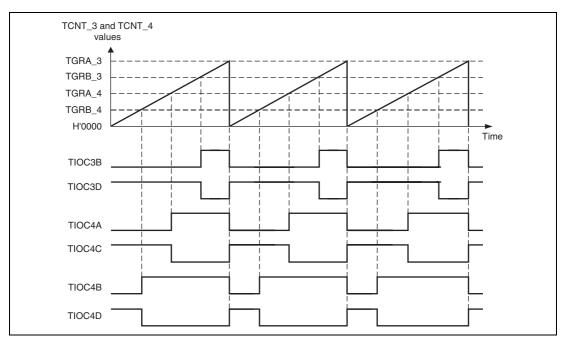

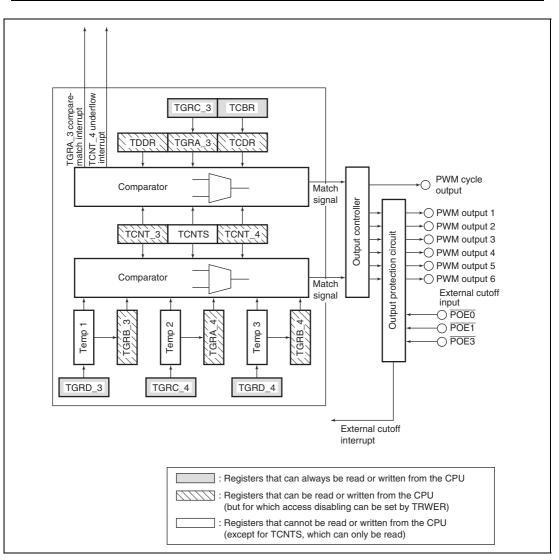

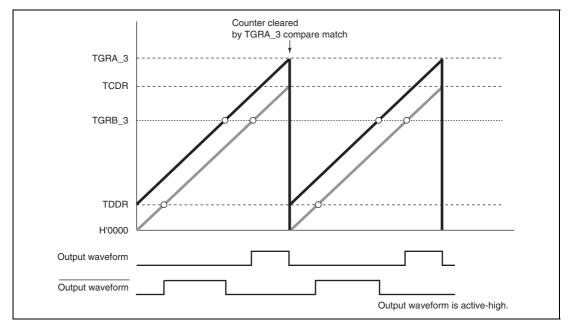

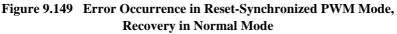

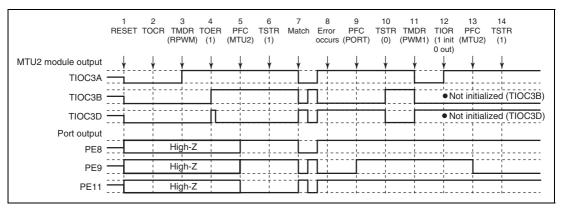

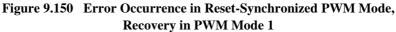

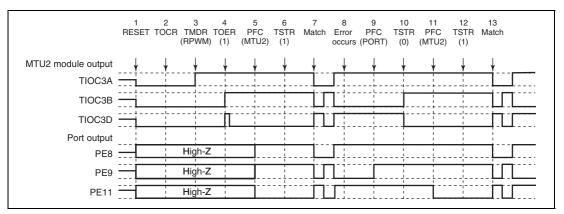

|     | 9.4.7   | Reset-Synchronized PWM Mode                                        | 266 |

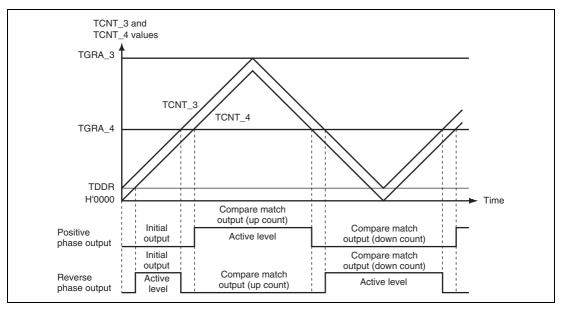

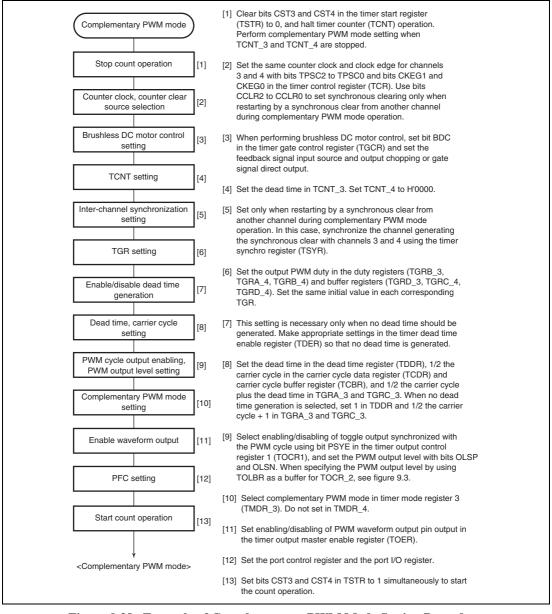

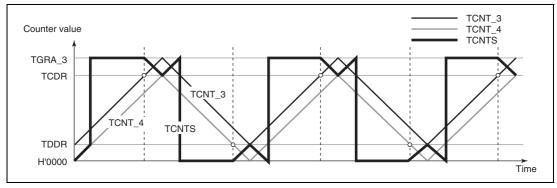

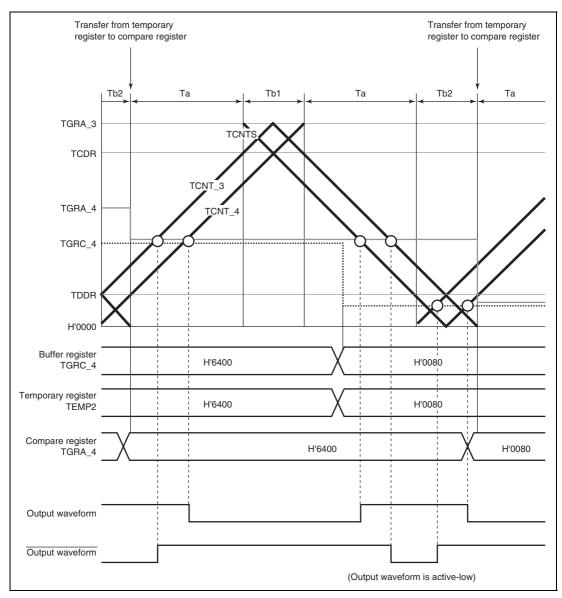

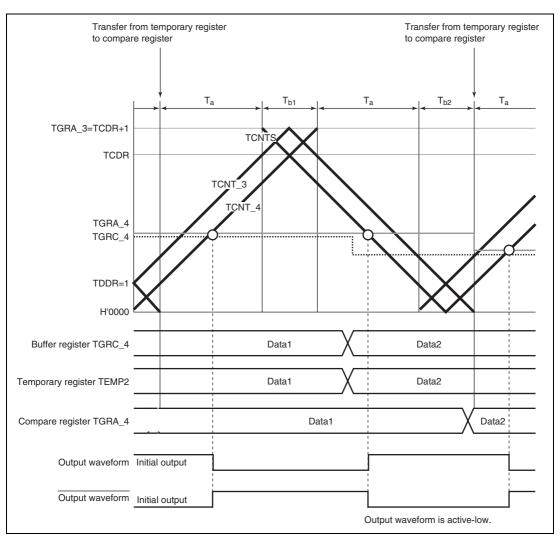

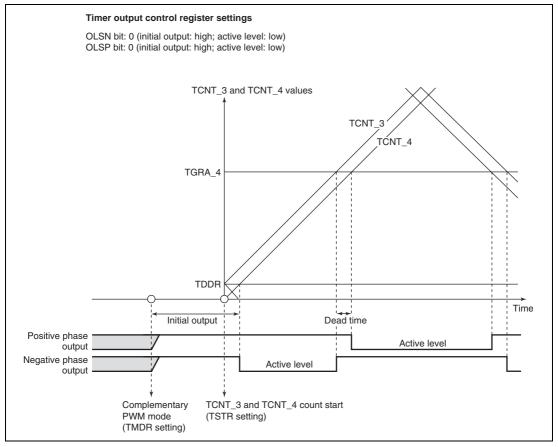

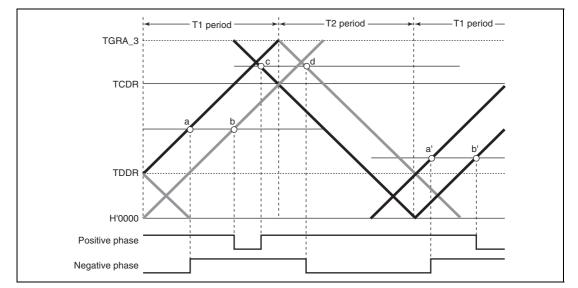

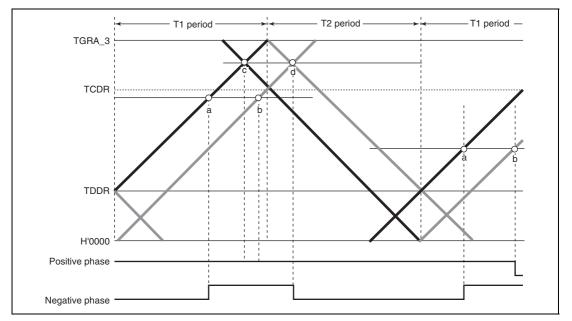

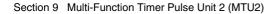

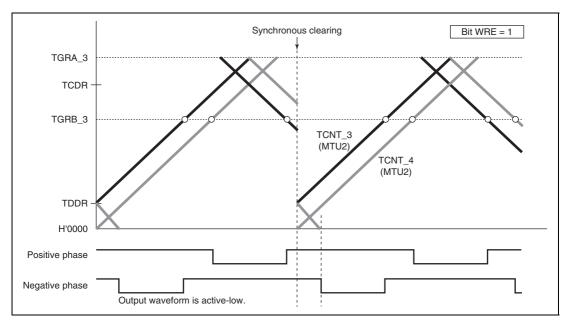

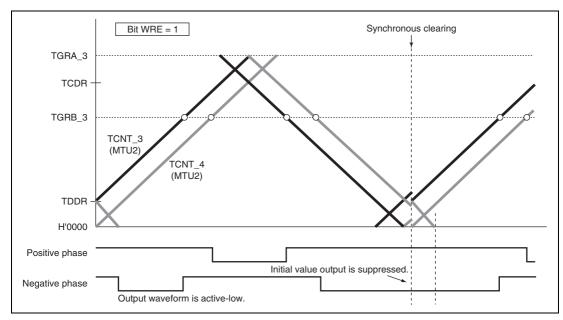

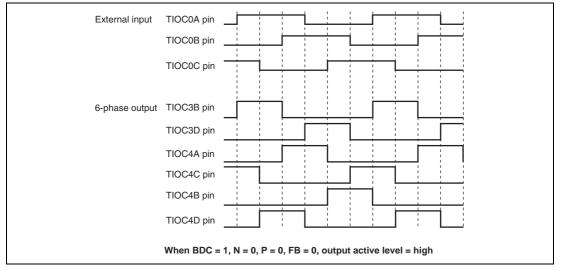

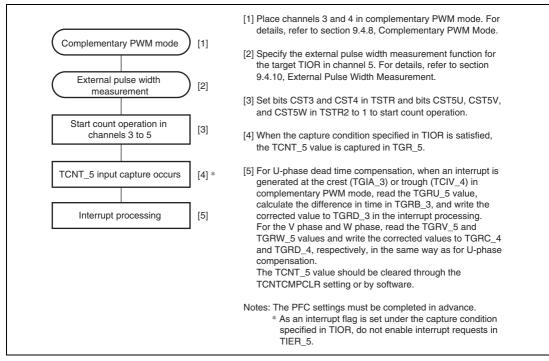

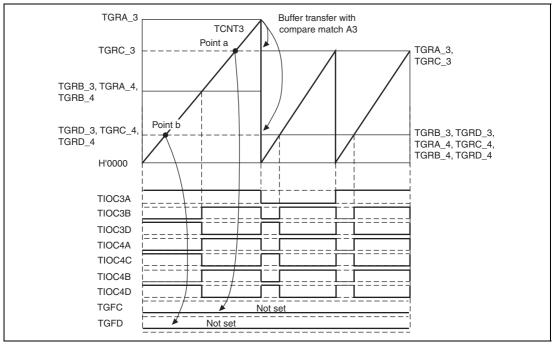

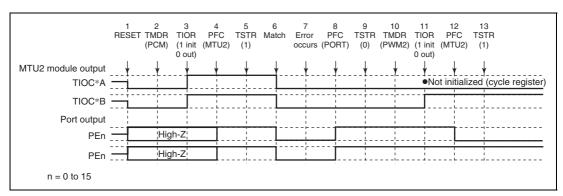

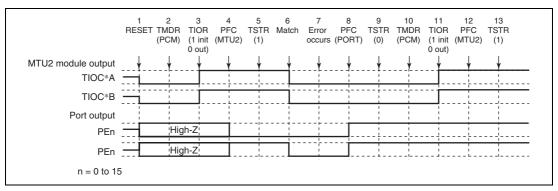

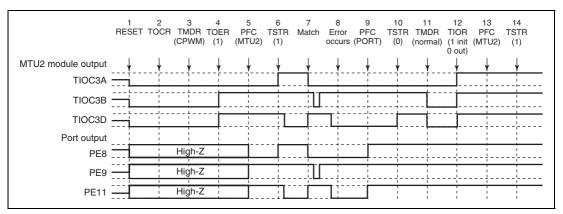

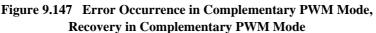

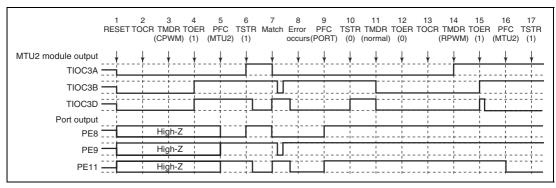

|     | 9.4.8   | Complementary PWM Mode                                             | 269 |

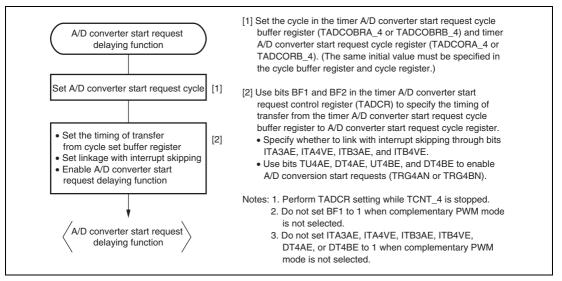

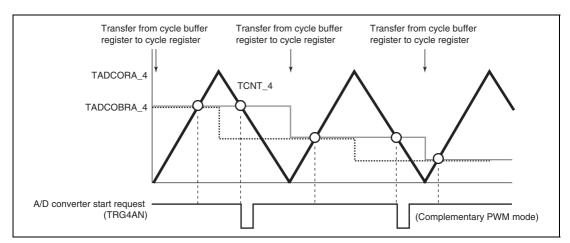

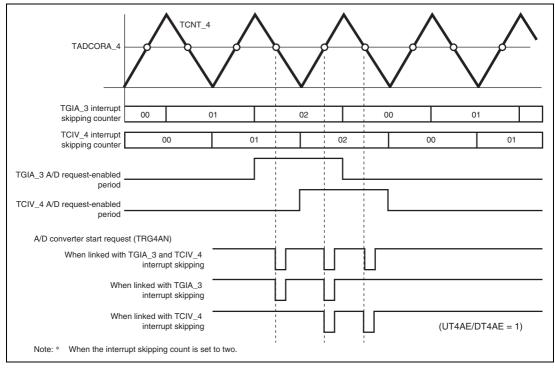

|     | 9.4.9   | A/D Converter Start Request Delaying Function                      | 308 |

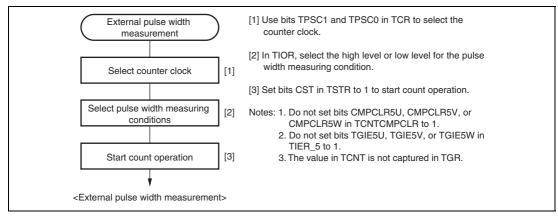

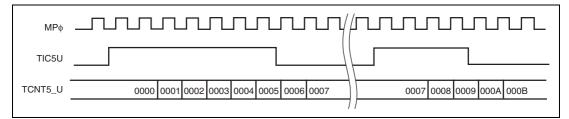

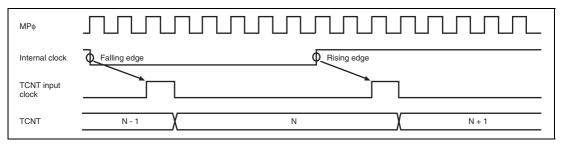

|     | 9.4.10  | External Pulse Width Measurement                                   | 312 |

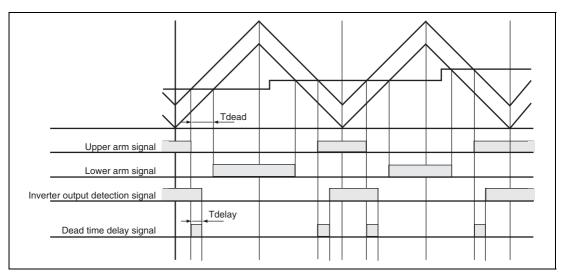

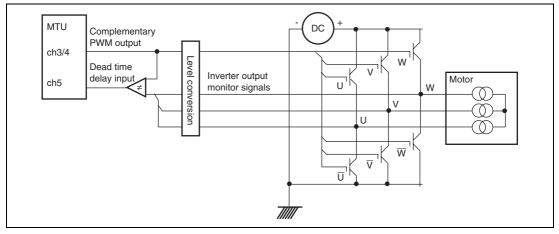

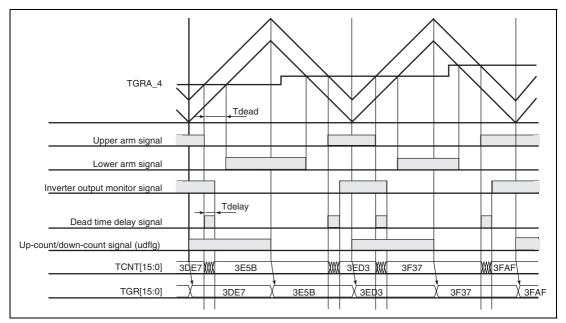

|     | 9.4.11  | Dead Time Compensation                                             | 313 |

|     | 9.4.12  | TCNT Capture at Crest and/or Trough in Complementary PWM Operation | 315 |

| 9.5 | Interru | pt Sources                                                         | 316 |

|     | 9.5.1   | Interrupt Sources and Priorities                                   | 316 |

|     | 9.5.2   | A/D Converter Activation                                           | 319 |

| 9.6 | Operati | ion Timing                                                         | 321 |

|     | 9.6.1   | Input/Output Timing                                                | 321 |

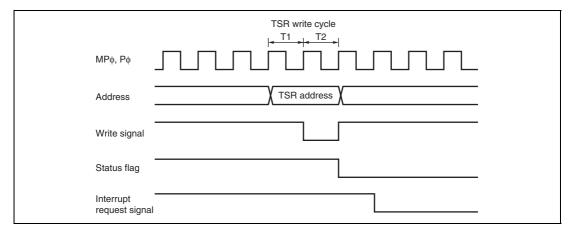

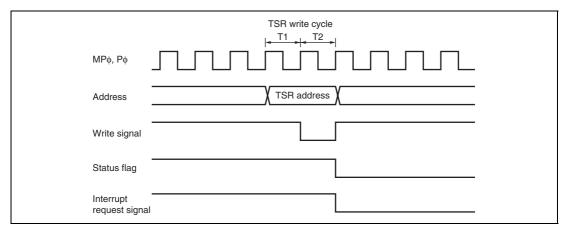

|     | 9.6.2   | Interrupt Signal Timing                                            | 328 |

| 9.7 | Usage   | Notes                                                              | 332 |

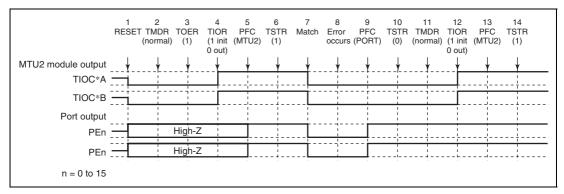

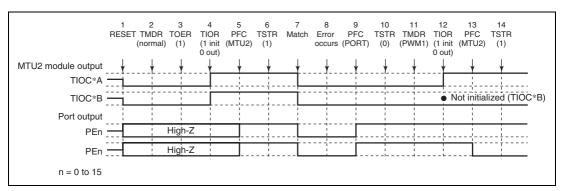

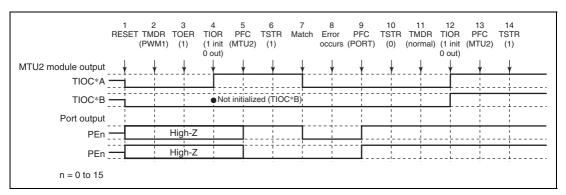

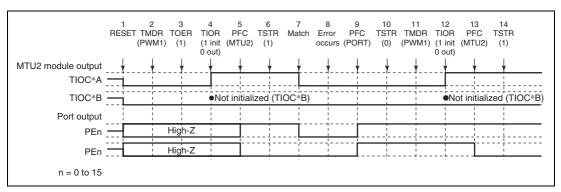

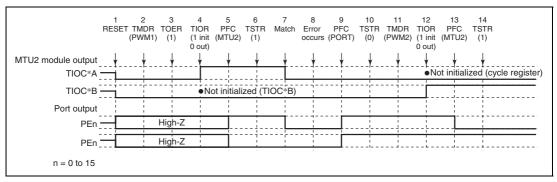

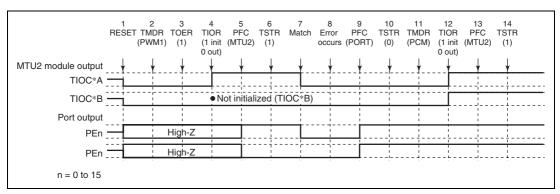

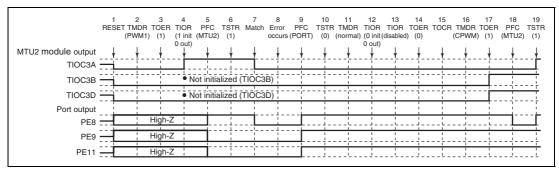

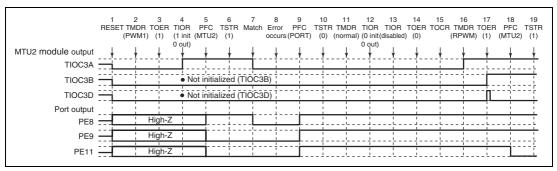

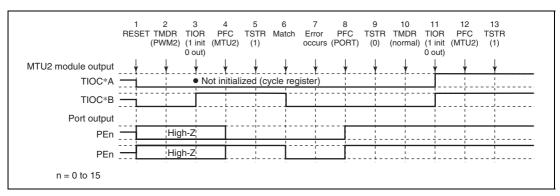

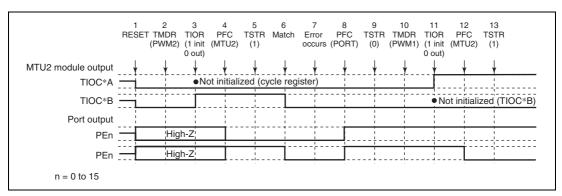

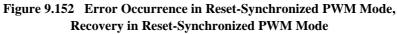

| 9.8.1       Operating Modes       348         9.8.2       Reset Start Operation       348         9.8.3       Operation in Case of Re-Setting Due to Error During Operation, etc.       349         9.8.4       Overview of Initialization Procedures and Mode Transitions in Case of Error during Operation, etc.       350         Section 10       Port Output Enable (POE)       381         10.1       Features       381         10.2       Input/Output Pins       383         10.3       Register Descriptions       384         10.3.1       Input Level Control/Status Register 1 (ICSR1)       385         10.3.3       Input Level Control/Status Register 3 (ICSR3)       389         10.3.4       Software Port Output Enable Register (SPOER)       391                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 9.7.1   | Module Standby Mode Setting                                            | 332 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|------------------------------------------------------------------------|-----|

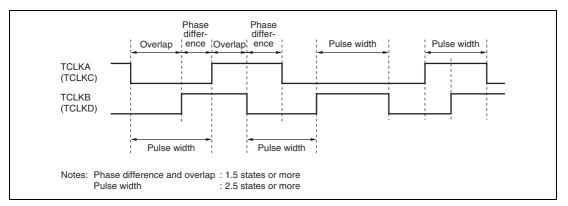

| 9.7.4       Contention between TCNT Write and Clear Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | 9.7.2   | Input Clock Restrictions                                               | 332 |

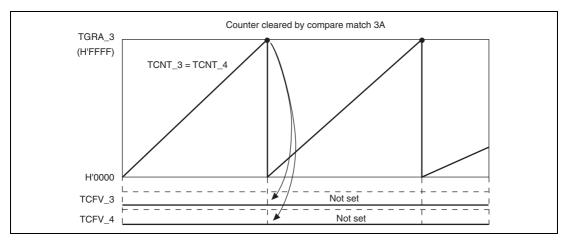

| 9.7.5       Contention between TCNT Write and Increment Operations       334         9.7.6       Contention between TGR Write and Compare Match       335         9.7.7       Contention between Buffer Register Write and TCNT Clear       337         9.7.8       Contention between TGR Read and Input Capture       338         9.7.9       Contention between TGR Read and Input Capture       338         9.7.10       Contention between TGR Write and Input Capture       339         9.7.11       Contention between Buffer Register Write and Input Capture       340         9.7.12       TCNT_2 Write and Overflow/Underflow Contention in Cascade Connection       340         9.7.13       Counter Value during Complementary PWM Mode       342         9.7.14       Buffer Operation Setting in Complementary PWM Mode       342         9.7.15       Reset Sync PWM Mode Buffer Operation and Compare Match Flag       343         9.7.16       Overflow Flags in Reset Synchronous PWM Mode       344         9.7.17       Contention between Overflow/Underflow and Counter Clearing       345         9.7.18       Contention between TCNT Write and Overflow/Underflow       346         9.7.19       Cautions on Transition from Normal Operation or PWM Mode 1 to<br>Reset-Synchronized PWM Mode       347         9.7.20       Output Level in Complementary PWM Mode and<br>Res                                                        |       | 9.7.3   | Caution on Period Setting                                              | 333 |

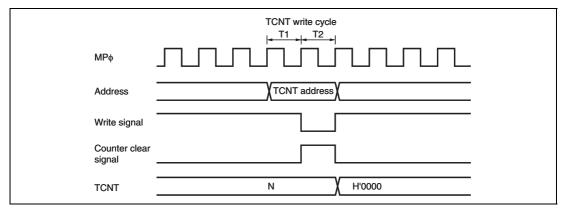

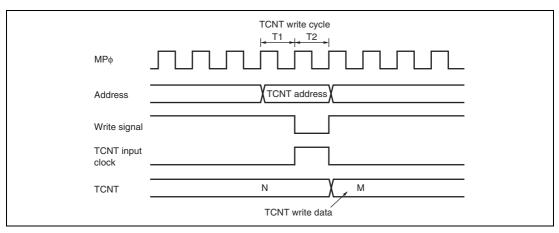

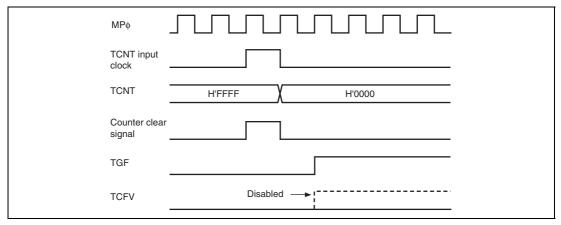

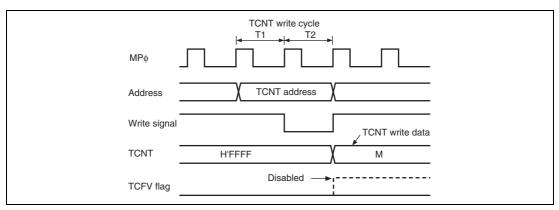

| 9.7.6       Contention between TGR Write and Compare Match       335         9.7.7       Contention between Buffer Register Write and TCNT Clear       336         9.7.8       Contention between TGR Read and Input Capture       338         9.7.10       Contention between TGR Read and Input Capture       339         9.7.11       Contention between TGR Write and Input Capture       340         9.7.12       TCNT_2 Write and Overflow/Underflow Contention in Cascade Connection       340         9.7.13       Counter Value during Complementary PWM Mode Stop       342         9.7.14       Buffer Operation Setting in Complementary PWM Mode       342         9.7.15       Reset Sync PWM Mode Buffer Operation and Compare Match Flag       343         9.7.16       Overflow/Hags in Reset Synchronous PWM Mode       344         9.7.17       Contention between TCNT Write and Overflow/Underflow       344         9.7.16       Overflow/Hags in Reset Synchronous PWM Mode       344         9.7.17       Contention between TCNT Write and Overflow/Underflow       346         9.7.19       Cautions on Transition from Normal Operation or PWM Mode 1 to       Reset-Synchronized PWM Mode         9.8       Ntrue Output Level in Complementary PWM Mode and       347         9.7.20       Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection                                                                         |       | 9.7.4   | Contention between TCNT Write and Clear Operations                     | 333 |

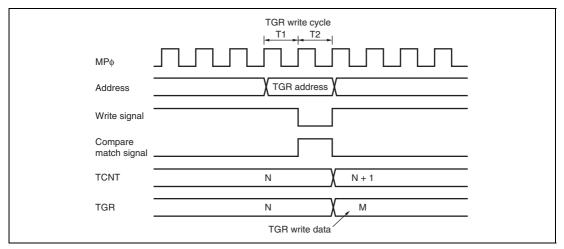

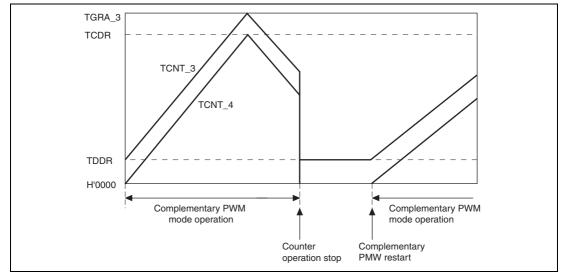

| 9.7.7       Contention between Buffer Register Write and Compare Match       336         9.7.8       Contention between TGR Read and Input Capture       337         9.7.9       Contention between TGR Read and Input Capture       338         9.7.10       Contention between TGR Write and Input Capture       340         9.7.11       Contention between Buffer Register Write and Input Capture       340         9.7.12       TCNT_2 Write and Overflow/Underflow Contention in Cascade Connection       340         9.7.13       Counter Value during Complementary PWM Mode Stop       342         9.7.16       Reset Sync PWM Mode Buffer Operation and Compare Match Flag       343         9.7.16       Overflow Flags in Reset Synchronous PWM Mode       344         9.7.17       Contention between TCNT Write and Overflow/Underflow       346         9.7.18       Contention between TCNT Write and Overflow/Underflow       346         9.7.19       Cautions on Transition from Normal Operation or PWM Mode 1 to<br>Reset-Synchronized PWM Mode       347         9.7.20       Output Level in Complementary PWM Mode and<br>Reset-Synchronized PWM Mode       347         9.7.21       Interrupts in Module Standby Mode       347         9.7.22       Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       347         9.8.1       Operating Modes                                                                    |       | 9.7.5   | Contention between TCNT Write and Increment Operations                 | 334 |

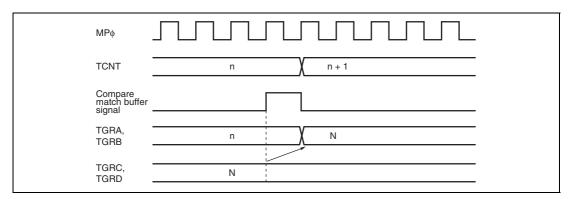

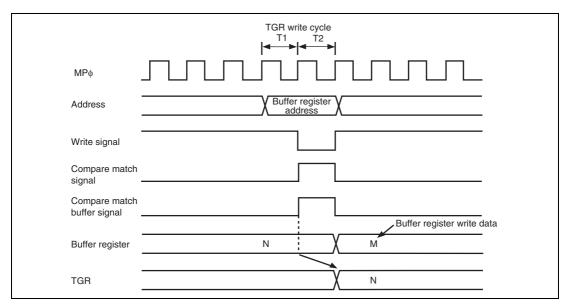

| 9.7.8       Contention between Buffer Register Write and TCNT Clear       337         9.7.9       Contention between TGR Read and Input Capture       338         9.7.10       Contention between TGR Write and Input Capture       339         9.7.11       Contention between Buffer Register Write and Input Capture       340         9.7.12       TCNT_2 Write and Overflow/Underflow Contention in Cascade Connection       340         9.7.13       Counter Value during Complementary PWM Mode Stop       342         9.7.14       Buffer Operation Setting in Complementary PWM Mode       342         9.7.15       Reset Sync PWM Mode Buffer Operation and Compare Match Flag       343         9.7.16       Overflow Flags in Reset Synchronous PWM Mode       344         9.7.17       Contention between Overflow/Underflow and Counter Clearing       346         9.7.19       Cautions on Transition from Normal Operation or PWM Mode 1 to       Reset-Synchronized PWM Mode       347         9.7.20       Output Level in Complementary PWM Mode and       347       347         9.7.21       Interrupts in Module Standby Mode       347         9.7.22       Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       347         9.7.23       Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       348         9.8.1       O                                                                                |       | 9.7.6   | Contention between TGR Write and Compare Match                         | 335 |

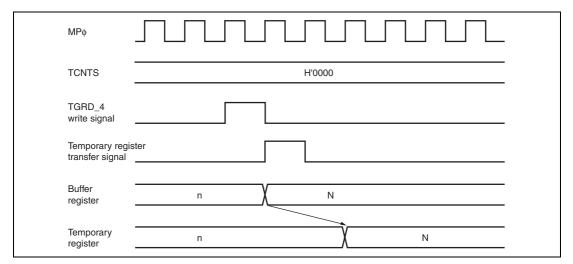

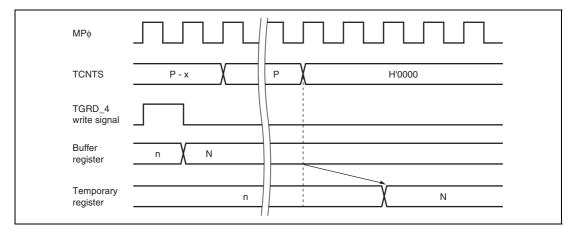

| 9.7.9       Contention between TGR Read and Input Capture.       338         9.7.10       Contention between TGR Write and Input Capture.       339         9.7.11       Contention between Buffer Register Write and Input Capture.       340         9.7.12       TCNT_2 Write and Overflow/Underflow Contention in Cascade Connection.       340         9.7.13       Counter Value during Complementary PWM Mode Stop       342         9.7.14       Buffer Operation Setting in Complementary PWM Mode       342         9.7.15       Reset Sync PWM Mode Buffer Operation and Compare Match Flag       343         9.7.16       Overflow Flags in Reset Synchronous PWM Mode       344         9.7.17       Contention between Overflow/Underflow and Counter Clearing       345         9.7.18       Contention between TCNT Write and Overflow/Underflow       346         9.7.19       Cautions on Transition from Normal Operation or PWM Mode 1 to<br>Reset-Synchronized PWM Mode       347         9.7.20       Output Level in Complementary PWM Mode and<br>Reset-Synchronized PWM Mode       347         9.7.21       Interrupts in Module Standby Mode       347         9.7.22       Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       347         9.7.23       Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       348         9.8.4       Opera                                                        |       | 9.7.7   | Contention between Buffer Register Write and Compare Match             | 336 |

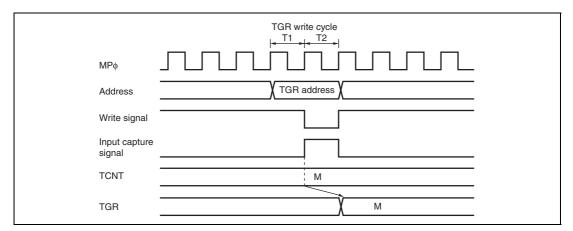

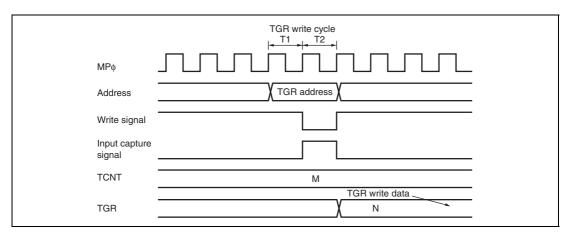

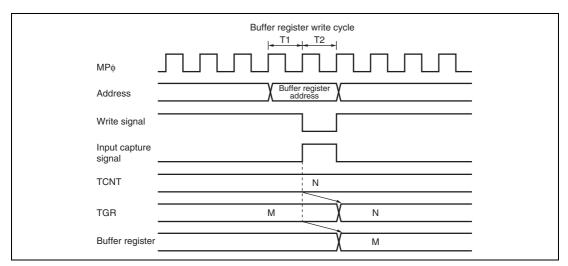

| 9.7.10       Contention between TGR Write and Input Capture       339         9.7.11       Contention between Buffer Register Write and Input Capture       340         9.7.12       TCNT_2 Write and Overflow/Underflow Contention in Cascade Connection       340         9.7.13       Counter Value during Complementary PWM Mode Stop       342         9.7.14       Buffer Operation Setting in Complementary PWM Mode       342         9.7.15       Reset Sync PWM Mode Buffer Operation and Compare Match Flag       343         9.7.16       Overflow Flags in Reset Synchronous PWM Mode       344         9.7.17       Contention between Overflow/Underflow and Counter Clearing       345         9.7.18       Contention between TCNT Write and Overflow/Underflow       346         9.7.19       Cautions on Transition from Normal Operation or PWM Mode 1 to<br>Reset-Synchronized PWM Mode       347         9.7.20       Output Level in Complementary PWM Mode and<br>Reset-Synchronized PWM Mode       347         9.7.21       Interrupts in Module Standby Mode       347         9.7.22       Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       347         9.7.23       Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       347         9.8.4       Operating Modes       348       348         9.8.1       Operating Modes                                                                      |       | 9.7.8   | Contention between Buffer Register Write and TCNT Clear                | 337 |

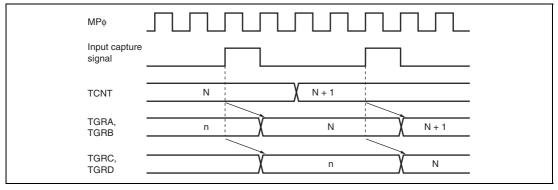

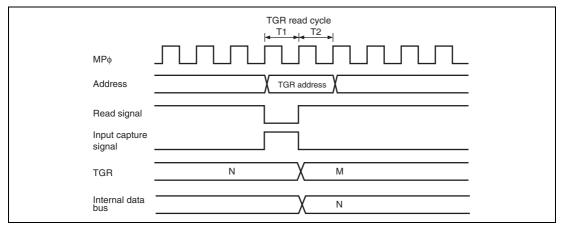

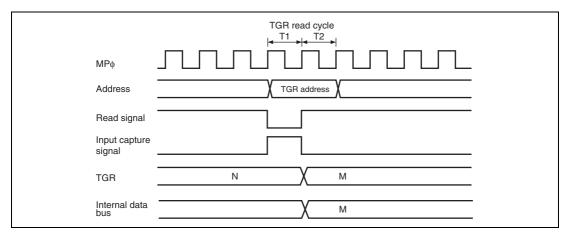

| 9.7.11       Contention between Buffer Register Write and Input Capture       340         9.7.12       TCNT_2 Write and Overflow/Underflow Contention in Cascade Connection       340         9.7.13       Counter Value during Complementary PWM Mode Stop       342         9.7.14       Buffer Operation Setting in Complementary PWM Mode       342         9.7.15       Reset Sync PWM Mode Buffer Operation and Compare Match Flag       343         9.7.16       Overflow Flags in Reset Synchronous PWM Mode       344         9.7.17       Contention between Overflow/Underflow and Counter Clearing       345         9.7.18       Contention between Overflow/Underflow and Counter Clearing       346         9.7.19       Cautions on Transition from Normal Operation or PWM Mode 1 to<br>Reset-Synchronized PWM Mode       346         9.7.20       Output Level in Complementary PWM Mode and<br>Reset-Synchronized PWM Mode       347         9.7.21       Interrupts in Module Standby Mode       347         9.7.22       Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       347         9.8.1       Operating Modes       348         9.8.2       Reset Start Operation       348         9.8.3       Operation in Case of Re-Setting Due to Error During Operation, etc.       349         9.8.4       Overview of Initialization Procedures and Mode Transitio                                                        |       | 9.7.9   | Contention between TGR Read and Input Capture                          | 338 |