# SCG4600 Synchronous Clock Generators

PLL

2111 Comprehensive Drive

Aurora, Illinois 60505

Phone: 630-851-4722

Fax: 630-851-5040

www.conwin.com

### **General Description**

The SCG4600 is a digital phase locked loop generating CML outputs from an intrinsically low jitter voltage controlled crystal oscillator.

The SCG4600 can lock to one of two external 8 kHz references, which is selectable using the SELAB input select pin. The unit has an acquisition time of about 1.5 seconds and it is tolerant of different reference duty cycles.

The SCG4600 includes an alarm output that indicates deviations from normal operation. If a Loss-of-Reference (LOR) or Loss-of-Lock (LOL) is detected the alarm with indicate the need for a reference rearrangement. If both references A and B are absent the module will enter Free Run operation. The FRstatus pin will indicate that the module is in Free Run operation. Frequency stability during Free Run operation is guaranteed to ±20 PPM. Additionally the Free Run mode may be entered manually.

The package dimensions are 1.05" x 1.03" x .375" (maximum) on a 4 layer FR4 board with J-Leads. Parts are assembled using high temperature solder to withstand 180°C surface mount reflow processes.

#### **Features**

- Phase Locked Output Frequency Control

- Intrinsically Low Jitter Crystal Oscillator

- CML Outputs

- Dual 8 kHz

References

- LOR & LOL Alarm.

- Force Free Run Function

- Automatic Free Run Operation on Loss of Both References A & B

- Input Duty Cycle Tolerant

- 3.3VDC Power Supply

| Bulletin  | SG028      |

|-----------|------------|

| Page      | 1 of 12    |

| Revision  | P01        |

| Date      | 19 July 02 |

| Issued By | MBatts     |

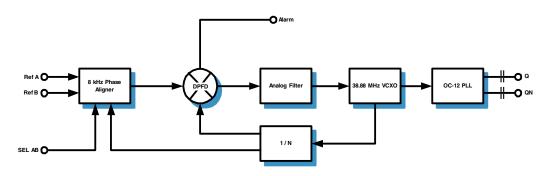

### **Block Diagram**

### Figure 1

### **Absolute Maximum Rating**

#### Table 1

| Symbol          | Parameter            | Minimum | Nominal | Maximum | Units | Notes |  |

|-----------------|----------------------|---------|---------|---------|-------|-------|--|

| V <sub>cc</sub> | Power Supply Voltage | -0.5    | -       | +4.0    | Volts | 1.0   |  |

| $V_{i}$         | Input Voltage        | -0.5    | -       | +5.5    | Volts | 1.0   |  |

| T <sub>s</sub>  | Storage Temperature  | -40.0   | -       | +85     | °C    | 1.0   |  |

### **Operating Specifications**

#### Table 2

| Symbol             | Parameter                               | Minimum | Nominal          | Maximum | Units      | Notes |

|--------------------|-----------------------------------------|---------|------------------|---------|------------|-------|

| V <sub>cc</sub>    | Power Supply Voltage                    | 3.135   | 3.3              | 3.465   | Volts      | 2.0   |

| I <sub>cc</sub>    | Power Supply Current                    | -       | 200              | -       | mA         |       |

| T <sub>o</sub>     | Temperature Range                       | 0       | -                | 70      | °C         |       |

| F <sub>o</sub>     | Available Output Frequencies            | -       | 622.08<br>155.52 | -       | MHz<br>MHz |       |

| F <sub>fr</sub>    | Free Run Frequency                      | -20     | -                | 20      | ppm        |       |

| F <sub>refa</sub>  | Reference Frequency A                   | -       | 8                | -       | kHz        |       |

| F <sub>refb</sub>  | Reference Frequency B                   | -       | 8                | -       | kHz        |       |

| F <sub>cap</sub>   | Capture/pull-in range                   | -25     | -                | 25      | ppm        |       |

| F <sub>bw</sub>    | Jitter Filter Bandwidth                 | -       | -                | 3       | Hz         | 3.0   |

| T <sub>jtol</sub>  | Input Jitter Tolerance                  | -       | -                | 6.25    | μs         |       |

| Taq                | Acquisition Time                        | -       | 1.4              | -       | S          | 4.0   |

| T <sub>rf</sub>    | Output Rise and Fall Time               | -       | 100              | -       | ps         | 5.0   |

| DC                 | Output Duty Cycle (20% 80%)             | 45      | -                | 55      | %          |       |

| MTIE <sub>sr</sub> | MTIE @ Synchronization<br>Rearrangement | -       | 50               | -       | ns         |       |

#### NOTES:

- 1.0 Operation of the device at these or any other condition beyond those listed under Operating Specifications is not implied. Exposure to Absolute Maximum Rating conditions for extended periods of time may affect device reliability.

- 2.0 Requires external regulation and supply decoupling. (2.2 uF, 330 pF)

- 3.0 3db loop response.

- 4.0 From a 20 PPM step in reference frequency

- 5.0 CML outputs ac coupled into 50-ohm load to  $\rm V_{\rm cc}.$

# **Input And Output Characteristics**

### Table 3

| Symbol          | Parameter                      | ameter Minimum Nominal Maximum |     | Maximum | Units | Notes |  |

|-----------------|--------------------------------|--------------------------------|-----|---------|-------|-------|--|

| CMOS Inp        | out and Output Characteristics |                                |     |         |       |       |  |

| $V_{ih}$        | High Level Input Voltage       | 2.0                            | -   | 5.5     | V     |       |  |

| V <sub>ii</sub> | Low Level Input Voltage        | 0.0                            | -   | 0.8     | V     |       |  |

| T <sub>io</sub> | I/O to Output Valid            | -                              | -   | 10      | ns    |       |  |

| C <sub>I</sub>  | Output Capacitance             | -                              | -   | 10      | рF    |       |  |

| $V_{oh}$        | High Level Output Voltage      | 2.4                            | -   | -       | V     |       |  |

| V <sub>ol</sub> | Low Level Output Voltage       | -                              | -   | 0.4     | V     |       |  |

| T <sub>ir</sub> | Input Reference Pulse Width    | 25.72                          | -   | -       | ns    |       |  |

| CML Outp        | ut Characteristics             |                                |     |         |       |       |  |

| V <sub>od</sub> | Differential Output Voltage    | -                              | 800 | 1200    | mV    | 5.0   |  |

## **Input Selection / Output Response**

#### Table 4

|       |               |                     | INPUTS           |                  |    |                      | OUTPUTS |   |    | NOTE |

|-------|---------------|---------------------|------------------|------------------|----|----------------------|---------|---|----|------|

| RESET | <b>ENABLE</b> | $SEL_{\mathtt{AB}}$ | REF <sub>A</sub> | $REF_{_{\rm B}}$ | FR | FR <sub>status</sub> | ALARM   | Q | QN |      |

| 1     | 0             | Χ                   | Χ                | Χ                | Χ  | 1                    | Χ       | Χ | Χ  | FR   |

| Х     | 1             | Χ                   | Χ                | Χ                | Χ  | HZ                   | HZ      | Χ | Χ  |      |

| 0     | 0             | Χ                   | Χ                | Χ                | 1  | 1                    | 1       | Χ | Χ  | FR   |

| 0     | 0             | 0                   | А                | А                | 0  | 0                    | 0       | Χ | Χ  | RA   |

| 0     | 0             | 1                   | А                | А                | 0  | 0                    | 0       | Χ | Χ  | RB   |

| 0     | 0             | 0                   | NA               | А                | 0  | 0                    | 1       | Χ | Χ  | U    |

| 0     | 0             | 1                   | NA               | А                | 0  | 0                    | 0       | Χ | Χ  | RB   |

| 0     | 0             | 1                   | А                | NA               | 0  | 0                    | 1       | Χ | Χ  | U    |

| 0     | 0             | 0                   | А                | NA               | 0  | 0                    | 0       | Χ | Х  | RA   |

| 0     | 0             | Χ                   | NA               | NA               | 0  | 1                    | 1       | Χ | Х  | FR   |

NOTES:

RA Locked to Reference A

RB Locked to Reference B

FR Free Run Mode

U Unstable (due to conditions shown, switch to active reference

NA Not Active

or Free Run)

HZ High Impedance

X Don't care

## **Jitter Generation Specifications**

### Table 5

| Frequency (MHz)                            | SONET Jitter BW 12 kHz - 1.3 MHz<br>pS (RMS) |  |  |

|--------------------------------------------|----------------------------------------------|--|--|

| 155.52                                     | 2.2 Typ.                                     |  |  |

| SONET Jitter BW 12 kHz - 5 MHz<br>pS (RMS) |                                              |  |  |

| 622.08                                     | 1.9 Typ.                                     |  |  |

# **Pin Description**

### Table 6

### All SCG4600 Models

| Pin # | Pin Name             | Pin Information                                       | Note |

|-------|----------------------|-------------------------------------------------------|------|

| 1     | ENABLE               | CML Enable / CMOS Tri-State (Enable = 0, Disable = 1) | 9.0  |

| 2     | TCK                  | No Connection, Internal Factory Programming Input.    | 8.0  |

| 3     | TDO                  | No Connection, Internal Factory Programming Input.    | 8.0  |

| 4     | REF <sub>A</sub>     | CMOS Reference Frequency Input.                       |      |

| 5     | SEL <sub>AB</sub>    | Input Reference Select Pin. (REFA = 0, REFB = 1)      | 9.0  |

| 6     | RESET                | RESET. (RESET = 1)                                    | 9.0  |

| 7     | REF <sub>B</sub>     | CMOS Reference Frequency Input.                       |      |

| 8     | GND                  | Ground.                                               |      |

| 9     | FR <sub>status</sub> | Free Run Status. (FR = 1)                             |      |

| 10    | V <sub>cc</sub>      | Supply Voltage relative to ground.                    |      |

| 11    | N/C                  | No Connection.                                        | 8.0  |

| 12    | ALARM                | Loss of Reference / Lock alarm. (Alarm = 1)           |      |

| 13    | FR                   | Force Free Run. (Phase Lock = 0, Free Run = 1)        | 9.0  |

| 14    | TDI                  | No Connection, Internal Factory Programming Input.    | 8.0  |

| 15    | TMS                  | No Connection, Internal Factory Programming Input.    | 8.0  |

| 16    | QN                   | Negative Differential CML Output.                     | 10.0 |

| 17    | GND                  | Ground.                                               |      |

| 18    | Q                    | Positive Differential CML Output.                     | 10.0 |

|       |                      |                                                       |      |

#### NOTES

- 8.0 Do not connect pin

- 9.0 Input pulled to ground

- 10.0 CML Outputs are internally AC coupled

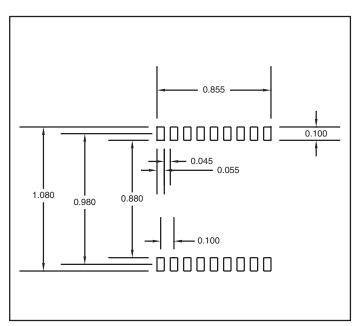

# **Circuit Board Footprint Recommendations**

Figure 2

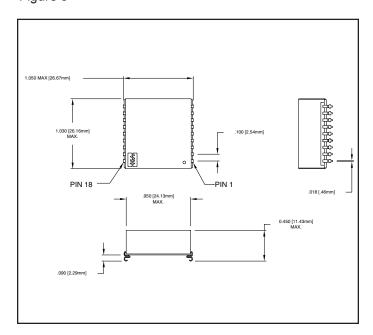

### **Mechanical Dimensions**

Figure 3

Figure 4

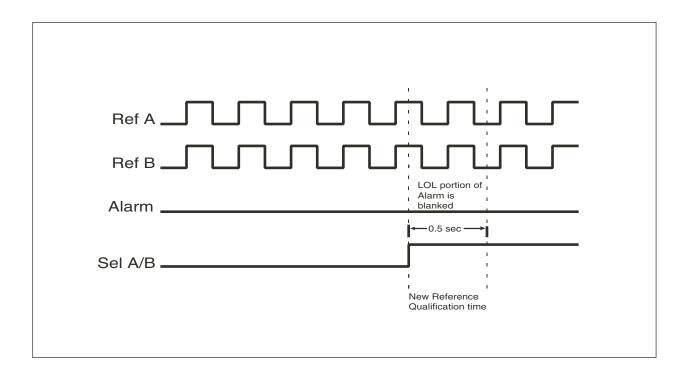

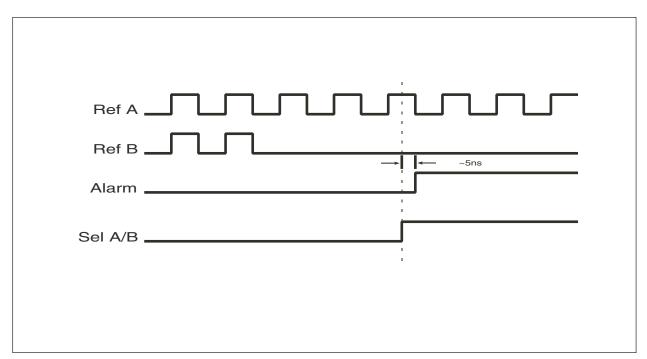

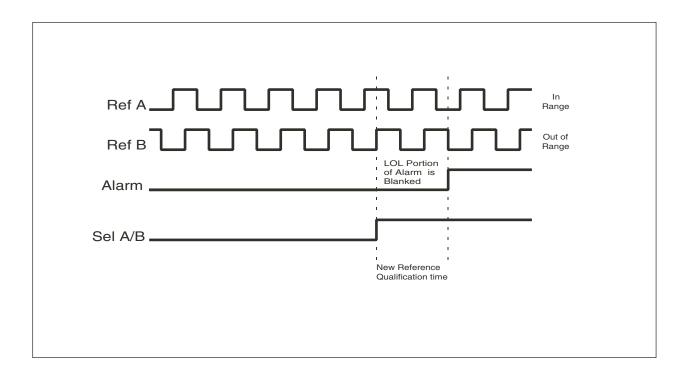

### Switch from A to B when Reference B is lost

Figure 5

Figure 6

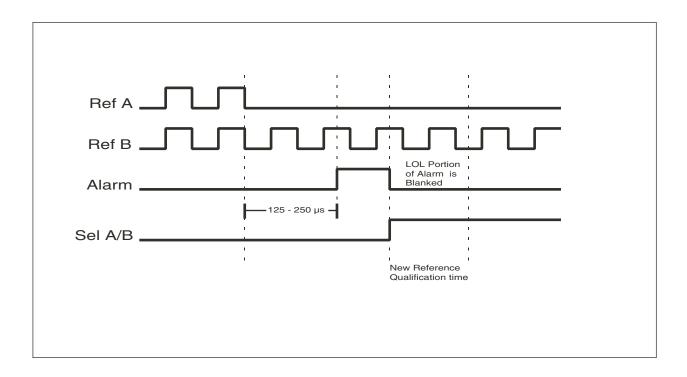

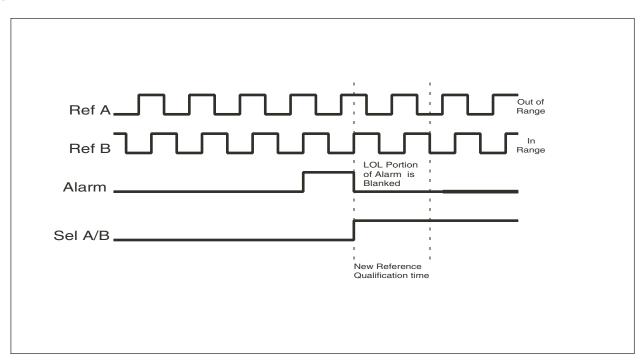

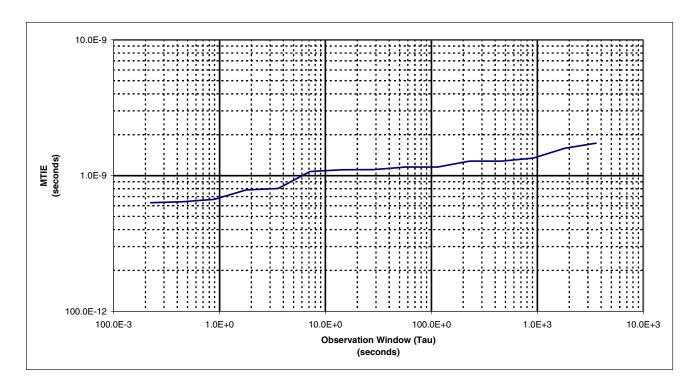

# Switch from A to B when A is out of range

Figure 7

Figure 8

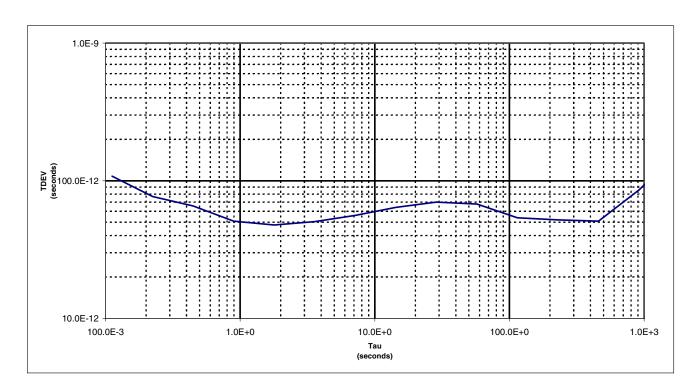

# Typical 622.08 MHz TDEV Measurement

Figure 10

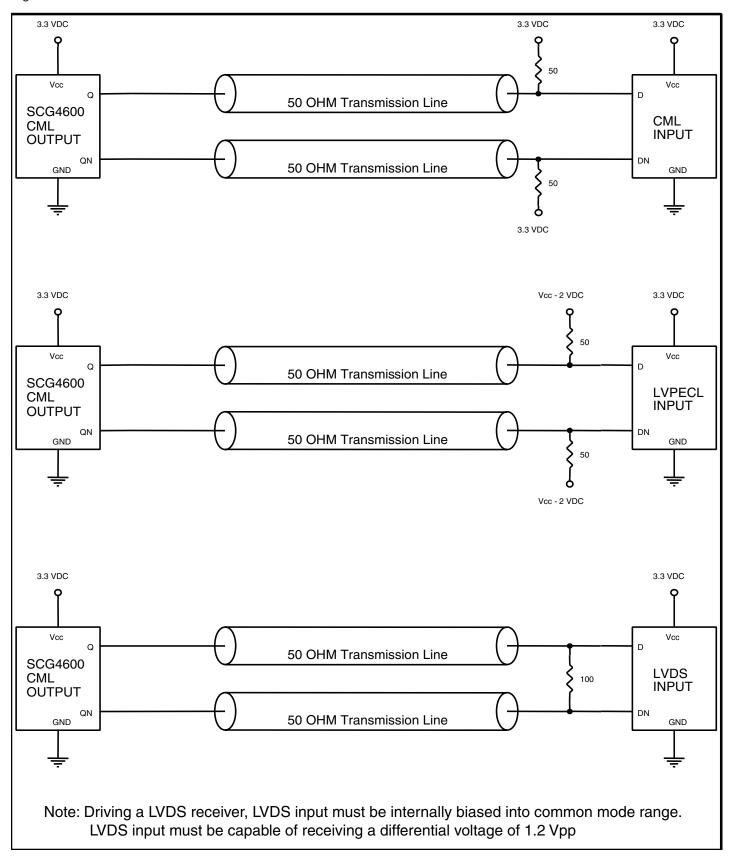

## **Suggested Differential Output Termination**

Figure 13

# **Ordering Information**

SCG{XXXX}-{FFF.FFF}{M}

XXXX equals a specific model (4600)

FFF.FFF equals the CML Output frequency (155.52, 622.08 MHz)

M equals MHZ and is added to all part numbers

Example: To order an SCG4600 with an CML Output of 622.08 MHz, Order part number SCG4600-622.08M

Please contact Connor-Winfield for other frequencies that may be available.

| Revision | Revision Date | Note                              |

|----------|---------------|-----------------------------------|

| P00      | 01/17/01      | Preliminary informational release |

| P01      | 7/19/02       | Added new frequency & reformatted |