# **VIESD1-SIP Series DC-DC Converter**

Rev. 06-2007

# **Description**

Designed to convert fixed voltages into an isolated regulated voltage, the VIESD1-SIP series is well suited for providing boardmount local supplies in a wide range of applications, including mixed analog/digital circuits, test & measurement equip., process/machine controls, datacom/telecom fields, etc...

### **Features**

- ·Isolated 1 W output

- Regulated

- ·High efficiency to 73%

- ·Dual voltage output

- ·Small footprint

- SIP package style

- ·Industry standard pinout

- ·UL94-V0 package

- ·No heatsink required

- ·3K Vdc isolation

- ·Temperature range: -40 ° C~+85 ° C

- ·No external component required

- ·Low cost

| Model              | Input   | Voltage       | Output  | Output ( | Current |            | Package |

|--------------------|---------|---------------|---------|----------|---------|------------|---------|

| Number             | Nominal | Range         | Voltage | Max.     | Min.    | Efficiency | Style   |

| VIESD1-S5-D5-SIP   | 5 Vdc   | 4.75~5.25 Vdc | ±5 Vdc  | ±100 mA  | ±10 mA  | 69%        | SIP     |

| VIESD1-S5-D9-SIP   | 5 Vdc   | 4.75~5.25 Vdc | ±9 Vdc  | ±56 mA   | ±6 mA   | 70%        | SIP     |

| VIESD1-S5-D12-SIP  | 5 Vdc   | 4.75~5.25 Vdc | ±12 Vdc | ±42 mA   | ±5 mA   | 72%        | SIP     |

| VIESD1-S5-D15-SIP  | 5 Vdc   | 4.75~5.25 Vdc | ±15 Vdc | ±33 mA   | ±4 mA   | 72%        | SIP     |

| VIESD1-S12-D5-SIP  | 12 Vdc  | 11.4~12.6 Vdc | ±5 Vdc  | ±100 mA  | ±10 mA  | 70%        | SIP     |

| VIESD1-S12-D9-SIP  | 12 Vdc  | 11.4~12.6 Vdc | ±9 Vdc  | ±56 mA   | ±6 mA   | 72%        | SIP     |

| VIESD1-S12-D12-SIP | 12 Vdc  | 11.4~12.6 Vdc | ±12 Vdc | ±42 mA   | ±5 mA   | 73%        | SIP     |

| VIESD1-S12-D15-SIP | 12 Vdc  | 11.4~12.6 Vdc | ±15 Vdc | ±33 mA   | ±4 mA   | 73%        | SIP     |

| VIESD1-S24-D5-SIP  | 24 Vdc  | 22.8~25.2 Vdc | ±5 Vdc  | ±100 mA  | ±10 mA  | 72%        | SIP     |

| VIESD1-S24-D9-SIP  | 24 Vdc  | 22.8~25.2 Vdc | ±9 Vdc  | ±56 mA   | ±6 mA   | 72%        | SIP     |

| VIESD1-S24-D12-SIP | 24 Vdc  | 22.8~25.2 Vdc | ±12 Vdc | ±42 mA   | ±5 mA   | 73%        | SIP     |

| VIESD1-S24-D15-SIP | 24 Vdc  | 22.8~25.2 Vdc | ±15 Vdc | ±33 mA   | ±4 mA   | 73%        | SIP     |

|                    |         |               |         |          |         |            |         |

### Note:

1. All specifications measured at TA=25°C, humidity <75%, nominal input voltage and rated output load unless otherwise specified.

# **Output Specifications**

| Item                                   | Test conditions          | Min. | Тур. | Max. | Units |

|----------------------------------------|--------------------------|------|------|------|-------|

| Output power                           |                          | 0.1  |      | 1    | W     |

| Line Regulation                        | For Vin change of 1%     |      |      | 0.25 | %     |

| Load Regulation                        | 10% to 100% full load    |      |      | 1    | %     |

| Output voltage accuracy 100% full load |                          |      |      | ±3   | %     |

| Temperature drift                      | 100% full load           |      |      | 0.03 | %/°C  |

| Output ripple & noise                  | 20Hz Bandwidth           |      | 10   | 15   | mVp-p |

| Switching frequency                    | Full load, nominal input |      | 100  |      | KHz   |

# **VIESD1-SIP Series DC-DC Converter**

Rev. 06-2007

**General Specifications**

| Short circuit protection      | 1 second                            |

|-------------------------------|-------------------------------------|

| Temperature rise at full load | 25°C Max, 15°C Typ.                 |

| Cooling                       | Free air convection                 |

| Operating temperature range   | -40°C to +85°C                      |

| Storage temperature range     | -55°C to +125°C                     |

| Soldering temperature         | 300°C (1.5mm from case for 10 sec.) |

| Storage humidity range        | ≤ 95%                               |

| Case material                 | Plastic (UL94-V0)                   |

| MTBF                          | >3,500,000 hrs.                     |

|                               |                                     |

**Isolation Specifications**

| Item                  | Test Conditions   | Min. | Тур. | Max. | Units |

|-----------------------|-------------------|------|------|------|-------|

| Isolation Voltage     | Tested for 1 min. | 3000 |      |      | Vdc   |

| Insulation Resistance | Test at 500 Vdc   | 1000 |      |      | ΜΩ    |

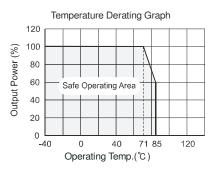

# **Typical Characteristics**

# Outline Dimensions & Recommended Layout Pattern

# **Pin Function**

# Package 27.50 RoHS 12.00 DC-DC CONVERTER YYWW 4.10 1.25 1.2 7 910 9.50 Bottom View Footprint 1.00\$\(\text{foot}\) -0.15/-0 \(\text{3}\) 1.12 1.12 1.7 910

| Pin                    | Function                        |

|------------------------|---------------------------------|

| 1<br>2<br>7<br>9<br>10 | Vin<br>GND<br>+ Vo<br>-Vo<br>0V |

|                        |                                 |

Note: All Pins on a 2.54mm pitch; all pin diameters are 0.50mm; all dimensions in mm.

- - 2.54

# **VIESD1-SIP Series DC-DC Converter**

Rev. 06-2007

### **Application Notes:**

### - Filtering

In some circuits which are sensitive to noise and ripple, a filtering capacitor may be added to the DC/DC output end and input end to reduce the noise and ripple. However, the capacitance of the output filter capacitor must be appropriate. If the capacitance is too big, a startup problem might arise. For every channel of output, providing that safe and reliable operation is ensured, the greatest capacitance of its filter capacitor is shown in the External Capacitor Table. To get an extreme low ripple, an "LC" filtering network may be connected to the input and output ends of the DC/DC converter, which may produce a more significant filtering effect. It should also be noted that the inductance and the frequency of the "LC" filtering network should be staggered with the DC/DC frequency to avoid mutual interference (see figure 1).

### - Requirement on Output Load

To ensure this module can operate efficiently and reliably, a minimum load is specified for this kind of DC/DC converter in addition to a maximum load (namely full load). During operation, make sure the specified range of input voltage is not exceeded, the minimum output load is not less than 10% of the full load, and that this product should never be operated under no load! If the actual output power is very small, please connect a resistor with proper resistance at the output end in parallel to increase the load, or use our company's products with a lower rated output power.

### - Overload protection

Under normal operating conditions, the output circuit of these products has no protection against over-current and short-circuits. The simplest method is to connect a self-recovery fuse in series at the input end or add a circuit breaker to the circuit.

## **External Capacitor Table**

| $V_{in}$ | External capacitor | V <sub>out</sub> | External capacitor |

|----------|--------------------|------------------|--------------------|

| 5VDC     | 4.7uF              | 5VDC             | 4.7uF              |

| 12VDC    | 2.2uF              | 9VDC             | 2.2uF              |

| 24VDC    | 1uF                | 12VDC            | 1uF                |

|          |                    | 15VDC            | 0.47uF             |