**Controller for TrenchPLUS FETs**

Rev. 02 — 21 January 2008

**Product data sheet**

### 1. Introduction

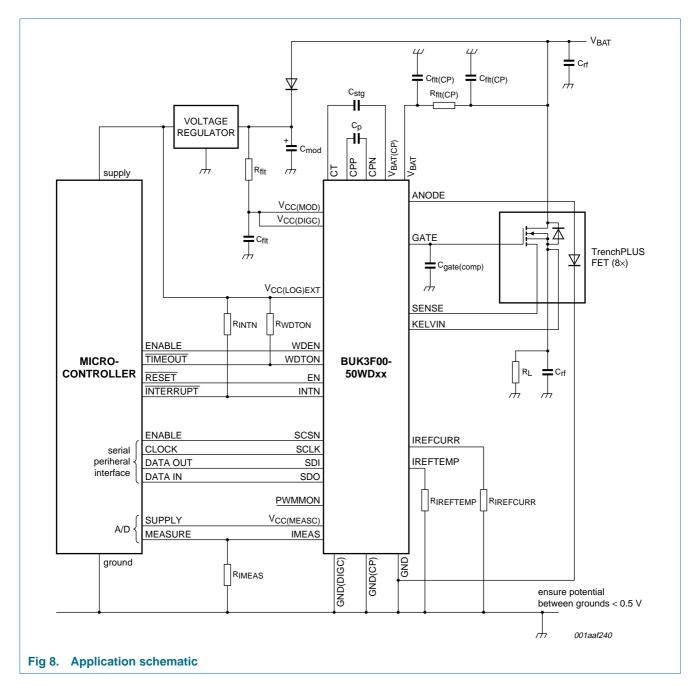

This data sheet describes a family of integrated circuits which provide direct digital control of multiple power switches (TrenchPLUS FETs) for use in automotive applications, and which are available in various configurations.

### 2. General description

Eight channel high-side switch controller in a leaded plastic quad flat package, with digital control and diagnostics, plus load current measurement.

Specific configurations are denoted by the last 2 letters in the type number.

### 3. Features

- Standby mode with very low power consumption

- Programmable drain current tripping

- Serial Peripheral Interface (SPI) communications

- Outputs controllable via SPI-bus or direct input

- Diagnostic status reporting via SPI-bus

- Analog and digital drain current measurement

- Watchdog for invalid commands or inactive SPI, with programmable time-out

- Programmable interrupt generator

- Overtemperature protection

- Pulse-width modulation with programmable frequency and duty cycle

- ESD protection on all pins

- Protection for battery transient overvoltage and reversed polarity battery connection

- Open-circuit detection

- Configurable fail-safe channel control options

### 4. Applications

Automotive applications such as DC and pulse-width modulation control in body control clusters, etc.

### 5. Quick reference data

| Table 1.         | Quick reference data   |            |                    |     |      |      |

|------------------|------------------------|------------|--------------------|-----|------|------|

| Symbol           | Parameter              | Conditions | Min                | Тур | Max  | Unit |

| V <sub>BAT</sub> | battery supply voltage | operating  | <sup>[1]</sup> 5.5 | 13  | 52   | V    |

| Tj               | junction temperature   |            | [2] -40            | -   | +150 | °C   |

[1] When V<sub>BAT</sub> < 9 V, the charge pump cannot be guaranteed to drive the external MOSFETs to achieve their specified R<sub>DSon</sub>.

[2] When  $T_i > 125$  °C, the device will function, but electrical parameters may deviate from the specified values.

### 6. Ordering information

#### Table 2.Ordering information

| Type number    | Packag | Package                                                                                       |          |  |  |  |  |  |

|----------------|--------|-----------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

|                | Name   | Description                                                                                   | Version  |  |  |  |  |  |

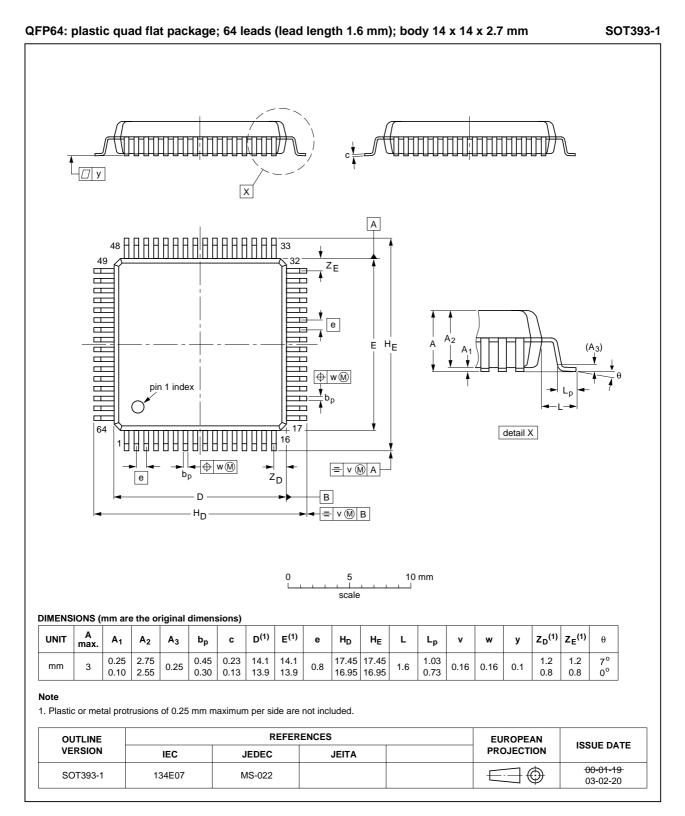

| BUK3F00-50WDFE | QFP64  | plastic quad flat package; 64 leads (lead length 1.6 mm); body 14 $\times$ 14 $\times$ 2.7 mm | SOT393-1 |  |  |  |  |  |

| BUK3F00-50WDFM |        |                                                                                               |          |  |  |  |  |  |

| BUK3F00-50WDFY |        |                                                                                               |          |  |  |  |  |  |

#### 6.1 Ordering options

#### Table 3.Type number differences

| Type number    | Description                                                           |

|----------------|-----------------------------------------------------------------------|

| BUK3F00-50WDFE | channel 4 has analog trip ratio of $3 \times I_{meas(ADC)(fs)}^{[1]}$ |

| BUK3F00-50WDFM | -                                                                     |

| BUK3F00-50WDFY | •                                                                     |

[1]  $I_{meas(ADC)(fs)}$  = full-scale ADC measure current.

User-accessible registers; see Table 5.

Protected settings; see Table 19.

Additional metal mask options; see Table 35.

**Controller for TrenchPLUS FETs**

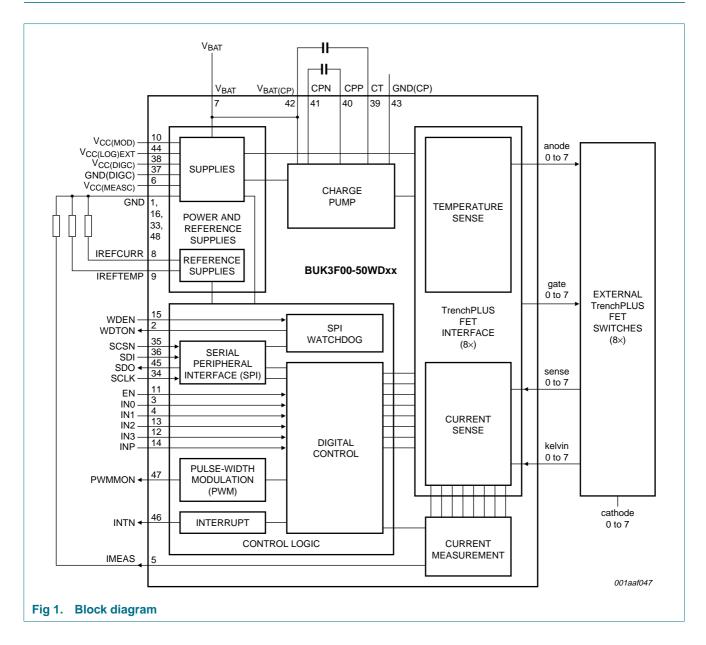

### 7. Block diagram

**Controller for TrenchPLUS FETs**

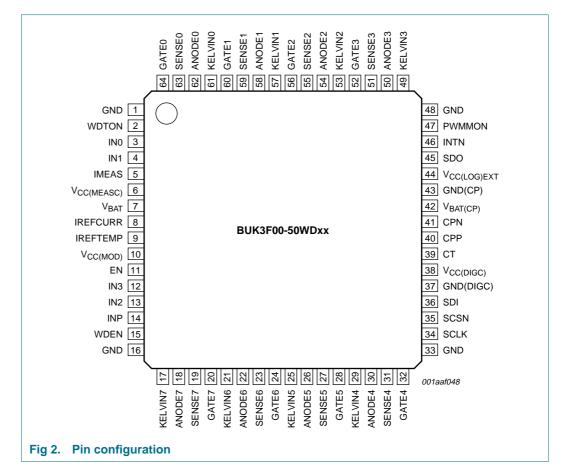

### 8. Pinning information

### 8.1 Pinning

#### 8.2 Pin description

#### Table 4. **Pin description** Symbol Pin Description **Supplies** $V_{BAT}$ 7 battery supply voltage GND 1, 16, 33, 48 battery ground 42 charge pump battery supply voltage V<sub>BAT(CP)</sub> GND(CP) charge pump ground 43 V<sub>CC(DIGC)</sub> 38 digital core supply voltage GND(DIGC) 37 digital core ground V<sub>CC(MOD)</sub> 10 module supply voltage V<sub>CC(LOG)EXT</sub> 44 external logic supply voltage for PWMMON and SDO outputs 6 measurement circuit supply voltage V<sub>CC(MEASC)</sub>

### Controller for TrenchPLUS FETs

| Table 4.          | Pin description     | continued                                                      |

|-------------------|---------------------|----------------------------------------------------------------|

| Symbol            | Pin                 | Description                                                    |

| Charge pu         | ump capacitors      |                                                                |

| CPP               | 40                  | positive connection to external pump capacitor                 |

| CPN               | 41                  | negative connection to external pump capacitor                 |

| СТ                | 39                  | connection to external storage capacitor                       |

| Digital           |                     |                                                                |

| EN                | 11                  | enable input; internal pull-down resistor                      |

| INTN              | 46                  | interrupt output; open-drain output                            |

| WDEN              | 15                  | watchdog enable input; internal pull-up resistor               |

| WDTON             | 2                   | watchdog timed output; open-drain output                       |

| PWMMON            | 47                  | PWM frequency monitor output                                   |

| Serial per        | ipheral interface   |                                                                |

| SCLK              | 34                  | SPI clock input; internal pull-down resistor                   |

| SCSN              | 35                  | SPI chip select input; internal pull-up resistor               |

| SDI               | 36                  | SPI data input; internal pull-down resistor                    |

| SDO               | 45                  | SPI data output; 3-state when inactive                         |

| Analog            |                     |                                                                |

| IREFCURI          | R 8                 | set reference for current measurement (with external resistor) |

| IREFTEM           | P 9                 | set reference for temperature sense (with external resistor)   |

| IMEAS             | 5                   | analog current measurement output (for selected channel)       |

| <b>Direct inp</b> | ut pins             |                                                                |

| IN0               | 3                   | direct input 0; internal pull-down resistor                    |

| IN1               | 4                   | direct input 1; internal pull-down resistor                    |

| IN2               | 13                  | direct input 2; internal pull-down resistor                    |

| IN3               | 12                  | direct input 3; internal pull-down resistor                    |

| INP               | 14                  | PWM input; internal pull-down resistor                         |

| Connectio         | ons for external Tr | renchPLUS switches                                             |

| Channel 0         |                     |                                                                |

| GATE0             | 64                  | gate                                                           |

| KELVIN0           | 61                  | source kelvin                                                  |

| SENSE0            | 63                  | current sense                                                  |

| ANODE0            | 62                  | anode of temperature sense diode                               |

| Channel 1         |                     |                                                                |

| GATE1             | 60                  | gate                                                           |

| KELVIN1           | 57                  | source kelvin                                                  |

| SENSE1            | 59                  | current sense                                                  |

| ANODE1            | 58                  | anode of temperature sense diode                               |

| Channel 2         |                     |                                                                |

| GATE2             | 56                  | gate                                                           |

| KELVIN2           | 53                  | source kelvin                                                  |

| SENSE2            | 55                  | current sense                                                  |

| ANODE2            | 54                  | anode of temperature sense diode                               |

**Controller for TrenchPLUS FETs**

| Table 4.  | Pin description continued |                                  |  |  |  |  |

|-----------|---------------------------|----------------------------------|--|--|--|--|

| Symbol    | Pin                       | Description                      |  |  |  |  |

| Channel 3 |                           |                                  |  |  |  |  |

| GATE3     | 52                        | gate                             |  |  |  |  |

| KELVIN3   | 49                        | source kelvin                    |  |  |  |  |

| SENSE3    | 51                        | current sense                    |  |  |  |  |

| ANODE3    | 50                        | anode of temperature sense diode |  |  |  |  |

| Channel 4 |                           |                                  |  |  |  |  |

| GATE4     | 32                        | gate                             |  |  |  |  |

| KELVIN4   | 29                        | source kelvin                    |  |  |  |  |

| SENSE4    | 31                        | current sense                    |  |  |  |  |

| ANODE4    | 30                        | anode of temperature sense diode |  |  |  |  |

| Channel 5 |                           |                                  |  |  |  |  |

| GATE5     | 28                        | gate                             |  |  |  |  |

| KELVIN5   | 25                        | source kelvin                    |  |  |  |  |

| SENSE5    | 27                        | current sense                    |  |  |  |  |

| ANODE5    | 26                        | anode of temperature sense diode |  |  |  |  |

| Channel 6 |                           |                                  |  |  |  |  |

| GATE6     | 24                        | gate                             |  |  |  |  |

| KELVIN6   | 21                        | source kelvin                    |  |  |  |  |

| SENSE6    | 23                        | current sense                    |  |  |  |  |

| ANODE6    | 22                        | anode of temperature sense diode |  |  |  |  |

| Channel 7 |                           |                                  |  |  |  |  |

| GATE7     | 20                        | gate                             |  |  |  |  |

| KELVIN7   | 17                        | source kelvin                    |  |  |  |  |

| SENSE7    | 19                        | current sense                    |  |  |  |  |

| ANODE7    | 18                        | anode of temperature sense diode |  |  |  |  |

BUK3F00-50WDXX\_2

Product data sheet

### 9. Functional description

The main functions of the device are:

- Power and reference supplies

- Charge pump

- Control logic

- Current measurement

- TrenchPLUS FET interface (8 ×)

### 9.1 Power and reference supplies

The main battery supplies power to the device and the eight TrenchPLUS FET switches. This device is intended for vehicle system applications that operate at a battery voltage of 12 V, 24 V or 42 V. The device has several different supply connections to ensure correct operation of the device within the application module.

#### 9.1.1 Battery supply: pins V<sub>BAT</sub> and GND

Pins V<sub>BAT</sub> and GND are the direct supply connections of the device to the battery.

**Low battery voltage** is detected on the charge pump supply pin  $V_{BAT(CP)}$ . Channels are switched off during extended low battery supply conditions and switched on when normal battery conditions return.

**Extended low battery voltage** occurs when the battery supply voltage  $V_{BAT}$  goes below:

- the battery undervoltage threshold ( $V_{th(uv)bat}$ ) for longer than the battery low time ( $t_{low(bat)}$ ), or

- the battery low threshold voltage (V<sub>th(low)bat</sub>)

**Transient low battery voltage** occurs when the battery supply voltage  $V_{BAT}$  goes below  $V_{th(uv)bat}$  for less than  $t_{low(bat)}$ , but remains above  $V_{th(low)bat}$ . Transient low battery voltage conditions affect the overcurrent protection; for details see <u>Section 9.5.2 "Overcurrent protection"</u>.

**Normal battery voltage** occurs when the battery supply voltage exceeds  $V_{th(uv)bat}$  for more than the battery high time ( $t_{high(bat)}$ ).

Hysteresis on detection reduces the possibility of repeated switching when the battery supply voltage is close to the threshold values.

The supply circuit has an internal overvoltage clamp to protect the control IC from overvoltage transients and is also protected against ESD. All four GND pins must be connected together to ground.

If this supply is connected to a reverse polarity battery voltage then the FET switches are turned on to protect against conduction through the source-drain diode. This protection operates whether the device is enabled or not.

#### 9.1.2 Module supply: pins V<sub>CC(MOD)</sub> and GND

Pins  $V_{CC(MOD)}$  and GND supply power to the circuits in the device that need to be kept functioning when the main battery supply dips below its normal operating limit. It is anticipated that the connection will be to the protected supply of the application module control circuits. This can be created using a suitable diode and storage capacitor from the battery supply. The connection should be decoupled close to the device.

**Low module voltage** causes the device to go through a Power-On Reset (POR). This condition is detected when the module supply voltage goes below the module undervoltage threshold ( $V_{th(uv)mod}$ ). The power-on reset is triggered when the supply voltage recovers and exceeds  $V_{th(uv)mod}$ . Hysteresis on this detection reduces the possibility of repeated resetting when the module supply is close to the threshold value.

The supply circuit has an internal overvoltage clamp to protect the control chip from overvoltage transients and is also protected against ESD. This supply should be protected against reverse battery connection in the application circuit.

#### 9.1.3 External logic supply: pins $V_{CC(LOG)EXT}$ and GND

The external logic supply provides power for the SDO and PWMMON output pins. Pin  $V_{CC(LOG)EXT}$  should be connected to the same supply (3.3 V or 5 V) used by the circuits that monitor these outputs.

#### 9.1.4 Analog measurement supply: pins V<sub>CC(MEASC)</sub> and GND

This supply provides power for the IMEAS analog current measurement output. Pin  $V_{CC(MEASC)}$  should be connected to the same supply (3.3 V or 5 V) used by the circuit that uses this output.

If this output is not needed, then pins  $V_{CC(MEASC)}$  and IMEAS should be grounded.

#### 9.1.5 Digital supply: pins V<sub>CC(DIGC)</sub> and GND(DIGC)

This supplies power to the internal regulator for the digital core and should be connected to the same potential as  $V_{CC(MOD)}$  and GND. It is not internally connected to the module supply, ensuring that digital noise does not affect the measurement circuits. The connection should be decoupled close to the device.

The digital supply circuit has an internal overvoltage clamp to protect the BUK3F00-50WDxx from overvoltage transients and is also protected against ESD.

#### 9.1.6 Reference supplies: pins IREFCURR and IREFTEMP

An internal band gap reference is used to ensure stable voltage and current references:

- Measured current reference pin IREFCURR: The full-scale analog output measurement current and the full-scale measurement current through the ADC are both set by connecting an external resistor between pins IREFCURR and GND.

- Temperature reference pin IREFTEMP: The forward current for the temperature sensing diodes in the TrenchPLUS FETs is set by connecting an external resistor between pins IREFTEMP and GND.

#### 9.2 Charge pump

The controller has an internal charge pump circuit to supply the gate voltage required to operate the high-side FET switches. The charge pump uses an internal oscillator and internal switches with external pump and storage capacitors.

#### 9.2.1 Charge pump supply: pins V<sub>BAT(CP)</sub> and GND(CP)

Pins  $V_{BAT(CP)}$  and GND(CP) supply power to the internal charge pump. This is derived from the  $V_{BAT}$  supply either via an internal resistor between pins  $V_{BAT}$  and  $V_{BAT(CP)}$  or by linking these pins externally. Pin GND(CP) should be connected to pin GND; the grounds are not internally connected to ensure any charge pump noise does not affect the measurement circuit. The connections should be decoupled close to the device.

The charge pump supply circuit has an internal overvoltage clamp to protect the BUK3F00-50WDxx from overvoltage transients and is also protected against ESD.

If connected to a reverse polarity battery voltage, the charge pump supply is protected by the internal resistor connection to  $V_{BAT}$ .

#### 9.2.2 Charge pump boost mode

To ensure fast start-up, the charge pump has a boost mode that operates for a set time. This mode is triggered at power-on reset and when the charge pump voltage falls below the charge pump fault threshold or the battery voltage stays below the undervoltage threshold. If the charge pump voltage is below the fault threshold after the charge pump boost is completed, then no further boost is possible until the charge pump fault is cleared.

#### 9.3 Control logic

The control logic is responsible for switching the individual FET channels on and off, depending on user settings and the implementation of protection methods. It contains registers used for storing the user settings for channel configurations, current reference and measurement, diagnostic and watchdog modes. Communication with a controller is via the SPI-bus.

The digital block is designed to support 8 channels; unused channels should be programmed off at all times.

#### 9.3.1 Digital control

The device is enabled by pin EN. When pin EN is LOW, the device is in Standby mode and all FETs are held off by an active switch with a standby resistance between pins GATE and KELVIN. When pin EN is HIGH, the device is enabled for normal operation. Pin EN can be used as the reset signal by a controller for the control logic. When pin EN is reset to HIGH, the device goes through a power-on reset, registers are loaded with their default values and channels are switched on or off according to the mapping for the individual device type.

Digital control consists of a number of registers that control the functions. The default value is loaded during power-on reset and, if the WRITE\_PROTECT option is enabled, for defined registers, when the SPI watchdog times out. For some registers the default setting can be programmed by metal mask options.

**Controller for TrenchPLUS FETs**

| Register <sup>[1]</sup> Name |                          | Description                                   | Mask               | Versio | n defaul | t value <sup>[2]</sup> |

|------------------------------|--------------------------|-----------------------------------------------|--------------------|--------|----------|------------------------|

|                              | lano                     |                                               | option             | FE     | FM       | FY                     |

| Read/write                   | registers <sup>[3]</sup> |                                               |                    | 1      |          |                        |

| 01h                          | CHAN_ONOFF               | channels select: on/off                       | N                  | 00h    | 00h      | 00h                    |

| 02h                          | IN02_MAP                 | direct input pins IN0 and IN2 mapping         | Y <u>[4]</u>       | 21h    | 10h      | 1Ch                    |

| 03h                          | IN13_MAP                 | direct input pins IN1 and IN3 mapping         | Y <u>[4]</u>       | 84h    | 40h      | 01h                    |

| 04h                          | INP_MAP                  | PWM input pin INP mapping                     | Y <u>[4]</u>       | 10h    | 08h      | 00h                    |

| 05h                          | ANDOR_MAP                | direct input pin AND/OR operation             | Y <u>[4]</u>       | 00h    | 00h      | 00h                    |

| 06h                          | CURR_MEAS                | channel select analog current measurement     | N                  | 00h    | 00h      | 00h                    |

| 07h                          | SEL_CURR_TRIP_<br>CHAN   | select current tripping channel               | Y <u>[4]</u>       | 00h    | 00h      | 00h                    |

| 08h                          | CHAN_OT_FAULT_CLR        | channel set overtemperature fault clear       | Y <u>[4]</u>       | 00h    | 00h      | 00h                    |

| 09h                          | PWM_SYNC                 | channel PWM synchronization                   | Ν                  | 00h    | 00h      | 00h                    |

| 0Ah                          | PWM_SAM_BEGINEND         | channel PWM sample point begin or end         | Ν                  | FFh    | FFh      | FFh                    |

| 0Ch                          | CHAN_WD_MAP              | select channel watchdog behavior              | Y <u>[4]</u>       | 21h    | 58h      | 1Dh                    |

| 0Dh                          | WD_TO                    | watchdog time-out period setting              | Y <u>[4]</u>       | 3Fh    | 3Fh      | 3Fh                    |

| 0Eh                          | CTRL_SET                 | controller settings                           | Y <u>[4]</u>       | 08h    | 08h      | 08h                    |

| 0Fh                          | INT_PWM_FREQ             | internal PWM frequency setting                | Y <u>[4]</u>       | B6h    | BBh      | B1h                    |

| 10h                          | PWM_DC_CH0               | internal PWM duty cycle setting for channel 0 | Y <u>[4][5]</u>    | FFh    | FFh      | FFh                    |

| 11h                          | PWM_DC_CH1               | internal PWM duty cycle setting for channel 1 | Y <u>[4][5]</u>    | FFh    | FFh      | FFh                    |

| 12h                          | PWM_DC_CH2               | internal PWM duty cycle setting for channel 2 | Y <u>[4][5]</u>    | FFh    | FFh      | FFh                    |

| 13h                          | PWM_DC_CH3               | internal PWM duty cycle setting for channel 3 | Y <u>[4][5]</u>    | FFh    | FFh      | FFh                    |

| 14h                          | PWM_DC_CH4               | internal PWM duty cycle setting for channel 4 | Y <u>[4][5]</u>    | FFh    | FFh      | FFh                    |

| 15h                          | PWM_DC_CH5               | internal PWM duty cycle setting for channel 5 | Y <u>[4][5]</u>    | FFh    | FFh      | FFh                    |

| 16h                          | PWM_DC_CH6               | internal PWM duty cycle setting for channel 6 | Y <u>[4][5]</u>    | FFh    | FFh      | FFh                    |

| 17h                          | PWM_DC_CH7               | internal PWM duty cycle setting for channel 7 | Y <u>[4][5]</u>    | FFh    | FFh      | FFh                    |

| 18h                          | OT_TRIPLEV_CH30          | overtemperature trip level channels 3 to 0    | Y <u>[4]</u>       | AAh    | AAh      | AAh                    |

| 19h                          | OT_TRIPLEV_CH74          | overtemperature trip level channels 7 to 4    | Y <u>[4]</u>       | AAh    | AAh      | AAh                    |

| 1Ah                          | IFSC_CH30                | full-scale reference current channels 3 to 0  | Y <u>[4]</u>       | AAh    | FFh      | FFh                    |

| 1Bh                          | IFSC_CH74                | full-scale reference current channels 7 to 4  | Y <u>[4]</u>       | AAh    | FFh      | FFh                    |

| 1Ch                          | CURR_TRIPLEV_CH0         | current trip level for channel 0              | N <mark>[4]</mark> | FFh    | FFh      | FFh                    |

| 1Dh                          | CURR_TRIPLEV_CH1         | current trip level for channel 1              | N <mark>[4]</mark> | FFh    | FFh      | FFh                    |

| 1Eh                          | CURR_TRIPLEV_CH2         | current trip level for channel 2              | N <mark>[4]</mark> | FFh    | FFh      | FFh                    |

| 1Fh                          | CURR_TRIPLEV_CH3         | current trip level for channel 3              | N <mark>[4]</mark> | FFh    | FFh      | FFh                    |

| 20h                          | CURR_TRIPLEV_CH4         | current trip level for channel 4              | N <mark>[4]</mark> | FFh    | FFh      | FFh                    |

| 21h                          | CURR_TRIPLEV_CH5         | current trip level for channel 5              | N <mark>[4]</mark> | FFh    | FFh      | FFh                    |

| 22h                          | CURR_TRIPLEV_CH6         | current trip level for channel 6              | N <mark>[4]</mark> | FFh    | FFh      | FFh                    |

| 23h                          | CURR_TRIPLEV_CH7         | current trip level for channel 7              | N <mark>[4]</mark> | FFh    | FFh      | FFh                    |

| 24h                          | IRQ_MAP                  | interrupt request mapping                     | Y <u>[4]</u>       | 04h    | 19h      | 00h                    |

| 25h                          | CURR_TRIP_<br>BLANKTIME  | current trip blanking time                    | Y <u>[4]</u>       | 2Fh    | 2Fh      | 2Fh                    |

| 26h                          | OLDET_ONOFF              | off-state open-circuit detection              | Ν                  | FFh    | FFh      | FFh                    |

#### Table 5. User-accessible registers

BUK3F00-50WDXX\_2

Product data sheet

**Controller for TrenchPLUS FETs**

| Table J. (              | Jsel-accessible registers |                                            |                    |                                      |     |     |

|-------------------------|---------------------------|--------------------------------------------|--------------------|--------------------------------------|-----|-----|

| Register <sup>[1]</sup> | Name                      | Description                                | Mask               | Version default value <sup>[2]</sup> |     |     |

|                         |                           |                                            | option             | FE                                   | FM  | FY  |

| 27h                     | READBACK                  | register and diagnostic read back          | Ν                  | 30h                                  | 30h | 30h |

| 28h                     | IRQ_CHAN_MAP              | interrupt generating channels              | N <mark>[4]</mark> | FFh                                  | FFh | FFh |

| Write-only r            | egisters <sup>[6]</sup>   |                                            |                    |                                      |     |     |

| 29h                     | CLEAR_CHAN_INTN           | clear channels and interrupt               |                    |                                      |     |     |

| 2Ah                     | CLEAR_WD                  | clear watchdog state                       |                    |                                      |     |     |

| Read-only r             | egisters <sup>[7]</sup>   |                                            |                    |                                      |     |     |

| 30h                     | DIAG_BASIC                | basic diagnostics                          |                    |                                      |     |     |

| 31h                     | DIAG_CTRL                 | controller diagnostics                     |                    |                                      |     |     |

| 32h                     | ISR                       | interrupt status register                  |                    |                                      |     |     |

| 33h                     | VERSION                   | device version number                      |                    |                                      |     |     |

| 34h                     | DIAG_CHAN_01              | VOUTHIGH and VOUTLOW states <sup>[8]</sup> |                    |                                      |     |     |

| 35h                     | DIAG_CHAN_02              | TSNSOPEN signal state <sup>[9]</sup>       |                    |                                      |     |     |

| 38h                     | DIAG_DETAIL_CH0           | detail diagnostics; channel 0              |                    |                                      |     |     |

| 39h                     | DIAG_DETAIL_CH1           | detail diagnostics; channel 1              |                    |                                      |     |     |

| 3Ah                     | DIAG_DETAIL_CH2           | detail diagnostics; channel 2              |                    |                                      |     |     |

| 3Bh                     | DIAG_DETAIL_CH3           | detail diagnostics; channel 3              |                    |                                      |     |     |

| 3Ch                     | DIAG_DETAIL_CH4           | detail diagnostics; channel 4              |                    |                                      |     |     |

| 3Dh                     | DIAG_DETAIL_CH5           | detail diagnostics; channel 5              |                    |                                      |     |     |

| 3Eh                     | DIAG_DETAIL_CH6           | detail diagnostics; channel 6              |                    |                                      |     |     |

| 3Fh                     | DIAG_DETAIL_CH7           | detail diagnostics; channel 7              |                    |                                      |     |     |

|                         |                           |                                            |                    |                                      |     |     |

#### Table 5. User-accessible registers ...continued

[1] This column denotes either the address used to write to the indicated register, or the data sent to register READBACK (27h) to read back from the indicated register.

[2] Default values for read/write registers are either fixed or programmable as mask options for individual types.

[3] 8-bit read/write registers store settings that control the behavior of the device. Default values are stored at power-on reset and data can be changed via SPI-bus communication. To help provide security of operation these registers can also be read back.

[4] Another metal mask option is available, which means that WRITE\_PROTECT is set. CHAN\_WD\_MAP and WD\_TO registers are write-protected by this option. The other registers indicated will be reloaded with default values if an SPI watchdog time-out occurs.

[5] Only bit 7 is mask programmable.

[6] 8-bit write-only registers clear tripped channels, interrupt and watchdog states when data is written. The values are not stored and cannot be read back.

[7] 16-bit read-only registers contain data about the state of the device for diagnostic use. Data cannot be written to these registers.

[8] VOUTHIGH: high-side FET is in on-state for overcurrent protection (> V<sub>th(on)(bat-KEL)</sub>).

VOUTLOW: high-side FET output voltage is below the voltage required for open-circuit detection (< V<sub>det(oc)off</sub>).

[9] TSNSOPEN: temperature sensor open-circuit.

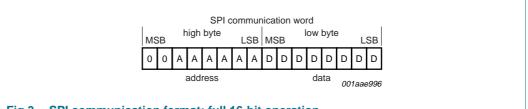

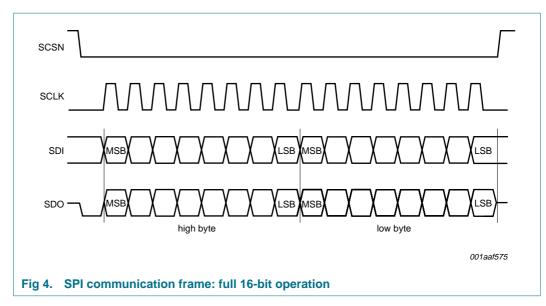

#### 9.3.2 Serial Peripheral Interface (SPI)

The SPI is used for communication with a controller and provides control and diagnostic functions. The device is configured as an SPI slave.

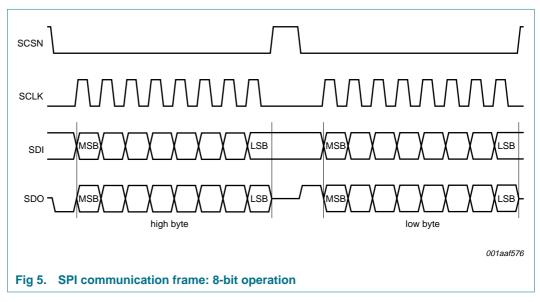

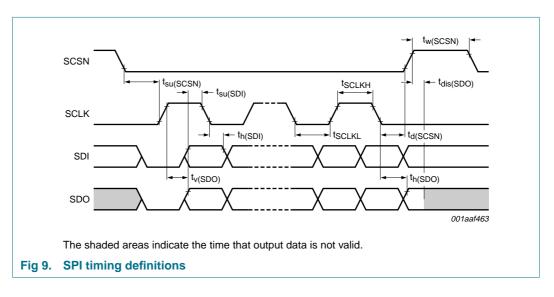

The interface consists of SPI Chip Select (SCSN), Serial Clock (SCLK), Serial Data In (SDI) and Serial Data Out (SDO). SPI communication is enabled when SCSN is set LOW. Data is shifted out to pin SDO on the SCLK rising edge. The data shifted out depends on which register is addressed by register READBACK (27h). Data is shifted in from pin SDI on the SCLK falling edge.

The controller can be timed to send data to SDI on the SCLK rising edge with data valid on the falling edge. Data is valid for reading on the falling edge. For full timing requirements; see <u>Table 25 "Recommended operating conditions"</u> and <u>Figure 9 "SPI timing definitions"</u>.

SPI communication uses 16-bit words; see <u>Figure 3</u>. The most significant byte, the register address byte, is transferred first. The 2 most significant bits of the register address byte are not used, they must always be logic 0. The 6 least significant bits form the actual register address.

Fig 3. SPI communication format; full 16-bit operation

When SCSN is set HIGH after a 16-bit valid communication, then the SDO output becomes inactive and goes to high-impedance. The data in the low byte is then transferred to the address given in the high byte. After this is completed the SPI shift register is refreshed with the latest contents of the register addressed by the entry in register READBACK. When 8-bit registers are read, the least significant byte is padded with 55h.

Data is checked for validity after SCSN goes HIGH. It is valid if the count of SCLK negative edges is a multiple of 8 and the address part (high byte) of the 16-bit message contains a valid address. An invalid address will result in a value of 00h being sent on SDO. To allow time for validity checking, writing data and refreshing the shift register, SCSN must be disabled (HIGH) for a period  $t_{w(SCSN)}$ .

**Controller for TrenchPLUS FETs**

To support 8-bit microcontrollers an 8-bit operation is possible; see <u>Figure 5</u>. In this operation, SCSN is taken HIGH between the 8-bit bytes. SDO is taken HIGH before the SCLK of the low byte to indicate that the low byte is to be sent.

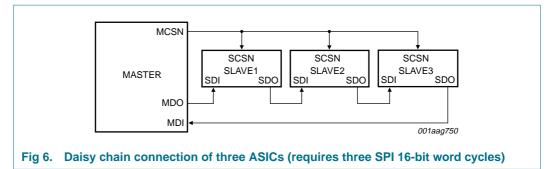

A number of devices can be daisy chained by connecting the SDO of the first device to the SDI of the next device and so on; see Figure 6.

All devices have their SCSN inputs connected to the same controller chip select so that they can be selected together. When n devices are daisy chained, then n SPI 16-bit word cycles must be executed to program all devices. Daisy chaining cannot be used with 8-bit SPI operation.

**Controller for TrenchPLUS FETs**

#### 9.3.3 SPI watchdog

The SPI watchdog detects if there is a breakdown in the SPI communication with the controller. A timer is activated that resets when a valid communication is received. If no valid SPI communications are received within the specified time-out period, the watchdog will signal this to the control logic.

The SPI watchdog is enabled either by setting pin WDEN = HIGH or by enabling watchdog active with bit WD\_TO[5]. FET channels can be turned either on or off when a watchdog time-out occurs as set by register CHAN\_WD\_MAP. Pin WDTON is set LOW for a selectable period when a watchdog time-out occurs and can be used as a reset for the controller. An interrupt on pin INTN can also be set when a watchdog time-out occurs.

Other functions of the device are not changed in Watchdog mode. In particular, if the SPI fault that caused the condition is resolved, SPI communication would work and diagnostics could be performed.

See <u>Section 11.1 "Reset for interrupt and SPI watchdog"</u> for details of clearing watchdog states.

| Table 6. | Select channel watchdog behavior register (address 0Ch) bit description |

|----------|-------------------------------------------------------------------------|

|----------|-------------------------------------------------------------------------|

| Address | Register                   | Bit    | Description                                                           |

|---------|----------------------------|--------|-----------------------------------------------------------------------|

| 0Ch     | CHAN_WD_MAP <sup>[1]</sup> | 7 to 0 | behavior when watchdog time-out occurs in individual channels 7 to 0: |

|         |                            |        | 1 = turn selected channel on <sup>[2]</sup>                           |

|         |                            |        | 0 = turn selected channel off                                         |

|         |                            |        |                                                                       |

[1] A metal mask option WRITE\_PROTECT is available, which means that registers are write protected.

[2] Provided channel is not mapped to a direct input pin. If channel is mapped to a direct input pin, then the channel will only turn on if the direct input pin is HIGH.

| Table 7. | Watchdog time-out period setting register (address 0Dh) bit description |        |                                       |  |  |  |

|----------|-------------------------------------------------------------------------|--------|---------------------------------------|--|--|--|

| Address  | Register Bit Description                                                |        |                                       |  |  |  |

| 0Dh      | WD_TO                                                                   | 7 to 6 | not used                              |  |  |  |

|          |                                                                         | 5      | enable watchdog                       |  |  |  |

|          |                                                                         | 4 to 0 | watchdog time-out period; see Table 8 |  |  |  |

| Time-out | t period |       |        |       |       |       |        |

|----------|----------|-------|--------|-------|-------|-------|--------|

| Value    | Time     | Value | Time   | Value | Time  | Value | Time   |

| 00h      | 1.0 ms   | 08h   | 4.1 ms | 10h   | 16 ms | 18h   | 66 ms  |

| 01h      | 1.3 ms   | 09h   | 5.1 ms | 11h   | 20 ms | 19h   | 82 ms  |

| 02h      | 1.5 ms   | 0Ah   | 6.1 ms | 12h   | 25 ms | 1Ah   | 98 ms  |

| 03h      | 1.8 ms   | 0Bh   | 7.2 ms | 13h   | 29 ms | 1Bh   | 115 ms |

| 04h      | 2.0 ms   | 0Ch   | 8.2 ms | 14h   | 33 ms | 1Ch   | 131 ms |

| 05h      | 2.6 ms   | 0Dh   | 10 ms  | 15h   | 41 ms | 1Dh   | 164 ms |

| 06h      | 3.1 ms   | 0Eh   | 12 ms  | 16h   | 49 ms | 1Eh   | 197 ms |

| 07h      | 3.6 ms   | 0Fh   | 14 ms  | 17h   | 57 ms | 1Fh   | 229 ms |

#### Table 8.Watchdog time-out period

Given times are valid for nominal master clock frequency.

#### 9.3.4 Pulse-Width Modulation (PWM)

PWM can be implemented on selected channels by either an internally generated signal or an externally connected signal.

For the internally generated signal, it is possible to select frequency and duty cycle and to synchronize the selected channels. The internally generated signal is used when the duty cycle is set to less than 100 %. For both internal and external PWM signals it is possible to specify the point at which the FET current is sampled in the PWM period.

An external PWM signal can be connected to the input pin INP (intended for normal PWM operation) or pins IN0 to IN3 (intended for fail-safe operation). The required channels are then mapped accordingly.

#### Table 9. PWM setting registers (addresses 09h, 0Ah, 0Fh, 10h to 17h) bit description

| Address    | Register                    | Bit    | Description                                                                                                                         |

|------------|-----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| 09h        | PWM_SYNC <sup>[1]</sup>     | 7 to 0 | PWM synchronization in individual channels 7 to 0:                                                                                  |

|            |                             |        | 1 = selected channel synchronized to previous channel in this mode                                                                  |

|            |                             |        | 0 = selected channel one eighth of internal PWM cycle out of phase                                                                  |

| 0Ah        | PWM_SAM_                    | 7 to 0 | PWM sample begin or end in individual channels 7 to 0 <sup>[2]</sup> :                                                              |

|            | BEGINEND                    |        | 1 = selected channel set to end                                                                                                     |

|            |                             |        | 0 = selected channel set to start                                                                                                   |

| 0Fh        | INT_PWM_FREQ <sup>[3]</sup> | 7 to 0 | internal PWM frequency setting for all channels:                                                                                    |

|            |                             |        | 00h to 3Fh: f = {code + 01h} $\times$ 0.125 Hz, from 0.125 Hz to 8.0 Hz in 0.125 Hz steps                                           |

|            |                             |        | 40h to 7Fh: f = {code $-$ 3Fh} $\times$ 0.5 Hz, from 0.5 Hz to 32.0 Hz, in 0.5 Hz steps                                             |

|            |                             |        | 80h to BFh: f = {code $-7Fh$ } × 2.0 Hz, from 2.0 Hz to 128.0 Hz, in 2.0 Hz steps                                                   |

|            |                             |        | C0h to FFh: f = {code – BFh} $\times$ 8.0 Hz, from 8.0 Hz to 512.0 Hz, in 8.0 Hz steps                                              |

| 10h to 17h | PWM_DC_CHn <sup>[3]</sup>   | 7 to 0 | internal PWM duty cycle for specified channel 7 to 0; duty cycle $\delta$ = (n + 1) / 256, where n = decimal number set in register |

|            |                             |        |                                                                                                                                     |

[1] If channels are run out-of-phase each will be staggered by one eighth of a PWM cycle. When more than one channel is selected by this command then the master signal is the channel with the lowest number. This does not apply to the external PWM signal on pin INP.

[2] Controls the point of the on-time at which the current is sampled for digital current measurement. Only operates when duty cycle is set to < 100 % or channel is mapped to pin INP.

[3] A metal mask option WRITE\_PROTECT is available which means that this register is reloaded with the default value if an SPI watchdog time-out occurs.

The PWM frequency can be monitored by making this an output on pin PWMMON. This is a controller setting; see <u>Section 9.5.5 "Controller settings</u>".

#### 9.3.5 Interrupt

An interrupt can be generated to notify a controller of an error condition. An interrupt will set pin INTN = LOW. Register settings define which faults can generate an interrupt and which FET channels can generate an interrupt for these faults.

Address Register Bit Description 24h IRQ MAP<sup>[1]</sup> interrupt request mapping; for each bit: 1 = INTN active 0 = INTN not active 7 invalid SPI communication 6 open-circuit 5 controller fault (charge pump fault or V<sub>BAT</sub> low) 4 temperature sensor diode open-circuit 3 watchdog time-out 2 channel overcurrent (threshold reached or exceeded) 1 channel overtemperature (threshold exceeded) 0 channel tripped under fault condition 28h IRQ\_CHAN\_MAP[1] 7 to 0 interrupt generation in individual channels 7 to 0: 1 = selected channel can generate interrupt 0 = selected channel cannot generate interrupt

Table 10.

Interrupt setting registers (addresses 24h, 28h) bit description

[1] A metal mask option WRITE\_PROTECT is available, which means that this register is reloaded with the default value if an SPI watchdog time-out occurs.

When an interrupt is generated, data in the interrupt status register will indicate the cause. See <u>Section 11.1 "Reset for interrupt and SPI watchdog"</u> for details of reading and clearing interrupt data.

#### 9.4 Current measurement

The current measurement is able to monitor the current from the sense connections of the TrenchPLUS FETs. This is achieved by using one current measurement circuit for each channel. The current measurement circuits control conditions at the sense pin of each FET channel and can produce either an analog or digital measurement output. The digital output can be read by a controller.

The current measurement circuit monitors the sense current according to the sense ratio of the TrenchPLUS FET. This ratio is only valid when the sense and main FETs of the TrenchPLUS device are fully active with V<sub>GS</sub> at about 4 V or greater, and with the same V<sub>GS</sub>.

#### 9.4.1 Current measurement circuits

For FET channels configured as high-side switches, the sense current is pulled from the sense connection. This current is adjusted until the voltage measured at the FET pin kelvin is the same as that measured at the FET pin sense. Since the main and sense

devices have common drain connections, the  $V_{DS}$  of the two devices are equal, and the correct sense current is being pulled. Current measurement is only possible when the voltage on pin KELVIN is above the  $V_{th(on)(bat-KEL)}$  threshold.

#### 9.4.2 Analog current measurement output

An analog current can be output on pin IMEAS that is proportional to the sense current measured on a selected FET channel. Any single channel can be multiplexed to this output at a time.

The accuracy and resolution of analog current measurement is determined by the voltage across the R<sub>IMEAS</sub> resistor with the measurement output current and the measurement range used. The measurement current is given by I<sub>meas</sub> = (I<sub>SENSE</sub> / I<sub>meas(ADC)(fs)</sub>) × 100  $\mu$ A, where I<sub>SENSE</sub> is the FET sense current and I<sub>meas(ADC)(fs)</sub> is the set full-scale current for the measurement range. For reliable current measurement, the voltage on pin IMEAS must be less than the measurement supply voltage on pin V<sub>CC(MEASC)</sub>. A resistor value giving high resolution at low measurement output current (for example, up to I<sub>meas(ADC)(fs)</sub>) may not provide the range for high measurement output current (for example, up to 8 × I<sub>meas(ADC)(fs)</sub>). Conversely, a value giving the range for high measurement current will give less resolution for low measurement current.

When the selected channel uses PWM, the analog measurement is able to follow the switched waveform, except when the duty cycle is very low, and high-side FETs are in the turn-on state. The voltage on pin IMEAS is limited just below the measurement supply voltage.

|         | •         |        | 5 ( , , , , , , , , , , , , , , , , , ,                                          |

|---------|-----------|--------|----------------------------------------------------------------------------------|

| Address | Register  | Bit    | Description                                                                      |

| 06h     | CURR_MEAS | 7 to 4 | not used; must be set to logic 0                                                 |

|         |           | 3      | current measurement setting:                                                     |

|         |           |        | 1 = enables current measurement in selected channel                              |

|         |           |        | 0 = disables current measurement in all channels                                 |

|         |           | 2 to 0 | selects measurement channel; binary value corresponds to channel number (0 to 7) |

Table 11. Analog current channel selection register (address 06h) bit description

#### 9.4.3 Digital current measurement output

8-bit successive approximation ADCs are used to measure the sense currents of the FET channels. The measured values are only considered valid when the FET has been on for the full conversion cycle. Digital measurements are stored and can be read by a controller. The reading from the ADC may not indicate zero if the channel is requested off. If PWM is not selected, the values are stored every ADC cycle. For PWM the digital measurement can be sampled at the start or end of the on time.

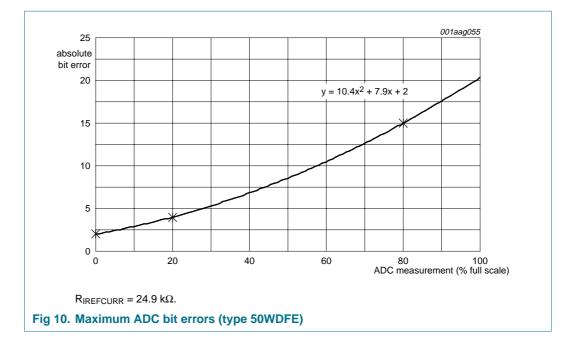

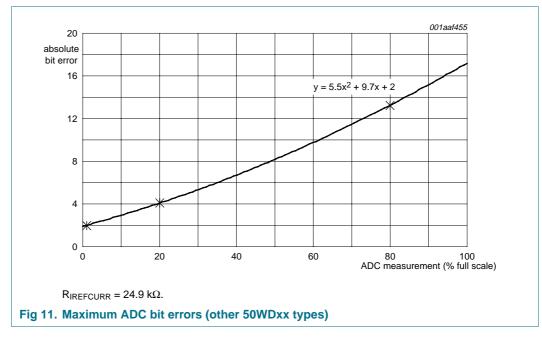

The ADC reading, up to the maximum 255 bits, is given by: reading =  $255 \times (I_{SENSE} / I_{meas(ADC)(fs)}) \times (50 \ \mu\text{A} / I_{IREFCURR})$ , where  $I_{IREFCURR}$  is the current through the current reference resistor ( $R_{IREFCURR}$ ). At  $I_{IREFCURR} = 50 \ \mu\text{A}$  this equation simplifies to give a direct relationship with the analog measurement current.

#### 9.4.4 Low battery supply voltage conditions

The current measurement interface operates at voltages very near the battery voltage. To permit reasonable headroom in the circuit, the current measurement interface is powered from the charge pump. The circuit cannot operate correctly when it is close to ground, as

BUK3F00-50WDXX 2

© NXP B.V. 2008. All rights reserved.

occurs in very low battery conditions. The current measurement interface may be non-functional, or may have degraded accuracy under low (out-of-specification) charge pump conditions.

#### 9.5 TrenchPLUS FET interface

The FET interface provides channel switching (on and off) and protection with the following features, described in priority order.

#### 9.5.1 Overtemperature protection

Overtemperature protection is adjusted by selecting the trip level of the temperature sense diode for each channel. To relate this to actual trip temperature, refer to the specification of the specific TrenchPLUS FET devices. Overtemperature protection can also be set to auto-reset with hysteresis (to reduce the possibility of repeated resets when the temperature remains high) or to latch on fault. The device also detects and reports a fault if the connection to a temperature sense diode is open-circuit.

Table 12. Overtemperature protection setting registers (addresses 08h, 18h, 19h) bit

|         | description                        |        |                                                                                                       |

|---------|------------------------------------|--------|-------------------------------------------------------------------------------------------------------|

| Address | Register                           | Bit    | Description                                                                                           |

| 08h     | CHAN_OT_FAULT_                     | 7 to 0 | overtemperature fault clear in channels 3 to 0:                                                       |

|         | CLR <sup>[1]</sup>                 |        | 1 = selected channel set to auto reset with hysteresis                                                |

|         |                                    |        | 0 = selected channel set to latches on fault                                                          |

| 18h     | OT_TRIPLEV_<br>CH30 <sup>[1]</sup> |        | set overtemperature trip level in channels 3 to 0 to one of four voltage trip levels <sup>[2]</sup> : |

|         |                                    |        | 00 = 2.31 V                                                                                           |

|         |                                    |        | 01 = 2.25 V                                                                                           |

|         |                                    |        | 10 = 2.16 V                                                                                           |

|         |                                    |        | 11 = 2.00 V                                                                                           |

|         |                                    | 7, 6   | channel 3 temperature sense diode threshold voltage                                                   |

|         |                                    | 5, 4   | channel 2 temperature sense diode threshold voltage                                                   |

|         |                                    | 3, 2   | channel 1 temperature sense diode threshold voltage                                                   |

|         |                                    | 1, 0   | channel 0 temperature sense diode threshold voltage                                                   |

| 19h     | OT_TRIPLEV_<br>CH74 <sup>[1]</sup> |        | set overtemperature trip level in channels 7 to 4 to one of four voltage trip levels <sup>[2]</sup> : |

|         |                                    |        | 00 = 2.31 V                                                                                           |

|         |                                    |        | 01 = 2.25 V                                                                                           |

|         |                                    |        | 10 = 2.16 V                                                                                           |

|         |                                    |        | 11 = 2.00 V                                                                                           |

|         |                                    | 7, 6   | channel 7 temperature sense diode threshold voltage                                                   |

|         |                                    | 5, 4   | channel 6 temperature sense diode threshold voltage                                                   |

|         |                                    | 3, 2   | channel 5 temperature sense diode threshold voltage                                                   |

|         |                                    | 1, 0   | channel 4 temperature sense diode threshold voltage                                                   |

[1] A metal mask option WRITE\_PROTECT is available which means that this register is reloaded with the default value if an SPI watchdog time-out occurs.

[2] Nominal trip voltages quoted for each trip level. Refer to data sheet for TrenchPLUS FET devices for equivalent temperature measurement.

BUK3F00-50WDXX 2

#### 9.5.2 Overcurrent protection

The overcurrent protection on each channel allows for high inrush currents. This protection also allows for turn-on or transient low battery conditions that can occur with the configuration of high-side FET switches. Delay time in operating overcurrent protection is determined by the actual FET.

For high-side switches, FET turn-on is determined when the sense voltage exceeds the sense low threshold voltage ( $V_{th(sense)low}$ ), within 40  $\mu$ s (nominal), and when the battery-to-kelvin voltage exceeds the on-state threshold voltage between the battery and pin KELVIN ( $V_{th(on)(bat-KEL)}$ ).

The following overcurrent protection is available:

**Turn-on overcurrent trip (TONOCH)** — For channels configured as high-side switches. Operates during FET turn-on or transient low battery conditions. The threshold level is a set multiple of  $I_{meas(ADC)(fs)} \times (I_{IREFCURR} / 50 \ \mu\text{A})$ . This is simplified when  $I_{IREFCURR} = 50 \ \mu\text{A}$ . For low current sense voltage (< 2.5 V) the trip level is below the specified multiple of  $I_{meas(ADC)(fs)}$ . This protection cannot be disabled.

**Overcurrent high trip (OCH)** — For channels configured as high-side switches. This does not operate during FET turn-on or transient low battery conditions. The threshold level is a set multiple of  $I_{meas(ADC)(fs)} \times (I_{IREFCURR} / 50 \ \mu A)$ . This is simplified when  $I_{IREFCURR} = 50 \ \mu A$ . This protection cannot be disabled or delayed.

**Overcurrent low trip (OCL)** — Operates at set currents of the ADC output up to  $I_{meas(ADC)(fs)}$  with the ADC measurement accuracy. The threshold level is set by register CURR\_TRIPLEV\_CHn. This protection can be disabled or delayed.

| Table 13. | FET channel protection set<br>description | FET channel protection setting registers (addresses 07h, 1Ah to 23h, 25h) bit description |                                                                                          |  |  |  |  |  |

|-----------|-------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|--|

| Address   | Register                                  | Bit                                                                                       | Description                                                                              |  |  |  |  |  |

| 07h       | SEL_CURR_TRIP_CHAN <sup>[1]</sup>         | 7 to 0                                                                                    | select current tripping for OCL in individual channels 7 to 0:                           |  |  |  |  |  |

|           |                                           |                                                                                           | 1 = selected                                                                             |  |  |  |  |  |

|           |                                           |                                                                                           | 0 = not selected                                                                         |  |  |  |  |  |

| 1Ah       | IFSC_CH30 <sup>[1]</sup>                  |                                                                                           | set $I_{meas(ADC)(fs)}$ data bits in channels 3 to 0 to one of four current trip levels: |  |  |  |  |  |

|           |                                           |                                                                                           | 00 = 0.5 mA                                                                              |  |  |  |  |  |

|           |                                           |                                                                                           | 01 = 1.0 mA                                                                              |  |  |  |  |  |

|           |                                           |                                                                                           | 10 = 1.5 mA                                                                              |  |  |  |  |  |

|           |                                           |                                                                                           | 11 = 2.0 mA                                                                              |  |  |  |  |  |

|           |                                           | 7, 6                                                                                      | set channel 3 full-scale current bits 1 and 0                                            |  |  |  |  |  |

|           |                                           | 5, 4                                                                                      | set channel 2 full-scale current bits 1 and 0                                            |  |  |  |  |  |

|           |                                           | 3, 2                                                                                      | set channel 1 full-scale current bits 1 and 0                                            |  |  |  |  |  |

|           |                                           | 1, 0                                                                                      | set channel 0 full-scale current bits 1 and 0                                            |  |  |  |  |  |

#### **Controller for TrenchPLUS FETs**

|               | description continued           |        |                                                                                                 |

|---------------|---------------------------------|--------|-------------------------------------------------------------------------------------------------|

| Address       | Register                        | Bit    | Description                                                                                     |

| 1Bh           | IFSC_CH74[1]                    |        | set I <sub>meas(ADC)(fs)</sub> data bits in channels 7 to 4 to one of four current trip levels: |

|               |                                 |        | 00 = 0.5 mA                                                                                     |

|               |                                 |        | 01 = 1.0 mA                                                                                     |

|               |                                 |        | 10 = 1.5 mA                                                                                     |

|               |                                 |        | 11 = 2.0 mA                                                                                     |

|               |                                 | 7, 6   | set channel 7 full-scale current bits 1 and 0                                                   |

|               |                                 | 5, 4   | set channel 6 full-scale current bits 1 and 0                                                   |

|               |                                 | 3, 2   | set channel 5 full-scale current bits 1 and 0                                                   |

|               |                                 | 1, 0   | set channel 4 full-scale current bits 1 and 0                                                   |

| 1Ch to<br>23h | CURR_TRIPLEV_CHn <sup>[1]</sup> | 7 to 0 | overcurrent trip threshold in channels 7 to 0; each bit represents $I_{meas(ADC)(fs)}$ / 255    |

| 25h           | CURR_TRIP_BLANKTIME             | 7, 6   | not used: must be set to logic 0                                                                |

|               |                                 | 5 to 0 | set overcurrent trip blanking time; see Table 14                                                |

|               |                                 |        |                                                                                                 |

# Table 13. FET channel protection setting registers (addresses 07h, 1Ah to 23h, 25h) bit description ...continued

[1] A metal mask option WRITE\_PROTECT is available, which means that this register is reloaded with the default value if an SPI watchdog time-out occurs.

| Blanking | 3       |       |         |       |        |       |        |

|----------|---------|-------|---------|-------|--------|-------|--------|

| Value    | Time    | Value | Time    | Value | Time   | Value | Time   |

| 00h      | 0 ms    | 0Ch   | 0.51 ms | 18h   | 4.1 ms | 24h   | 33 ms  |

| 01h      | 0.08 ms | 0Dh   | 0.64 ms | 19h   | 5.1 ms | 25h   | 41 ms  |

| 02h      | 0.10 ms | 0Eh   | 0.77 ms | 1Ah   | 6.1 ms | 26h   | 49 ms  |

| 03h      | 0.11 ms | 0Fh   | 0.90 ms | 1Bh   | 7.2 ms | 27h   | 57 ms  |

| 04h      | 0.13 ms | 10h   | 1.0 ms  | 1Ch   | 8.2 ms | 28h   | 66 ms  |

| 05h      | 0.16 ms | 11h   | 1.3 ms  | 1Dh   | 10 ms  | 29h   | 82 ms  |

| 06h      | 0.19 ms | 12h   | 1.5 ms  | 1Eh   | 12 ms  | 2Ah   | 98 ms  |

| 07h      | 0.22 ms | 13h   | 1.8 ms  | 1Fh   | 14 ms  | 2Bh   | 115 ms |

| 08h      | 0.26 ms | 14h   | 2.0 ms  | 20h   | 16 ms  | 2Ch   | 131 ms |

| 09h      | 0.32 ms | 15h   | 2.6 ms  | 21h   | 20 ms  | 2Dh   | 164 ms |

| 0Ah      | 0.38 ms | 16h   | 3.1 ms  | 22h   | 25 ms  | 2Eh   | 197 ms |

| 0Bh      | 0.45 ms | 17h   | 3.6 ms  | 23h   | 29 ms  | 2Fh   | 229 ms |

|          |         |       |         |       |        |       |        |

#### Table 14. Overcurrent low trip blanking time

-- . . .

#### 9.5.3 Gate inductive ring-off clamp

For high-side switches an inductive ring-off clamp can provide gate-source voltage to allow conduction through the FET. This protects the FET by reducing the possibility of high drain-source voltages when turning off current to an inductive load. The gate is initially set to the source voltage to turn the FET off. During turn-off an inductive load will force the source voltage negative and the gate will follow this until the voltage between gate and ground reaches the inductive ring-off clamp voltage V<sub>CL</sub>. As the source voltage continues negative, the gate-to-source voltage will increase, turning the FET on and allowing conduction through the FET and preventing excessive voltage between drain and source.

The negative voltage on the source then forces current in the inductive load to reduce rapidly to zero. As the source voltage returns to ground, the gate-source voltage becomes zero and the FET is turned off.

#### 9.5.4 Loss-of-ground protection

A loss-of-ground condition can occur if the ground connection for the circuit is disconnected with the load ground still connected. With the FET off, it is possible for the ground voltage to drift up to battery voltage with the FET source voltage still held at ground. A resistance between pins GATE and KELVIN will hold the FET off provided the inductive ring-off clamp voltage V<sub>CL</sub> between gate and ground is not exceeded, otherwise the FET will start to turn on. Hence, loss of ground protection can only be guaranteed when V<sub>BAT</sub> <  $|V_{CL}|$ .

#### 9.5.5 Controller settings

It is possible to select a low switching rate for high-side switches at the beginning of turn-on and at the end of turn-off. This switching option improves EMC in the high-side switching application.

The PWM frequency can be monitored on pin PWMMON. This output has a 50 % duty cycle.

| Register<br>CTRL_SET <sup>[1]</sup> | <b>Bit</b><br>7 to 4 | Description<br>not applicable; set to logic 0                |

|-------------------------------------|----------------------|--------------------------------------------------------------|

| CTRL_SET <sup>[1]</sup>             | 7 to 4               | not applicable: set to logic 0                               |

|                                     |                      |                                                              |

|                                     | 3                    | sets switching rate at start of turn-on and end of turn-off: |

|                                     |                      | 1 = low switching rate                                       |

|                                     |                      | 0 = high switching rate                                      |

|                                     | 2                    | PWM signal on pin PWMMON:                                    |

|                                     |                      | 1 = available                                                |

|                                     |                      | 0 = not available <sup>[2]</sup>                             |

|                                     | 1 to 0               | not used; must be set to logic 0                             |

|                                     |                      |                                                              |

#### Table 15. Controller settings register (address 0Eh) bit description

[1] A metal mask option WRITE\_PROTECT is available which means that this register is reloaded with the default value if an SPI watchdog time-out occurs.

[2] When signal not available, this pin goes to 0 V.

#### 9.5.6 Open-circuit detection

Open-circuit is normally detected when switches are in the on-state. The ADC checks that at least a minimal current is flowing through the sense circuit. The threshold level is determined by the setting DIG\_OLTH[3:0] and is a mask option.

For high-side switches it is possible to detect an open-circuit in the off-state. The FET kelvin source voltage is monitored with a current  $I_{det(oc)off}$  and an open-circuit is reported if the threshold voltage  $V_{det(oc)off}$  is exceeded after a nominal 192  $\mu$ s delay. This off-state open-circuit detection is independent of on-state open-circuit detection. For high-side switches in the off-state, it is also possible to detect when the voltage between pin KELVIN and  $V_{BAT}$  is less than  $V_{th(on)(bat-KEL)}$  (a short-circuit).

#### **Controller for TrenchPLUS FETs**

| Table 16. | Off-state open- | Off-state open-circuit detection register (address 26h) bit description |                                                                                |  |  |  |  |

|-----------|-----------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| Address   | Register        | Bit                                                                     | Description                                                                    |  |  |  |  |

| 26h       | OLDET_ONOFF     | 7 to 0                                                                  | off-state open-circuit detection <sup>[1]</sup> in individual channels 7 to 0: |  |  |  |  |

|           |                 |                                                                         | 1 = off-state open-circuit detection enabled in selected<br>channel            |  |  |  |  |

|           |                 |                                                                         | 0 = off-state open-circuit detection disabled in selected<br>channel           |  |  |  |  |

[1] For high-side switches only.

#### 9.5.7 Channel selection

Channel selection allows the FET channels to be switched on directly.

| Table 17. | Channel selection register (address 01h) bit description          |  |                          |  |  |  |

|-----------|-------------------------------------------------------------------|--|--------------------------|--|--|--|

| Address   | Register Bit Description                                          |  |                          |  |  |  |

| 01h       | CHAN_ONOFF 7 to 0 direct switch-on of individual channels 7 to 0: |  |                          |  |  |  |

|           |                                                                   |  | 1 = selected channel on  |  |  |  |

|           |                                                                   |  | 0 = selected channel off |  |  |  |

#### 9.5.8 Mapping channels for direct channel control and PWM

Channels can be mapped to the input pin INP (intended for an external PWM signal) or to pins IN0 to IN3 for direct control (intended for fail-safe channel control by connection to  $V_{CC(LOG)EXT}$  and GND, or an external PWM signal). All channels (0 to 7) can be mapped to pin INP. Channels 0 to 3 can be mapped to pins IN0 and IN1. Channels 4 to 7 can be mapped to pins IN2 and IN3. Input pins IN0 plus IN1 and IN2 plus IN3 are combined according to the AND/OR operation. If a channel is switched on (by register CHAN\_ONOFF), the channel is switched on irrespective of the state on the direct input pins IN0 to IN3; see Section 9.5.7.

|         | description                |        |                                           |

|---------|----------------------------|--------|-------------------------------------------|

| Address | Register                   | Bit    | Description                               |

| 02h     | IN02_MAP <sup>[1][2]</sup> |        | direct input pins IN0 and IN2 mapping:    |

|         |                            |        | 1 = mapped                                |

|         |                            |        | 0 = not mapped                            |

|         |                            | 7 to 4 | map individual channels 7 to 4 to pin IN2 |

|         |                            | 3 to 0 | map individual channels 3 to 0 to pin IN0 |

| 03h     | IN13_MAP <sup>[1][2]</sup> |        | direct input pins IN1 and IN3 mapping:    |

|         |                            |        | 1 = mapped                                |

|         |                            |        | 0 = not mapped                            |

|         |                            | 7 to 4 | map individual channels 7 to 4 to pin IN3 |

|         |                            | 3 to 0 | map individual channels 3 to 0 to pin IN1 |

| 04h     | INP_MAP <sup>[2]</sup>     | 7 to 0 | direct input pin INP map channels 7 to 0: |

|         |                            |        | 1 = mapped                                |

|         |                            |        | 0 = not mapped                            |

|         |                            |        |                                           |

| Table 18. | Channel selection and pin mapping register (addresses 02h to 05h) bit |

|-----------|-----------------------------------------------------------------------|

|           | description                                                           |

#### Controller for TrenchPLUS FETs

|         | descriptioncontinu       |        |                                                                  |  |  |

|---------|--------------------------|--------|------------------------------------------------------------------|--|--|

| Address | Register                 | Bit    | Description                                                      |  |  |

| 05h     | ANDOR_MAP <sup>[1]</sup> |        | direct input pin AND/OR operation                                |  |  |

|         |                          | 7 to 4 | direct input AND/OR operation for individual<br>channels 7 to 4: |  |  |

|         |                          |        | 1 = pin IN2 AND pin IN3                                          |  |  |

|         |                          |        | 0 = pin IN2 OR pin IN3                                           |  |  |

|         |                          | 3 to 0 | direct input AND/OR operation for individual<br>channels 3 to 0: |  |  |

|         |                          |        | 1 = pin IN0 AND pin IN1                                          |  |  |

|         |                          |        | 0 = pin IN0 OR pin IN1                                           |  |  |

#### Channel selection and pin mapping register (addresses 02h to 05h) bit Table 18.

[1] A metal mask option WRITE PROTECT is available, which means that these registers are reloaded with the default value if an SPI watchdog time-out occurs.

In Watchdog mode; pins IN0 to IN3 reset channel faults (such as short-circuit) when the pin is set to LOW; [2] Pin INP does not reset channel faults. Hence, it is not recommended that an external PWM signal is connected to pins IN0 to IN3 for normal operation.

#### 9.5.9 FET channel on/off control

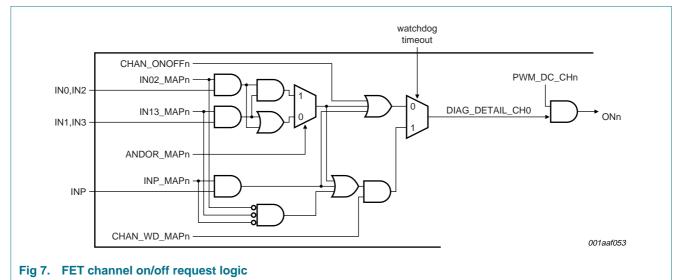

Each FET channel can be switched by a request from different sources, the logical relationship between these sources is shown in Figure 7.

#### 9.5.10 Power dissipation