# L6740L

# Hybrid controller (4+1) for AMD SVID and PVID processors

### Features

- Hybrid controller: compatible with PVI and SVI CPUs

- Dual controller: 2 to 4 scalable phases for CPU CORE, 1 Phase for NB

- Dual-Edge asynchronous architecture with LTB technology<sup>TM</sup>

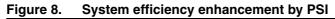

- PSI management to increase efficiency in Light-Load conditions

- Dual Over-Current protection: Average and per-Phase

- Load indicator (CORE section)

- Voltage positioning

- Dual remote sense

- Adjustable independent reference offset

- Feedback disconnection protection

- Programmable OV protection

- Oscillator internally fixed at 150kHz externally adjustable

- LSLess startup to manage Pre-biased output

- Flexible driver support

- HTQFP48 package

## Applications

- Hybrid High-Current VRM / VRD for Desktop / Server / Workstation / IPC CPUs supporting PVI and SVI interface

- High-density DC / DC converters

## Description

L6740L is a hybrid CPU Power Supply Controller compatible with both Parallel (PVI) and Serial (SVI) protocols for AMD Processors.

The device embeds two independent control loops for the CPU core and the integrated NB, each one with its own set of protections. L6740L is able to work in Single-Plane mode, addressing only the CORE Section, according to the parallel DAC codification. When in Dual-Plane mode, it is compatible with the AMD SVI specification addressing the CPU and NB voltages according to the SVI bus commands.

The Dual-Edge Asynchronous Architecture is optimized by LTB technology<sup>TM</sup> allowing fast load-transient response minimizing the output capacitor and reducing the total BOM cost.

PSI management allows the device to selectively turn-off phases when the CPU is in low-power states increasing the over-all efficiency.

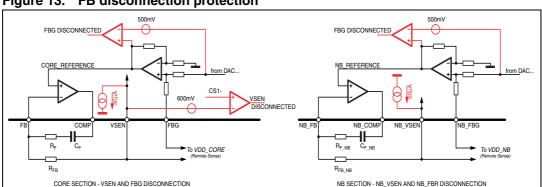

Fast protection against load over current is provided for both the Sections. Furthermore, feedback disconnection protection prevents from damaging the load in case of misconnections in the system board..

| Order codes | Package | Packaging     |

|-------------|---------|---------------|

| L6740L      | HTQFP48 | Tube          |

| L6740LTR    | HTQFP48 | Tape and reel |

#### Table 1. Device summary

| 4                |

|------------------|

| 4                |

| 7                |

| 8                |

| 8                |

| . 12             |

| . 13             |

| . 13             |

| . 13             |

| . 15             |

| . 16             |

| . 16             |

| . 16             |

| . 18             |

| . 18             |

| . 18             |

| . 21             |

| . 21             |

| . 22             |

| . 22             |

| . 23             |

| . 24             |

| . 24             |

| . 25             |

| . 26             |

| . 26             |

| . 27             |

| . 27             |

| -<br>-<br>-<br>- |

57

|    | 6.8    | NB section - Maximum Duty-Cycle limitation |

|----|--------|--------------------------------------------|

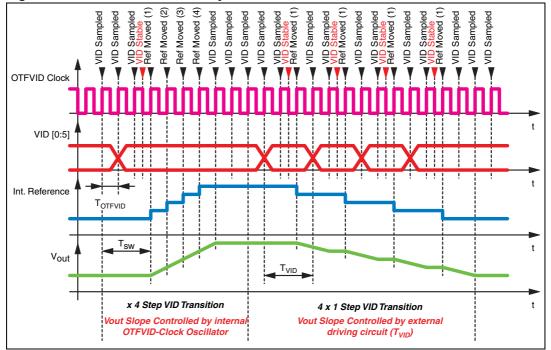

|    | 6.9    | On-The-Fly VID transitions                 |

|    | 6.10   | Soft-start                                 |

|    |        | 6.10.1 LS-Less Start-up                    |

| 7  | Outpu  | ut voltage monitoring and protections      |

|    | 7.1    | Programmable over voltage 31               |

|    | 7.2    | Feedback disconnection                     |

|    | 7.3    | PWRGOOD                                    |

|    | 7.4    | Over-current                               |

|    |        | 7.4.1 CORE section                         |

|    |        | 7.4.2 NB section                           |

| 8  | Main   | oscillator                                 |

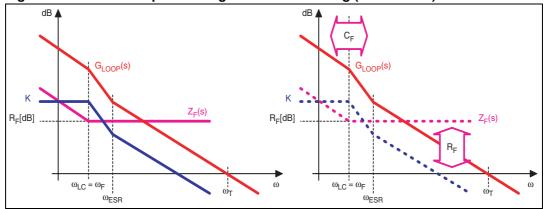

| 9  | Syste  | m control loop compensation                |

|    | 9.1    | Compensation network guidelines            |

| 10 | LTB to | echnology™                                 |

| 11 | Layou  | ut guidelines                              |

|    | 11.1   | Power components and connections 41        |

|    | 11.2   | Small signal components and connections    |

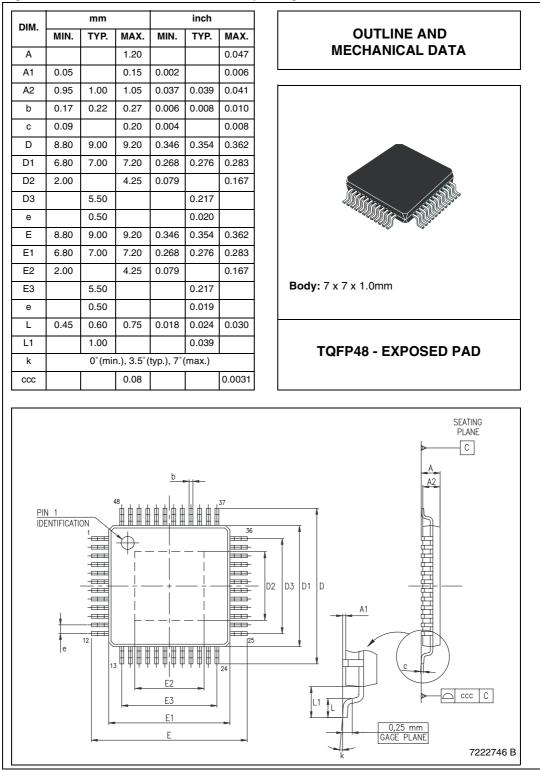

| 12 | TQFP   | 48 mechanical data & package dimensions    |

| 13 | Revis  | ion history                                |

57

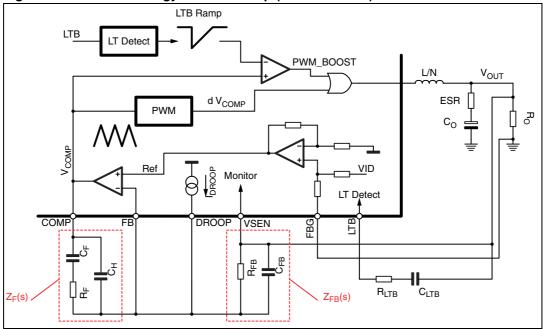

# **1** Typical application circuit and block diagram

## **1.1** Application circuit

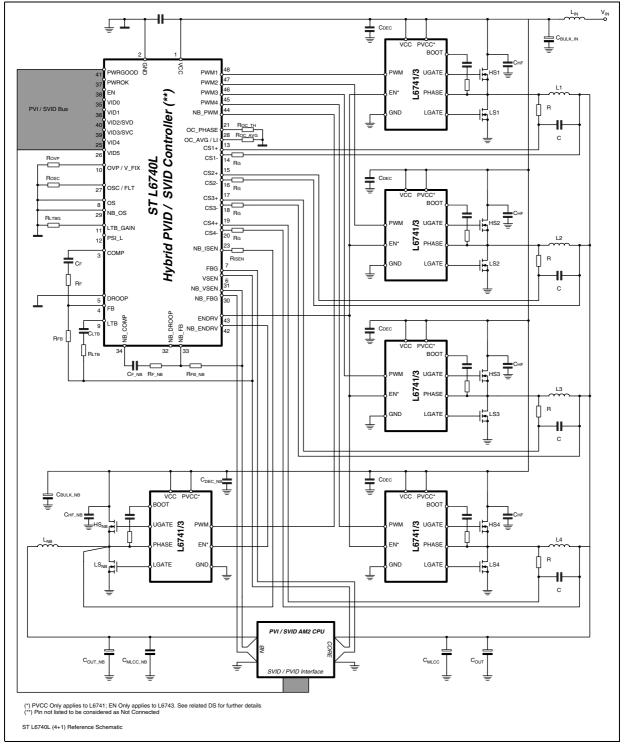

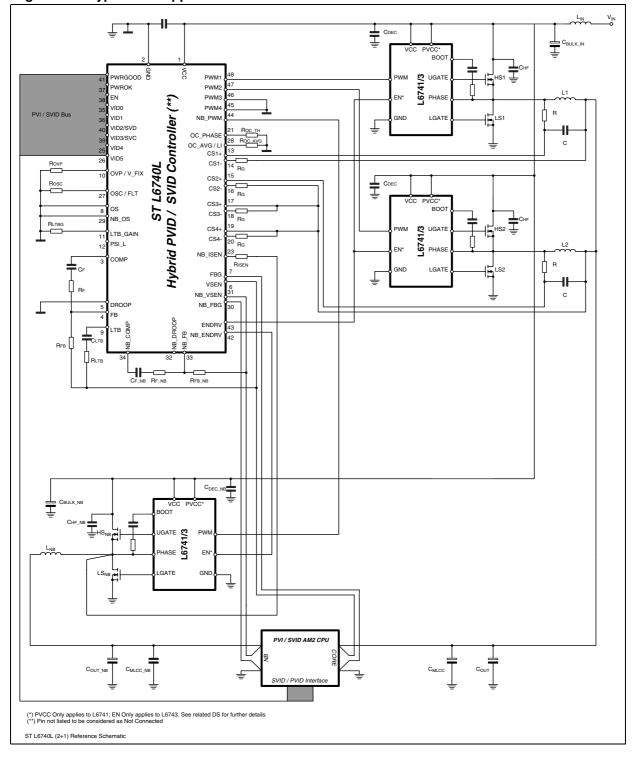

#### Figure 1. Typical 4+1 application circuit

Figure 2. Typical 3+1 application circuit

Figure 3. Typical 2+1 application circuit

### L6740L

## 1.2 Block diagram

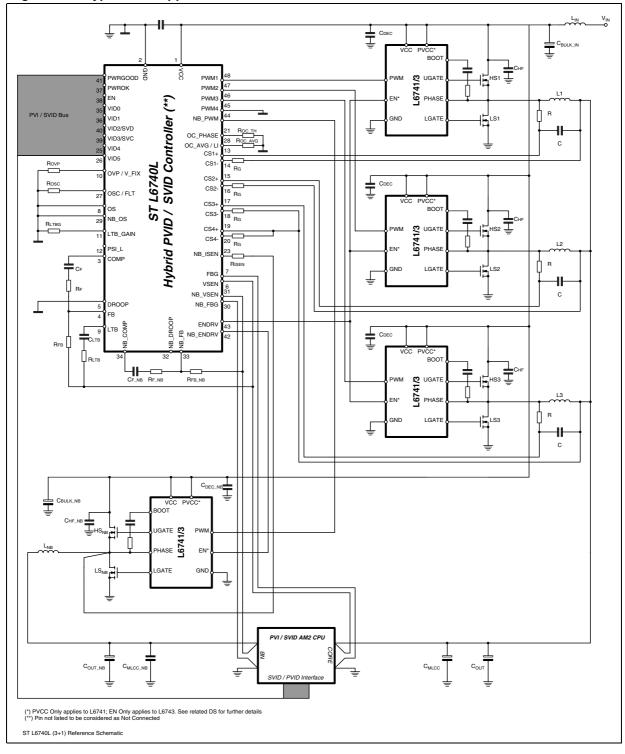

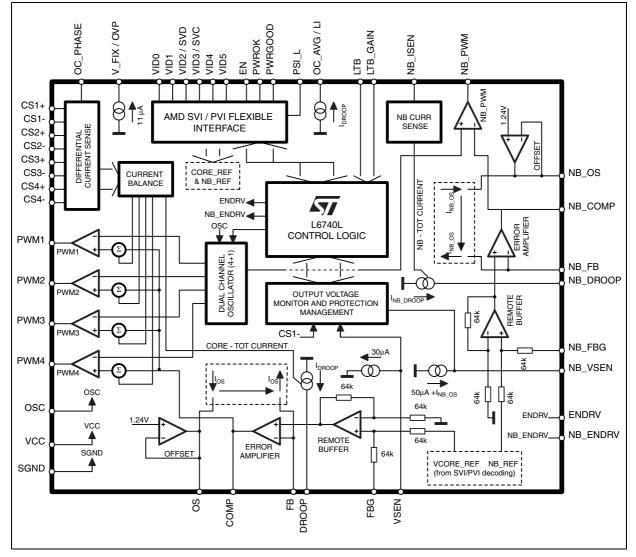

#### Figure 4. Block diagram

57

# 2 Pins description and connection diagrams

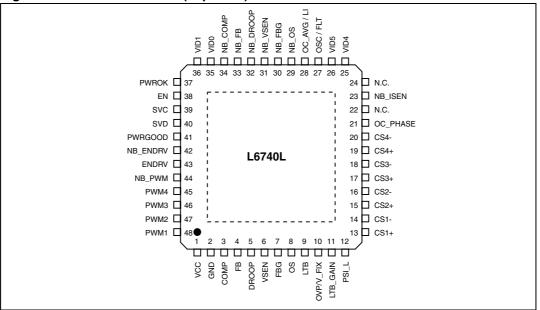

#### Figure 5. Pins connection (Top View)

## 2.1 Pin descriptions

| Pi                                                                                                                                                                                         | n#      | Name  | Function                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $1 \qquad \qquad \text{VCC} \qquad \begin{array}{c} \text{Device power supply.} \\ \text{Operative voltage is 12V } \pm 15\%. \text{ Filter with } 1\mu\text{F MLCC to SGND.} \end{array}$ |         |       |                                                                                                                                                                                          |

| 2                                                                                                                                                                                          | 2       | SGND  | All the internal references are referred to this pin. Connect to the PCB Signal Ground.                                                                                                  |

| 3                                                                                                                                                                                          |         | COMP  | Error amplifier output. Connect with an $\rm R_F$ - $\rm C_F$ to FB. The CORE section or the device cannot be disabled by grounding this pin.                                            |

| 4                                                                                                                                                                                          | SECTION | FB    | Error amplifier inverting input. Connect with a resistor $R_{FB}$ to VSEN and with an $R_{F}$ - $C_{F}$ to COMP. Offset current programmed by OS is sunk through this pin.               |

| 5                                                                                                                                                                                          | CORE S  | DROOP | A current proportional to the total current read is sourced from this pin according to the Current Reading Gain.<br>Short to FB to implement Droop Function, if not used, short to SGND. |

| 6 VSEN                                                                                                                                                                                     |         | VSEN  | Output voltage monitor.<br>It manages OVP and UVP protections and PWRGOOD. Connect to the<br>positive side of the load for remote sensing. See <i>Section</i> 7 for details.             |

#### Table 2.Pin description

| Pin# Name Function |                                                                                                                                                           | Function    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                  | 7     FBG     Remote ground sense.       Connect to the negative side of the load for remote sensing. See Section 9 for proper layout of this connection. |             | Connect to the negative side of the load for remote sensing. See                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8                  | core section %                                                                                                                                            |             | Offset programming pin.<br>Internally set to 1.24V. Connecting a $R_{OS}$ resistor to SGND allows to set<br>a current that is mirrored into FB pin in order to program a positive off-<br>set according to the selected $R_{FB}$ .<br>Short to SGND to disable the function. See <i>Section 6.4</i> for details.                                                                                                                                                                                                                                                                                                |

| 9                  | 0                                                                                                                                                         | LTB         | LTB Technology <sup>TM</sup> Input pin.<br>Connect through an $R_{LTB}$ - $C_{LTB}$ network to the regulated voltage<br>(CORE Section) to detect load transient. See <i>Section 10</i> for details.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1                  | 0                                                                                                                                                         | OVP / V_FIX | <i>OVP.</i> Over Voltage Programming Pin. Internally pulled-up to 3.3V by 11 $\mu$ A. Connect to SGND through a R <sub>OVP</sub> resistor and filter with 10nF (typ) to set a fixed voltage according to the R <sub>OVP</sub> resistor. If floating it will program 3.3V threshold. See <i>Section 7</i> for details.<br><i>V_FIX - Hardware override.</i> Short to SGND to enter VFIX mode (WARNING: this condition overrides any code programmed on the VIDx lines). In this case, the device will use SVI inputs as static VIDs and OVP threshold will be set to 1.8V. See <i>Section 5.4.5</i> for details. |

| 11                 | CORE<br>SECTION                                                                                                                                           | LTB_GAIN    | LTB Technology <sup>TM</sup> gain pin.<br>Connect to SGND through a resistor $R_{LTBGAIN}$ to program the LTB Gain. See <i>Section 10</i> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1:                 | 12 PSI_L                                                                                                                                                  |             | Power Saving Indicator (SVI Mode).<br>Open-drain Input/Output pin. See <i>Section 5.4.3</i> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13                 |                                                                                                                                                           | CS1+        | Channel 1 Current Sense Positive Input. Connect through an R-C filter to the phase-side of the channel 1 inductor. See <i>Section 9</i> for proper layout of this connection.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14                 | 14 CS1-                                                                                                                                                   |             | Channel 1 Current Sense Negative Input. Connect through a R <sub>G</sub> resistor to the output-side of the channel inductor.<br>See <i>Section 9</i> for proper layout of this connection.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15                 | TION                                                                                                                                                      | CS2+        | Channel 2 Current Sense Positive Input. Connect through an R-C filter to the phase-side of the channel 2 inductor.<br>See <i>Section 9</i> for proper layout of this connection.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16                 | CORE SECTION                                                                                                                                              | CS2-        | Channel 2 Current Sense Negative Input. Connect through a R <sub>G</sub> resistor to the output-side of the channel inductor.<br>See <i>Section 9</i> for proper layout of this connection.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17 CS3+            |                                                                                                                                                           | CS3+        | Channel 3 Current Sense Positive Input. Connect through an R-C filter to the phase-side of the channel 3 inductor. When working at 2 phase, directly connect to $V_{out\_CORE}$ .<br>See <i>Section 9</i> for proper layout of this connection.                                                                                                                                                                                                                                                                                                                                                                 |

|                    |                                                                                                                                                           | CS3-        | Channel 3 Current Sense Negative Input. Connect through a $R_G$ resistor to the output-side of the channel inductor. When working at 2 phase, connect through $R_G$ to CS3+.<br>See <i>Section 9</i> for proper layout of this connection.                                                                                                                                                                                                                                                                                                                                                                      |

Table 2.

Pin description (continued)

| Pi           | Pin# Name Function |                | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|--------------|--------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 19           | NO                 | CS4+           | Channel 4 Current Sense Positive Input. Connect through an R-C filter to the phase-side of the channel 4 inductor. When working at 2 or 3 phase, directly connect to $V_{out\_CORE}$ . See <i>Section 9</i> for proper layout of this connection.                                                                                                                                                                                                                                                                                                |  |

| 20           | CORE SECTION       | CS4-           | Channel 4 Current Sense Negative Input. Connect through a $R_G$ resistor to the output-side of the channel inductor. When working at 2 or 3 phase, connect through $R_G$ to CS4+.<br>See <i>Section 9</i> for proper layout of this connection.                                                                                                                                                                                                                                                                                                  |  |

| 21           |                    | OC_PHASE       | Per-Phase Over Current (CORE Section).<br>Internally set to 1.24V, connecting to SGND with a resistor $R_{OC_TH}$ it<br>programs the OC threshold per-phase. See <i>Section 7.4.1</i> for details.                                                                                                                                                                                                                                                                                                                                               |  |

| 2            | 22                 | NC             | Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 23           | NB<br>SECTION      | NB_ISEN        | NB Current Sense Pin.<br>Used for NB voltage positioning and NB_OCP. Connect through a resis-<br>tor R <sub>ISEN</sub> to the relative LS Drain. See <i>Section 7.4</i> for details.                                                                                                                                                                                                                                                                                                                                                             |  |

| 2            | 24                 | NC             | Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 25,<br>26    | PVI<br>INTERFACE   | VID4, VID5     | Voltage IDentification Pins.<br>Internally pulled-low by $10\mu A$ , they are used to program the output voltage. Used only in PVI-Mode, ignored when in SVI-Mode.See <i>Section 5</i> for details.                                                                                                                                                                                                                                                                                                                                              |  |

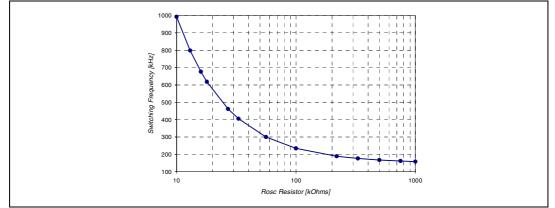

| 27 OSC / FLT |                    | OSC / FLT      | <i>OSC</i> : It allows programming the switching frequency $F_{SW}$ of both Sections. Switching frequency can be increased according to the resistor $R_{OSC}$ connected from the pin to. SGND with a gain of 6.8kHz/µA (see <i>Section 8</i> for details). If floating, the switching frequency is 150kHz per phase.<br><i>FLT</i> : The pin is forced high (3.3V) in case of an OV / UV fault. To recover from this condition, cycle VCC or the EN pin. See <i>Section 7</i> for details.                                                      |  |

| 28           | CORE SECTION       | OC_AVG /<br>LI | Average Over Current and Load Indicator Pin.<br>A current proportional to the current delivered by the CORE Section (a copy of the DROOP current) is sourced through this pin.<br>The Average-OC threshold is programmed by connecting a resistor $R_{OC\_AVG}$ to SGND. When the generated voltage crosses the OC\_AVG threshold ( $V_{OC\_AVGTH} = 2.5V$ Typ) the device latches with all mosfets OFF (to recover, cycle VCC or the EN pin).<br>A load indicator with 2.5V end-of-scale is then implemented.<br>See Section 7.4.1 for details. |  |

| 29           | NB SECTION         | NB_OS          | Offset Programming Pin.<br>Internally set to 1.24V, connecting a $R_{OS\_NB}$ resistor to SGND allows<br>setting a current that is mirrored into NB_FB pin in order to program a<br>positive offset according to the selected $R_{FB\_NB}$ . Short to SGND to dis-<br>able the function. See <i>Section 6.7</i> for details.                                                                                                                                                                                                                     |  |

| 30           |                    |                | Connect to the negative side of the load to perform remote sense. See                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

Table 2.

Pin description (continued)

| Pin# Name |                     | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-----------|---------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31        |                     | NB_VSEN    | NB output voltage monitor.<br>It manages OVP and UVP protections and PWRGOOD. Connect to the<br>positive side of the NB load to perform remote sensing. See <i>Section 9</i><br>for proper layout of this connection.                                                                                                                                                                                                                            |  |

| 32        | NB_DROOP            |            | A current proportional to the total current read by the NB section is sourced through this pin according to the Current Reading Gain (R <sub>ISEN</sub> ). Short to NB_FB to implement Droop Function or connect to SGND through a resistor and filter with 1nF capacitor to implement NB LOAD Indicator. If not used, short to SGND.                                                                                                            |  |

| 33        | NB                  | NB_FB      | NB error amplifier inverting input. Connect with a resistor $R_{FB\_NB}$ to NB_VSEN and with an $R_{F\_NB}$ - $C_{F\_NB}$ to NB_COMP. Offset current programmed by NB_OS is sunk through this pin.                                                                                                                                                                                                                                               |  |

| 34        |                     | NB_COMP    | Error amplifier output. Connect with an $R_{F\_NB}$ - $C_{F\_NB}$ to NB_FB. The NB Section or the device cannot be disabled by grounding this pin.                                                                                                                                                                                                                                                                                               |  |

| 35,<br>36 |                     |            | Voltage IDentification Pins.<br>Internally pulled-low by $10\mu$ A, they are used to program the output voltage. VID1 is monitored on the EN pin rising-edge to define the operative mode of the controller (SVI or PVI). When in SVI Mode, VID0 is ignored. See <i>Section 5</i> for details.                                                                                                                                                   |  |

| 37        | SVI / PVI INTERFACE | PWROK      | System-wide Power Good Input (SVI Mode).<br>Internally pulled-low by 10µA. When low, the device will decode the two<br>SVI bits (SVC, SVD) to determine the <i>Pre-PWROK Metal VID</i> (default<br>condition when pin is floating).<br>When high, the device will actively run the SVI protocol.<br><i>Pre-PWROK Metal VID</i> are latched after EN is asserted and re-used in<br>case of PWROK de-assertion. Latch is reset by VCC or EN cycle. |  |

| 38 EN     |                     | EN         | VR Enable. Internally pulled-up to $3.3V$ by $10\mu A$ .<br>Pull-low to disable the device. When set free, the device immediately<br>checks for the VID1 status to determine the SVI / PVI protocol to be<br>adopted and configures itself accordingly. See <i>Section 5</i> for details.                                                                                                                                                        |  |

| 39        | ITERFACE            | SVC / VID3 | Voltage IDentification Pin - SVI Clock Pin.<br>Internally pulled-low by $10\mu$ A, it is used to program the output voltage.<br>When in SVI-Mode, it is considered as Serial-VID-Data (Input / Open<br>Drain Output). See <i>Section 5</i> for details.                                                                                                                                                                                          |  |

| 40        | SVI / PVI INTERFACE | SVD / VID2 | Voltage IDentification Pins - SVI Data Pin.<br>Internally pulled-low by $10\mu$ A, it is used to program the output voltage.<br>When in SVI-Mode, it is considered as Serial-VID-Data (Input / Open<br>Drain Output). See <i>Section 5</i> for details.                                                                                                                                                                                          |  |

| 4         | 1                   | PWRGOOD    | VCORE and NB Power Good.<br>It is an open-drain output set free after SS as long as both the voltage<br>planes are within specifications. Pull-up to 3.3V (typ) or lower, if not<br>used it can be left floating.<br>When in PVI Mode, it monitors the CORE Section only.                                                                                                                                                                        |  |

| Table 2. | Pin description | (continued) |

|----------|-----------------|-------------|

|----------|-----------------|-------------|

NB

CORE

NB SECTION

CORE

PWM1 to

PWM4

Thermal pad

Pin#

42

43

44

45 to

48

| Name     | Function                                                                                                                                                                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NB_ENDRV | External driver enable.<br>Open Drain output used to control NB Section external driver status:<br>pulled-low to manage HiZ conditions or pulled-high to enable the driver.<br>Pull up to 3.3V (typ) or lower.<br>When in PVI Mode, NB Section is always kept in HiZ. |

| ENDRV    | External Driver enable.<br>Open Drain output used to control CORE Section external driver status:<br>pulled-low to manage HiZ conditions or pulled-high to enable the driver.<br>Pull up to 3.3V (typ) or lower.                                                      |

| NB_PWM   | PWM output.<br>Connect to external driver PWM input. The device is able to manage<br>HiZ status by setting the pin floating. When in PVI Mode, NB Section is<br>kept in HiZ. See <i>Section 5.4.4</i> for details about HiZ management.                               |

Connect to external drivers PWM inputs. The device is able to manage

By shorting to SGND PWM4 or PWM3 and PWM4, it is possible to pro-

Thermal pad connects the Silicon substrate and makes good thermal

gram the CORE section to work at 3 or 2 phase respectively.

See Section 5.4.4 for details about HiZ management.

contact with the PCB. Connect to the PGND plane.

Table 2. Pin description (continued)

PWM outputs.

HiZ status by setting the pins floating.

## 2.2 Thermal data

| Table | 3. | Thermal | data |

|-------|----|---------|------|

|       |    |         |      |

| Symbol            | Parameter                                                                    | Value      | Unit |

|-------------------|------------------------------------------------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance junction to ambient<br>(Device soldered on 2s2p PC Board) | 40         | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction to case                                          | 1          | °C/W |

| T <sub>MAX</sub>  | Maximum junction temperature                                                 | 150        | °C   |

| T <sub>STG</sub>  | Storage temperature range                                                    | -40 to 150 | °C   |

| TJ                | Junction temperature range                                                   | 0 to 125   | °C   |

# 3 Electrical specifications

## 3.1 Absolute maximum ratings

#### Table 4. Absolute maximum ratings

| Symbol          | Parameter               | Value       | Unit |

|-----------------|-------------------------|-------------|------|

| V <sub>CC</sub> | to PGND                 | 15          | V    |

|                 | All other Pins to PGNDx | -0.3 to 3.6 | V    |

## 3.2 Electrical characteristics

#### Table 5. Electrical characteristics

(V<sub>CC</sub>=12V±15%, T<sub>J</sub> = 0°C to 70°C unless otherwise specified).

| Symbol              | Parameter                   | Test conditions              | Min. | Тур. | Max. | Unit |  |  |

|---------------------|-----------------------------|------------------------------|------|------|------|------|--|--|

| Supply curr         | Supply current and power-ON |                              |      |      |      |      |  |  |

| I <sub>CC</sub>     | VCC supply current          |                              |      | 20   |      | mA   |  |  |

| 1.11.4.0            | VCC Turn-ON                 | VCC rising                   |      |      | 9    | V    |  |  |

| UVLO <sub>VCC</sub> | VCC Turn-OFF                | VCC falling                  | 7    |      |      | V    |  |  |

| Oscillator          |                             |                              | ·    |      |      |      |  |  |

| F                   | Main oscillator accuracy    |                              | 135  | 150  | 165  | kHz  |  |  |

| F <sub>SW</sub>     | Oscillator adjustability    | $R_{OSC} = 27k\Omega$        | 380  | 465  | 550  | kHz  |  |  |

| $\Delta V_{OSC}$    | PWM ramp amplitude          | CORE and NB section          |      | 2    |      | V    |  |  |

| FAULT               | Voltage at Pin OSC          | OVP, UVP latch active        | 3    |      | 3.6  | V    |  |  |

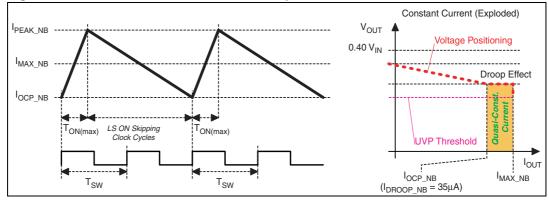

|                     | NB duty-cycle limit         | I <sub>NB_DROOP</sub> = 0μA  |      | 80   |      | %    |  |  |

| d <sub>MAX_NB</sub> |                             | I <sub>NB_DROOP</sub> = 35μA |      | 40   |      | %    |  |  |

| PVI / SVI int       | erface                      |                              |      |      |      |      |  |  |

|                     | Input high                  |                              | 2    |      |      | V    |  |  |

| EN,                 | Input low                   |                              |      |      | 0.80 | V    |  |  |

| PWROK               | Pull-up current             | EN Pin                       |      | 10   |      | μA   |  |  |

|                     | Pull-down current           | PWORK Pin                    |      | 10   |      | μA   |  |  |

| VID2,/SVD           | Input high                  | (SVI Mode)                   | 0.95 |      |      | V    |  |  |

| VID3/SVC            | Input low                   | (SVI Mode)                   |      |      | 0.65 | V    |  |  |

| SVD                 | Voltage low (ACK)           | I <sub>SINK</sub> = -5mA     |      |      | 250  | mV   |  |  |

|                     | Input high                  | (PVI mode)                   | 1.3  |      |      | V    |  |  |

| VID0 to<br>VID5     | Input low                   | (PVI mode)                   |      |      | 0.80 | V    |  |  |

|                     | Pull-down current           |                              |      | 10   |      | μA   |  |  |

| V_FIX               | Entering V_FIX mode         |                              |      |      | 0.90 | V    |  |  |

Electrical characteristics (continued)  $(V_{CC}=12V\pm15\%, T_J=0^\circ C \text{ to } 70^\circ C \text{ unless otherwise specified}).$

| Symbol                 | Parameter                         | Test conditions                                        | Min.  | Тур.  | Max.  | Unit |

|------------------------|-----------------------------------|--------------------------------------------------------|-------|-------|-------|------|

| PSI_L                  | Voltage Low                       | I <sub>SINK</sub> = -5mA                               |       |       | 250   | mV   |

| Voltage posi           | tioning (CORE and NB Se           | ction)                                                 |       |       |       |      |

| CORE                   |                                   | VSEN to V <sub>CORE</sub> ; FBG to GND <sub>CORE</sub> | -8    |       | 8     | mV   |

| NB                     | Output voltage accuracy           | NBVSEN to $V_{NB}$ ; NBFBG to $GND_{FB}$               | -10   |       | 10    | mV   |

|                        | OFFSET bias voltage               | I <sub>OS</sub> = 0 to 250μA                           | 1.190 | 1.24  | 1.290 | V    |

| OS, NB_OS              | OFFSET current range              |                                                        | 0     |       | 250   | μA   |

|                        | OFFSET - I <sub>FB</sub> accuracy | I <sub>OS</sub> = 0 to 250μA                           | -15   |       | 15    | %    |

| DROOP                  |                                   | $I_{DROOP} = 0$ to 140µA; OS = OFF                     | -9    |       | 9     | μA   |

| NB_DROOP               | DROOP accuracy                    | $I_{NB_DROOP} = 0$ to $35\mu A$ ; OS = OFF             | -4    |       | 4     | μA   |

| A <sub>0</sub>         | EA DC gain                        |                                                        |       | 100   |       | dB   |

| SR                     | Slew rate                         | COMP, NB_COMP to SGND = 10pF                           |       | 20    |       | V/µs |

| PWM output             | s (CORE and NB Section)           |                                                        |       |       | •     |      |

| PWMx,                  | Output high                       | I = 1mA                                                | 3     |       | 3.6   | V    |

| NB_PWM                 | Output low                        | l = -1mA                                               |       |       | 0.2   | V    |

| I <sub>PWMx</sub>      | Test current                      |                                                        |       | 10    |       | μA   |

| ENDRV,<br>NB_ENDRV     | Output low                        | I = -5mA                                               |       |       | 0.4   | V    |

| Protections            |                                   | ·                                                      |       |       |       |      |

|                        | Over voltage protection           | V_FIX Mode (V_FIX = SGND);<br>VSEN, NB_VSEN Rising     | 1.720 | 1.800 | 1.880 | V    |

| OVP                    | Bias current                      |                                                        | 7     | 11    | 15    | μA   |

|                        | OV programmability                | R <sub>OVP</sub> = 180kΩ                               | 1.730 | 1.800 | 1.870 | V    |

| UVP                    | Under voltage protection          | VSEN, NB_VSEN Falling; wrt Ref.                        | -470  | -400  | -330  | mV   |

|                        | PGOOD threshold                   | VSEN, NB_VSEN Falling; wrt Ref                         | -300  | -250  | -200  | mV   |

| PWRGOOD                | Voltage low                       | I <sub>PWRGOOD</sub> = -4mA                            |       |       | 0.4   | V    |

|                        |                                   | Sourced from NB_VSEN; OS = OFF                         |       | 50    |       | μA   |

| I <sub>VSEN-DISC</sub> | VSEN disconnection                | Sunk from VSEN; OS = OFF                               |       | 30    |       | μA   |

| V <sub>FB-DISC</sub>   | FB disconnection                  | CORE - V <sub>CS-</sub> Rising, above VSEN             | 500   | 600   | 700   | mV   |

| FBG DISC               | FBG disconnection                 | EA NI input wrt VID                                    | 350   | 450   | 550   | mV   |

| OC_PHASE               | Per-phase OC                      | CORE section; bias voltage                             | 1.200 | 1.240 | 1.280 | V    |

| kV <sub>OC_AVGTH</sub> | Average OC                        | CORE section                                           | 2.430 | 2.500 | 2.570 | V    |

| kl <sub>OC_AVGTH</sub> | Average OC                        | $I_{DROOP} = 0$ to 140µA; OS = OFF                     | -11   |       | 11    | μA   |

| I <sub>OCTH_NB</sub>   | OC threshold                      | NB section                                             | 32    | 37.5  | 43    | μA   |

## 4 Device description and operation

L6740L is a hybrid CPU Power Supply Controller compatible with both Parallel (PVI) and Serial (SVI) protocols for AMD K8 - Second Generation Processors. The device provides complete control logic and protections for a high-performance step-down DC-DC voltage regulator, optimized for advanced microprocessor power supply supporting both PVI and SVI communication. It embeds two independent controllers for CPU CORE and the integrated NB, each one with its own set of protections.

L6740L is able to detect which kind of CPU is connected in order to configure itself to work as a Single-Plane PVI controller or Dual-Plane SVI controller.

The Controller performs a single-phase control for the NB Section and a programmable 2-to-4 phase control for the CORE Section featuring Dual-Edge non-Latched architecture: this allows fast load-transient response optimizing the output filter consequently reducing the total BOM cost. Further reduction can be achieved by enabling LTB Technology<sup>(TM)</sup>. NB phase (when enabled) will be automatically phase-shifted with respect to the CORE phases in order to reduce the total input rms current amount.

PSI\_L Flag is sent to the VR through the SVI bus. The controller monitors this flag and selctively modifies the phase number in order to optimize the system efficiency when the CPU enters low-power states. This causes the over-all efficiency to be maximized at light loads so reducing losses and system power consumption.

Both sections feature programmable Over-Voltage protection and adjustable constant Over-Current protection. Voltage positioning (LL) is possible thanks to an accurate fully-differential current-sense across the main inductors for the CORE Section and thanks to the loss-less current sense across Low-Side MOSFET  $R_{dsON}$  for the NB section. In both cases, LL may be disabled and the generated current information may be used to implement a Load Indicator function.

L6740L features dual remote sensing for the regulated outputs (CORE and NB) in order to recover from PCB voltage drops also protecting the load from possible feedback network disconnections.

LSLess start-up function allows the controller to manage pre-biased start-up avoiding dangerous current return through the main inductors as well as negative undershoot on the output voltage if the output filter is still charged before start-up.

L6740L also supports V\_FIX mode for system debugging: in this particular configuration the SVI bus is used as a static bus configuring 4 operative voltages for both the sections and ignoring any serial-VID command.

When working in PVI mode, the device features On-the-Fly VID management: VID code is continuously sampled and the reference update according to the variation detected,

L6740L is available in TQFP48 Package.

## 5 Hybrid CPU support and CPU\_TYPE detection

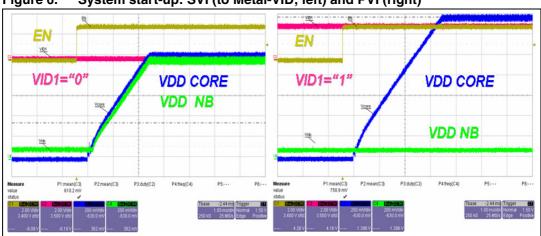

L6740L is able to detect the type of the CPU-core connected and to configure itself accordingly. At system Start-up, on the rising-edge of the EN signal, the device monitors the status of VID1 and configures the PVI mode (VID1 = 1) or SVI mode (VID1 = 0).

When in PVI mode, L6740L uses the information available on the VID[0: 5] bus to address the CORE Section output voltage according to *Table 6*. NB Section is kept in HiZ mode.

When in SVI mode, L6740L ignores the information available on VID0, VID4 and VID5 and uses VID2 and VID3 as a SVI bus addressing the CORE and NB Sections according to the SVI protocol.

**Caution:** To avoid any risk of errors in CPU type detection (i.e. detecting SVI CPU when PVI CPU is installed on the socket and viceversa), it is reccomended to carefully control the start-up sequencing of the system hosting L6740L in order to ensure than on the EN rising-edge, VID1 is in valid and correct state.

## 5.1 PVI - parallel interface

PVI is a 6-bit-wide parallel interface used to address the CORE Section reference. According to the selected code, the device sets the CORE Section reference and regulates its output voltage as reported into *Table 6*.

NB Section is always kept in HiZ; no activity is performed on this section. Furthermore, PWROK information is ignored as well since the signal only applies to the SVI protocol.

### 5.2 PVI start-up

Once the PVI mode has been detected, the device uses the whole code available on the VID[0:5] lines to define the reference for the CORE section. NB Section is kept in HiZ. Soft-Start to the programmed reference is performed regardless of the state of PWROK.

See Section 6.10 for details about Soft-Start.

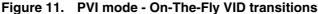

Figure 6. System start-up: SVI (to Metal-VID; left) and PVI (right)

| L6740L |

|--------|

|--------|

| Table | 0.   | Voltage identifications (VID) codes for PVI n |      |      |      |                   |      | I mode |      |      |      |      |                   |

|-------|------|-----------------------------------------------|------|------|------|-------------------|------|--------|------|------|------|------|-------------------|

| VID5  | VID4 | VID3                                          | VID2 | VID1 | VID0 | Output<br>voltage | VID5 | VID4   | VID3 | VID2 | VID1 | VID0 | Output<br>voltage |

| 0     | 0    | 0                                             | 0    | 0    | 0    | 1.5500            | 1    | 0      | 0    | 0    | 0    | 0    | 0.7625            |

| 0     | 0    | 0                                             | 0    | 0    | 1    | 1.5250            | 1    | 0      | 0    | 0    | 0    | 1    | 0.7500            |

| 0     | 0    | 0                                             | 0    | 1    | 0    | 1.5000            | 1    | 0      | 0    | 0    | 1    | 0    | 0.7375            |

| 0     | 0    | 0                                             | 0    | 1    | 1    | 1.4750            | 1    | 0      | 0    | 0    | 1    | 1    | 0.7250            |

| 0     | 0    | 0                                             | 1    | 0    | 0    | 1.4500            | 1    | 0      | 0    | 1    | 0    | 0    | 0.7125            |

| 0     | 0    | 0                                             | 1    | 0    | 1    | 1.4250            | 1    | 0      | 0    | 1    | 0    | 1    | 0.7000            |

| 0     | 0    | 0                                             | 1    | 1    | 0    | 1.4000            | 1    | 0      | 0    | 1    | 1    | 0    | 0.6875            |

| 0     | 0    | 0                                             | 1    | 1    | 1    | 1.3750            | 1    | 0      | 0    | 1    | 1    | 1    | 0.6750            |

| 0     | 0    | 1                                             | 0    | 0    | 0    | 1.3500            | 1    | 0      | 1    | 0    | 0    | 0    | 0.6625            |

| 0     | 0    | 1                                             | 0    | 0    | 1    | 1.3250            | 1    | 0      | 1    | 0    | 0    | 1    | 0.6500            |

| 0     | 0    | 1                                             | 0    | 1    | 0    | 1.3000            | 1    | 0      | 1    | 0    | 1    | 0    | 0.6375            |

| 0     | 0    | 1                                             | 0    | 1    | 1    | 1.2750            | 1    | 0      | 1    | 0    | 1    | 1    | 0.6250            |

| 0     | 0    | 1                                             | 1    | 0    | 0    | 1.2500            | 1    | 0      | 1    | 1    | 0    | 0    | 0.6125            |

| 0     | 0    | 1                                             | 1    | 0    | 1    | 1.2250            | 1    | 0      | 1    | 1    | 0    | 1    | 0.6000            |

| 0     | 0    | 1                                             | 1    | 1    | 0    | 1.2000            | 1    | 0      | 1    | 1    | 1    | 0    | 0.5875            |

| 0     | 0    | 1                                             | 1    | 1    | 1    | 1.1750            | 1    | 0      | 1    | 1    | 1    | 1    | 0.5750            |

| 0     | 1    | 0                                             | 0    | 0    | 0    | 1.1500            | 1    | 1      | 0    | 0    | 0    | 0    | 0.5625            |

| 0     | 1    | 0                                             | 0    | 0    | 1    | 1.1250            | 1    | 1      | 0    | 0    | 0    | 1    | 0.5500            |

| 0     | 1    | 0                                             | 0    | 1    | 0    | 1.1000            | 1    | 1      | 0    | 0    | 1    | 0    | 0.5375            |

| 0     | 1    | 0                                             | 0    | 1    | 1    | 1.0750            | 1    | 1      | 0    | 0    | 1    | 1    | 0.5250            |

| 0     | 1    | 0                                             | 1    | 0    | 0    | 1.0500            | 1    | 1      | 0    | 1    | 0    | 0    | 0.5125            |

| 0     | 1    | 0                                             | 1    | 0    | 1    | 1.0250            | 1    | 1      | 0    | 1    | 0    | 1    | 0.5000            |

| 0     | 1    | 0                                             | 1    | 1    | 0    | 1.0000            | 1    | 1      | 0    | 1    | 1    | 0    | 0.4875            |

| 0     | 1    | 0                                             | 1    | 1    | 1    | 0.9750            | 1    | 1      | 0    | 1    | 1    | 1    | 0.4750            |

| 0     | 1    | 1                                             | 0    | 0    | 0    | 0.9500            | 1    | 1      | 1    | 0    | 0    | 0    | 0.4625            |

| 0     | 1    | 1                                             | 0    | 0    | 1    | 0.9250            | 1    | 1      | 1    | 0    | 0    | 1    | 0.4500            |

| 0     | 1    | 1                                             | 0    | 1    | 0    | 0.9000            | 1    | 1      | 1    | 0    | 1    | 0    | 0.4375            |

| 0     | 1    | 1                                             | 0    | 1    | 1    | 0.8750            | 1    | 1      | 1    | 0    | 1    | 1    | 0.4250            |

| 0     | 1    | 1                                             | 1    | 0    | 0    | 0.8500            | 1    | 1      | 1    | 1    | 0    | 0    | 0.4125            |

| 0     | 1    | 1                                             | 1    | 0    | 1    | 0.8250            | 1    | 1      | 1    | 1    | 0    | 1    | 0.4000            |

| 0     | 1    | 1                                             | 1    | 1    | 0    | 0.8000            | 1    | 1      | 1    | 1    | 1    | 0    | 0.3875            |

| 0     | 1    | 1                                             | 1    | 1    | 1    | 0.7750            | 1    | 1      | 1    | 1    | 1    | 1    | 0.3750            |

Table 6.

Voltage identifications (VID) codes for PVI mode

#### 5.3 SVI - serial interface

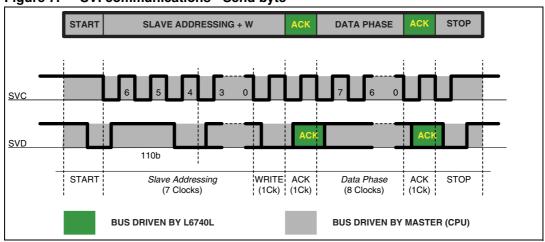

SVI is a two wire, Clock and Data, bus that connects a single master (CPU) to one slave (L6740L). The master initiates and terminates SVI transactions and drives the clock, SVC, and the data, SVD, during a transaction. The slave receives the SVI transactions and acts accordingly. SVI wire protocol is based on fast-mode  $I^2C$ .

SVI interface also considers two additional signal needed to manage the system start-up. These signals are EN and PWROK. The device return a PWRGOOD signal if the output voltages are in regulation.

## 5.4 SVI start-up

Once the SVI mode has been detected on the EN rising-edge, L6740L checks for the status of the two serial VID pins, SVC and SVD, and stores this value as the *Pre-PWROK Metal VID*. The controller initiate a soft-start phase regulating both CORE and NB voltage planes to the voltage level prescribed by the *Pre-PWROK Metal VID*. See *Table 7* for details about *Pre-PWROK Metal VID* codifications. The stored *Pre-PWROK Metal VID* value are re-used in any case of PWROK de-assertion.

After bringing the output rails into regulation, the controller asserts the PWRGOOD signal and waits for PWROK to be asserted. Until PWROK is asserted, the Controller regulates to the *Pre-PWROK Metal VID* ignoring any commands coming from the SVI interface.

After PWROK is asserted, the processor has initialized the serial VID interface and L6740L waits for commands from the CPU to move the voltage planes from the *Pre-PWROK Metal VID* values to the operative VID values. As long as PWROK remains asserted, the controller will react to any command issued through the SVI interface according to SVI Protocol.

See Section 6.10 for details about Soft-Start.

| svc | SVD | Output voltage [V]  |            |  |  |

|-----|-----|---------------------|------------|--|--|

| 370 | 370 | Pre-PWROK Metal VID | V_FIX Mode |  |  |

| 0   | 0   | 1.1V                | 1.4V       |  |  |

| 0   | 1   | 1.0V                | 1.2V       |  |  |

| 1   | 0   | 0.9V                | 1.0V       |  |  |

| 1   | 1   | 0.8V                | 0.8V       |  |  |

Table 7.V\_FIX mode and MetalVID

#### 5.4.1 Set VID command

The *Set VID Command* is defined as the command sequence that the CPU issues on the SVI bus to modify the voltage level of the CORE Section and/or the NB Section.

During a *Set VID Command*, the processor sends the start (START) sequence followed by the address of the Section which the *Set VID Command* applies. The processor then sends the write (WRITE) bit. After the write bit, the Voltage Regulator (VR) sends the acknowledge (ACK) bit. The processor then sends the VID bits code during the *data phase*. The VR sends the acknowledge (ACK) bit after the data phase. Finally, the processor sends the stop (STOP) sequence. After the VR has detected the stop, it performs an On-the-Fly VID

transition for the addressed section(s) or, more in general, react to the sent command accordingly. Refer to *Figure 7*, *Table 8* and *Table 9* for details about the *Set VID Command*.

L6740L is able to manage individual power OFF for both the Sections. The CPU may issue a serial VID command to power OFF or power ON one Section while the other one remains powered. In this case, the PWRGOOD signal remains asserted.

| Table 8. SVI send byte - Ade | ress and data phase description |

|------------------------------|---------------------------------|

|------------------------------|---------------------------------|

| bits          | Description                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------|

| Address phase |                                                                                                                 |

| 6:4           | Always 110b.                                                                                                    |

| 3             | Not Applicable, ignored.                                                                                        |

| 2             | Not Applicable, ignored.                                                                                        |

| 1             | CORE Section <sup>(1)</sup> .<br>If set then the following data byte contains the VID code for CORE Section.    |

| 0             | NB Section <sup>(1)</sup> .<br>If set then the following data byte contains the VID code for NB Section.        |

| Data phase    |                                                                                                                 |

| 7             | PSI_L Flag (Active low).When asserted, the VR is allowed to enter Power-Saving mode. See <i>Section 5.4.3</i> . |

| 6:0           | VID Code. See Table 9.                                                                                          |

1. Assertion in both bit 1 and 0 will address the VID code to both CORE and NB simultaneously.

Table 9.

Data phase - Serial VID codes.

| Table 9. Data phase - Serial VID codes. |                   |           |                   |           |                   |           |                   |

|-----------------------------------------|-------------------|-----------|-------------------|-----------|-------------------|-----------|-------------------|

| SVI [6:0]                               | Output<br>voltage | SVI [6:0] | Output<br>voltage | SVI [6:0] | Output<br>voltage | SVI [6:0] | Output<br>voltage |

| 000_0000                                | 1.5500            | 010_0000  | 1.1500            | 100_0000  | 0.7500            | 110_0000  | 0.3500            |

| 000_0001                                | 1.5375            | 010_0001  | 1.1375            | 100_0001  | 0.7375            | 110_0001  | 0.3375            |

| 000_0010                                | 1.5250            | 010_0010  | 1.1250            | 100_0010  | 0.7250            | 110_0010  | 0.3250            |

| 000_0011                                | 1.5125            | 010_0011  | 1.1125            | 100_0011  | 0.7125            | 110_0011  | 0.3125            |

| 000_0100                                | 1.5000            | 010_0100  | 1.1000            | 100_0100  | 0.7000            | 110_0100  | 0.3000            |

| 000_0101                                | 1.4875            | 010_0101  | 1.0875            | 100_0101  | 0.6875            | 110_0101  | 0.2875            |

| 000_0110                                | 1.4750            | 010_0110  | 1.0750            | 100_0110  | 0.6750            | 110_0110  | 0.2750            |

| 000_0111                                | 1.4625            | 010_0111  | 1.0625            | 100_0111  | 0.6625            | 110_0111  | 0.2625            |

| 000_1000                                | 1.4500            | 010_1000  | 1.0500            | 100_1000  | 0.6500            | 110_1000  | 0.2500            |

| 000_1001                                | 1.4375            | 010_1001  | 1.0375            | 100_1001  | 0.6375            | 110_1001  | 0.2375            |

| 000_1010                                | 1.4250            | 010_1010  | 1.0250            | 100_1010  | 0.6250            | 110_1010  | 0.2250            |

| 000_1011                                | 1.4125            | 010_1011  | 1.0125            | 100_1011  | 0.6125            | 110_1011  | 0.2125            |

| 000_1100                                | 1.4000            | 010_1100  | 1.0000            | 100_1100  | 0.6000            | 110_1100  | 0.2000            |

| 000_1101                                | 1.3875            | 010_1101  | 0.9875            | 100_1101  | 0.5875            | 110_1101  | 0.1875            |

| 000_1110                                | 1.3750            | 010_1110  | 0.9750            | 100_1110  | 0.5750            | 110_1110  | 0.1750            |

| 000_1111                                | 1.3625            | 010_1111  | 0.9625            | 100_1111  | 0.5625            | 110_1111  | 0.1625            |

| 001_0000                                | 1.3500            | 011_0000  | 0.9500            | 101_0000  | 0.5500            | 111_0000  | 0.1500            |

| 001_0001                                | 1.3375            | 011_0001  | 0.9375            | 101_0001  | 0.5375            | 111_0001  | 0.1375            |

| 001_0010                                | 1.3250            | 011_0010  | 0.9250            | 101_0010  | 0.5250            | 111_0010  | 0.1250            |

| 001_0011                                | 1.3125            | 011_0011  | 0.9125            | 101_0011  | 0.5125            | 111_0011  | 0.1125            |

| 001_0100                                | 1.3000            | 011_0100  | 0.9000            | 101_0100  | 0.5000            | 111_0100  | 0.1000            |

| 001_0101                                | 1.2875            | 011_0101  | 0.8875            | 101_0101  | 0.4875            | 111_0101  | 0.0875            |

| 001_0110                                | 1.2750            | 011_0110  | 0.8750            | 101_0110  | 0.4750            | 111_0110  | 0.0750            |

| 001_0111                                | 1.2625            | 011_0111  | 0.8625            | 101_0111  | 0.4625            | 111_0111  | 0.0625            |

| 001_1000                                | 1.2500            | 011_1000  | 0.8500            | 101_1000  | 0.4500            | 111_1000  | 0.0500            |

| 001_1001                                | 1.2375            | 011_1001  | 0.8375            | 101_1001  | 0.4375            | 111_1001  | 0.0375            |

| 001_1010                                | 1.2250            | 011_1010  | 0.8250            | 101_1010  | 0.4250            | 111_1010  | 0.0250            |

| 001_1011                                | 1.2125            | 011_1011  | 0.8125            | 101_1011  | 0.4125            | 111_1011  | 0.0125            |

| 001_1100                                | 1.2000            | 011_1100  | 0.8000            | 101_1100  | 0.4000            | 111_1100  | OFF               |

| 001_1101                                | 1.1875            | 011_1101  | 0.7875            | 101_1101  | 0.3875            | 111_1101  | OFF               |

| 001_1110                                | 1.1750            | 011_1110  | 0.7750            | 101_1110  | 0.3750            | 111_1110  | OFF               |

| 001_1111                                | 1.1625            | 011_1111  | 0.7625            | 101_1111  | 0.3625            | 111_1111  | OFF               |

L6740L

#### 5.4.2 PWROK de-assertion

Anytime PWROK de-asserts while EN is asserted, the controller uses the previously stored *Pre-PWROK Metal VID* and regulates all the planes to that level performing an On-the-Fly transition to that level.

PWRGOOD is treated appropriately being de-asserted in case the *Pre-PWROK Metal VID* voltage is out of the initial voltage specifications.

#### 5.4.3 **PSI\_L** and efficiency optimization at light-load.

PSI\_L is an active-low flag (i.e. low logic level when asserted) that can be set by the CPU to allow the VR to enter Power-Saving mode to maximize the system efficiency when in light-load conditions. The status of the flag is communicated to the controller through the SVI bus and it is reported on the PSI\_L pin (open-drain).

The controller monitors the PSI\_L pin also to define the PSI Strategy, that is the action performed by the controller when PSI\_L is asserted. According to *Table 10*, by programming different voltage divider on PSI\_L, it is possible to configure the device to disable one or two phases while PSI\_L is asserted. The device can also be configured to take no action so phase number will not change after PSI\_L assertion.

In case the phase number is changed, the device will disable one or two phases starting from the highest one (i.e. if working at 3 phases, phase 3 will be disabled in case of 1 phase reduction; phase 2 and 3 in case of 2phase reduction). To disable Phases, the controller will set HiZ on the related PWM and re-configure internal phase-shift to maintain the interleaving. Furthermore, the internal current-sharing will be adjusted to consider the phase number reduction. ENDRV will remain asserted.

When PSI\_L is de-asserted, the device will return to the original configuration.

Start-up is performed with all the configured phases enabled. In case of On-the-Fly VID transitions, the device will maintain the phase configuration set before.

PSI Strategy (i.e. the voltage across PSI\_L) is read and stored when PWRGOOD is asserted at the end of the Soft-Start phase.

The phase number management is affected by the external driver selected.

If the external driver features the EN function, PSI\_L can be tied directly to the EN of the drivers of the phases that will be disabled.

Furthermore, in case the desired strategy is to work in single phase when 4phases are configured, PSI\_L can be tied also to the EN of the driver connected to Phase2 (apparently, from 4phases the max reduction would be to 2phase min.) in order to disable also this phase during low-power mode.

If the external driver manages HiZ through the PWM input, PSI\_L will be connected only to the external divider used to set the strategy. The system can be down-graded to single-phase only if configured for three phases.

Since PSI\_L can be used to enable some of the external drivers connected, the status of the pin is the logic AND between the PSI\_L Flag and the status of the ENDRV pin: if the controller wants to disable the external drivers pulling low ENDRV (because of protections or simply for start-up synchronization) also PSI\_L will be tied low.

NB Section is not impacted by PSI\_L status change. *Figure 8* shows an example of the efficiency improvement that can be achieved by enabling the PSI management.

| PSI_L           | PSI strategy                                                      |  |  |  |  |

|-----------------|-------------------------------------------------------------------|--|--|--|--|

| GND             | No Strategy.<br>PSI_L still reproduces the status of the PSI Flag |  |  |  |  |

| Pull-Up to <3V  | Phase number is cut by 1 while PSI_L is asserted.                 |  |  |  |  |

| Pull-Up to 3.3V | Phase number is cut by 2 while PSI_L is asserted.                 |  |  |  |  |

Table 10. PSI strategy

#### 5.4.4 HiZ management

L6740L is able to manage HiZ through both the PWMx and driver enable signals. When the controller wants to set in high impedance the output of one Section, it set the relative PWM floating and, at the same time, pulls-low the related ENDRV.

#### 5.4.5 Hardware jumper override - V\_FIX

Anytime the pin OVP/V\_FIX is driven low, the controller enters V\_FIX mode.

When in V\_FIX mode, both NB and CORE Section voltages are governed by the information shown in *Table 7*. Regardless of the state of PWROK, the device will work in SVI mode. SVC and SVD are considered as static VID and the output voltage will change according to their status. Dynamic SVC/SVD-change management is provided in this condition.

V\_FIX mode is intended for system debug only.

Protection management differs in this case, see *Section 7.1* for details.

## 6 Output voltage positioning

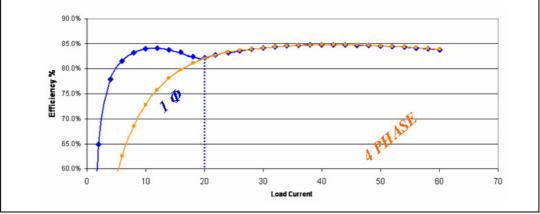

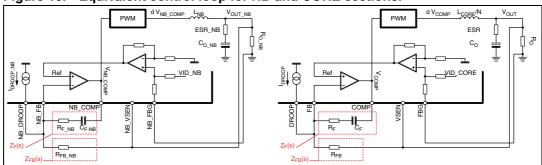

Output voltage positioning is performed by selecting the controller operative-mode (*SVI, PVI* and *V\_FIX*) and by programming the Droop Function and Offset to the reference of both the sections (See *Figure 9*). The controller reads the current delivered by each Section by monitoring the voltage drop across the Low-Side MOSFET for NB Section or DCR Inductors for CORE Section. The current ( $I_{DROOP} / I_{DROOP_NB}$ ) sourced from the DROOP / NB\_DROOP pin, directly proportional to the read current, causes the related section output voltage to vary according to the external  $R_{FB} / R_{FB_NB}$  resistor so implementing the desired load-line effect. The current ( $I_{OS} / I_{OS_NB}$ ) programmed through the OS / NB\_OS pins is sunk from the FB / NB\_FB pins causing the output voltage to be offset according to the resistance  $R_{FB} / R_{FB_NB}$  connected.

L6740L embeds a dual Remote-Sense Buffer to sense remotely the regulated voltage of each Section without any additional external components. In this way, the output voltage programmed is regulated compensating for board and socket losses. Keeping the sense traces parallel and guarded by a power plane results in common mode coupling for any picked-up noise.

Both DROOP and OFFSET function can be disabled: see *Section 6.3* and *Section 6.4* for details about CORE Section and *Section 6.6* and *Section 6.7* for details about NB Section. In case DROOP effect is not desired, the current information sourced from the DROOP pin may be used to implement a Load Indicator as reported in *Section 6.3* and *Section 6.6*.

Figure 9. Voltage positioning

CORE Section implements a flexible 2 to 4 interleaved-phase converter. To program the desired number of phase, simply short to SGND the PWMx signal that is not required to be used according to *Table 11*. For three phase operation, short PWM4 to SGND while for two phase operation, short PWM3 and PWM4 to SGND.

**Caution:** For the disabled phase(s), the current reading pins need to be properly connected to avoid errors in Current-Sharing and Voltage-Positioning: CSx+ needs to be connected to the regulated output voltage while CSx- needs to be connected to CSx+ through the same Rg resistor used for the active phases.

| Phase number | PWM1           | PWM2  | PWM3 | PWM4 |  |

|--------------|----------------|-------|------|------|--|

| 1            | n/a            |       |      |      |  |

| 2            | to D           | river | SGND | SGND |  |

| 3            | to Driver SGNI |       |      | SGND |  |

| 4            | to Driver      |       |      |      |  |

Table 11.

CORE section - Phase number programming

## 6.2 CORE section - Current reading and current sharing loop

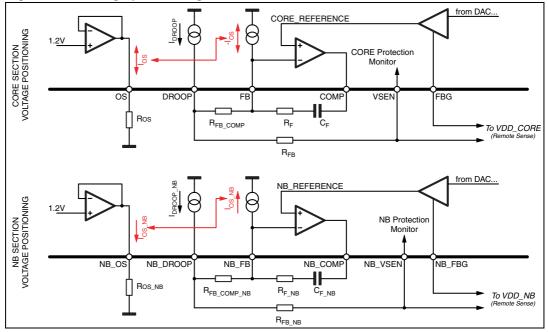

L6740L embeds a flexible, fully-differential current sense circuitry for the CORE Section that is able to read across inductor parasitic resistance or across a sense resistor placed in series to the inductor element. The fully-differential current reading rejects noise and allows placing sensing element in different locations without affecting the measurement's accuracy. The trans-conductance ratio is issued by the external resistor Rg placed outside the chip between CSx- pin toward the reading points. The current sense circuit always tracks the current information, the pin CSx+ is used as a reference keeping the CSx- pin to this voltage. To correctly reproduce the inductor current an R-C filtering network must be introduced in parallel to the sensing element. The current that flows from the CSx- pin is then given by the following equation (See *Figure 10*):

$$I_{CSx-} = \frac{DCR}{R_{G}} \cdot \frac{1 + s \cdot L/DCR}{1 + s \cdot R \cdot C} \cdot I_{PHASEx}$$

Considering now to match the time constant between the inductor and the R-C filter applied (Time constant mismatches cause the introduction of poles into the current reading network causing instability. In addition, it is also important for the load transient response and to let the system show resistive equivalent output impedance) it results:

$$\frac{L}{R_{L}} = R \cdot C \quad \Rightarrow \quad I_{CSx-} = \frac{R_{L}}{R_{G}} \cdot I_{PHASEx} = I_{INFOx}$$

$R_G$  resistor is typically designed in order to have an information current  $I_{INFOx}$  in the range of about  $35\mu A$  ( $I_{OCTH}$ ) at the OC Threshold.

L6740L

Current reading - CORE section (left) and NB section (right) Figure 10.

The current read through the CSx+ / CSx- pairs is converted into a current IINFOx proportional to the current delivered by each phase and the information about the average current  $I_{AVG} = \Sigma I_{INFOx} / N$  is internally built into the device (N is the number of working phases). The error between the read current IINFOx and the reference IAVG is then converted into a voltage that with a proper gain is used to adjust the duty cycle whose dominant value is set by the voltage error amplifier in order to equalize the current carried by each phase.

#### 6.3 CORE section - Load-line and load-indicator (Optional)

L6740L is able to introduce a dependence of the output voltage on the load current recovering part of the drop due to the output capacitor ESR in the load transient. Introducing a dependence of the output voltage on the load current, a static error, proportional to the output current, causes the output voltage to vary according to the sensed current.

Figure 10 shows the Current Sense Circuit used to implement the Load-Line. The current flowing across the inductor(s) is read through the R - C filter across CSx+ and CSx- pins. R<sub>G</sub> programs a transconductance gain and generates a current I<sub>CSx</sub> proportional to the current of the phase. The sum of the I<sub>CSx</sub> current is then sourced by the FB pin (I<sub>DROOP</sub>). R<sub>FB</sub> gives the final gain to program the desired load-line slope (Figure 9).

Time constant matching between the inductor (L / DCR) and the current reading filter (RC) is required to implement a real equivalent output impedance of the system so avoiding over and/or under shoot of the output voltage as a consequence of a load transient. See Section 6.2. The output characteristic vs. load current is then given by (Offset disabled):

$$V_{CORE} = VID - R_{FB} \cdot I_{DROOP} = VID - R_{FB} \cdot \frac{DCR}{R_G} \cdot I_{OUT} = VID - R_{LL} \cdot I_{OUT}$$

Where R<sub>LL</sub> is the resulting load-line resistance implemented by the CORE Section.

The whole power supply can be then represented by a "real" voltage generator with an equivalent output resistance R<sub>II</sub> and a voltage value of VID.

R<sub>FB</sub> resistor can be then designed according to the R<sub>LL</sub> specifications as follow:

$$R_{FB} = R_{LL} \cdot \frac{R_G}{DCR}$$

Caution: Load-Line (DROOP) implementation is optional, in case it is not desired, the resulting current information may be employed for other purposes, such as an additional Load Indicator

(LI). In this case, simply connect a resistor  $R_{L1}$  to SGND: the resulting voltage drop across  $R_{L1}$  will be proportional to the delivered current according to the following relationship:

$$V_{DROOP} = R_{LI} \cdot \frac{DCR}{R_G} \cdot I_{OUT}$$

In case no additional information about the delivered current is requested, the DROOP pin can be shorted to SGND.