# SC250 Step-Down DC-DC Converter with Bias LDO for RF Power Amplifiers

## **POWER MANAGEMENT**

### Description

The SC250 is a synchronous step-down converter designed specifically for use as an adaptive voltage supply for CDMA and WCDMA RF Power Amplifiers (PAs). The output voltage can be adjusted dynamically between 0.3V and (Vin - 0.4)V through a linear analog control input. For high power operation, a maximum control input signal level forces the device into bypass mode where the input is connected directly to the output via an internal P-Channel pass transistor. Bypass mode also occurs when the output load demands duty cycles in excess of the maximum rated duty cycle.

The SC250 also provides an LDO regulator which can be used to supply a 2.85V bias to the PA. The internal clock runs at 1MHz to maximize efficiency while still allowing the use of small surface mount inductors and capacitors can be used.

The peak current rating of the internal PMOS switch allows a DC output current of 600mA. The bypass PMOS current rating allows a minimum of 1A DC output current in the bypass mode. Shutdown turns off all the control circuitry to achieve a typical shutdown current of  $0.1\mu A$ .

#### **Features**

- Adjustable output voltage range 0.3 to 3.6V

- Linearly proportional V<sub>DAC</sub> to V<sub>OUT</sub> relationship for increased PA efficiency

- Pass-through mode automatic and on demand

- ◆ Input voltage range 2.7V to 5V

- ◆ Typical settling time 40µs

- Output current capability 600mA

- ◆ Maximum output current in bypass mode 1A

- ◆ Up to 96% efficiency

- Constant frequency operation 1MHz

- ◆ Less than 1µA shutdown current

- ♦ Internal 75mΩ PMOS bypass transistor

- ◆ PA bias voltage supply 2.85V, 20mA, 1.5%

- ◆ MLPD-W8, 2.3 x 2.3mm package

### **Applications**

- CDMA and WCDMA Phones

- Handheld Radios

- RF PC Cards

- Battery Powered RF Devices

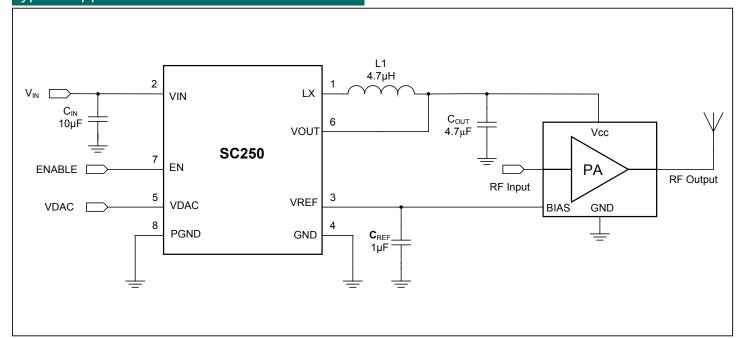

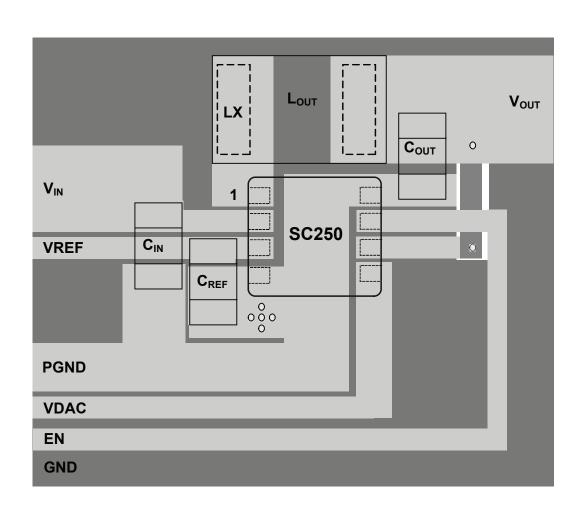

## Typical Application Circuit

## Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

| Parameter                                 | Symbol                    | Maximum                           | Units |

|-------------------------------------------|---------------------------|-----------------------------------|-------|

| Input Supply Voltage                      | V <sub>IN</sub>           | -0.3 to 7                         | V     |

| EN and VDAC Inputs                        | $V_{\rm EN}, V_{\rm DAC}$ | -0.3 to 7                         | V     |

| LX Pin Voltage (Power switch OFF)         | V <sub>LX</sub>           | -1 to V <sub>IN</sub> + 1, 7V MAX | V     |

| VOUT Voltage                              | V <sub>out</sub>          | -0.3 to 7                         | V     |

| VOUT Short Circuit to GND duration        | t <sub>sc</sub>           | Continuous                        | S     |

| Thermal Impedance Junction to Ambient (1) | $\theta_{	exttt{JA}}$     | 110                               | °C/W  |

| Operating Ambient Temperature Range       | T <sub>A</sub>            | -40 to +85                        | °C    |

| Junction Temperature                      | T <sub>JC</sub>           | +150                              | °C    |

| Storage Temperature                       | T <sub>s</sub>            | -60 to +160                       | °C    |

| Peak IR Reflow Temperature                | T <sub>P</sub>            | 260                               | °C    |

| ESD Protection Level (2)                  | V <sub>ESD</sub>          | 2                                 | kV    |

Note:

### **Electrical Characteristics**

Unless otherwise noted:  $V_{_{IN}} = V_{_{EN}} = 3.6 \text{V}$ ,  $T_{_{A}} = -40 \text{ to } 85 \,^{\circ}\text{C}$ . Typical values are at  $T_{_{A}} = +25 \,^{\circ}\text{C}$ .

| Parameter                        | Symbol                | Conditions                                                | Min  | Тур  | Max  | Units |

|----------------------------------|-----------------------|-----------------------------------------------------------|------|------|------|-------|

| Input Voltage Range              | V <sub>IN</sub>       |                                                           | 2.7  |      | 5.0  | ٧     |

| V Accuracy                       | V                     | $V_{IN} = 4V, V_{DAC} = 0.1V, I_{OUT} = 0.3A$             | 0.25 | 0.3  | 0.35 | V     |

| V <sub>оит</sub> Accuracy        | V <sub>OUT</sub>      | $V_{IN} = 4V, V_{DAC} = 1.1V, I_{OUT} = 0.3A$             | 3.23 | 3.3  | 3.37 | V     |

| V <sub>OUT</sub> Line Regulation | V <sub>OUT LINE</sub> | $V_{IN} = 2.7V \text{ to } 5.0V, V_{DAC} = 0.7V$          |      |      | 0.4  | %/V   |

| V <sub>OUT</sub> Load Regulation | V <sub>OUT LOAD</sub> | $I_{OUT} = 0A \text{ to } 600 \text{ mA}, V_{DAC} = 0.7V$ |      | -0.7 |      | %     |

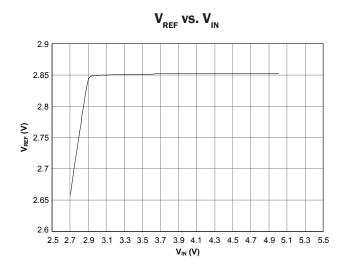

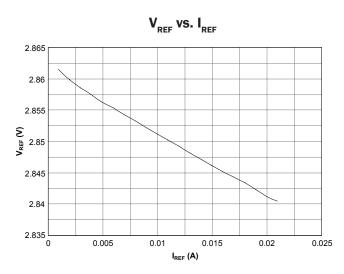

| V <sub>REF</sub> Accuracy        | V <sub>REF</sub>      | I <sub>REF</sub> = 10 mA                                  | 2.8  | 2.85 | 2.9  | V     |

| V <sub>REF</sub> Line Regulation | V <sub>REF LINE</sub> | $I_{REF} = 1 \text{ mA}, I_{OUT} = 0 \text{A}$            |      |      | 0.3  | %/V   |

| V <sub>REF</sub> Load Regulation | V <sub>REF LOAD</sub> | I <sub>REF</sub> = 0.1 to 20 mA                           |      | -0.5 |      | %     |

| V <sub>REF</sub> Load Current    | I <sub>REF</sub>      |                                                           |      |      | 20   | mA    |

| Peak Inductor Current            | I <sub>LX PK</sub>    |                                                           | 0.8  |      | 1.5  | А     |

| Bypass FET Current Limit         | I <sub>PASS</sub>     |                                                           | 1    |      | 2.5  | А     |

<sup>1)</sup> Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

<sup>2)</sup> Tested according to JEDEC standard JESD22-A114-B.

## Electrical Characteristics (Cont.)

| Parameter                                        | Symbol                                | Conditions                                                             | Min  | Тур | Max  | Units |

|--------------------------------------------------|---------------------------------------|------------------------------------------------------------------------|------|-----|------|-------|

|                                                  |                                       | Normal Mode (V <sub>DAC</sub> < 1V)                                    |      | 1.5 |      |       |

| Quiescent Current                                | I <sub>Q</sub>                        | Bypass Mode (V <sub>DAC</sub> > 1.4V)                                  |      | 1   |      | mA mA |

| Shutdown Current                                 | I <sub>SD</sub>                       | LX = open, EN = GND, $V_{OUT}$ = open, $T_A$ = 25°C                    |      | 0.1 | 1    | μA    |

| VDAC Regulated Output<br>Mode                    | V <sub>DAC</sub>                      | V <sub>IN</sub> = 4.2V                                                 | 0.10 |     | 1.20 | V     |

| VDAC Pass-Through                                | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | V <sub>DAC</sub> Rising                                                | 1.28 |     | 1.37 |       |

| Mode Threshold                                   | V <sub>DAC PT</sub>                   | V <sub>DAC</sub> Falling                                               | 1.20 |     | 1.3  | V     |

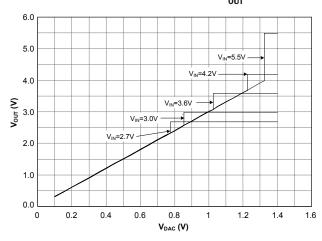

| VDAC to VOUT Transfer<br>Ratio                   | G <sub>v</sub>                        |                                                                        |      | 3   |      | V/V   |

| R <sub>DS ON</sub> of Bypass<br>P-Channel FET    | R <sub>PASS</sub>                     | $I_{OUT} = 100 \text{mA}, V_{IN} = 3 \text{V}, V_{DAC} = 1.4 \text{V}$ |      | 75  |      | mΩ    |

| R <sub>DS ON</sub> of P-Channel<br>Switching FET | R <sub>DSP</sub>                      | I <sub>OUT</sub> = 100mA, V <sub>IN</sub> = 3V                         |      | 400 |      | mΩ    |

| R <sub>DS ON</sub> of N-Channel<br>Switching FET | R <sub>DSN</sub>                      | I <sub>OUT</sub> = 100mA, V <sub>IN</sub> = 3V                         |      | 250 |      | mΩ    |

| LX Leakage Current PMOS                          | I <sub>LXP</sub>                      | V <sub>IN</sub> = 3.6V, LX = 0V, EN = GND                              |      |     | 2    | μA    |

| LX Leakage Current NMOS                          | I <sub>LXN</sub>                      | V <sub>IN</sub> = 3.6V, LX = 3.6V, EN = GND                            |      |     | 2    | μA    |

| VOUT Pin Bypass<br>PMOS Leakage                  | I <sub>LVOUT</sub>                    | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 0V, EN = GND                |      |     | 2    | μA    |

| Oscillator Frequency (Fixed Frequency)           | f <sub>osc</sub>                      | V <sub>DAC</sub> > 0.2V                                                | 0.85 | 1   | 1.15 | MHz   |

| Oscillator Frequency<br>(Variable Frequency)     | f <sub>oscv</sub>                     | V <sub>DAC</sub> = 0.1V                                                | 0.65 |     |      | MHz   |

| Logic Input High                                 | V <sub>IH</sub>                       |                                                                        | 1.6  |     |      | V     |

| Logic Input Low                                  | V <sub>IL</sub>                       |                                                                        |      |     | 0.6  | V     |

| Control Input Current - High                     | I <sub>IH</sub>                       | VDAC/EN =3.6V                                                          |      |     | ±2   | μA    |

| Control Input Current - Low                      | I <sub>IL</sub>                       | VDAC/EN = GND                                                          |      |     | ±2   | μA    |

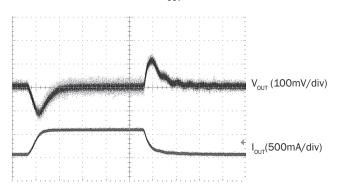

| Enable Transient<br>Over/Undershoot              | OS <sub>EN</sub>                      |                                                                        |      | 20  |      | %     |

| Enable Transient Settling<br>Time                | t <sub>EN-ST</sub>                    |                                                                        |      | 40  |      | μs    |

| VDAC Transient<br>Over/Undershoot                | OS <sub>VDAC</sub>                    |                                                                        |      | 20  |      | %     |

| VDAC Transient Settling<br>Time                  | t <sub>VDAC-ST</sub>                  |                                                                        |      | 40  |      | μs    |

# Electrical Characteristics (Cont.)

| Parameter                                                           | Symbol                | Conditions | Min | Тур | Max | Units |

|---------------------------------------------------------------------|-----------------------|------------|-----|-----|-----|-------|

| Pass-Through Transition<br>Over/Undershoot                          | OS <sub>PASS</sub>    |            |     | 20  |     | %     |

| Pass-Through Transition<br>Settling Time                            | t <sub>PASS-ST</sub>  |            |     | 40  |     | μs    |

| Thermal Shutdown                                                    | T <sub>SD</sub>       |            |     | 160 |     | °C    |

| Thermal Shutdown<br>Hysteresis                                      | T <sub>SDH</sub>      |            |     | 15  |     | °C    |

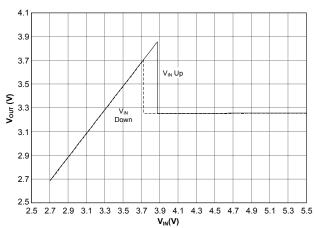

| Auto Pass-Through<br>Threshold (V <sub>IN</sub> -V <sub>OUT</sub> ) | PT <sub>TH</sub>      |            | 400 | 430 | 460 | mV    |

| Auto Pass-Through<br>Threshold Hysteresis                           | PT <sub>TH_HYST</sub> |            | 135 | 160 | 190 | mV    |

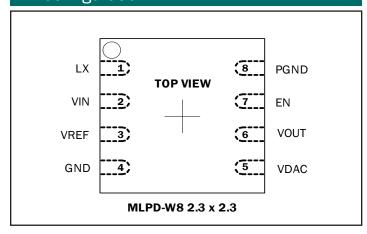

## Pin Configuration

## Ordering Information

| DEVICE                       | PACKAGE          |

|------------------------------|------------------|

| SC250WLTRT <sup>(1)(2)</sup> | MLPD-W8 2.3x2.3  |

| SC250EVB                     | Evaluation Board |

#### Note:

- 1) Available on tape and reel only. A reel contains 3000 devices.

- 2) Device is WEEE and RoHS compliant.

## **Marking Information**

Marking for the 2.3 x 2.3mm MLPD 8 Lead Package: ww = Datecode (Reference Package Marking Design Guidelines, Appendix A)

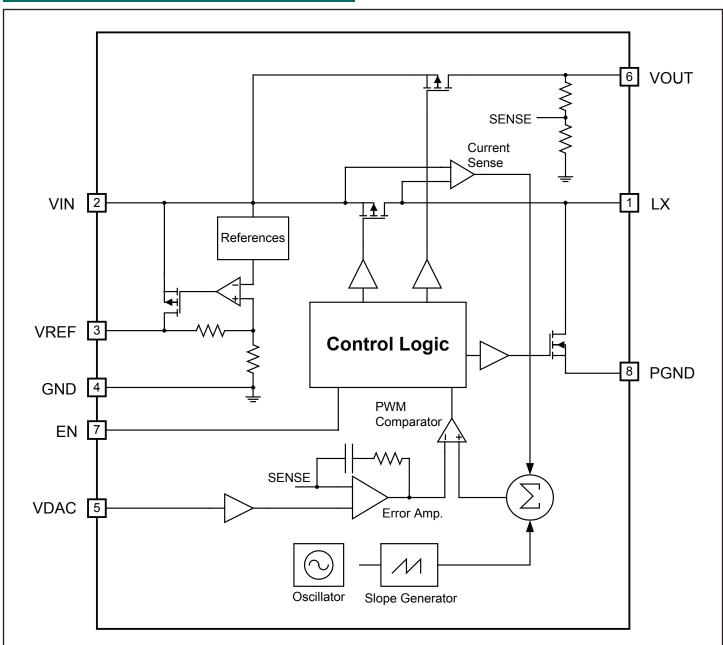

# Block Diagram

## Pin Descriptions

| Pin# | Pin Name | Pin Function                                                                                                                                                                                                                                                 |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | LX       | Inductor connection to the switching FETs                                                                                                                                                                                                                    |

| 2    | VIN      | Input voltage connection                                                                                                                                                                                                                                     |

| 3    | VREF     | 2.85V, 20mA reference supply — can be used as a supply for power amplifier bias inputs or to supply a resistive divider on $V_{DAC}$ to set a fixed level of $V_{OUT}$ .                                                                                     |

| 4    | GND      | Ground connection                                                                                                                                                                                                                                            |

| 5    | VDAC     | Analog control voltage input ranges between 0.1 and 1.2V for control of $V_{\text{OUT}}$ in accordance with the $V_{\text{OUT}}$ = 3 x $V_{\text{DAC}}$ transfer function. $V_{\text{DAC}}$ > 1.4V enables pass-through mode using the internal pass MOSFET. |

| 6    | VOUT     | Regulated output voltage and feedback                                                                                                                                                                                                                        |

| 7    | EN       | Enable digital input: a high input enables the SC250, a low disables the output and reduces quiescent current to less than 1µA and LX becomes high impedance.                                                                                                |

| 8    | PGND     | Ground reference for internal N-channel MOSFET                                                                                                                                                                                                               |

### **Applications Information**

#### **SC250 Detailed Description**

The SC250 adaptive power controller is a step-down, fixed frequency pulse-width modulated DC-DC converter designed for use with RF Power Amplifiers (PAs) in CDMA and WCDMA handsets and modules. The SC250 output is used to supply DC power to the PA rather than connecting the DC input pin directly to the battery supply. A substantial system power efficiency improvement can be achieved by allowing the system controller to adaptively adjust the DC power to the PA, reducing the total power consumption of the device when in low-power mode. To improve efficiency at all RF output gain settings, the PA supply voltage is adjusted in a linear fashion, minimizing PA supply headroom and losses.

A consequence of using the SC250 to power the PA, rather than using a linear regulator or direct connection to the battery, is that less current is needed. Reduced current consumption results in more talk-time for the handset.

#### **Operation Modes**

The SC250 output voltage is dependent on the  $V_{DAC}$  analog control voltage, defined by the following relationship:

$$V_{OUT} = 3 \times V_{DAC}$$

In a typical PA system application, the system controller determines what output power level is needed from the PA and adjusts the VDAC voltage to match the required PA headroom for optimized efficiency.

#### Pass-Through Mode

When the VDAC voltage reaches 1.36V, the SC250 enters pass-through mode. If the demanded output voltage is within 430mV of the input voltage, the SC250 automatically enters pass-through as this exceeds the maximum controlled duty cycle of the power converter. In pass-through mode, the device enables an internal P-Channel MOSFET that bypasses the converter, connecting the output directly to the input. The  $R_{\rm DSON}$  of this FET is extremely low, so there is little voltage drop across the part. Pass-through allows the lowest insertion loss possible between  $\rm V_{IN}$  and  $\rm V_{OUT}$  under high-power conditions, thereby maintaining maximum efficiency under these conditions.

#### **Bias Supply Output**

In addition to the main output, the SC250 also provides a low current LDO output that can be used as a bias supply for power amplifiers. This output provides a regulated 2.85V with output current capability up to 20mA. The 2.85V output is guaranteed for input supply voltages in excess of 2.95V.

#### **Protection Features**

The SC250 provides the following protection features:

- Thermal shutdown

- · Current limit

- Under-voltage lockout

#### **Thermal Shutdown**

The device has a thermal shutdown feature to protect the device if the junction temperature exceeds 150°C. In thermal shutdown, the PWM drive is disabled, effectively tri-stating the LX output. The device will not be enabled again until the temperature reduces by 10°C.

#### **Short-Circuit Protection**

The PMOS and NMOS power devices of the buck switcher stage are protected by current limit functions. In the case of a short to ground on the output, the LX pin will switch with minimum duty cycle. The duty cycle is short enough to allow the inductor to discharge during each cycle, thereby preventing the inductor current from "staircasing."

The pass-through PMOS is also protected by a current limit function. When the part is first enabled in pass-through, the output capacitor charges up with a large surge current. This surge current is internally limited for protection purposes, but the limit is set high enough to meet fast start-up times. In order to protect against a short-circuit condition and to allow the transient response time, an internal timer allows the part to operate under current limit conditions for a maximum of 64 cycles of the internal clock (1MHz typical). If the short-circuit conditions persists, the pass-through PMOS will turn off for 1ms, after which the first timer is restarted. This allows the part to manage thermal dissipation while giving it the ability to recover when the fault condition is removed.

### Applications Information (Cont.)

### **Under-Voltage Lockout**

Under-voltage lockout protection is used to prevent erroneous operation. As the input decreases, the device shuts down when the voltage drops below 2.35V and will not restart until the input voltage exceeds approximately 2.5V.

#### **Inductor Selection**

The SC250 is designed for use with a  $4.7\mu H$  inductor. The magnitude of the inductor current ripple is dependent on the inductor value and can be determined by the following equation:

$$\Delta I_{L} = \frac{V_{\text{OUT}} \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)}{L \times f_{\text{OSC}}}$$

This equation demonstrates the relationship between input voltage, output voltage, and inductor ripple current.

The inductor should have a low DC resistance to minimize the conduction losses and maximize efficiency. As a minimum requirement, the DC current rating of the inductor should be equal to the maximum load current plus half of the inductor current ripple as shown by the following equation:

$$I_{LPK} = I_{OUT(MAX)} + \frac{\Delta I_L}{2}$$

Final inductor selection depends on various design considerations such as efficiency, EMI, size, and cost. Table 1 lists the manufacturers of practical inductor options.

Table 1 — Recommended Inductors

| Manufacturer/Part #          | Value<br>(µH) | DCR<br>(Ω) | Saturation<br>Current (A) | Tolerance<br>(%) | Dimensions<br>LxWxH (mm) |

|------------------------------|---------------|------------|---------------------------|------------------|--------------------------|

| BI Technologies<br>HM66304R7 | 4.7           | 0.072      | 1.32                      | 20               | 4.7 × 4.7 ×3.0           |

| Coilcraft<br>D01608C-472ML   | 4.7           | 0.09       | 1.5                       | 20               | 6.6 × 4.5 ×3.0           |

| TDK<br>VLCF4018T- 4R7N1R0-2  | 4.7           | 0.101      | 1.07                      | 30               | 4.3 × 4.0 ×1.8           |

### **C**<sub>IN</sub> Selection

The source input current to a buck converter is non-continuous. To prevent large input voltage ripple, a low

ESR ceramic capacitor is required. A minimum value of  $10\mu\text{F}$  should be used for sufficient input voltage filtering and a  $22\mu\text{F}$  should be used for improved input voltage filtering.

### $\mathbf{C}_{\text{out}}$ Selection

The internal compensation is designed to work with a certain output filter corner frequency defined by the equation:

$$f_{\text{c}} = \frac{1}{2\pi\sqrt{L \times C_{\text{OUT}}}}$$

This single pole filter is designed to operate with an output capacitor value of  $4.7\mu F$ .

Output voltage ripple is a combination of the voltage ripple from the inductor current charging and discharging the output capacitor, and the voltage created from the inductor current ripple through the output capacitor ESR. Selecting an output capacitor with a low ESR will reduce the output voltage ripple component that is dependent upon this ESR, as can be seen in the following equation:

$$\Delta V_{\text{OUT(ESR)}} = \Delta I_{\text{L(ripple)}} \times ESR_{\text{(COUT)}}$$

Capacitors with X7R or X5R ceramic dielectric are strongly recommended for their low ESR and superior temperature and voltage characteristics. Y5V capacitors should not be used as their temperature coefficients make them unsuitable for this application. Table 2 lists the manufacturers of recommended capacitor options.

Table 2 — Recommended Capacitors

| Manufacturer/Part Number     | Value<br>(μF) | Rated<br>Voltage<br>(VDC) | Туре | Case Size |

|------------------------------|---------------|---------------------------|------|-----------|

|                              |               | (\$50)                    |      |           |

| Murata<br>GRM21BR60J226ME39L | 22            | 6.3                       | X5R  | 0805      |

| Murata<br>GRM188R60J106MKE19 | 10            | 6.3                       | X5R  | 0603      |

| TDK<br>C2012X5R0J106K        | 10            | 6.3                       | X5R  | 0603      |

| Murata<br>GRM188R60J475KE19D | 4.7           | 6.3                       | X5R  | 0603      |

## Applications Information (Cont.)

### **PCB Layout Considerations**

Poor layout can degrade the performance of the DC-DC converter and can be a contributory factor in EMI problems, ground bounce and resistive voltage losses. Poor regulation and instability can result.

A few simple design rules can be implemented to ensure good layout:

- Place the inductor and filter capacitors as close to the device as possible and use short wide traces between the power components.

- 2. Route the output voltage feedback and  $V_{\text{DAC}}$  path away from inductor and LX node to minimize noise and magnetic interference.

- Maximize ground metal on component side to improve the return connection and thermal dissipation.

Separation between the LX node and GND should be maintained to avoid coupling of switching noise to the ground plane.

- 4. To further reduce noise interference on sensitive circuit nodes, use a ground plane with several vias connecting to the component side ground.

## **Typical Characteristics**

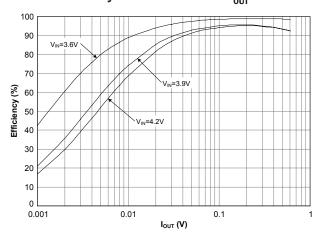

# Efficiency vs. Load Current $V_{out} = 3.2V$

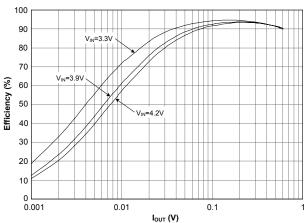

# Efficiency vs. Load Current $V_{OUT} = 2.5V$

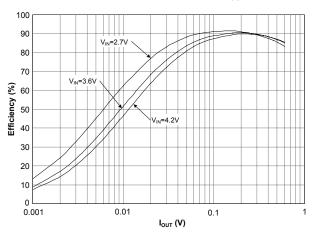

# Efficiency vs. Load Current $V_{out} = 1.5V$

Efficiency vs. Load Current  $V_{OUT} = 1.2V$

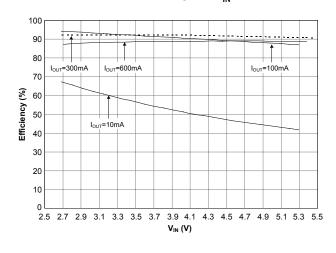

## Efficiency vs. V<sub>IN</sub>

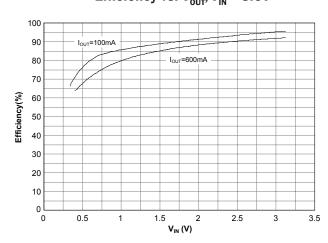

Efficiency vs.  $V_{OUT}$ ,  $V_{IN} = 3.6V$

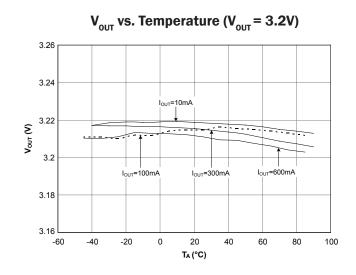

## Typical Characteristics (Cont.)

# Control Transfer Function $I_{out} = 0.3A$

# Auto Bypass Function, $V_{out} = 3.25V$

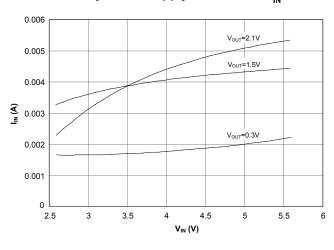

## Dynamic Supply Current vs. $V_{IN}$

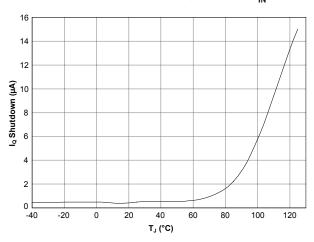

## Shutdown Current vs. Temperature, $V_{IN} = 3.6V$

## Load Regulation, $V_{out} = 2.1V$

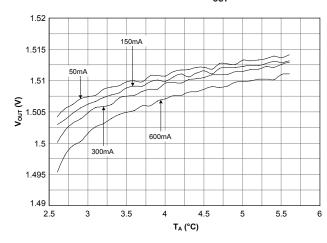

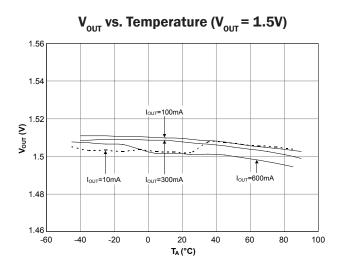

# Line Regulation, $V_{out} = 1.5V$

## Typical Characteristics (Cont.)

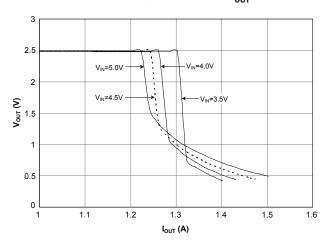

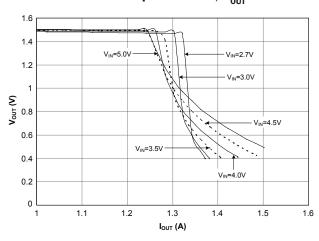

# Maximum Output Current, $V_{out} = 2.5V$

## Maximum Output Current, V<sub>OUT</sub> = 1.8V

## Typical Characteristics (Cont.)

# Maximum Output Current, $V_{\text{out}} = 1.5V$

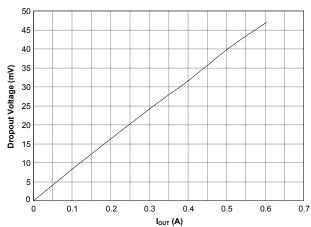

# Dropout Voltage vs. Bypass Load Current

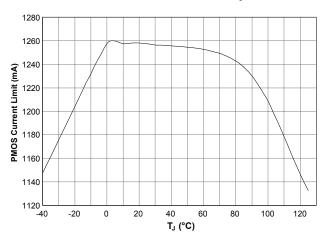

### **PMOS Current Limit vs. Temperature**

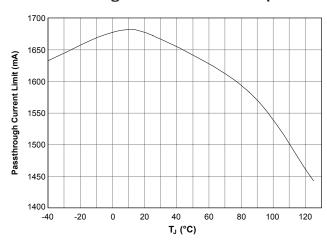

### **Passthrough Current Limit vs. Temperature**

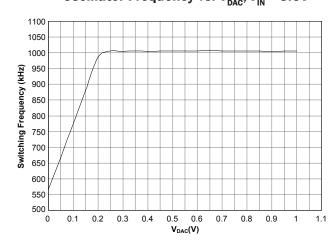

## Oscillator Frequency vs. $V_{DAC}$ , $V_{IN} = 3.6V$

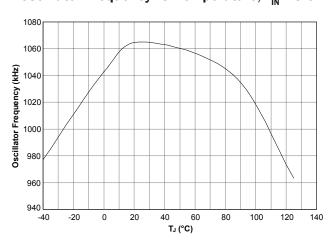

## Oscillator Frequency vs. Temperature, $V_{IN} = 3.6V$

## Typical Characteristics (Cont.)

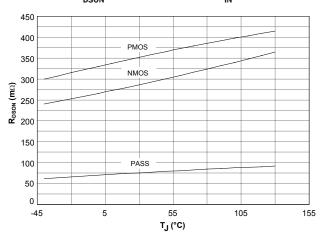

## $R_{DSON}$ vs. Temperature, $V_{IN} = 3.6V$

#### 350 PMOS 300 250 200 150 100 PASS 50 3.0 3.5 4.5 2.5 4.0 5.0 5.5 $V_{IN}(V)$

$R_{\rm DSON}$  vs.  $V_{\rm IN}$

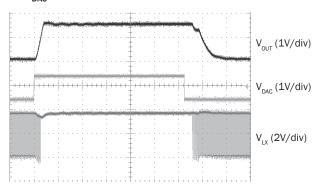

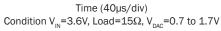

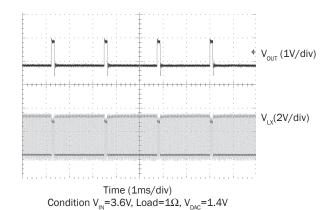

## $V_{DAC}$ Step Response (Pass-through)

## $V_{\mathrm{DAC}}$ Step Response (100% duty)

400

Time (40µs/div) Condition V $_{\rm IN}$ =3V, Load=15 $\Omega,$  V $_{\rm DAC}$ =0.7 to 1V

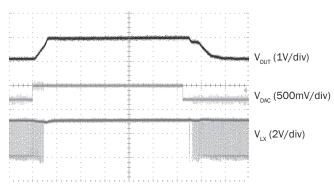

## **V**<sub>DAC</sub> Step Response

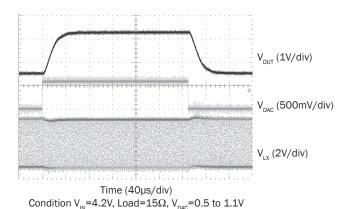

#### **Enable Transient**

## Typical Characteristics (Cont.)

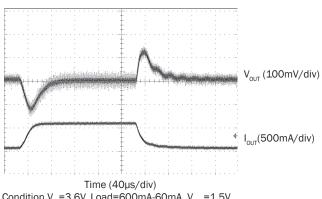

## Load Step response ( $V_{OUT}$ =3.25V)

Time (40µs/div) Condition  $V_{IN}$ =4.2V, Load=600mA-60mA,  $V_{OUT}$ =3.25V

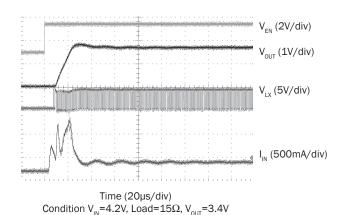

### **Enable Start-Up**

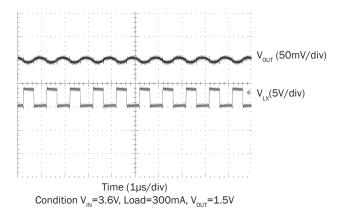

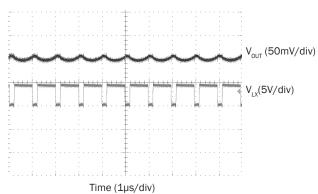

## Output Ripple Waveform (V<sub>OUT</sub>=1.5V)

## Load Step response $(V_{OUT}=1.5V)$

Condition  $V_{IN}$ =3.6V, Load=600mA-60mA,  $V_{OIIT}$ =1.5V

## Output Ripple Waveform (V<sub>out</sub>=3.25V)

Condition  $V_{IN}$ =4.2V, Load=300mA,  $V_{OUT}$ =3.25V

### **Pass-Through Current Limit**

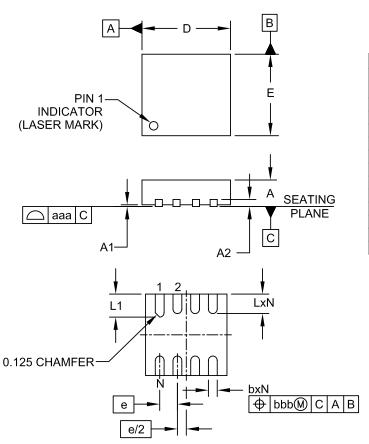

## Outline Drawing - MLPD-W8, 2.3 x 2.3

|         | DIMENSIONS |        |      |             |        |      |

|---------|------------|--------|------|-------------|--------|------|

| ΟΙΜ     | INCHES     |        |      | MILLIMETERS |        |      |

| וואווטן | MIN        | MOM    | MAX  | MIN         | NOM    | MAX  |

| Α       | .028       | .030   | .031 | 0.70        | 0.75   | 0.80 |

| A1      | .000       | .001   | .002 | 0.00        | 0.02   | 0.05 |

| A2      |            | (800.) |      |             | (0.20) |      |

| р       | .008       | .010   | .012 | 0.20        | 0.25   | 0.30 |

| О       | .087       | .091   | .094 | 2.20        | 2.30   | 2.40 |

| П       | .087       | .091   | .094 | 2.20        | 2.30   | 2.40 |

| Ф       | .0         | 20 BS  | C    | 0.          | 50 BS  | C    |

| Г       | .018       | .022   | .026 | 0.45        | 0.55   | 0.65 |

| L1      | .022       | .026   | .030 | 0.55        | 0.65   | 0.75 |

| N       | 8          |        |      |             | 8      |      |

| aaa     | .003       |        |      |             | 0.08   |      |

| bbb     | .003       |        |      |             | 0.08   |      |

#### NOTES:

1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

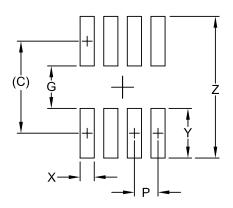

## Land Pattern - MLPD-W8, 2.3 x 2.3

|     | DIMENSIONS |             |  |  |  |  |

|-----|------------|-------------|--|--|--|--|

| DIM | INCHES     | MILLIMETERS |  |  |  |  |

| С   | (.077)     | (1.95)      |  |  |  |  |

| G   | .035       | 0.90        |  |  |  |  |

| Р   | .020       | 0.50        |  |  |  |  |

| Х   | .012       | 0.30        |  |  |  |  |

| Y   | .041       | 1.05        |  |  |  |  |

| Z   | .118       | 3.00        |  |  |  |  |

#### NOTES:

THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

## **Contact Information**

Semtech Corporation

Power Management Products Division

200 Flynn Road, Camarillo, CA 93012

Phone: (805) 498-2111 FAX (805)498-3804

www.semtech.com