# 1.0 Product Description

### 1.1 Functional Overview

The VSC9142 is a dual-mode STS-48c/AU-4-16c SONET/SDH to packet/ATM framing device. In the POS (packet over SONET) mode, the device can be used in equipment interconnecting IP/PPP/HDLC equipment over public or private SONET/SDH networks. Similarly, in the ATM over SONET (ATM) mode, this device can be used in equipment interconnecting ATM switches. Features of the VSC9142 include: full insertion/extraction of the transport overhead, bit error rate and extensive SONET/packet/cell performance monitoring, packet/cell filtering and discarding functionalities, JTAG TAP controller, and an 8-bit CPU interface with eight general purpose I/O ports.

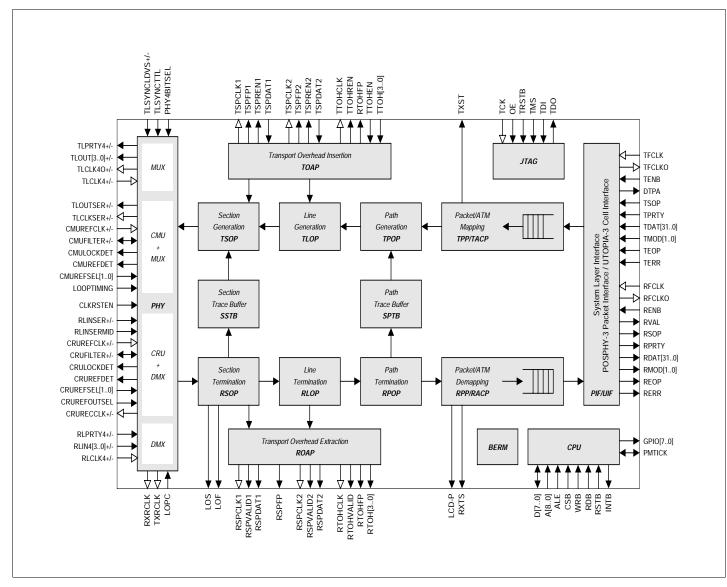

When used in conjunction with a high-speed mux/demux transceiver, this device provides a complete physical layer solution for packet/ATM over SONET/SDH, LAPS (ITU COM 7-224), and certain Ethernet over SONET/SDH applications at the STS-48/STM-16 line rate. In addition, this device provides a 4-bit interface for higher bandwidth applications at STS-192/STM-64 line rates. The VSC9142 integrates the following major functional blocks, illustrated in Figure 1.1.

- Serial or 4-bit Line-Side Interface

- 32-bit Packet/UTOPIA Drop-Side Interface

- Packet/ATM Mapping/Demapping

- SONET/SDH Section, Line, and Path SPE/VC Overhead Processing

- Transport Overhead Insertion/Extraction

- SONET/SDH Section and Path Trace Buffers

- Generic 8-Bit Microprocessor Interface

- Bit Error Rate Monitor

- JTAG Test Access Port

1.0 Product Description Page 1

Figure 1.1. VSC9142 Functional Block Diagram

1.0 Product Description

### 1.2 VSC9142 Functional Blocks

The VSC9142 is partitioned into the functional blocks shown in Figure 1.1. The bullets below define the essential function of the data transmit and receive blocks. The sections following the bullets summarize the key features of each functional block in Figure 1.1.

- Physical Line Side Interface (PHY) is the interface between the line side and the VSC9142's SONET/SDH overhead and payload processing. The PHY performs clock and data recovery on received data in addition to deserialization. Serialization and clock multiplication is performed on the transmit data. An optional 4-bit interface for STS-192 use is provided in both the transmit and receive direction.

- Section overhead processing (RSOP) responsibilities in the receive (Rx) flow are frame synchronization and descrambling, plus Section alarms and error monitoring. Transmit (Tx) Section overhead processing (TSOP) operations include frame pattern generation with scrambling, and alarm and Section error insertion.

- The Rx flow portion of the Line overhead processing blocks (RLOP/TLOP) handles Line

alarm and error monitoring, automatic protection switching, and synchronization status

extraction on the Rx flow. Line overhead processing in the Tx flow include Line alarm

insertion, error code insertion, automatic protection switching insertion, and

synchronization status insertion.

- Rx flow functions in the Path overhead processing blocks (RPOP/TPOP) include pointer interpretation, Path overhead extraction, and monitoring Path alarms. Tx functions for Path overhead processing are pointer generation, error code (B3) insertion, and status backreporting.

- Packet processing is handled by the RPP/TPP blocks (which also contain the RACP/TACP ATM Cell processing blocks, described next). Packet processing includes PPP/HDLC framing and deframing when the VSC9142 is used in Packet-over-SONET/SDH applications. In the Rx path, this includes HDLC frame boundary alignment, decompression of the PPP Octet-Stuffing procedure, detection of short/long packets, FCS checking, and abort sequence detection. Tx functions are PPP packet encapsulation, PPP octet stuffing, generation of HDLC frames, FCS generation, and scrambling. Various diagnostic and performance monitoring features are also provided in these blocks.

- The ATM cell processing blocks (RACP/TACP) perform ATM cell mapping and demapping for ATM-over-SONET/SDH applications. Rx flow functions include ATM cell boundary alignment (cell delineation), idle/unassigned cell filtering, single bit error correction in cell headers, cell payload descrambling, and performance monitoring. Tx flow functions include HEC field generation for ATM cell headers, cell rate adaptation using idle/unassigned cells, and cell payload scrambling.

- The receive/transmit FIFOs (Rx FIFO/Tx FIFO) provide clock domain synchronization

and buffering between the SONET/SDH transmission path and the drop-side

ATM/packet FIFO interface. FIFO overrun/underrun conditions are detected, and

programmable full/empty flags are provided.

- The overhead access port (ROAP/TOAP) blocks enable extraction and insertion of transport overhead octets for SONET/SDH frames.

- The SONET/SDH Section/Path trace buffers (SSTB/SPTB) handle extraction and

insertion of trace messages. The Rx side extracts and compares received messages with

expected messages and performs persistency checks. The Tx side inserts trace messages.

- The POS-PHY Level 3 Packet Interface/UTOPIA-3 like ATM Cell Interface (PIF/UIF) block provides a physical drop-side user-interface between a packet/ATM network and the SONET/SDH flows in the VSC9142 device. The primary external interfaces for the PIF/UIF block are two 32-bit busses, one to transmit and one to receive data.

- The bit error rate monitor (BERM) block provides overall performance monitoring for the link, measuring BERs down to 10<sup>-10</sup>.

- The JTAG test access port (JTAG TAP) enables external boundary scan compliant with the IEEE 1149.1 Standard Test Port and Boundary Scan Architecture standard.

- This generic microprocessor interface (CPU) facilitates all device configuration, status and performance information extraction, and test-mode operations.

## 1.2.1 Transmit Path Processing

Physical Line Side Interface (PHY)

- Selectable reference frequency for the clock multiplication unit

- Reference and lock detect signals for the clock multiplication unit

Page 4 1.0 Product Description

- Looptiming ability to lock the transmit clock to the recovered line clock

- Facility loopback capability for special application or test purposes

- 4-bit interface with programmable parity bit (even or odd) for outgoing data, and synchronization pin (TLSYNC) for STS-192/STM-64 applications

- Programmable reference clock output (8kHz, 19MHz, 38MHz, or 78MHz) derived from the transmit line side clock, either the clock multiplier clock the 4-bit transmit line clock

#### SONET/SDH Section Overhead Generation (TSOP)

- Supports insertion of Line Alarm Indication Signal (AIS-L; i.e., all "1s" in the line-side transmit data stream except for Section overhead). AIS-L insertion can be automatically triggered by activity on the special purpose serial interfaces.

- Computes and inserts the Section BIP-8 code in B1 octets of transmitted frames (insertion of B1 errors can be forced for diagnostics purposes)

- Generates and inserts A1 A2 framing octets in transmitted frames (insertion of framing bit errors can be forced for diagnostics purposes)

- J0 octet supports both SONET and SDH formats, or can be programmed to a fixed value compatible with older equipment using C1 identification octets

- Z0 growth octets supports both SONET and SDH formats, or can be programmed to carry C1 identification octets for compatibility with older equipment

- Optionally scrambles the outgoing data stream with a frame-synchronous scrambler of a sequence length of 127 and a generating polynomial of  $1 + x^6 + x^7$

- Supports forced insertion of all "0s" (LOS) in the outgoing data stream after scrambling for diagnostic purposes

- Enables octets present at the special purpose input ports in the TOAP block to be inserted into the D1-D3, E1, F1 and J0 octets of the outgoing Section overhead

- Enables all reserved Section overhead octets (i.e., for future national or international standards) to be written as 0x00

SONET/SDH Section/Path Trace Buffers (SSTB/SPTB) Transmit Functions

- Store, frame, and insert programmable trace messages into transmit stream

- Supports three different Section/Path trace message formats (transported in the J0 octet) in both the transmit and receive directions (i.e., single octet SONET messages, 16-octet SDH messages, or 64-octet SONET CLLI messages)

- Checks received Section/Path trace messages for persistency and issues a "mismatch" alarm if required

#### SONET/SDH Line Overhead Generation (TLOP)

- Generates and inserts programmable K1 K2 Automatic Protection Switching (APS) octets in the outgoing data stream

- Generates and inserts Line Remote Defect Indication (RDI-L) in the outgoing data stream on detection of LOS, LOF, or AIS-L alarms in the receive stream

- Calculates and inserts Line BIP-384 code in outgoing B2 octets of the current frame (insertion of B2 errors can be forced for diagnostics purposes)

- Enables the number of Line BIP-384 errors detected in the Receive Line Overhead Processor (RLOP) to be backreported via Line REI in the M1 octet (up to 255 errors can be backreported per frame in individual mode)

- Supports individual- and block-mode backreporting via the M1 octet (insertion of M1 errors can be forced for diagnostics purposes)

- Provides for insertion of a programmable Synchronization Status (SS) value in the S1 octet

- Inserts octets present at the special purpose ports of the Transmit Overhead Access Port (TOAP) into the D4-D12, E2, S1, K1 and K2 octets of the outgoing Line overhead

- Enables all reserved Line overhead octets (i.e., for future national or international standards) to be overwritten as 0x00

- H1, H2, and H3 octets from the Transmit Overhead Access Port (TOAP) can be inserted

into the H1, H2, and H3 overhead octets, or applied as an error mask to the H1, H2, and

H3 overhead octets

SONET/SDH Overhead Insertion Port (TOAP)

Page 6 1.0 Product Description

- Provides two identical, independent special purpose ports to enable insertion of special purpose octets and certain SONET/SDH alarms specific to Automatic Protection Switching (APS) into the transport overhead

- Enables selective insertion of acquired transport overhead octets into corresponding transmitted overhead octets of the SONET/SDH frame via the nibble input port TTOH[3..0]

#### SONET/SDH Path Overhead Generation (TPOP)

- H1 H2 pointer octets can be programmed to support SONET or SDH

- Pointer diagnostic functions are provided, and the remaining 47 H1 H2 octets are programmable

- Path BIP-8 is computed and inserted in the B3 octet. B3 errors can be inserted for diagnostics.

- The number of Path BIP-8 errors detected in the Receive Path Overhead Processor (RPOP) is backreported as Path Remote Error Indications (REI-P) for insertion in G1 octets (supports both individual- and block-mode accumulation).

- Path Remote Defect Indications (RDI-P) insertion is optionally enabled or disabled for the following alarms: LOS, LOF, AIS-L, AIS-P, LOP-P, TIM-P, UNEQ-P, LCD-P and PLM-P. Current and previous RDI-P formats are supported.

- Programmable Path Signal Label (C2) and Path trace (J1) octets

- Programmable F2, H4, Z3, Z4, and Z5 octets

#### Packet Processing and Monitoring (TPP)

- Programmable insertion of HDLC Flag Sequence octet

- Programmable value for minimum Flag Sequence octets to separate HDLC frames

- HDLC Address-Control-compression insertion control mechanism

- Programmable Address field insertion after start of Flag Sequence

- Programmable Control field insertion after start of Address field

- The Frame Check Sequence (FCS) can be generated using two methods:

- Using the 16-bit, CRC-CCITT generating polynomial  $1 + x^5 + x^{12} + x^{16}$

- Using the 32-bit, CRC-32 generating polynomial  $1 + x + x^2 + x^4 + x^5 + x^7 + x^8 + x^{10} + x^{11} + x^{12} + x^{16} + x^{22} + x^{23} + x^{26} + x^{32}$

- Octet Stuffing, or "escaping", can be applied after FCS generation and partial scrambling, if enabled. The Control Escape octet and Octet Stuffing Mask are programmable. The Asyc-Control-Character-Map (ACCM) can accommodate a maximum of five octet values, and each value can be individually enabled or disabled.

- Transmitted data is scrambled using a self-synchronizing scrambler (SSS) polynomial  $1 + x^{43}$ . Full and/or partial scrambling can be independently enabled or disabled.

- The inserted PPP Protocol field can be extracted from the Tx FIFO or internallygenerated with a programmable size and value.

- The Tx FIFO is programmable over a range from 1 to 4095 words, or up to 16380 octets

of data. All valid packet octets stored in the Tx FIFO are read out and mapped to PPP

Protocol/Information fields of generated PPP/HDLC frames.

- Supports packet- and word-based Tx PIF/UIF transfer modes

- The TXF\_ERR signal enables errors to be inserted into the FCS, or the transmitted HDLC frame to be aborted.

- Transmitted Address, Control or Protocol fields can be XORed with a programmable mask value via the CPU interface for diagnostic purposes.

- 32-bit performance monitoring counters can be programmed to observe:

- Octets read from the Tx FIFO

- Good HDLC frames transmitted (i.e., non-aborted, non-FCS errored)

- Aborted HDLC frames transmitted

- FCS Errored HDLC frames transmitted

- Long or short packets read from the Tx FIFO

- Empty HDLC frames transmitted

- Octets before or after octet-stuffing (excluding Abort sequences)

ATM Cell Mapping (TACP)

Page 8 1.0 Product Description

- ATM cells are mapped to SONET STS-48c SPEs or SDH STM-16 AU-4-16cs.

Programmable idle/unassigned cells are inserted into the cell stream.

- Optional scrambling of the 48-octet information field using the self-synchronizing scrambling polynomial  $1 + x^{43}$

- HEC generator carries out CRC-8 calculations over the first four header octets using the generating polynomial  $1 + x + x^2 + x^8$ , and the coset polynomial  $1 + x^2 + x^4 + x^6$  can be added to the result. The HEC can then be optionally inserted into the fifth octet of cell headers as they are read from the Tx FIFO.

- Tx FIFO accommodates up to eight ATM cells

#### UTOPIA-Level 3/POS-PHY-3 Cell/Packet Transmit Interface (PIF/UIF)

- Standards-compliant POS (packet over SONET/SDH) interface

- Programmable parity bit (even or odd) checking

- Interface supports both word- and packet/cell-level transfer modes

- Single PHY UTOPIA-3 like interface for ATM applications

- Programmable "decode-response time" for flow control flags

- DTPA signal output to indicate "level" of the Tx FIFO word count based on programmable high and low "water marks"

- Tx FIFO reset or flush via the CPU interface

## 1.2.2 Receive Path Processing

Physical Line Side Interface (PHY)

- Selectable reference frequency for the clock recovery unit

- Reference and lock detect signals for the clock recovery unit

- Equipment loopback capability for special application or test purposes

- 4-bit interface with programmable parity bit (even or odd) checking

- Programmable reference clock output (8kHz, 19MHz, 38MHz, or 78MHz) derived from the receive line side clock, either the recovered serial line clock or the 4-bit receive clock

- Dedicated input for Loss of Optical Carrier (LOPC) alarm monitoring

#### SONET/SDH Section Overhead Termination (RSOP)

- Frame alignment via A1/A2 frame pattern recognition in incoming data stream

- Supports 12-, 24-, or 48-bit A1/A2 framing patterns

- Out Of Frame (OOF) and Loss Of Frame (LOF) alarm condition detection

- Issues alarms for Loss Of Frame (LOF) condition based on programmable monitoring of OOF condition

- Optionally descrambles the incoming data stream with a generating polynomial of  $1 + x^6 + x^7$  and a sequence length of 127

- Detects and accumulates Section BIP-8 errors from the B1 octet of received frames (supports both individual- and block-mode accumulation)

- Monitors for absence of transitions or "all-zero" pattern in the incoming data stream prior to descrambling

- Provides programmable detection and termination criteria for Loss Of Signal (LOS) condition

- Supports insertion of Line Alarm Indication Signal (AIS-L; i.e., all "1s" in the line side receive data stream except for Section overhead). AIS-L insertion can be automatically triggered on detection of LOS, LOF, or Loss of Optical Carrier (LOPC) conditions.

- Enables extraction of the entire Section overhead via the Receive Overhead Access Port (ROAP)

- Extracts J0, E1, F1, and D1-D3 octets from Section overhead, and subsequently inserts them into octets on special purpose output ports in the ROAP block

#### SONET/SDH Section/Path Trace Buffers (SSTB/SPTB) Receive Functions

• Checks received Section trace messages for persistency and issues a "mismatch" alarm if required

Page 10 1.0 Product Description

Supports three different Section trace message formats (transported in the J0 octet) in both the transmit and receive directions (i.e., single octet SONET messages, 16-octet SDH messages, or 64-octet SONET CLLI messages)

#### SONET/SDH Line Overhead Termination (RLOP)

- Extracts and filters Line Remote Defect Indication (RDI-L) and Line Alarm Indication Signal (AIS-L) alarms from received K2 octets (supports programmable filtering constraints)

- Detects and accumulates Line BIP-384 errors from received B2 octets (supports both individual- and block-mode accumulation)

- Detects and accumulates Line Remote Error Indications (REI-L) from received M1 octets (supports both individual- and block-mode accumulation)

- Extracts and filters Synchronization Status (SS) from received S1 octets (supports "unstable/mismatch" alarms and programmable filtering constraints)

- Extracts and filters K1/K2 Automatic Protection Switching (APS) octets (supports "unstable" alarms and programmable filtering constraints)

- Optionally extracts Line overhead via the ports in the ROAP block

- Extracts D4-D12, S1, E2, and K1-K2 octets from Line overhead, and subsequently inserts them into octets on the special purpose output ports in the ROAP block

#### SONET/SDH Overhead Extraction Port (ROAP)

- Provides two identical, independent special purpose ports to enable extraction of special purpose octets and certain SONET/SDH alarms specific to Automatic Protection Switching (APS) from the transport overhead

- Outputs the RSPFP frame pulse signal, as well as clocks and control signals associated with each output stream.

- Enables acquisition of the entire Section/Line transport overhead via the nibble output port RTOH[3..0]

SONET/SDH Path Overhead Termination (RPOP)

- Extracts and interprets H1 H2 pointer octets which are used to define the SONET SPE (synchronous payload envelope) or SDH VC (virtual container) according to ANSI T1.105 and ITU-T G.707 recommendations

- Monitors H1 H2 octets for concatenation indication (CI)

- Provides diagnostic pointer functions

- Supports Path Alarm Indication Signal (AIS-P) and Loss of Pointer (LOP-P) alarm declaration

- Detects and accumulates Path BIP-8 errors from received B3 octets (supports both individual- and block-mode accumulation)

- Detects and accumulates Path Remote Error Indications (REI-P) from received G1 octets (supports both individual- and block-mode accumulation). Up to 64000 individual errors can be detected per second.

- Programmable detection of Path Remote Defect Indications (RDI-P) from received G1 octets

- Programmable detection and alarm generation for Path Signal Label from received C2 octets

#### Packet Processing and Monitoring (RPP)

- Programmable identification of the HDLC Flag Sequence

- Programmable detection and discard of invalid frames

- Programmable expected Control Escape and Octet Destuffing Mask

- Programmable expected Address and Control fields

- Programmable Protocol field declaration and processing

- Detects Abort Sequence in incoming HDLC frames

- Verifies the received Frame Check Sequence (FCS) field

- The Frame Check Sequence (FCS) can be generated using two methods:

- Using the 16-bit, CRC-CCITT generating polynomial  $1 + x^5 + x^{12} + x^{16}$

Page 12 1.0 Product Description

- Using the 32-bit, CRC-32 generating polynomial  $1 + x + x^2 + x^4 + x^5 + x^7 + x^8 + x^{10} + x^{11} + x^{12} + x^{16} + x^{22} + x^{23} + x^{26} + x^{32}$

- Descrambles received data using self-synchronizing scrambler (SSS) polynomial  $1 + x^{43}$  (full and/or partial descrambling can be independently enabled or disabled)

- Programmable long- and short-packet checking

- Programmable support for Self Describing Padding

- Optional storage of PPP Protocol field in Rx FIFO

- 4096 word Rx FIFO accommodates up to 16380 PPP Protocol/Information field octets

- Two different programmable definitions for received "errored" HDLC frames

- Programmable packet discard and error marking filter.

- 32-bit performance monitoring counters to observe:

- Aborted HDLC frames received

- FCS errored HDLC frames received

- Empty HDLC frames received

- Received HDLC frames with Address-Control-compression found

- Long or short packets received

- Invalid frames received

- Octets received before or after octet destuffing

- Frames received, excluding invalid frames

- Packets discarded by label filtering

- Error-marked packets from label filtering

- Packets stored in the Rx FIFO

- Error-marked packets stored in the Rx FIFO

- Packet octets stored in the Rx FIFO

- PPP padding octets received

- SPE Transparent Mode passes the SONET STS-48c SPE or SDH STM-16 AU-4-16c payload directly to the Rx FIFO without processing

ATM Cell Demapping (RACP)

- Cell Delineation is completed using a shortened cyclic code with the generating

polynomial 1 + x + x<sup>2</sup> + x<sup>8</sup>. The coset polynomial 1 + x<sup>2</sup> + x<sup>4</sup> + x<sup>8</sup> can be added to the

calculated HEC check bits before comparison.

- Supports single-bit header error correction, as well as programmable cell dropping during single or multiple error detection

- Optional descrambling of the 48-octet information field using the self-synchronizing descrambler polynomial  $1+\mathbf{x}^{43}$

- Cell filtering via programmable GFC, PTI, or CLP fields

- Detection and monitoring of correctable and uncorrectable HEC errors, as well as the number of cells written to the Rx FIFO

- Rx FIFO accommodates up to eight ATM cells

#### UTOPIA-Level 3/POS-PHY-3 Cell/Packet Receive Interface (PIF/UIF)

- Standards-compliant POS (packet over SONET/SDH) interface

- Programmable parity bit (even or odd)

- Interface supports both word- and cell/packet-level transfer modes

- Single PHY UTOPIA-3 like interface for ATM applications

- Rx FIFO reset or flush via the CPU interface

## 1.2.3 Microprocessor Interface (CPU)

- Read/write support for all configuration bits, and access regardless of device clock source status (except reset state)

- Configuration bits include selection bits, interrupt masking bits, and programmable counter/control values

- Provides eight programmable General Purpose Input/Output (GPIO) ports for monitoring and controlling external signals

- All GPIOs support bistable interrupts when configured as input ports

Page 14 1.0 Product Description

Clock activity monitors are available on all input clocks

### 1.2.4 JTAG Test Access Port (JTAG TAP)

The JTAG test access port (TAP) enables external boundary scan to be performed in compliance with the IEEE 1149.1 Standard Test Port and Boundary Scan Architecture Standard

### 1.2.5 Bit Error Rate Monitor (BERM)

- Bit error rate monitoring based on Line BIP (B2 octet) error codes (measurement precision down to 10-10)

- Four independent BER monitors with individual programmable accumulation periods, saturation thresholds (i.e., maximum number of errors that can be accumulated per frame), and alarm thresholds

- BER Signal Degrade (BER-SD) alarm is provided for BER monitors 1 and 2

- BER Signal Fail (BER-SF) alarm is provided for BER monitors 3 and 4

# 1.3 Applications

The VSC9142 facilitates the development of highly-integrated, single-board STS-48/STM-16 with concatenated payload to packet/ATM interface line cards. In the POS (packet over SONET) mode, the device can be used to interconnect IP/PPP/HDLC equipment to public or private SONET/SDH networks. Similarly, in the ATM over SONET (ATM) mode, this device can be used to interconnect ATM switches. The VSC9142 is an ideal platform for developing highly-integrated switches, routers, hubs; WAN equipment; and test systems.

## 1.3.1 Typical System Utilization

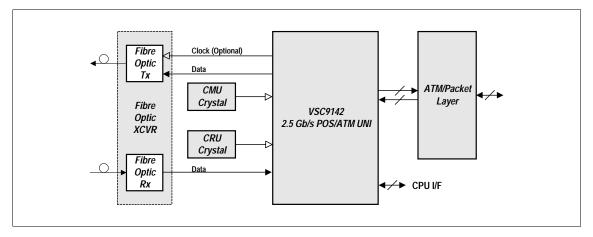

Since the VSC9142 contains all necessary physical interface blocks, the device can mate directly to the Optical transceiver. Figure 1.2 shows a top-level view of a typical ATM or packet over SONET application for the VSC9142.

Figure 1.2. Typical ATM- or packet-to-SONET Interface Application

## 1.3.2 Loopback Configurations

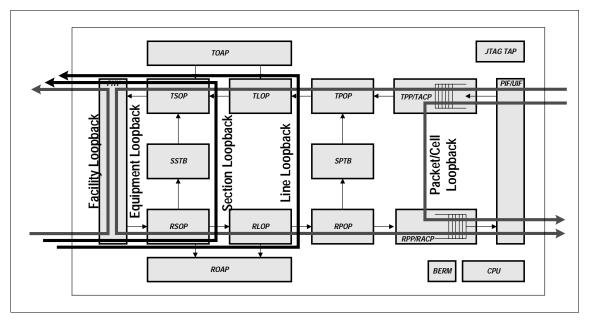

System development and test are simplified via five internal loopback modes. These include equipment, facility, section, line, and packet/UTOPIA loops (see Figure 1.3). The VSC9142's facility loopback mode enables the device to be used for regeneration applications. In this capacity, connections to the device's drop side are not required. In equipment and drop loop modes, external clock sources are muxed internally.

- Facility Loopback connects the PHY block receive input (post demultiplexing) back to the PHY transmit output. The receive and transmit core clocks must be frequency locked via looptiming or register configuration.

- Equipment Loopback connects the data path output from the TSOP block (transmit direction) back to the input of the RSOP block (receive direction). The receive core clock must be set equal to the transmit core clock, via looptiming or register configuration. Likewise RFCLK and TFCLK are required to be frequency locked.

- Section Loopback connects the data path output from the RSOP block to the input of the TSOP block. The receive and transmit core clocks must be frequency locked.

- Line Loopback connects the data path output from the RLOP block to the input of the TLOP block. The receive and transmit core clocks must be frequency locked.

- Packet/Cell Loopback connects the output from the Tx FIFO in the TPP/TAPC block to

the input of the Rx FIFO in the RPP/RAPC block. The receive and transmit core clocks

are required to be frequency locked.

Page 16 1.0 Product Description

Figure 1.3. VSC9142 Internal Loopback Paths

## 1.4 Pin Definitions

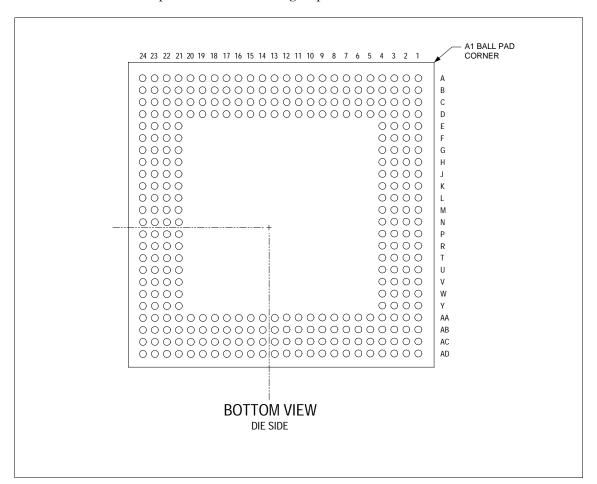

Figure 1.4 identifies the external ball pads in the 320-pin BGA package. Table 1.1 provides a detailed functional description of all hardware signal pins in the device.

Figure 1.4. VSC9142 320 BGA Ball Pad Identification

Page 18 1.0 Product Description

Table 1.1. Hardware Signal Definitions (1 of 12)

|                                  | Pin Label                                                                                            | Pad                                                  | I/O | Туре | Signal Name                               | Description                                                                                                                                                                                                                                                                             |

|----------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | RLINSER-<br>RLINSER+                                                                                 | F24<br>G24                                           | I   | PECL | Serial Line<br>Receive Data               | Serial line data input.                                                                                                                                                                                                                                                                 |

|                                  | RLIN4[0]-<br>RLIN4[0]+<br>RLIN4[1]-<br>RLIN4[1]+<br>RLIN4[2]-<br>RLIN4[2]+<br>RLIN4[3]-<br>RLIN4[3]+ | D22<br>E21<br>E22<br>D23<br>F21<br>F22<br>E23<br>F23 | I   | LVDS | Parallel Line<br>Receive Data             | This is the parallel line-side receive data bus for the incoming STS-48c/STM-16 AU-4-16c data stream. RLIN4[3] is the most significant and first bit arriving bit on the serial data stream. RLIN4[30] is sampled on the rising edge of RLCLK4+. RLIN4[30]+ are the true signal values. |

|                                  | RLPRTY4-<br>RLPRTY4+                                                                                 | C22<br>C23                                           | I   | LVDS | Parallel Line<br>Receive Parity           | This is a programmable (even/odd) parity bit for parallel line receive data RLIN4[30]. RLPRTY4 is sampled on the rising edge of RLCLK4+. RLPRTY4+ is the true signal value.                                                                                                             |

| ıals                             | RLCLK4-<br>RLCLK4+                                                                                   | D24<br>C24                                           | I   | LVDS | Parallel Line<br>Receive Clock            | This is the reference clock input for the parallel line-receive data carried in RLIN4[30]+/ The nominal frequency is 622.08 MHz for STS-48c/STM-16 AU-4-16c operation. RLCLK4+ is the true signal value.                                                                                |

| Physical Interface (PHY) Signals | RLINSERMID                                                                                           | H23                                                  | I   | N/A  | Serial Line<br>Receive Data<br>Center Tap | RLINSER+/- has a 100 ohms on-chip resistor termination which has a center tap between the two 50 ohm resistors. The center tap can be used to bias the centerpoint for single ended applications or decoupled to GND for differential applications.                                     |

| terfac                           | CRUREFCLK-<br>CRUREFCLK+                                                                             | J21<br>J22                                           | I   | PECL | CRU Reference<br>Clock                    | This input is the reference clock used within phase locked loop in the clock recovery unit.                                                                                                                                                                                             |

| cal In                           | CRUREFDET                                                                                            | AD15                                                 | 0   | TTL  | CRU Reference<br>Clock Detect             | This output indicates the presense of clock transistions on CRUREFCLK+/ The signal is active high.                                                                                                                                                                                      |

| Physic                           | CRULOCKDET                                                                                           | AC15                                                 | 0   | TTL  | CRU Lock Detect                           | This output indicatest the lock status of the PLL within the CRU with respect to CRUREFCLK+/ The signal is active high.                                                                                                                                                                 |

|                                  | CRUREFSEL1<br>CRUREFSEL0                                                                             | AB15<br>AA15                                         | I   | TTL  | CRU Reference<br>Clock Select             | These inputs select which frequency is to be expected on CRUREFCLK+/ The binary combination of the two pins are described below (CRUREFSEL0 noted first).  00 78 MHz  01 155 MHz  10 311 MHz                                                                                            |

|                                  | CRURECCLK-<br>CRURECCLK+                                                                             | K24<br>J24                                           | 0   | PECL | CRU Recovered<br>Clock                    | This reference clock output is derived from the 2.5 Gb/s reference clock divided down according to CRUREFSEL[10].                                                                                                                                                                       |

|                                  | CRUFILTER-<br>CRUFILTER+                                                                             | L23<br>K22                                           | I   | N/A  | CRU Loop Filter                           | These inputs are brought off-chip to connect to a capacitor which completes the CRU loop filter. CRUFILTER+ should be connected to one side of a 0.1uF capacitor while CRUFILTER- should be connected to the other side of the capacitor.                                               |

|                                  | CRUREFOUTSEL                                                                                         | AD16                                                 | I   | TTL  | CRURECCLK<br>Output Selector              | This input selects the clock to be output on pins CRURECCLK+/ A high level selects a looped version of the reference clock, while a low level selects the divided version of the recovered clock.                                                                                       |

Table 1.1 Hardware Signal Definitions (2 of 12)

|                                          | Pin Label                                                                               | Pad                                                    | I/O | Туре | Signal Name                            | Description                                                                                                                                                                                                                                                                                                              |

|------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|-----|------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | TLOUTSER-<br>TLOUTSER+                                                                  | N24<br>M24                                             | 0   | PECL | Serial Line<br>Transmit Data           | Serial line data output.                                                                                                                                                                                                                                                                                                 |

|                                          | TLCLKSER-<br>TLCLKSER+                                                                  | R24<br>P24                                             | 0   | PECL | Serial Line<br>Transmit Clock          | Serial line clock output                                                                                                                                                                                                                                                                                                 |

|                                          | TLOUT4[0]- TLOUT4[0]+ TLOUT4[1]- TLOUT4[1]+ TLOUT4[2]- TLOUT4[2]+ TLOUT4[3]- TLOUT4[3]+ | V23<br>V22<br>V24<br>W23<br>Y22<br>W21<br>AA24<br>AA23 | 0   | LVDS | Parallel Line<br>Transmit Data         | This is the parallel line-side transmit data bus for the outgoing STS-48c/STM-16 AU-4-16c data stream. TLOUT4[3] is the most significant and first transmitted bit in the serial data stream. TLOUT4[30] is latched out the rising edge of TLCLK4+, but is centered about TLCLK4O TLOUT[30]+ are the true signal values. |

| Physical Interface (PHY) Signals (cont.) | TLPRTY4-<br>TLPRTY4+                                                                    | U23<br>U22                                             | 0   | LVDS | Parallel Line<br>Transmit Parity       | This is a programmable (even/odd) parity bit for parallel line transmit data TLOUT4[3.0]. TLPRTY4 is latched out on the rising edge of TLCLK4+, but is centered about TLCLK4O TLPRTY4+ is the true signal value.                                                                                                         |

| (PHY) Sign                               | TLCLK4-<br>TLCLK4+                                                                      | T24<br>U24                                             | I   | LVDS | Parallel Line<br>Transmit Clock        | This is the reference clock input for the parallel line-transmit data carried in TLOUT4[30]+/ The nominal frequency is 622.08 MHz for STS-48c/STM-16 AU-4-16c operation. TLCLK4+ is the true signal value.                                                                                                               |

| Interface                                | TLCLK4O-<br>TLCLK4O+                                                                    | Y24<br>W24                                             | 0   | LVDS | Parallel Line<br>Transmit Clock<br>Out | This output is the looped version of the reference clock input TLCLK4+/ The nominal frequency is 622.08 MHz for STS-48c/STM-16 AU-4-16c operation. TLCLK4O+ is the true signal value.                                                                                                                                    |

| sical                                    | CMUREFCLK-<br>CMUREFCLK+                                                                | N23<br>M23                                             | Ι   | PECL | CMU Reference<br>Clock                 | This input is the reference clock used for the clock multiplier unit.                                                                                                                                                                                                                                                    |

| Phy                                      | CMUREFDET                                                                               | AC17                                                   | 0   | TTL  | CMU Reference<br>Clock Detect          | This output indicates the presense of clock transistions on CMUREFCLK+/ The signal is active high.                                                                                                                                                                                                                       |

|                                          | CMULOCKDET                                                                              | AC16                                                   | 0   | TTL  | CMU Lock Detect                        | This output indicatest the lock status of the PLL within the CMU with respect to CMUREFCLK+/ The signal is active high.                                                                                                                                                                                                  |

|                                          | CMUREFSEL1<br>CMUREFSEL0                                                                | AB16<br>AA16                                           | I   | TTL  | CMU Reference<br>Clock Select          | These inputs select which frequency is to be expected on CMUREFCLK+/ The binary combination of the two pins are described below (CMUREFSEL0 noted first).  00 78 MHz 01 155 MHz 10 311 MHz                                                                                                                               |

|                                          | CMUFILTER-<br>CMUFILTER+                                                                | L22<br>L21                                             | I   | N/A  | CMU Loop Filter                        | These inputs are brought off-chip to connect to a capacitor which completes the CMU loop filter. CMUFILTER+ should be connected to one side of a 0.1uF capacitor while CMUFILTER-should be connected to the other side of the capacitor.                                                                                 |

Page 20 1.0 Product Description

Table 1.1 Hardware Signal Definitions (3 of 12)

|                                          | Pin Label                  | Pad        | I/O | Туре | Signal Name                        | Description                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------|----------------------------|------------|-----|------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | CLKRSTEN                   | AC12       | I   | TTL  | Clock Reset<br>Enable              | Asserting CLKRSTEN halts all primary clock outputs (TXRCLK, RXRCLK, RSPCLK1, RSPCLK2, RTOHCLK, TSPCLK1, TSPCLK2, and TTOHCLK) during master reset. If deasserted, all primary clock outputs run normally during master reset.                                                                                                                     |

|                                          | LOOPTIMING                 | AD18       | I   | TTL  | Looptime Enable                    | This input enables looptiming which forces the CMU and subsequent Tx clocks to be referenced to the recovered line clock. This signal is active high although the associated register can override the pin.                                                                                                                                       |

| Physical Interface (PHY) Signals (cont.) | LOPC                       | AC13       | I   | TTL  | Loss of Optical<br>Carrier         | This input is used to monitor the optical carrier signal status, and detected changes which can be used to generate interrupts. This enables the optical signal to be monitored via the device CPU interface. When LOPC is asserted, the receive processor is optionally clocked by the transmit clock (derived from TLCLK4+/- or the CMU clock). |

| се (РНУ)                                 | PHY4BITSEL                 | AB14       | I   | TTL  | 4-Bit Physical<br>Interface Select | This input selects the 4 bit interface and disables the CRU and CMU. This input is active high.                                                                                                                                                                                                                                                   |

| cal Interfa                              | TLSYNCLVDS-<br>TLSYNCLVDS+ | T22<br>T21 | I   | LVDS | Transmit<br>Synchronization        | This is the LVDS input for the synchronous reset signal for the line-side transmit processor. (NOTE: TLSYNCLVDS/TLSYNCTTL is intended for use in STS-192/STM-64 applications only.)                                                                                                                                                               |

| Physi                                    | TLSYNCTTL                  | AB23       | I   | TTL  | Transmit<br>Synchronization        | This is the TTL input for the synchronous reset signal for the line-side transmit processor. (NOTE: TLSYNCLVDS/TLSYNCTTL is intended for use in STS-192/STM-64 applications only.)                                                                                                                                                                |

|                                          | RXRCLK                     | AD12       | 0   | TTL  | Receive<br>Reference Clock         | This reference clock output is derived from the serial or parallel receive line clock and can be programmed to operate at 78MHz, 38MHz, 19MHz, or 8kHz frequencies.                                                                                                                                                                               |

|                                          | TXRCLK                     | B21        | 0   | TTL  | Line Transmit<br>Reference Clock   | This reference clock output is derived from the serial or parallel transmit line clock and can be programmed to operate at 78MHz, 38MHz, 19MHz, or 8kHz frequencies.                                                                                                                                                                              |

Table 1.1 Hardware Signal Definitions (4 of 12)

|                              |                                 |          | 9   |      | 1110113 (1 01 1         |                                                                 |

|------------------------------|---------------------------------|----------|-----|------|-------------------------|-----------------------------------------------------------------|

|                              | Pin Label                       | Pad      | I/O | Туре | Signal Name             | Description                                                     |

|                              | TDAT/TUDATA[0]                  | J3       | - 1 | TTL  | Transmit Packet         | POS Mode: This 32-bit data bus is used to drive four-octet true |

|                              | TDAT/TUDATA[1]                  | J4       |     |      | Data Bus                | data from the Packet to PHY layer. TDAT[31] is the MSB.         |

|                              | TDAT/TUDATA[2]                  | H3       |     |      | (TDAT <i>x</i> )        | Packets are aligned to the 32-bit TDAT x boundary.              |

|                              | TDAT/TUDATA[3]                  | G1       |     |      | or                      | ATM Mode: This 32-bit data bus is used to drive four-octet true |

|                              | TDAT/TUDATA[4]                  | G2       |     |      | UTOPIA<br>Transmit Cell | data from the ATM to PHY layer. TUDATA[31] is the MSB.          |

|                              | TDAT/TUDATA[5]                  | G3       |     |      | Data Bus                |                                                                 |

|                              | TDAT/TUDATA[6]                  | F1       |     |      | (TUDATAx)               |                                                                 |

|                              | TDAT/TUDATA[7]                  | F2       |     |      | (TODATAX)               |                                                                 |

| SE                           | TDAT/TUDATA[8]                  | F3       |     |      |                         |                                                                 |

| l g                          | TDAT/TUDATA[9]                  | E2       |     |      |                         |                                                                 |

| Signals                      | TDAT/TUDATA[10]                 | E3       |     |      |                         |                                                                 |

| ≒                            | TDAT/TUDATA[11]                 | F4       |     |      |                         |                                                                 |

| ısı                          | TDAT/TUDATA[12]                 | D1       |     |      |                         |                                                                 |

| - Ze                         | TDAT/TUDATA[13]                 | D2       |     |      |                         |                                                                 |

|                              | TDAT/TUDATA[14]                 | D3       |     |      |                         |                                                                 |

| '\                           | TDAT/TUDATA[15]                 | E4       |     |      |                         |                                                                 |

| ∃                            | TDAT/TUDATA[16]                 | C1       |     |      |                         |                                                                 |

| ᆸ                            | TDAT/TUDATA[17]                 | C2       |     |      |                         |                                                                 |

| <u>9</u>                     | TDAT/TUDATA[18]                 | D5       |     |      |                         |                                                                 |

| Si                           | TDAT/TUDATA[19]                 | B3       |     |      |                         |                                                                 |

| Drop Side (PIF/UIF) Transmit | TDAT/TUDATA[20]                 | A3       |     |      |                         |                                                                 |

| ă                            | TDAT/TUDATA[21]                 | C4       |     |      |                         |                                                                 |

|                              | TDAT/TUDATA[22]                 | B4       |     |      |                         |                                                                 |

|                              | TDAT/TUDATA[23]                 | D6       |     |      |                         |                                                                 |

|                              | TDAT/TUDATA[24]                 | C5       |     |      |                         |                                                                 |

|                              | TDAT/TUDATA[25]                 | A4       |     |      |                         |                                                                 |

|                              | TDAT/TUDATA[26]                 | C6       |     |      |                         |                                                                 |

|                              | TDAT/TUDATA[27]                 | B5<br>B6 |     |      |                         |                                                                 |

|                              | TDAT/TUDATA[28]                 | В6<br>С7 |     |      |                         |                                                                 |

|                              | TDAT/TUDATA[29] TDAT/TUDATA[30] | C7<br>A6 |     |      |                         |                                                                 |

|                              | TDAT/TUDATA[30] TDAT/TUDATA[31] | A6<br>D9 |     |      |                         |                                                                 |

|                              | TUAT/TUUATA[31]                 | DA       |     |      |                         |                                                                 |

Page 22 1.0 Product Description

Table 1.1 Hardware Signal Definitions (5 of 12)

|                                              | Pin Label                                            | Pad      | I/O | Туре | Signal Name                                                             | Description                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------|------------------------------------------------------|----------|-----|------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                              | POS Mode: TPRTY ATM Mode: TUPRTY                     | C8       | I   | TTL  | Transmit Bus<br>Parity                                                  | POS Mode: TRPRTY is the odd/even (programmable, default odd) parity bit over TDAT[310]. The signal is only valid when asserted simultaneously with TENB.  ATM Mode: TUPRTY is the odd/even (programmable, default                                                                                                       |

|                                              |                                                      |          |     |      |                                                                         | odd) parity bit over TUDATA[31.0], driven by the ATM layer. The signal is valid when asserted simultaneously with TUENB*.                                                                                                                                                                                               |

|                                              | POS Mode:<br>TMOD[1]<br>TMOD[0]                      | A7<br>B7 | _   | TTL  | Transmit Word<br>Modulo                                                 | POS Mode only: These inputs are used to qualify TDATx data octets. The state of TMOD[1,0] defines which of the four TDAT octets contain valid data when both TEOP and TENB are asserted. Non-EOP words always contain four valid TDAT octets.                                                                           |

| t.)                                          | POS Mode:<br>TSOP<br>ATM Mode:<br>TUSOC              | С9       | I   | TTL  | Transmit Start of Packet or UTOPIA Transmit Start of                    | <b>POS Mode:</b> TSOP is asserted (active high) by the Packet layer to indicate that TDAT <i>x</i> contains the first valid octet of a new packet. The signal is valid when asserted simultaneously with TENB. The packet interface can be operated without using this signal.                                          |

| nals (cont                                   |                                                      |          |     |      | Cell                                                                    | <b>ATM Mode:</b> TUSOC is asserted (active high) by the ATM layer to indicate that TUDATAx contains the first valid octet of the cell. The signal is only valid when asserted simultaneously with TUENB*.                                                                                                               |

| smit Sig                                     | POS Mode:<br>TEOP                                    | D10      | I   | TTL  | Transmit End of<br>Packet                                               | <b>POS Mode only:</b> TEOP is asserted (active high) by the Packet layer to indicate that TDAT <i>x</i> contains the last valid octet of the packet. Only valid when asserted simultaneously with TENB.                                                                                                                 |

| Drop Side (PIF/UIF) Transmit Signals (cont.) | POS Mode:<br>DTPA<br>ATM Mode:<br>TUFULL*/<br>TUCLAV | А9       | 0   | TTL  | Transmit Polled-<br>PHY Packet<br>Available<br>or<br>Transmit Full/Cell | POS Mode: DTPA transitions high when a programmable minimum number of octets are available in the Tx FIFO. Once high, the DTPA indicates that the Tx FIFO is not full. When DTPA transitions low, it optionally indicates that the Tx FIFO is full or near full.                                                        |

| Drop Side (                                  |                                                      |          |     |      | Available                                                               | ATM Mode: TUFULL*/TUCLAV is indicates "Full" or "Cell Available" status of UTOPIA transmit interface for flow control. TUFULL* is for word-level flow control; TUCLAV is for cell-level flow control. Polarity is selectable via an internal register bit (i.e., TUFULL* active low/TUCLAV active high, or vice versa). |

|                                              | <i>POS Mode:</i><br>TERR                             | В9       | -   | TTL  | Transmit Error<br>Indicator                                             | POS Mode only: An active TERR flag can be used to force HDLC frame abortion, or insertion of FCS error in the transmitted HDLC/PPP frames. The TERR value is only valid for TEOP-marked words, and is ignored for all other word writes.                                                                                |

|                                              | POS Mode:<br>TENB                                    | C10      | _   | TTL  | Transmit Write<br>Enable                                                | <b>POS Mode:</b> TENB is used by the Packet layer to indicate cycles when TDAT <i>x</i> contains valid packet data (active low).                                                                                                                                                                                        |

|                                              | ATM Mode:<br>TUENB*                                  |          |     |      |                                                                         | ATM Mode: TUENB* is used by the ATM layer to indicate cycles when TUDATAx contains valid cell data (active low).                                                                                                                                                                                                        |

|                                              | POS Mode:<br>TFCLK                                   | A10      | I   | TTL  | Transmit Write<br>Clock                                                 | <b>POS Mode:</b> TFCLK is a reference clock provided by the Packet layer to the PHY layer to synchronize transfers on TDATx.                                                                                                                                                                                            |

|                                              | <i>ATM Mode:</i><br>TUCLK                            |          |     |      |                                                                         | ATM Mode: TUCLK is a reference clock provided by the ATM layer to the PHY layer to synchronize transfers on TUDATAx.                                                                                                                                                                                                    |

|                                              | POS Mode:<br>TFCLKO                                  | B10      | 0   | TTL  | Transmit Write<br>Clock Looped                                          | POS Mode: TFCLKO is the TFCLK transfer synchronization reference clock from the Packet layer looped out.                                                                                                                                                                                                                |

|                                              | <i>ATM Mode:</i><br>TUCLKO                           |          |     |      |                                                                         | ATM Mode: TUCLKO is the TUCLK transfer synchronization reference clock from the ATM layer looped out.                                                                                                                                                                                                                   |

Table 1.1 Hardware Signal Definitions (6 of 12)

|                                     | Pin Label                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pad                                                                                          | 1/0 | Туре | Signal Name                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Drop Side (PIF/UIF) Receive Signals | RDAT/RUDATA[0] RDAT/RUDATA[1] RDAT/RUDATA[1] RDAT/RUDATA[2] RDAT/RUDATA[3] RDAT/RUDATA[4] RDAT/RUDATA[5] RDAT/RUDATA[6] RDAT/RUDATA[6] RDAT/RUDATA[8] RDAT/RUDATA[10] RDAT/RUDATA[10] RDAT/RUDATA[11] RDAT/RUDATA[11] RDAT/RUDATA[12] RDAT/RUDATA[14] RDAT/RUDATA[15] RDAT/RUDATA[16] RDAT/RUDATA[17] RDAT/RUDATA[17] RDAT/RUDATA[18] RDAT/RUDATA[18] RDAT/RUDATA[19] RDAT/RUDATA[20] RDAT/RUDATA[21] RDAT/RUDATA[22] RDAT/RUDATA[23] RDAT/RUDATA[24] RDAT/RUDATA[25] RDAT/RUDATA[26] RDAT/RUDATA[27] RDAT/RUDATA[28] RDAT/RUDATA[29] RDAT/RUDATA[30] | W1 V3 V2 V1 U3 U2 T4 T3 T2 T1 R4 R3 R2 R1 P3 P2 N1 N4 N3 N2 M3 M4 M2 M1 L2 L3 K1 K2 K3 K4 J1 | 0   |      | Recevie Packet Data Bus (RDAT x) or Receive Cell Data Bus (RUDATAx) | POS Mode: This 32-bit data bus is used to drive four-octet true data from the PHY to Packet layer. RDAT[31] is the MSB. Packets are aligned to the 32-bit RDAT x boundary.  ATM Mode: This 32-bit data bus is used to drive four-octet true data from the PHY to ATM layer. RUDATA[31] is the MSB.                                                                                             |

|                                     | RDAT/RUDATA[31]  POS Mode:  RPRTY  ATM Mode:  RUPRTY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Y3                                                                                           | 0   | TTL  | Receive Bus<br>Parity                                               | POS Mode: RPRTY is the odd/even (programmable, default odd) parity bit over RDAT[310].  ATM Mode: RUPRTY is the odd/even (programmable, default odd) parity bit over RUDATA[310].                                                                                                                                                                                                              |

|                                     | POS Mode:<br>RMOD[1]<br>RMOD[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | W2<br>W3                                                                                     | 0   | TTL  | Receive Word<br>Modulo                                              | POS Mode only: These outputs are used to qualify RDATx data octets. The state of RMOD[1,0] defines which of the four RDAT octets contain valid data when REOP is asserted. Non-EOP words always contain four valid RDAT octets.                                                                                                                                                                |

|                                     | POS Mode:<br>RSOP<br>ATM Mode:<br>RUSOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AA1                                                                                          | 0   | TTL  | Receive Start of<br>Packet<br>or<br>UTOPIA Receive<br>Start of Cell | POS Mode: RSOP is asserted (active high) by the Packet layer to indicate that RDATx contains the first valid octet of a new packet. The packet interface can be operated without using this signal.  ATM Mode: RUSOC is asserted (active high) by the ATM layer to indicate that RUDATAx contains the first valid octet of a cell. This signal is used to support multiple PHY configurations. |

Page 24 1.0 Product Description

Table 1.1 Hardware Signal Definitions (7 of 12)

|                                             | Pin Label                                             | Pad  | I/O | Туре | Signal Name                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------|-------------------------------------------------------|------|-----|------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | POS Mode:<br>REOP                                     | AB2  | 0   | TTL  | Receive End of<br>Packet                                       | <b>POS Mode only:</b> REOP is asserted (active high) to indicate that RDAT <i>x</i> contains the last valid octet of the packet.                                                                                                                                                                                                                                                                                                             |

| nt.)                                        | POS Mode:<br>RVAL<br>ATM Mode:<br>RUEMPTY*/<br>RUCLAV | AA2  | 0   | TTL  | Receive Data Valid<br>or<br>Receive<br>Empty/Cell<br>Available | POS Mode: RVAL asserted (active high) indicates that the recevie data signals (RDATx, RSOP, REOP, RMOD, RPRTY, and RERR) are valid. When RAL is low, all receive signals are invalid and must be disregarded. RVAL transitions low when the Rx FIFO is empty or the end of a packet is reached, and data will not be removed from the Rx FIFO while RVAL is low. Once deasserted, RVAL remains so until the current PHY has been deselected. |

| Drop Side (PIF/UIF) Receive Signals (cont.) |                                                       |      |     |      |                                                                | ATM Mode: RUEMPTY*/RUCLAV indicates "Empty" or "Cell Available" status of the UTOPIA receive interface for flow control. RUEMPTY* is for word-level flow control; RUCLAV is for cell-level flow control. Polarity is selectable via an internal register bit (i.e., RUCLAV active high/RUEMPTY* active low, or vice versa).                                                                                                                  |

| ) Receiv                                    | POS Mode:<br>RERR                                     | W4   | 0   | TTL  | Receive Error<br>Indicator                                     | POS Mode only: An asserted RERR flag (active high) indicates that the packet contained an error (i.e., abort/FCS error). The RERR flag is only asserted during EOP-marked words.                                                                                                                                                                                                                                                             |

| (PIF/UIF                                    | POS Mode:<br>RENB<br>ATM Mode:                        | AA3  | I   | TTL  | Receive Read<br>Enable                                         | <b>POS Mode:</b> RENB is used by the Packet layer to indicate that the RVAL, RSOP, RPRTY, RDATx, RMODx, REOP, and RERR signals will be sampled at the end of the nest cycle (active low).                                                                                                                                                                                                                                                    |

| Jrop Side                                   | RUENB*                                                |      |     |      |                                                                | ATM Mode: RUENB* is used by the ATM layer to indicate that RUDATA, RUSOC, and RPRTY will be sampled at the end of the nest cycle (active low).                                                                                                                                                                                                                                                                                               |

|                                             | POS Mode:<br>RFCLK                                    | Y4   | I   | TTL  | Receive FIFO<br>Write Clock                                    | <b>POS Mode:</b> RFCLK is a reference clock provided by the Packet layer to the PHY layer to synchronize transfers on RDATx.                                                                                                                                                                                                                                                                                                                 |

|                                             | <i>ATM Mode:</i><br>RUCLK                             |      |     |      | Receive Write<br>Clock                                         | ATM Mode: RUCLK is a reference clock provided by the ATM layer to the PHY layer to synchronize transfers on RUDATAx.                                                                                                                                                                                                                                                                                                                         |

|                                             | POS Mode:<br>RFCLKO                                   | AA4  | 0   | TTL  | Receive FIFO<br>Write Clock<br>Looped                          | POS Mode: RFCLKO is the RFCLK transfer synchronization reference clock looped out.                                                                                                                                                                                                                                                                                                                                                           |

|                                             | ATM Mode:<br>RUCLKO                                   |      |     |      | or  Receive Write Clock Looped                                 | ATM Mode: RUCLKO is the RUCLK transfer synchronization reference clock looped out.                                                                                                                                                                                                                                                                                                                                                           |

| Time Stamp Signals                          | TXTS                                                  | AA6  | 0   | TTL  | Transmit Time<br>Stamp                                         | TXTS is an active high pulse generated when a cell/packet exits the TPP block. The difference in time between a TXTS pulse and a TSOP/TUSOC pulse can be used to determine transmit FIFO latency.                                                                                                                                                                                                                                            |

| Time Stan                                   | RXTS                                                  | AC3  | 0   | TTL  | Receive Time<br>Stamp                                          | RXTS is an active high pulse generated when a new cell/packet arrives in the RPP block. The difference in time between an RXTS pulse and an RSOP/RUSOC pulse is used to determine receive FIFO latency.                                                                                                                                                                                                                                      |