# OVERVOLTAGE PROTECTION FOR LUCENT TECHNOLOGIES LCAS

Symmetrical and Asymmetrical Characteristics for Optimum Protection of Lucent L7581/2/3 LCAS

| TERMINAL           | $V_{DRM}$  | V <sub>(BO)</sub> |  |  |

|--------------------|------------|-------------------|--|--|

| PAIR               | V          | V                 |  |  |

| T-G (SYMMETRICAL)  | ±105       | ±130              |  |  |

| R-G (ASYMMETRICAL) | +105, -180 | +130, -220        |  |  |

**CUSTOMISED VERSIONS AVAILABLE**

###

D PACKAGE (TOP VIEW)

NC - No internal connection

# Rated for International Surge Wave Shapes

| WAVE SHAPE | STANDARD     | I <sub>TSP</sub><br>A |

|------------|--------------|-----------------------|

| 2/10 μs    | GR-1089-CORE | 175                   |

| 8/20 µs    | ANSI C62.41  | 120                   |

| 10/160 µs  | FCC Part 68  | 60                    |

| 10/700 μs  | ITU-T K20/21 | 50                    |

| 10/560 μs  | FCC Part 68  | 45                    |

| 10/1000 µs | GR-1089-CORE | 35                    |

- Ion-Implanted Breakdown Region Precise And Stable Voltage Low Voltage Overshoot Under Surge

- Planar Passivated Junctions

Low Off-State Current < ±10 μA</li>

- Small Outline Surface Mount Package

Available Ordering Options

| CARRIER          | ORDER #       |

|------------------|---------------|

| Tube             | TISPL758LF3D  |

| Taped and reeled | TISPL758LF3DR |

# description

The TISPL758LF3 is an integrated combination of a symmetrical bidirectional overvoltage protector and an asymmetrical bidirectional overvoltage protector. It is designed to limit the peak voltages on the line terminals of the Lucent Technologies L7581/2/3 LCAS (Line Card Access Switches). An LCAS may also be referred to as a Solid State Relay, SSR, i.e. a replacement of the conventional electromechanical relay.

The TISPL758LF3D voltages are chosen to give adequate LCAS protection for all switch conditions. The most potentially stressful

# device symbol

Terminals T, R and G correspond to the alternative line designators of A, B and C

condition is low level power cross when the LCAS switches are closed. Under this condition, the TISPL758LF3D limits the voltage and corresponding LCAS dissipation until the LCAS thermal trip operates and opens the switches.

Under open-circuit ringing conditions, the line ring (R) conductor will have high peak voltages. For battery backed ringing, the ring conductor will have a larger peak negative voltage than positive i.e. the peak voltages are asymmetric. An overvoltage protector with a similar voltage asymmetry will give the most effective protection. On a connected line, the tip (T) conductor will have much smaller voltage levels than the opencircuit ring conductor values. Here a symmetrical voltage protector gives adequate protection.

Overvoltages are normally caused by a.c. power system or lightning flash disturbances which are induced or conducted on to the telephone line. These overvoltages are initially clipped by protector breakdown clamping until the voltage rises to the breakover level, which causes the

Support from the Microelectronics Group of Lucent Technologies Inc. is gratefully acknowledged in the definition of the TISPL758LF3D voltage levels and for performing TISPL758LF3D evaluations.

# PRODUCT INFORMATION

# TISPL758LF3D

# INTEGRATED SYMMETRICAL AND ASYMMETRICAL BIDIRECTIONAL OVERVOLTAGE PROTECTORS FOR LUCENT TECHNOLOGIES L7581/2/3 LINE CARD ACCESS SWITCHES

JANUARY 1998 - REVISED OCTOBER 1998

device to crowbar into a low-voltage on state. This low-voltage on state causes the current resulting from the overvoltage to be safely diverted through the device. For negative surges, the high crowbar holding current prevents d.c. latchup with the SLIC current, as the surge current subsides. The TISPL758LF3 is guaranteed to voltage limit and withstand the listed international lightning surges in both polarities.

These protection devices are supplied in a small-outline surface mount (D) plastic package. The difference between the TISPL758LF3D and TISPL758LF3DR versions is shown in the ordering information.

# absolute maximum ratings, T<sub>A</sub> = 25°C (unless otherwise noted)

| RATING                                                                             |               | SYMBOL              | VALUE       | UNIT |

|------------------------------------------------------------------------------------|---------------|---------------------|-------------|------|

| Repetitive peak off-state voltage R-G termina                                      |               | V                   | -180, +105  | V    |

|                                                                                    | T-G terminals | $V_{DRM}$           | -105, +105  | V    |

| Non-repetitive peak on-state pulse current (see Notes 1, 2 and 3)                  |               |                     |             |      |

| 2/10 µs (GR-1089-CORE, 2/10 µs voltage wave shape)                                 |               |                     | 175         |      |

| 8/20 μs (ANSI C62.41, 1.2/50 μs voltage wave shape)                                |               |                     | 120         |      |

| 10/160 μs (FCC Part 68, 10/160 μs voltage wave shape)                              |               |                     | 60          |      |

| 5/200 µs (VDE 0433, 2.0 kV, 10/700 µs voltage wave shape)                          |               |                     | 50          | ٨    |

| 0.2/310 μs (I3124, 2.0 kV, 0.5/700 μs voltage wave shape)                          |               | I <sub>TSP</sub>    | 50          | Α    |

| 5/310 µs (ITU-T K20/21, 2.0 kV, 10/700 µs voltage wave shape)                      |               |                     | 50          |      |

| 5/310 µs (FTZ R12, 2.0 kV, 10/700 µs voltage wave shape)                           |               |                     | 50          |      |

| 10/560 µs (FCC Part 68, 10/560 µs voltage wave shape)                              |               |                     | 45          |      |

| 10/1000 μs (GR-1089-CORE, 10/1000 μs voltage wave shape)                           |               |                     | 35          |      |

| Non-repetitive peak on-state current (see Notes 1, 2 and 3)                        |               |                     |             |      |

| full sine wave                                                                     | 50 Hz         |                     | 16          | ۸    |

|                                                                                    | 60 Hz         | I <sub>TSM</sub>    | 20          | Α    |

| Repetitive peak on-state current, 50/60 Hz, (see Notes 2 and 3)                    |               | I <sub>TSM</sub>    | 2x1         | Α    |

| Initial rate of rise of on-state current, Exponential current ramp, Maximum ramp v | alue < 70 A   | di <sub>T</sub> /dt | 150         | A/µs |

| Junction temperature                                                               |               | $T_J$               | -40 to +150 | °C   |

| Storage temperature range                                                          |               | T <sub>stg</sub>    | -40 to +150 | °C   |

NOTES: 1. Above the maximum specified temperature, derate linearly to zero at 150°C lead temperature.

- 2. Initially the TISPL758LF3 must be in thermal equilibrium with  $0^{\circ}$ C <  $T_J$  < $70^{\circ}$ C.

- 3. The surge may be repeated after the TISPL758LF3 returns to its initial conditions.

# recommended operating conditions

|    |                                  |                                             | MIN | TYP | MAX | UNIT |

|----|----------------------------------|---------------------------------------------|-----|-----|-----|------|

| R1 | Series Resistor for GR-1089-CORE | first-level surge, operational pass (4.5.7) | 20  |     |     | Ω    |

|    | Series Resistor for FCC Part 68  | 10/160 non-operational pass                 | 0   |     |     |      |

| R1 |                                  | 10/160 operational pass                     | 18  |     |     | Ω    |

| KI |                                  | 10/560 non-operational pass                 | 0   |     |     | 22   |

|    |                                  | 10/560 operational pass                     | 10  |     |     |      |

| R1 | Series Resistor for ITU-T K20/21 | 10/700, < 2 kV, operational pass            | 0   |     |     | Ω    |

| KI |                                  | 10/700, 4 kV, operational pass              | 40  |     |     | 52   |

# TISPL758LF3D INTEGRATED SYMMETRICAL AND ASYMMETRICAL BIDIRECTIONAL OVERVOLTAGE PROTECTORS FOR LUCENT TECHNOLOGIES L7581/2/3 LINE CARD ACCESS SWITCHES

JANUARY 1998 - REVISED OCTOBER 1998

# electrical characteristics for the T-G and R-G terminal pairs, $T_J = 25$ °C (unless otherwise noted)

|                   | PARAMETER TEST CONDITIONS             |                                                                                         | VALUE         |      |     | UNIT |      |

|-------------------|---------------------------------------|-----------------------------------------------------------------------------------------|---------------|------|-----|------|------|

|                   | TANAMETER                             | TEST CONDITIONS                                                                         |               | MIN  | TYP | MAX  | ONII |

| I <sub>DRM</sub>  | Repetitive peak off-<br>state current | $V_D = \pm V_{DRM}$ , (See Note 4)                                                      |               |      |     | ±10  | μA   |

| V                 | Breakover voltage                     | $dv/dt = \pm 250 \text{ V/ms},  R_{SOURCE} = 300 \Omega$                                | R-G terminals | -220 |     | +130 | V    |

| V <sub>(BO)</sub> | breakover voltage                     | uv/ut = ±250 v/iiis, K <sub>SOURCE</sub> = 500 ½                                        | T-G terminals | -130 |     | +130 | v    |

| V                 | Impulse breakover volt-               | Rated impulse conditions with operational pass series                                   | R-G terminals | -240 |     | +140 | V    |

| V <sub>(BO)</sub> | age                                   | resistor                                                                                | T-G terminals | -140 |     | +140 | v    |

|                   | Holding current                       | di/dt = -30 mA/ms                                                                       |               | +100 |     |      | mA   |

| 'н                | riolaling current                     | di/dt = +30  mA/ms                                                                      |               | -150 |     |      | ША   |

| I <sub>D</sub>    | Off-state current                     | $0 < V_D < \pm 50 \text{ V}, T_J = 85^{\circ}\text{C}$                                  |               |      |     | ±10  | μA   |

| C <sub>TG</sub>   | Off-state capacitance                 | $f = 100 \text{ kHz}, V_d = 1 \text{ V rms} V_{TG} = -5 \text{ V}, (See Note 5)$        |               |      | 18  | 36   | pF   |

| C <sub>RG</sub>   | Off-state capacitance                 | $f = 100 \text{ kHz}$ , $V_d = 1 \text{ V rms}$ $V_{TG} = -50 \text{ V}$ , (See Note 5) | )             |      | 10  | 20   | pF   |

NOTES: 4. Positive and negative values of V<sub>DRM</sub> are not equal. See ratings table

# thermal characteristics

|                 | PARAMETER                               |  | TYP | MAX | UNIT |

|-----------------|-----------------------------------------|--|-----|-----|------|

| $R_{\theta JA}$ | Junction to free air thermal resistance |  |     | 160 | °C/W |

<sup>5.</sup> These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The third terminal is connected to the guard terminal of the bridge.

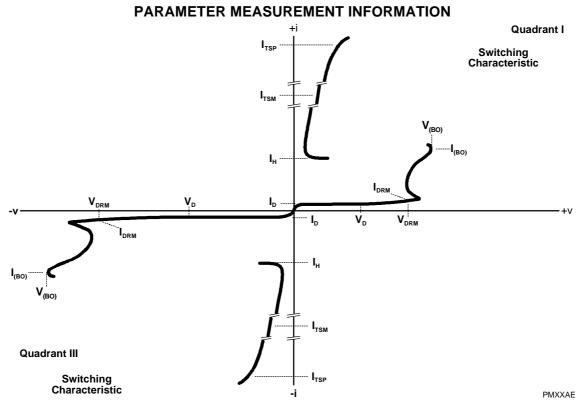

Figure 1. ASYMMETRICAL VOLTAGE-CURRENT CHARACTERISTIC FOR R-G TERMINAL PAIR

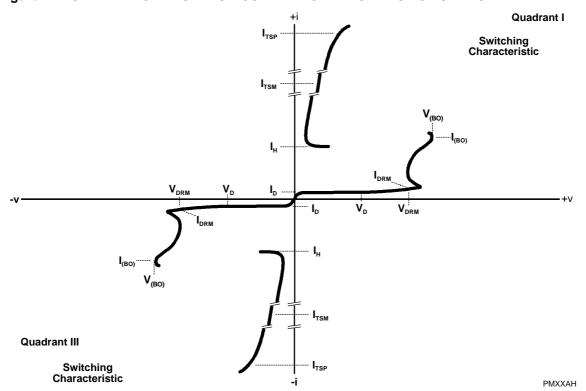

Figure 2. SYMMETRICAL VOLTAGE-CURRENT CHARACTERISTIC FOR T-G TERMINAL PAIR

JANUARY 1998 - REVISED OCTOBER 1998

# **TYPICAL CHARACTERISTICS**

# OFF-STATE CURRENT

JUNCTION TEMPERATURE 100  $V_D = \pm 50 \text{ V}$ 10 I<sub>D</sub> - Off-State Current - μΑ 1 0.1 0.01 0.001 -25 0 25 50 75 100 125 150 T, - Junction Temperature - °C

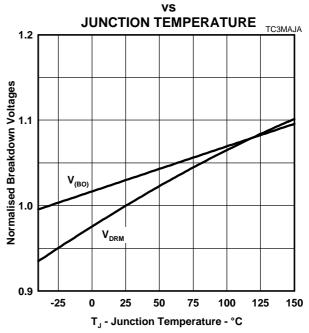

# NORMALISED BREAKOVER VOLTAGE

Figure 3.

# 1.2 1.0 0-001 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0-01 0

# NORMALISED BREAKDOWN VOLTAGES

Figure 4.

# NORMALISED HOLDING CURRENT

JUNCTION TEMPERATURE TC3MAHA 2.0 NORMALISED HOLDING CURRENT 1.5 1.0 0.9 0.8 0.7 0.6 0.5 -25 25 50 75 100 150 125 T<sub>J</sub> - Junction Temperature - °C Figure 6.

Figure 5.

# **APPLICATIONS INFORMATION**

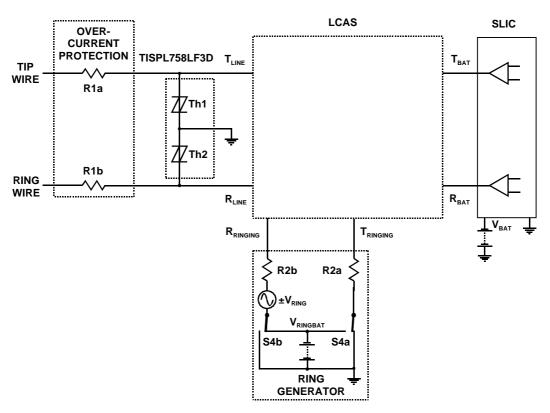

Figure 7. LCAS PROTECTION WITH A TISPL758LF3D

JANUARY 1998 - REVISED OCTOBER 1998

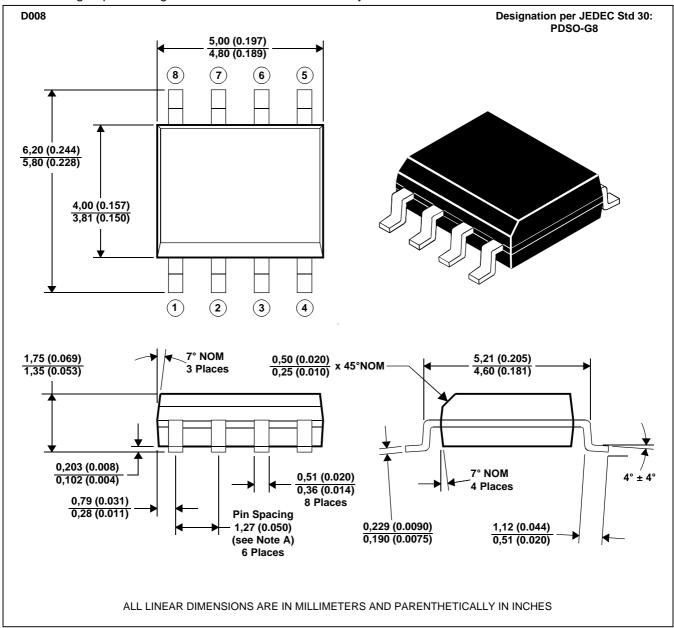

# **MECHANICAL DATA**

# **D008**

# plastic small-outline package

This small-outline package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound will withstand soldering temperature with no deformation, and circuit performance characteristics will remain stable when operated in high humidity conditions. Leads require no additional cleaning or processing when used in soldered assembly.

MDXXAA

NOTES: A. Leads are within 0,25 (0.010) radius of true position at maximum material condition.

- B. Body dimensions do not include mold flash or protrusion.

- C. Mold flash or protrusion shall not exceed 0,15 (0.006).

- D. Lead tips to be planar within  $\pm 0.051$  (0.002).

# TISPL758LF3D INTEGRATED SYMMETRICAL AND ASYMMETRICAL BIDIRECTIONAL OVERVOLTAGE PROTECTORS FOR LUCENT TECHNOLOGIES L7581/2/3 LINE CARD ACCESS SWITCHES

JANUARY 1998 - REVISED OCTOBER 1998

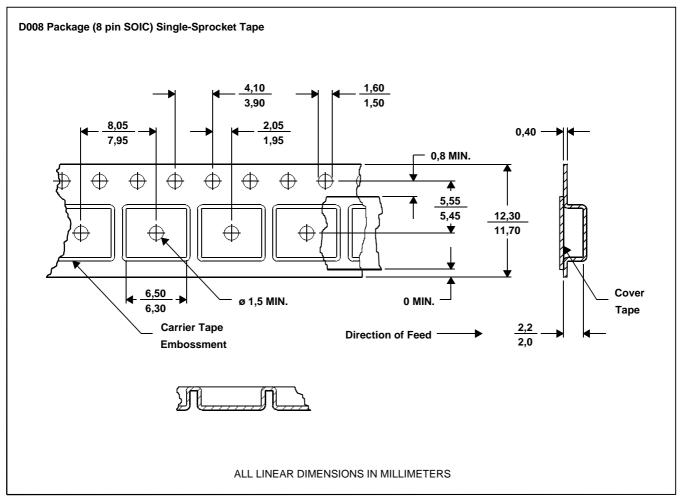

# **MECHANICAL DATA**

# D008

# tape dimensions

NOTES: A. Taped devices are supplied on a reel of the following dimensions:-

MDXXAT

Reel diameter: 330 + 0.0/-4.0 mmReel hub diameter:  $100 \pm 2.0 \text{ mm}$ Reel axial hole:  $13.0 \pm 0.2 \text{ mm}$

B. 2500 devices are on a reel.

# INTEGRATED SYMMETRICAL AND ASYMMETRICAL BIDIRECTIONAL OVERVOLTAGE PROTECTORS FOR LUCENT TECHNOLOGIES L7581/2/3 LINE CARD ACCESS SWITCHES

JANUARY 1998 - REVISED OCTOBER 1998

# IMPORTANT NOTICE

Power Innovations Limited (PI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to verify, before placing orders, that the information being relied on is current.

PI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with PI's standard warranty. Testing and other quality control techniques are utilized to the extent PI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

PI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor is any license, either express or implied, granted under any patent right, copyright, design right, or other intellectual property right of PI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

PI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORISED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS.

Copyright © 1998, Power Innovations Limited