#### **Product Description**

Sirenza Microdevices' **SLD-1000** is a robust 4 Watt high performance LDMOS transistor die, designed for operation from 10 to 2700MHz. It is an excellent solution for applications requiring high linearity and efficiency. The SLD-1000 is typically used as a driver or output stage for power amplifier, or transmitter applications. These robust power transistors are fabricated using Sirenza's high performance XEMOS II<sup>TM</sup> process.

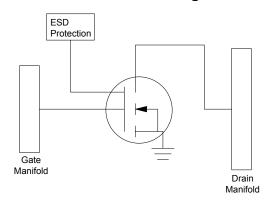

### **Functional Schematic Diagram**

# Source - Backside Contact

# **SLD-1000**

#### 4 Watt Discrete LDMOS FET -Bare Die

#### **Product Features**

- 4 Watt Output P<sub>1dB</sub>

- Single Polarity Operation

- 19dB Gain at 900 MHz

- XeMOS II<sup>TM</sup> LDMOS

- Integrated ESD Protection, Class 1B

- Aluminum Topside Metallization

- Gold Backside Metallization

#### **Applications**

- Base Station PA Driver

- Repeaters

- Military Communications

- RFID

- GSM, CDMA, Edge, WDCDMA

#### **RF Specifications**

| Symbol                                                                                                                                                                   | Parameter                                                     | Unit  | Min | Тур | Max  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------|-----|-----|------|

| Frequency                                                                                                                                                                | Frequency of Operation                                        | MHz   | 10  | -   | 2700 |

| Gain 3.5 Watts CW, 900 MHz                                                                                                                                               |                                                               | dB    | -   | 19  | -    |

| Efficiency                                                                                                                                                               | Drain Efficiency at 3.5 Watts CW, 900 MHz                     | %     | -   | 43  | -    |

| Linearity                                                                                                                                                                | 3 <sup>rd</sup> Order IMD at 3.5 Watts PEP (Two Tone) 900 MHz | dBc   | -   | -30 | -    |

| Lineanty                                                                                                                                                                 | 1dB Compression (P <sub>1dB</sub> ) 900 MHz                   | Watts | -   | 4   | -    |

| R <sub>TH</sub>                                                                                                                                                          | Thermal Resistance (Junction-to-Case, mounted in package)     | °C/W  | -   | 11  | -    |

| Test Conditions: Mounted in ceramic package and tested in Sirenza Evaluation Board V <sub>DS</sub> = 28.0V, I <sub>DQ</sub> = 30mA, T <sub>Mounting Surface</sub> = 25°C |                                                               |       |     |     |      |

#### **DC Specifications**

| Symbol                    | Parameter                                                                      | Unit   | Min | Typical | Max |

|---------------------------|--------------------------------------------------------------------------------|--------|-----|---------|-----|

| 9 <sub>m</sub>            | Forward Transconductance @ 30mA I <sub>DS</sub>                                | mA / V |     | 150     |     |

| V <sub>GS</sub> Threshold | I <sub>DS</sub> =3mA                                                           | Volts  | 3.0 | 4.2     | 5.0 |

| V <sub>DS</sub> Breakdown | 1mA I <sub>DS</sub> Current                                                    | Volts  | 65  | 70      |     |

| C <sub>iss</sub>          | Input Capacitance (Gate to Source) V <sub>GS</sub> =0V, V <sub>DS</sub> =28V   | pF     |     | 5.2     |     |

| C <sub>rss</sub>          | Reverse Capacitance (Gate to Drain) V <sub>GS</sub> =0V, V <sub>DS</sub> =28V  | pF     |     | 0.2     |     |

| C <sub>oss</sub>          | Output Capacitance (Drain to Source) V <sub>GS</sub> =0V, V <sub>DS</sub> =28V | pF     |     | 3.2     |     |

| R <sub>DSon</sub>         | Drain to Source Resistance, V <sub>GS</sub> =10V V <sub>DS</sub> =250mV        | Ω      |     | 3.0     | 3.5 |

#### SLD-1000 10-2700 MHz 4 Watt LDMOS FET - Bare Die

### **Quality Specifications**

| Parameter  | Description      | Unit  | Typical               |

|------------|------------------|-------|-----------------------|

| ESD Rating | Human Body Model | Volts | 750                   |

| MTTF       | 200°C Channel    | Hours | 1.2 X 10 <sup>6</sup> |

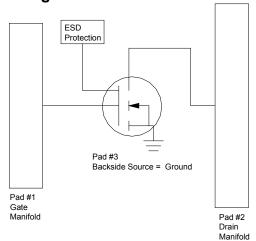

#### **Contact Description**

| Pad # | Function | Description                                                                                                                                               |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Gate     | Aluminum metallized manifold MOSFET Gate with ESD protection structure. (Topside contact)                                                                 |

| 2     | Drain    | Aluminum metallized manifold MOSFET Drain. (Topside contact)                                                                                              |

| 3     | Source   | Chrome Gold metallized MOSFET Source contact. Appropriate electrical, mechanical and thermal connection required for proper operation. (Backside contact) |

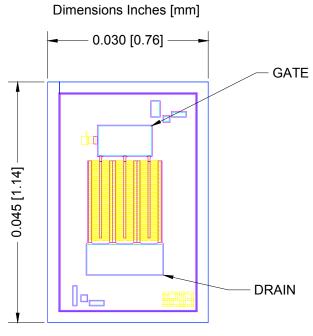

#### **Pad Diagram**

#### **Absolute Maximum Ratings**

| •                                                      |             |       |

|--------------------------------------------------------|-------------|-------|

| Parameters                                             | Value       | Unit  |

| Drain Voltage (V <sub>DS</sub> )                       | 35          | Volts |

| Gate Voltage (V <sub>GS</sub> ), V <sub>DS</sub> =0    | 20          | Volts |

| RF Input Power                                         | +30         | dBm   |

| Load Impedance for Continuous Operation Without Damage | 10:1        | VSWR  |

| Output Device Channel Temperature                      | +200        | °C    |

| Storage Temperature Range                              | -40 to +150 | °C    |

Operation of this device beyond any one of these limits may cause permanent damage. For reliable continuous operation see typical setup values specified in the table on page one.

#### Note 1

Gate voltage must be applied to to the device concurrently or after application of drain voltage to prevent potentially destructive oscillations. Bias voltages should never be applied to the transistor unless it is properly terminated on both input and output.

#### Note 2:

The required  $V_{GS}$  corresponding to a specific  $I_{DQ}$  will vary from device to device due to the normal die-to-die variation in threshold voltage with LDMOS transistors.

#### Note 3:

The threshold voltage ( $V_{GSTH}$ ) of LDMOS transistors varies with device temperature. External temperature compensation may be required. See Sirenza application notes AN-067 LDMOS Bias Temperature Compensation.

**Caution: ESD Sensitive**

Appropriate precaution in handling, packaging and testing devices must be observed.

Phone: (800) SMI-MMIC

### SLD-1000 10-2700 MHz 4 Watt LDMOS FET - Bare Die

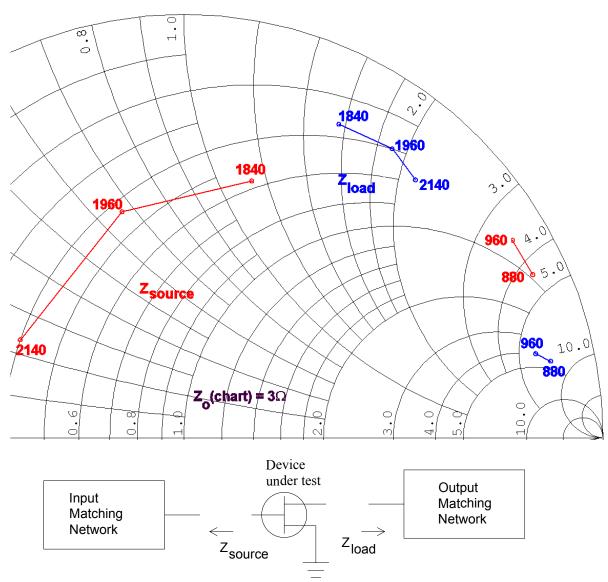

#### **Impedance Data**

| Frequency (MHz) | Z <sub>source</sub> | $Z_{load}$    |

|-----------------|---------------------|---------------|

| 880             | 2.7 + j 13.1        | 12.5 + j 22.5 |

| 960             | 1.9 + j 10.6        | 11.8 + j 18.3 |

| 1840            | 1.7 + j 3.4         | 1.0 + j 4.7   |

| 1960            | 1.3 + j 2.0         | 1.2 + j 5.7   |

| 2140            | 1.2 + j 0.7         | 1.7 + j 6.4   |

Impedances Referenced to Wirebond/PCB Interface.

## **De-embedding Information**

| Description          | Gate  | Drain |

|----------------------|-------|-------|

| Number of Bond Wires | 2     | 3     |

| Length of Bond Wires | 0.040 | 0.040 |

| Height of Bond Wires | 0.006 | 0.006 |

| Pitch of Bond Wires  | 0.005 | 0.005 |

| Bond Wire Diameter   | 0.002 | 0.002 |

All Dimensions in Inches.

Wirebond Heights Referenced to Top Surface of Die.

$Z_{source}$  and  $Z_{load}$  are the optimal impedances presented to the SLD-1000 when operating at 28V, Idq=30mA, Pout=3.5 W PEP.

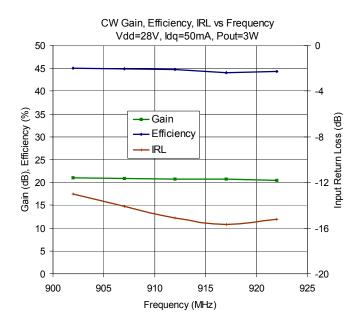

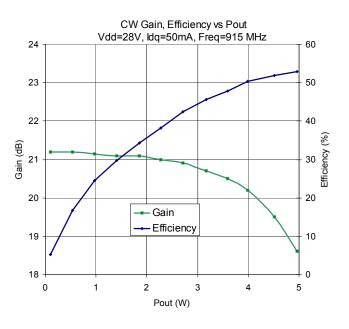

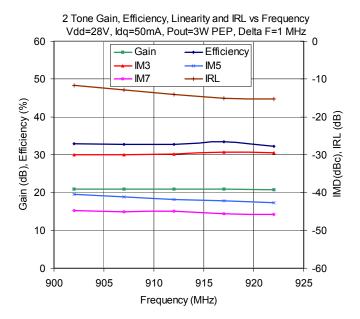

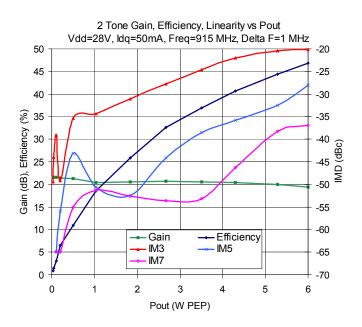

# Typical Performance Curves for packaged die tested in SLD-1083CZ 900 MHz Application Circuit

### Die Map

SOURCE - BACKSIDE CONTACT - NOT SHOWN DIE THICKNESS - 0.004 [0.10]

AuSi, AuSn, or AuGe eutectic die attach is recommended. AlSi bond wires are recommended.

#### **Part Number Ordering Information**

| Part Number | Gel Pack          |

|-------------|-------------------|

| SLD-1000    | 100 pcs. per pack |

Die are screened prior to dicing to DC parameters and are shipped per Sirenza application note AN-039 Visual Criteria of Unpackaged Die.