# Low Voltage Synchronous Buck Controller

The NCP1586 is a low cost PWM controller designed to operate from a 5 V or 12 V supply. This device is capable of producing an output voltage as low as 0.8 V. This 8–pin device provides an optimal level of integration to reduce size and cost of the power supply. The NCP1586 provides a 1 A gate driver design and an internally set 275 kHz oscillator. In addition to the 1 A gate drive capability, other efficiency enhancing features of the gate driver include adaptive non–overlap circuitry. The NCP1586 also incorporates an externally compensated error amplifier and a capacitor programmable soft–start function. Protection features include programmable short circuit protection and under voltage lockout (UVLO). The NCP1586 comes in an 8–pin SOIC package.

#### Features

- Input Voltage Range from 4.5 to 13.2 V

- 275 kHz Internal Oscillator

- Boost Pin Operates to 26.5 V

- Voltage Mode PWM Control

- 0.8 V ±1.0 % Internal Reference Voltage

- Adjustable Output Voltage

- Capacitor Programmable Soft-start

- Internal 1 A Gate Drivers

- 80% Max Duty Cycle

- Input Under Voltage Lockout

- Programmable Current Limit

- This is a Pb–Free Device

## Applications

- Graphics Cards

- Desktop Computers

- Servers / Networking

- DSP & FPGA Power Supply

- DC–DC Regulator Modules

## **ON Semiconductor®**

http://onsemi.com

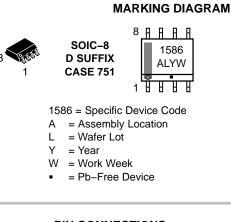

#### **ORDERING INFORMATION**

| Device      | Package   | Shipping <sup>†</sup> |

|-------------|-----------|-----------------------|

| NCP1586DR2G | SOIC-8    | 2500/Tape & Reel      |

|             | (Pb-Free) |                       |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

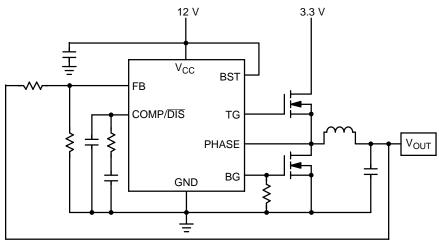

Figure 1. Typical Application Diagram

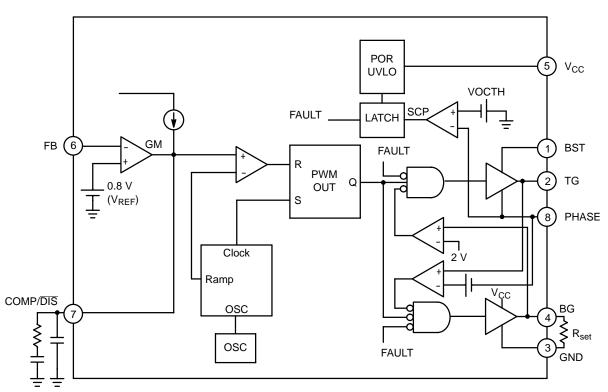

Figure 2. Detailed Block Diagram

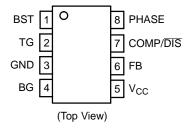

## PIN FUNCTION DESCRIPTION

| Pin No. | Symbol          | Description                                                                                                                                                                                                                                                                                                                                                      |

|---------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | BST             | Supply rail for the floating top gate driver. To form a boost circuit, use an external diode to bring the desired input voltage to this pin (cathode connected to BST pin). Connect a capacitor ( $C_{BST}$ ) between this pin and the PHASE pin. Typical values for $C_{BST}$ range from 0.1 $\mu$ F to 1 $\mu$ F. Ensure that $C_{BST}$ is placed near the IC. |

| 2       | TG              | Top gate MOSFET driver pin. Connect this pin to the gate of the top N–Channel MOSFET.                                                                                                                                                                                                                                                                            |

| 3       | GND             | IC ground reference. All control circuits are referenced to this pin.                                                                                                                                                                                                                                                                                            |

| 4       | BG              | Bottom gate MOSFET driver pin. Connect this pin to the gate of the bottom N–Channel MOSFET.                                                                                                                                                                                                                                                                      |

| 5       | V <sub>CC</sub> | Supply rail for the internal circuitry. Operating supply range is 4.5 V to 13.2 V. Decouple with a 1 $\mu$ F capacitor to GND. Ensure that this decoupling capacitor is placed near the IC.                                                                                                                                                                      |

| 6       | FB              | This pin is the inverting input to the error amplifier. Use this pin in conjunction with the COMP pin to compensate the voltage–control feedback loop. Connect this pin to the output resistor divider (if used) or directly to $V_{out}$ .                                                                                                                      |

| 7       | COMP/DIS        | Compensation Pin. This is the output of the error amplifier (EA) and the non-inverting input of the PWM comparator. Use this pin in conjunction with the FB pin to compensate the voltage-control feedback loop. The compensation capacitor also acts as a soft-start capacitor. Pull this pin low for disable.                                                  |

| 8       | PHASE           | Switch node pin. This is the reference for the floating top gate driver. Connect this pin to the source of the top MOSFET.                                                                                                                                                                                                                                       |

#### ABSOLUTE MAXIMUM RATINGS

| Pin Name                                 | Symbol          | V <sub>MAX</sub>               | V <sub>MIN</sub>              |

|------------------------------------------|-----------------|--------------------------------|-------------------------------|

| Main Supply Voltage Input                | V <sub>CC</sub> | 15 V                           | –0.3 V                        |

| Bootstrap Supply Voltage Input           | BST             | 30 V wrt/GND<br>15 V wrt/PHASE | -0.3 V                        |

| Switching Node (Bootstrap Supply Return) | PHASE           | 25 V                           | -0.7 V<br>-5.0 V for < 50 ns  |

| High–Side Driver Output (Top Gate)       | TG              | 30 V wrt/GND<br>15 V wrt/PHASE | −0.3 V<br>wrt/PHASE           |

| Low-Side Driver Output (Bottom Gate)     | BG              | 15 V                           | -0.3 V<br>-2.0 V for < 200 ns |

| Feedback                                 | FB              | 5.5 V                          | –0.3 V                        |

| COMP/DISABLE                             | COMP/DIS        | 5.5 V                          | –0.3 V                        |

#### MAXIMUM RATINGS

| Rating                                                                | Symbol           | Value       | Unit |

|-----------------------------------------------------------------------|------------------|-------------|------|

| Thermal Resistance, Junction-to-Ambient                               | $R_{\theta JA}$  | 165         | °C/W |

| Thermal Resistance, Junction-to-Case                                  | $R_{\theta JC}$  | 45          | °C/W |

| NCP1586 Operating Junction Temperature Range                          | TJ               | 0 to 125    | °C   |

| NCP1586 Operating Ambient Temperature Range                           | T <sub>A</sub>   | 0 to 70     | °C   |

| Storage Temperature Range                                             | T <sub>stg</sub> | -55 to +150 | °C   |

| Lead Temperature Soldering (10 sec): Reflow (SMD styles only) Pb-Free |                  | 260         | °C   |

| Moisture Sensitivity Level                                            | MSL              | 1           | -    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

| <b>ELECTRICAL CHARACTERISTICS</b> (0°C < $T_A$ < 70°C; 4.5 V < $V_{CC}$ < 13.2 V, 4.5 V < BST < 26.5 V, $C_{TG}$ = $C_{BG}$ = 1.0 nF |  |

|--------------------------------------------------------------------------------------------------------------------------------------|--|

| (REF:NTD30N02), for min/max values unless otherwise noted.)                                                                          |  |

| Characteristic                                      | Conditions                                                        | Min   | Тур  | Max   | Unit     |

|-----------------------------------------------------|-------------------------------------------------------------------|-------|------|-------|----------|

| Input Voltage Range                                 | -                                                                 | 4.5   | -    | 13.2  | V        |

| Boost Voltage Range                                 | -                                                                 | 4.5   | -    | 26.5  | V        |

| Supply Current                                      |                                                                   |       |      |       |          |

| Quiescent Supply Current                            | $V_{FB}$ = 1.0 V, No Switching<br>$V_{CC}$ = 13.2 V               | 0.1   | -    | 0.9   | mA       |

| Boost Quiescent Current                             | $V_{FB}$ = 1.0 V, No Switching, $V_{CC}$ = 13.2 V                 | 2.0   | 3.0  | 4.0   | mA       |

| Under Voltage Lockout                               |                                                                   |       |      |       |          |

| UVLO Threshold                                      | V <sub>CC</sub> Rising Edge                                       | 3.9   | 4.0  | 4.1   | V        |

| UVLO Hysteresis                                     | _                                                                 | 365   | 415  | 465   | mV       |

| Switching Regulator                                 |                                                                   |       |      |       |          |

| VFB Feedback Voltage,<br>Control Loop in Regulation | $T_A = 0$ to $70^{\circ}C$                                        | 0.792 | 0.8  | 0.808 | V        |

| Oscillator Frequency                                | $T_A = 0$ to $70^{\circ}C$                                        | 250   | 275  | 300   | kHz      |

| Ramp-Amplitude Voltage                              |                                                                   | 0.8   | 1.1  | 1.4   | V        |

| Minimum Duty Cycle                                  |                                                                   | 0     | -    | -     | %        |

| Maximum Duty Cycle                                  |                                                                   | 70    | 75   | 80    | %        |

| BG Minimum On Time                                  |                                                                   | -     | 500  | -     | ns       |

| Error Amplifier (GM)                                |                                                                   |       |      |       |          |

| Transconductance                                    |                                                                   | 3.0   | -    | 4.4   | mmho     |

| Open Loop DC Gain                                   |                                                                   | 55    | 70   | -     | DB       |

| Output Source Current                               | V <sub>FB</sub> < 0.8 V                                           | 80    | 120  | -     | μΑ       |

| Output Sink Current                                 | V <sub>FB</sub> > 0.8 V                                           | 80    | 120  | -     |          |

| Input Offset Voltage                                |                                                                   | -2.0  | 0    | 2.0   | mV       |

| Input Bias Current                                  |                                                                   | -     | 0.1  | 1.0   | μΑ       |

| Soft-Start                                          |                                                                   |       |      |       |          |

| SS Source Current                                   | V <sub>FB</sub> < 0.8 V                                           | 8.0   | -    | 14    | μΑ       |

| Switch Over Threshold                               | V <sub>FB</sub> = 0.8 V                                           | -     | 100  | -     | % of Vre |

| Gate Drivers                                        |                                                                   |       |      |       |          |

| Upper Gate Source                                   |                                                                   | -     | 1.0  | -     | А        |

| Upper Gate Sink                                     |                                                                   | -     | 1.0  | -     | А        |

| Lower Gate Source                                   | $V_{CC} = 12 \text{ V}, \text{ VTG} = \text{VBG} = 2.0 \text{ V}$ | -     | 1.0  | -     | А        |

| Lower Gate Sink                                     |                                                                   | -     | 1.0  | -     | А        |

| TG Falling to BG Rising Delay                       | V <sub>CC</sub> = 12 V, TG < 2.0 V, BG > 2.0 V                    | -     | 40   | 90    | ns       |

| BG Falling to TG Rising Delay                       | V <sub>CC</sub> = 12 V, BG < 2.0 V, TG > 2.0 V                    | _     | 40   | 60    | ns       |

| Enable Threshold                                    |                                                                   | 0.3   | 0.4  | 0.5   | V        |

| Over-Current Protection                             | -                                                                 |       | -    |       |          |

| OCSET Current Source                                | Sourced from BG pin, before SS                                    | _     | 10   | -     | μΑ       |

| OC Switch–Over Threshold                            |                                                                   | -     | 700  | -     | mV       |

| Fixed OC Threshold                                  |                                                                   | _     | -375 | -     | mV       |

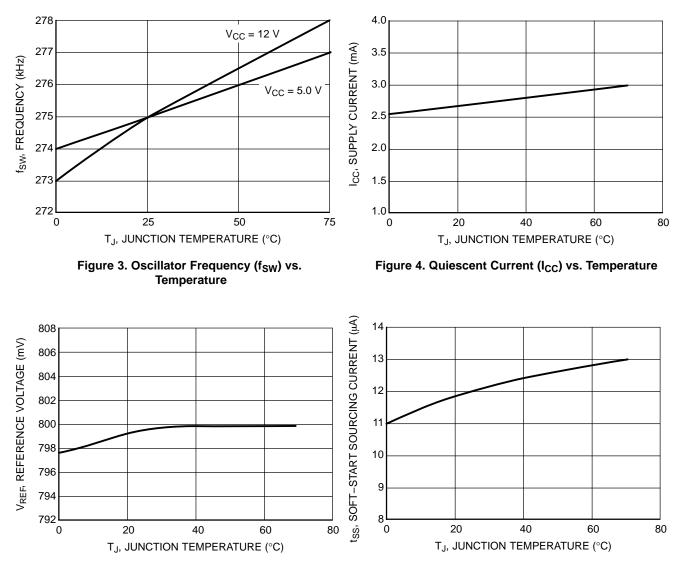

## **TYPICAL CHARACTERIZATION CURVES**

(T<sub>A</sub> = 25°C unless otherwise noted)

Figure 6. Soft–Start Sourcing Current (t<sub>SS</sub>) vs. Temperature

#### DETAILED OPERATING DESCRIPTION

#### General

The NCP1586 is an 8–pin PWM controller intended for DC–DC conversion from 5.0 V & 12 V buses. The NCP1586 has a 1 A internal gate driver circuit designed to drive N–channel MOSFETs in a synchronous–rectifier buck topology. The output voltage of the converter can be precisely regulated down to 800 mV  $\pm$ 1.0% when the V<sub>FB</sub> pin is tied to V<sub>OUT</sub>. The switching frequency, is internally set to 275 kHz. A high gain operational transconductance error amplifier (OTA) is used.

#### **Duty Cycle and Maximum Pulse Width Limits**

In steady state DC operation, the duty cycle will stabilize at an operating point defined by the ratio of the input to the output voltage. The NCP1586 can achieve an 80% duty cycle. There is a built in off-time which ensures that the bootstrap supply is charged every cycle. The NCP1586 can allow a 12 V to 0.8 V conversion at 275 kHz.

#### Input Voltage Range (V<sub>CC</sub> and BST)

The input voltage range for both  $V_{CC}$  and BST is 4.5 V to 13.2 V with respect to GND and PHASE, respectively. Although BST is rated at 13.2 V with respect to PHASE, it can also tolerate 26.4 V with respect to GND.

#### **External Enable/Disable**

When the Comp pin voltage falls or is pulled externally below the 400 mV threshold, it disables the PWM Logic and the gate drive outputs. In this disabled mode, the operational transconductance amplifier (EOTA) output source current is reduced and limited to the Soft–Start mode of 10  $\mu$ A.

#### **Normal Shutdown Behavior**

Normal shutdown occurs when the IC stops switching because the input supply reaches UVLO threshold. In this case, switching stops, the internal SS is discharged, and all GATE pins go low. The switch node enters a high impedance state and the output capacitors discharge through the load with no ringing on the output voltage.

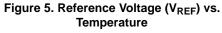

#### External Soft-Start

The NCP1586 features an external soft–start function, which reduces inrush current and overshoot of the output voltage. Soft–start is achieved by using the internal current source of 10  $\mu$ A (typ), which charges the external integrator capacitor of the transconductance amplifier. Figure 7 is a typical soft–start sequence. This sequence begins once V<sub>CC</sub> surpasses its UVLO threshold and OCP programming is complete. During soft–start, as the Comp Pin rises through 400 mV, the PWM Logic and gate drives are enabled. When the feedback voltage crosses 800 mV, the EOTA will be given control to switch to its higher regulation mode output current of 120  $\mu$ A.

#### UVLO

Undervoltage Lockout (UVLO) is provided to ensure that unexpected behavior does not occur when  $V_{CC}$  is too low to support the internal rails and power the converter. For the NCP1586, the UVLO is set to ensure that the IC will start up when  $V_{CC}$  reaches 4.0 V and shutdown when  $V_{CC}$  drops below 3.7 V. This permits operation when converting from a 5.0 input voltage.

#### **Overcurrent Threshold Setting**

NCP1586 allows to easily program an Overcurrent Threshold ranging from 50 mV to 550 mV, simply by adding a resistor (RSET) between BG and GND. During a short period of time following  $V_{CC}$  rising over UVLO threshold, an internal 10  $\mu$ A current (I<sub>OCSET</sub>) is sourced from BG pin, determining a voltage drop across R<sub>OCSET</sub>. This voltage drop will be sampled and internally held by the device as Overcurrent Threshold. The OC setting procedure overall time length is about 6 ms. Connecting a R<sub>OCSET</sub> resistor between BG and GND, the programmed threshold will be:

$$IOCth = \frac{IOCSET \cdot ROCSET}{RDS(on)}$$

(eq. 1)

RSET values range from 5 k $\Omega$  to 55 k $\Omega$ . In case R<sub>OCSET</sub> is not connected, the device switches the OCP threshold to a fixed 375 mV value: an internal safety clamp on BG is triggered as soon as BG voltage reaches 700 mV, enabling the 375 mV fixed threshold and ending OC setting phase. The current trip threshold tolerance is ±25 mV. The accuracy of the set point is best at the highest set point (550 mV). The accuracy will decrease as the set point decreases.

#### **Current Limit Protection**

In case of a short circuit or overload, the low–side (LS) FET will conduct large currents. The controller will shut down the regulator in this situation for protection against overcurrent. The low–side R<sub>DS(on)</sub> sense is implemented at the end of each of the LS–FET turn–on duration to sense the over current trip point. While the LS driver is on, the Phase voltage is compared to the internally generated OCP trip voltage. If the phase voltage is lower than OCP trip voltage, an overcurrent condition occurs and a counter is initiated. When the counter completes, the PWM logic and both HS–FET and LS–FET are turned off. The controller will retry to see if the short circuit or overload condition is removed through the soft start cycle. The minimum turn–on time of the LS–FET is set to be 500 nS.

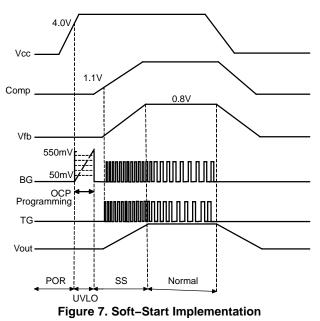

#### Drivers

The NCP1586 includes 1 A gate drivers to switch external N-channel MOSFETs. This allows the NCP1586 to address high-power as well as low-power conversion requirements. The gate drivers also include adaptive non-overlap circuitry. The non-overlap circuitry increase efficiency, which minimizes power dissipation, by minimizing the body diode conduction time.

A detailed block diagram of the non-overlap and gate drive circuitry used in the chip is shown in Figure 8.

Figure 8. Block Diagram

Careful selection and layout of external components is required, to realize the full benefit of the onboard drivers. The capacitors between  $V_{CC}$  and GND and between BST and SWN must be placed as close as possible to the IC. The current paths for the TG and BG connections must be optimized. A ground plane should be placed on the closest layer for return currents to GND in order to reduce loop area and inductance in the gate drive circuit.

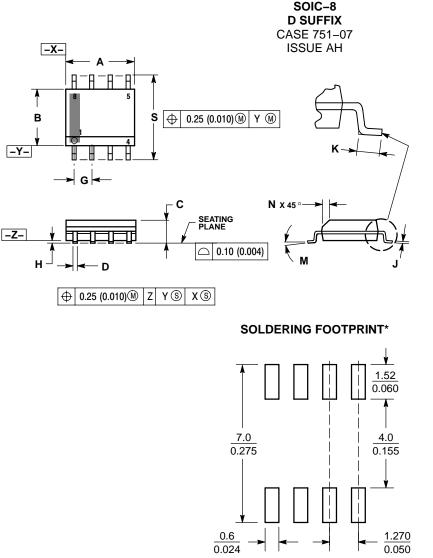

#### PACKAGE DIMENSIONS

NOTES

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION. 3.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) 4 PER SIDE.

- PROTRUSION D DOES NOT INCLUDE DAMBAR PROTRUSION ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT 5

- MAXIMUM MATERIAL CONDITION 751–01 THRU 751–06 ARE OBSOLETE. NEW STANDARD IS 751–07. 6

|     | MILLIMETERS |          | INC   | HES       |  |  |

|-----|-------------|----------|-------|-----------|--|--|

| DIM | MIN         | MAX      | MIN   | MAX       |  |  |

| Α   | 4.80        | 5.00     | 0.189 | 0.197     |  |  |

| в   | 3.80        | 4.00     | 0.150 | 0.157     |  |  |

| С   | 1.35        | 1.75     | 0.053 | 0.069     |  |  |

| D   | 0.33        | 0.51     | 0.013 | 0.020     |  |  |

| G   | 1.27        | 1.27 BSC |       | 0.050 BSC |  |  |

| Н   | 0.10        | 0.25     | 0.004 | 0.010     |  |  |

| J   | 0.19        | 0.25     | 0.007 | 0.010     |  |  |

| κ   | 0.40        | 1.27     | 0.016 | 0.050     |  |  |

| М   | 0 °         | 8 °      | 0 °   | ° 8       |  |  |

| Ν   | 0.25        | 0.50     | 0.010 | 0.020     |  |  |

| s   | 5.80        | 6.20     | 0.228 | 0.244     |  |  |

mm SCALE 6:1 (inches \*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative