#### **Features**

- · Generates standard CCITT R1 MF tones

- Digital input control

- Linear (analog) output

- · Power output capable of driving standard line

- 14-pin DIP

- Single 5-Volt supply

- Inexpensive 3.58 MHz time base

### **Applications**

- Telephone systems

- Test equipment

## **Description**

The M-993 is a monolithic CMOS integrated circuit designed to generate multifrequency (MF) tone pairs for use in trunk signaling. The tones generated conform to CCITT R1 signal recommendations and to AT&T MF standards. The M-993 permits design engineers to implement a highly accurate MF sender with a minimum of space, power, and added components. The accuracy of the tone frequencies is assured through use of an easily obtained 3.58 MHz color burst crystal or an external 3.58 MHz clock source.

# **Ordering Information**

| Part # | Description        |

|--------|--------------------|

| M-993  | 14-pin plastic DIP |

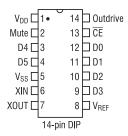

### Pin Diagram

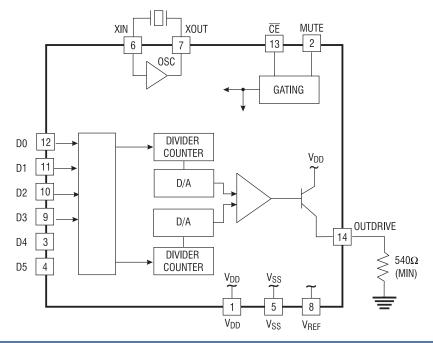

## **Block Diagram**

## **Absolute Maximum Ratings**

| Storage Temperature           | -55 to 125°C                      |  |  |

|-------------------------------|-----------------------------------|--|--|

| Operating Ambient Temperature | -25 to 70°C                       |  |  |

| V <sub>DD</sub>               | 7.0V                              |  |  |

| Any Input Voltage             | $V_{SS}$ - 0.6 to $V_{DD}$ + 0.6V |  |  |

#### Note:

Absolute Maximum Ratings are stress ratings. Stresses in excess of these ratings can cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this data sheet is not implied. Exposure of the device to the absolute maximum ratings for an extended period may degrade the device and effect its reliability.

# **Specifications**

|               | Parameter                                                 | Min                    | Тур     | Max                    | Units | Notes |  |  |  |

|---------------|-----------------------------------------------------------|------------------------|---------|------------------------|-------|-------|--|--|--|

| Power Supply  | V <sub>DD</sub>                                           | 4.75                   | -       | 5.25                   | V     | 1     |  |  |  |

| and Reference | Current Drain, IDD                                        | -                      | 2.0/4.0 | -                      | mA    | 8     |  |  |  |

|               | V <sub>REF</sub> PIN:                                     |                        |         |                        |       |       |  |  |  |

|               | Voltage                                                   | 48% of V <sub>DD</sub> | -       | 52% of V <sub>DD</sub> | %     | -     |  |  |  |

|               | Internal Resistance from $V_{REF}$ to $V_{DD}$ , $V_{SS}$ | 3.25                   | -       | 6.75                   | kΩ    | -     |  |  |  |

| Oscillator    | Frequency Deviation                                       | -0.01                  | -       | +0.01                  | %     | 7     |  |  |  |

|               | External CLock: (X <sub>OUT</sub> open)                   |                        |         |                        |       |       |  |  |  |

|               | V <sub>IL</sub>                                           | 0                      | -       | 0.2                    | V     | -     |  |  |  |

|               | V <sub>IH</sub>                                           | V <sub>DD</sub> - 0.2  | -       | V <sub>DD</sub>        | V     | -     |  |  |  |

|               | Duty Cycle                                                | 40                     | -       | 60                     | %     | -     |  |  |  |

|               | X <sub>IN</sub> , X <sub>OUT</sub> Loading:               |                        |         |                        |       |       |  |  |  |

|               | Capacitance                                               | -                      | -       | 10                     | pF    | 9     |  |  |  |

|               | Resistance                                                | 20                     | -       | -                      | MΩ    | -     |  |  |  |

| Tone Output   | Frequency Deviation                                       | -1.5                   | -       | 1.5                    | %     | -     |  |  |  |

|               | Level                                                     | 110                    | -       | 180                    | mV    | 2     |  |  |  |

|               | Distorting Components                                     | -35                    | -       | -                      | dB    | 2, 3  |  |  |  |

|               | Idle                                                      | -                      | -       | -60                    | dBm   | 4     |  |  |  |

|               | OUTDRIVE Envelope Rise Time                               | -                      | -       | 4                      | ms    | 5     |  |  |  |

| Control       | DX, CE Pins:                                              |                        |         |                        |       |       |  |  |  |

|               | V <sub>IL</sub>                                           | -                      | -       | 0.5                    | V     | 6     |  |  |  |

|               | V <sub>IH</sub>                                           | 2.5                    | -       | -                      | V     | -     |  |  |  |

|               | Mute Pins:                                                |                        |         |                        |       |       |  |  |  |

|               | VOL (ISINK = -100 μA)                                     | -                      | -       | 1.5                    | V     | -     |  |  |  |

|               | VOH (ISOURCE = 100 μA)                                    | V <sub>DD</sub> - 1.5  | -       | -                      | V     | -     |  |  |  |

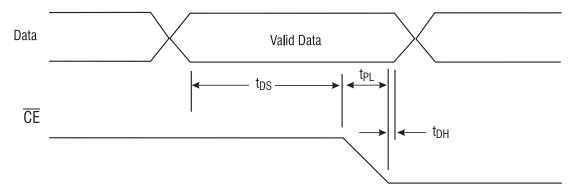

| Timing        | Data Setup (t <sub>DSRT</sub> )                           | 200                    | -       | -                      | ns    | 10    |  |  |  |

| Ů             | Data Hold (t <sub>DH</sub> )                              | 10                     | -       | -                      | ns    | -     |  |  |  |

|               | Chip Enable Fall (t <sub>PL</sub> )                       | -                      | -       | 90                     | ns    | -     |  |  |  |

|               | Tone On Delay $(t_{TO})$                                  | 5                      | -       | -                      | ms    | -     |  |  |  |

|               | Tone Off Delay $(t_{TD})$                                 | 5                      | -       | -                      | ms    | -     |  |  |  |

|               | Mute Delay from Outdrive (t <sub>MO</sub> )               | -                      | -       | 200                    | ns    | -     |  |  |  |

Unless otherwise noted,  $V_{DD}$  -  $V_{SS}$  = 5 VDC, Ta - 25° C

Notes:

- 1. All DC voltages are referenced to V<sub>SS</sub>.

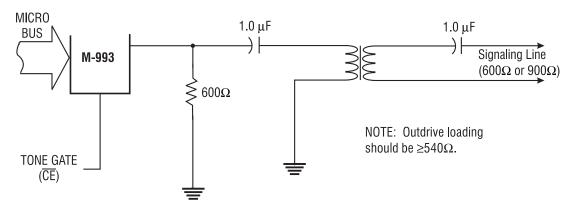

2. Vrms per tone, 540W load.

3. Any one frequency relative to the lowest level output tone (f<4000 Hz).

- 5. To 90% maximum amplitude.

- 6. For all supply voltages in the operating range.

7. At XOUT pin as compared to 3.579545 MHz.

8. OUTDRIVE with load >5 KW/OUTDRIVE with 540W load.

- Crystal oscillator active.

Measured 90% to 10%.

<sup>1.</sup> Exceeding these ratings may permanently damage the M-993.

#### **Pin Function**

| Pin              | Function                                    |

|------------------|---------------------------------------------|

| CE               | Latches data and enables output (active low |

|                  | input).                                     |

| D0 - D3          | Data input pins. (See Data/Tone Selection.) |

| D4-D5            | Leave open.                                 |

| MUTE             | Output indicates that a signal is being     |

|                  | generated at OUTDRIVE.                      |

| OUTDRIVE         | Linear buffered tone output.                |

| $V_{DD}$         | Most positive power supply input pin.       |

| $V_{REF}$        | Internally generated mid-power supply       |

|                  | voltage (output).                           |

| $V_{SS}$         | Most negative power supply input pin.       |

| X <sub>IN</sub>  | Crystal oscillator or digital clock input.  |

| X <sub>OUT</sub> | Crystal oscillator output.                  |

### **Data/Tone Selection**

| D3 | D2 | D1 | D0 | Frequency (Hz) |      | Use            |

|----|----|----|----|----------------|------|----------------|

|    |    |    |    | 1              | 2    |                |

| 0  | 0  | 0  | 0  | 1100           | 1700 | Key Pulse (KP) |

| 0  | 0  | 0  | 1  | 700            | 900  | Digit 1        |

| 0  | 0  | 1  | 0  | 700            | 1100 | Digit 2        |

| 0  | 0  | 1  | 1  | 900            | 1100 | Digit 3        |

| 0  | 1  | 0  | 0  | 700            | 1300 | Digit 4        |

| 0  | 1  | 0  | 1  | 900            | 1300 | Digit 5        |

| 0  | 1  | 1  | 0  | 1100           | 1300 | Digit 6        |

| 0  | 1  | 1  | 1  | 700            | 1500 | Digit 7        |

| 1  | 0  | 0  | 0  | 900            | 1500 | Digit 8        |

| 1  | 0  | 0  | 1  | 1100           | 1500 | Digit 9        |

| 1  | 0  | 1  | 0  | 1300           | 1500 | Digit 0        |

| 1  | 0  | 1  | 1  | 1500           | 1700 | ST             |

| 1  | 1  | 0  | 0  | 900            | 1700 | ST1            |

| 1  | 1  | 0  | 1  | 1300           | 1700 | ST2            |

| 1  | 1  | 1  | 0  | 700            | 1700 | ST3            |

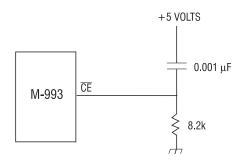

#### **Power-On Reset Circuit**

A typical control sequence for the M-993 is: (1) set data lines Selection for data settings for a particular tone pair output).to desired frequency selection, (2) wait for data lines to settle, (3) drive the chip enable (CE) low, (4) maintain CE low for desired tone duration (Note: data lines may be changed after data hold time), and (5) return CE to a logic high.

In a bus-oriented system, noise on the data lines may propagate through the device and appear at the output. To safeguard against this, use an external latch to clock the data into the device. In addition, it is good practice to bypass the  $V_{\rm REF}$  pin to ground with a small capacitor (~0.01mF) to reduce power supply noise. The designer should be aware of device timing requirements and design accordingly. Beware of hardwiring the data input pins for dedicated tone generation. An RC network like that shown in Power-On Reset Circuit should be used to momentarily reset the device immediately following a power-up to ensure reliable operation.

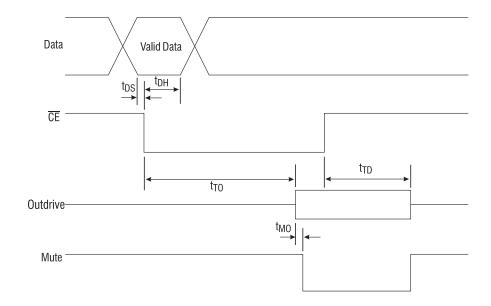

# **Timing Diagram**

# **Expanded Timing Diagram**

# **Typical Application**

# **Mechanical Dimensions**

# 14-Pin DIP

|    | Tolerances |      |             |      |  |  |  |

|----|------------|------|-------------|------|--|--|--|

|    | Inc        | hes  | Metric (mm) |      |  |  |  |

|    | Min        | Max  | Min         | Max  |  |  |  |

| Α  | -          | .210 | -           | 5.33 |  |  |  |

| A1 | .015       | -    | .38         | -    |  |  |  |

| b  | .014       | .022 | .36         | .56  |  |  |  |

| b2 | .045       | .070 | 1.1         | 1.8  |  |  |  |

| С  | .008       | .014 | .20         | .36  |  |  |  |

| D  | .735       | .775 | 18.7        | 19.7 |  |  |  |

| Е  | .300       | .325 | 7.6         | 8.3  |  |  |  |

| E1 | .240       | .280 | 6.1         | 7.1  |  |  |  |

| е  | .100       | BSC  | 2.54 BSC    |      |  |  |  |

| ес | 0°         | 15°  | 0°          | 15°  |  |  |  |

| L  | .115       | .150 | 2.9         | 4.1  |  |  |  |

Drawing not to scale.

Does not reflect actual part marking.

Dimensions mm (inches)

#### **CLARE LOCATIONS**

Clare Headquarters 78 Cherry Hill Drive Beverly, MA 01915 Tel: 1-978-524-6700 Fax: 1-978-524-4900

Toll Free: 1-800-27-CLARE

Clare Switch Division 4315 N. Earth City Expressway Earth City, MO 63045

Tel: 1-314-770-1832 Fax: 1-314-770-1812

Clare Micronix Division 145 Columbia

Aliso Viejo, CA 92656-1490 Tel: 1-949-831-4622

Tel: 1-949-831-4622 Fax: 1-949-831-4628

#### **SALES OFFICES**

#### **AMERICAS**

## **Americas Headquarters**

Clare

78 Cherry Hill Drive Beverly, MA 01915 Tel: 1-978-524-6700 Fax: 1-978-524-4900 Toll Free: 1-800-27-CLARE

#### **Eastern Region**

Clare

603 Apache Court Mahwah, NJ 07430 Tel: 1-201-236-0101 Fax: 1-201-236-8685 Toll Free: 1-800-27-CLARE

### **Central Region**

Clare Canada Ltd. 3425 Harvester Road, Suite 202 Burlington, Ontario L7N 3N1

Tel: 1-905-333-9066 Fax: 1-905-333-1824

# Western Region

Clare

1852 West 11th Street, #348

Tracy, CA 95376 Tel: 1-209-832-4367 Fax: 1-209-832-4732 Toll Free: 1-800-27-CLARE

#### Canada

Clare Canada Ltd. 3425 Harvester Road, Suite 202 Burlington, Ontario L7N 3N1

Tel: 1-905-333-9066 Fax: 1-905-333-1824

### **EUROPE**

#### **European Headquarters**

CP Clare nv Bampslaan 17 B-3500 Hasselt (Belgium) Tel: 32-11-300868 Fax: 32-11-300890

#### **France**

Clare France Sales Lead Rep 99 route de Versailles 91160 Champlan France

Tel: 33 1 69 79 93 50

Fax: 33 1 69 79 93 59

#### Germany

Clare Germany Sales ActiveComp Electronic GmbH Mitterstrasse 12 85077 Manching Germany

Tel: 49 8459 3214 10 Fax: 49 8459 3214 29

#### Italy

C.L.A.R.E.s.a.s. Via C. Colombo 10/A I-20066 Melzo (Milano) Tel: 39-02-95737160 Fax: 39-02-95738829

#### Sweden

Clare Sales Comptronic AB Box 167 S-16329 Spånga Tel: 46-862-10370 Fax: 46-862-10371

# United Kingdom

Clare UK Sales Marco Polo House Cook Way Bindon Road Taunton

UK-Somerset TA2 6BG Tel: 44-1-823 352541 Fax: 44-1-823 352797

#### ASIA/PACIFIC

#### Asian Headquarters

Clare Room N1016, Chia-Hsin, Bldg II, 10F, No. 96, Sec. 2 Chung Shan North Road Taipei, Taiwan R.O.C.

Tel: 886-2-2523-6368 Fax: 886-2-2523-6369

# http://www.clare.com

Clare, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. Neither circuit patent licenses nor indemnity are expressed or implied. Except as set forth in Clare's Standard Terms and Conditions of Sale, Clare, Inc. assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

The products described in this document are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or where malfunction of Clare's product may result in direct physical harm, injury, or death to a person or severe property or environmental damage. Clare, Inc. reserves the right to discontinue or make changes to its products at any time without notice.

Specification: DS-M-993-R1 ©Copyright 2001, Clare, Inc. All rights reserved. Printed in USA. 7/18/01