# **LS7060C** LS7061C

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

January 2002

# **32 BIT BINARY UP COUNTER** WITH BYTE MULTIPLEXED THREE-STATE OUTPUTS ADVANCE INFORMATION

#### **FEATURES:**

- DC to 50MHz Count Frequency

- Byte Multiplexer

- DC to 10MHz Byte Output Scan Frequency

- +4.75V to +5.25V Operation (VDD VSS)

- Three-State Data Outputs; Bus, TTL and CMOS Compatible

- Inputs TTL and CMOS Compatible

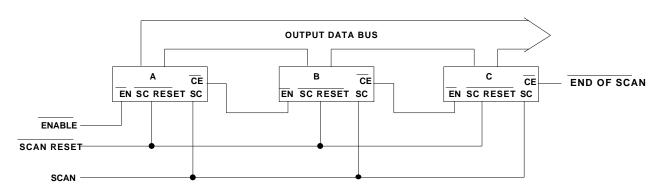

- Unique Cascade Feature Allows Multiplexing of Successive Bytes of Data in Sequence in Multiple Counter Systems

- · Low Power Dissipation

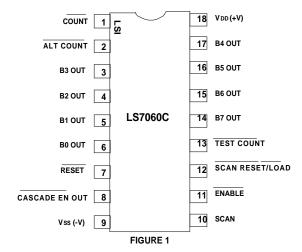

- LS7060C (DIP), LS7060C-S (SOIC) See Figure 1

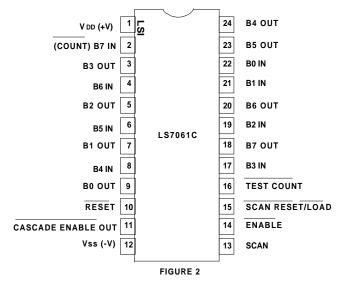

- LS7061C (DIP), LS7061C-S (SOIC) See Figure 2

#### **DESCRIPTION:**

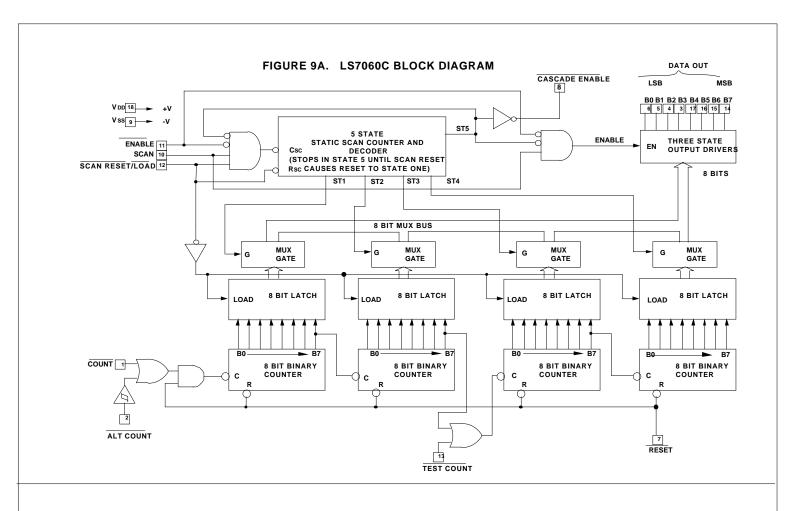

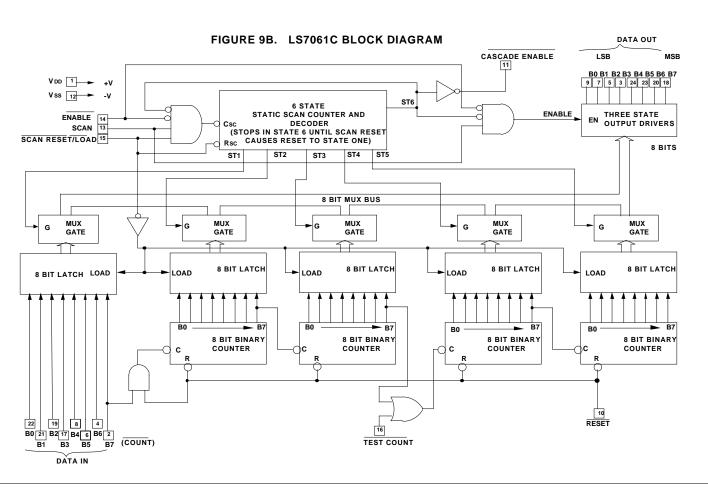

The LS7060C/LS7061C are CMOS Silicon Gate, 32 bit Up Counters. The ICs include latches, multiplexer, byte output sequencer, eight three-state binary data output drivers and output cascading logic.

# **DESCRIPTION OF OPERATION:**

# 32 BIT BINARY UP COUNTER - LS7060C (LS7061C)

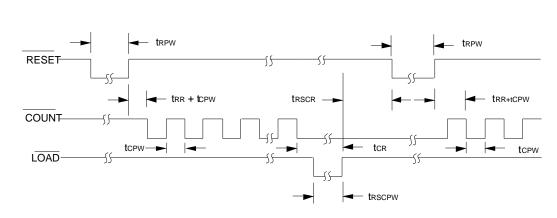

The 32 bit static ripple through counter increments on the negative edge of the input count pulse. Maximum ripple time is 20ns transition count of 32 ones to 32 zeros.

Guaranteed count frequency is DC to 50MHz.

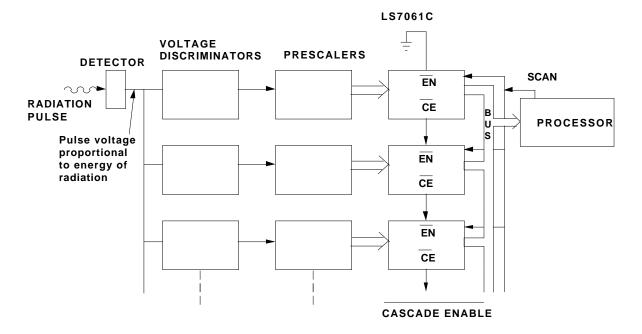

See Figure 9A (9B) for Block Diagram.

# COUNT. ALT COUNT (LS7060C)

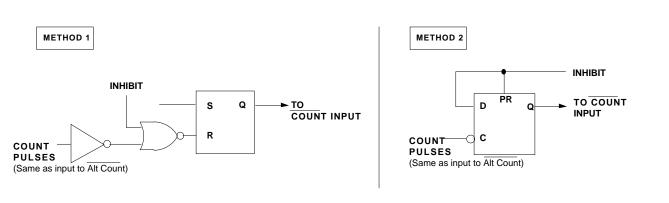

Input count pulses to the 32 bit counter may be applied through either of these two inputs. The ALT COUNT input circuitry contains a Schmitt trigger network which allows proper counting with "infinitely" long clock edges. A high applied to either of these two inputs inhibits counting.

# COUNT (LS7061C)

Input count pulses to the 32 bit counter may be applied through this input. This input is the most significant bit of the external data byte.

# RESET

All 32 counter bits are reset to zero when RESET is brought low for a minimum of 20ns. RESET must be high for a minimum of 10ns before next valid count can be recorded.

# **TEST COUNT**

Count pulses may be applied to the last 16 bits of the binary counter through this input, as long as Bit 16 of the counter is a low. The counter advances on the negative transition of these pulses. This input is intended to be used for test purposes.

NOTE: LS7060C and LS7061C can directly replace LS7060 and LS7061 in all existing applications.

#### **PIN ASSIGNMENT - TOP VIEW**

#### PIN ASSIGNMENT - TOP VIEW

# **LATCHES**

32 bits of latch are provided for storage of counter data for the LS7060C. 40 bits of latch are provided for the LS7061C of which eight are for storage of a high speed external prescaling counter and the remaining 32 are for the contents of the chip counter data. All latches are loaded when the LOAD input is brought low for a minimum of 10ns and kept low until a minimum of 20ns has elapsed from previous negative edge of count pulse (ripple time). Storage of valid data occurs when LOAD is brought high for a minimum of 20ns before next negative edge of count pulse or RESET.

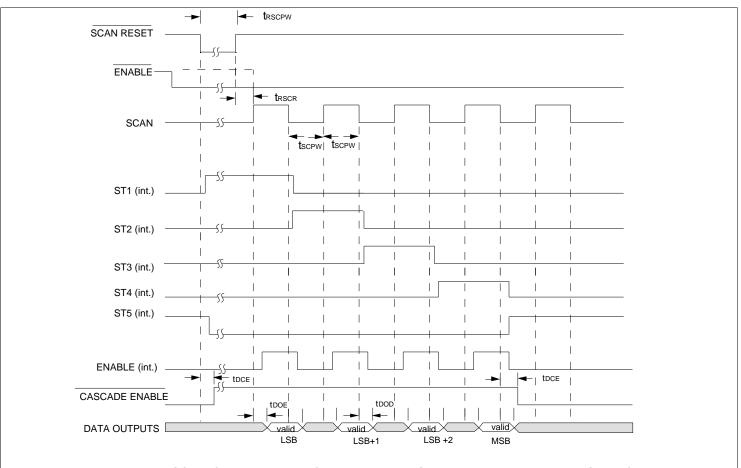

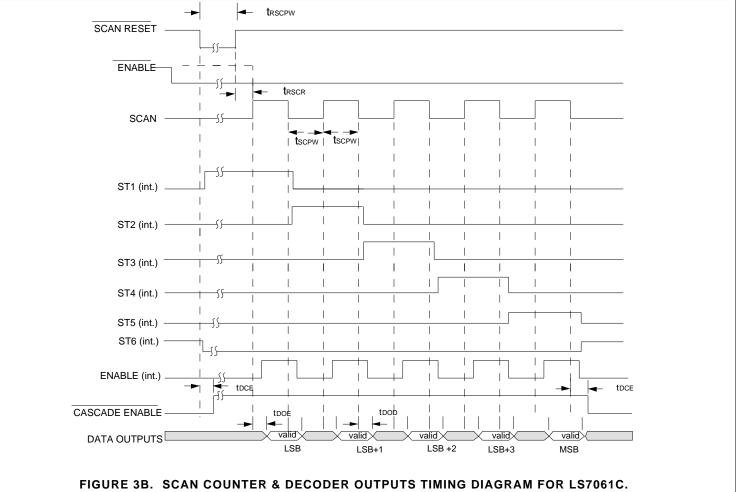

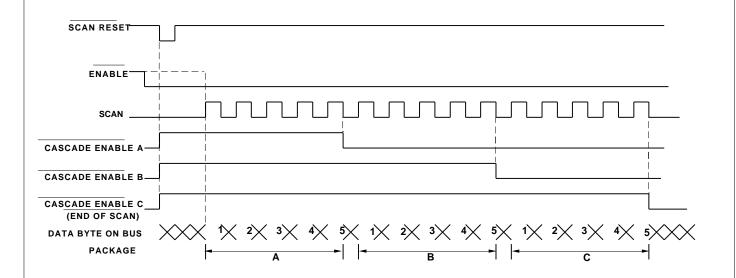

#### SCAN COUNTER AND DECODER

The scan counter is reset to the least significant byte position (State 1) when SCAN RESET input is brought low for a minimum of 10ns. The scan counter is enabled for counting as long as the ENABLE input is held low. The counter advances to the next significant byte position on each negative transition of the SCAN pulse. When the scan counter advances to State 5 for the LS7060C or Stage 6 for the LS7061C it disables the Output Drivers and stops in that state until SCAN RESET is again brought low.

# **SCAN**

When the scan counter is enabled, each negative transition of this input advances the scan counter to its next state. When SCAN is low the Data Outputs are disabled. When SCAN is brought high the Data Outputs are enabled and present the latched counter data corresponding to the present state of the scan counter. Therefore, in microprocessor applications, the Data Output Bus may be utilized for other activities while new data is propagating to the outputs. This positive SCAN pulse can be viewed as a "Place the next byte on my bus" instruction from the microprocessor. Minimum positive and negative pulse widths of 10ns for the SCAN signal are required for scan counter operation.

# SCAN RESET/LOAD

When this input is brought low for a minimum of 10ns, the scan counter is reset to State 1, the least significant byte position, and the latches are simultaneously loaded with new count information.

#### **ENABLE**

When this input is high, the scan counter and the Data Outputs are disabled. When ENABLE is low, the scan counter and Data Outputs are enabled for normal operation. Transition of this input should only be made while the SCAN input is in a low state in order to prevent false clocking of the scan counter.

# **CASCADE ENABLE**

This output is normally high. It transitions low and stays low when the scan counter advances to State 5 for LS7060C and State 6 for LS7061C. In a multiple counter system this output is connected to the ENABLE input of the next counter in the cascade string. The SCAN input and SCAN RESET/LOAD input are carried to all the counters in the "Cascade". Counter 1 then presents its bytes of data to the Output Bus on each positive transition of the SCAN pulse as previously discussed. When State 5 for LS7060C or State 6 for LS7061C of Counter 1 is achieved, Counter 2 presents its data to the Output Bus. This sequence continues until all counters in the cascade have been addressed. See Figure 5 for an illustration of a 3 device cascade design. This output is TTL and CMOS compatible.

#### THREE-STATE DATA OUTPUT DRIVERS

The eight Data Output Drivers are disabled when either ENABLE input is high, the scan counter is in State 5 for LS7060C and State 6 for LS7061C, or the SCAN input is low. The Output Drivers are TTL and Bus compatible.

# ABSOLUTE MAXIMUM RATINGS:

| PARAMETER                | SYMBOL | VALUE       | UNIT |

|--------------------------|--------|-------------|------|

| StorageTemperature       | Tstg   | -55 to +150 | °C   |

| Operating Temperature    | TA     | 0 to +70    | °C   |

| Voltage (any pin to Vss) | Vin    | +10 to -0.3 | V    |

# DC ELECTRICAL CHARACTERISTICS:

$(VDD = +5V \pm 5\%, VSS = 0V, TA = 0^{\circ}C \text{ to } +70^{\circ}C \text{ unless otherwise noted.})$

| PARAMETER                                     | SYMBOL  | MIN  | MAX  | UNIT | CONDITIONS                                                 |

|-----------------------------------------------|---------|------|------|------|------------------------------------------------------------|

| Quiescent Power Supply<br>Current             | IDD     | -    | 0.5  | mA   | VDD = Max, Outputs No Load, Ø Frequency                    |

| Power Supply Current                          | IDD     | 4    | -    | mA   | 15 MHz Operating Frequency  VDD = Max, Outputs No Load     |

| Power Supply Current                          | IDD     | -    | 8    | mA   | At Maximum Operating Frequency  VDD = Max, Outputs No Load |

| Input High Voltage                            | Vih     | +3.5 | Vdd  | V    | -                                                          |

| Input Low Voltage                             | VIL     | 0    | +0.6 | V    | -                                                          |

| Output High Voltage                           |         |      |      |      |                                                            |

| CASCADE ENABLE                                | Voн     | +2.4 | -    | V    | Io = -6mA, $VDD = Min$                                     |

| B0 - B7                                       | Vон     | +2.4 | -    | V    | Io = -33mA, $VDD = Min$                                    |

| Output Low Voltage                            |         |      |      |      |                                                            |

| CASCADE ENABLE                                | Vol     | -    | +0.4 | V    | IO = 3mA, $VDD = Min$                                      |

| B0 - B7                                       | Vol     | -    | +0.4 | V    | Io = 10mA, VDD = Min                                       |

| Output Source Current                         | Isource | -34  | -    | mA   | Vo = +1.2V, VDD = Min                                      |

| B0 - B7 Outputs                               |         | -36  | -    | mA   | Vo = +0.8V, $VDD = Min$                                    |

|                                               |         | -38  | -    | mA   | Vo = +0.4V, $VDD = Min$                                    |

| Output Sink Current                           | Isink   | 25   | -    | mA   | Vo = +1.2V, $VDD = Min$                                    |

| B0 - B7 Outputs                               |         | 20   | -    | mA   | Vo = +0.8V, $VDD = Min$                                    |

|                                               |         | 10   | -    | mA   | Vo = +0.4V, $VDD = Min$                                    |

| Output Leakage Current<br>B0 - B7 (Off State) | lol     | -    | 10   | nA   | VO = +.4V to $+2.4V$ , $VDD = Min$                         |

| Input Capacitance                             | CIN     | -    | 6    | pF   | $TA = 25^{\circ}C$ , $f = 1MHz$                            |

| Output Capacitance                            | Соит    | -    | 12   | pF   | $TA = 25^{\circ}C$ , $f = 1MHz$                            |

| Input Leakage Current<br>ENABLE, RESET, SCAN  | lμ      | -    | 10   | nA   | VDD = Max                                                  |

|                    | SYMBOL | MIN | MAX  | UNIT | CONDITIONS               |

|--------------------|--------|-----|------|------|--------------------------|

| INPUT CURRENT      |        |     |      |      |                          |

| *SCAN RESET/LOAD   | lін    | -   | -3.5 | μΑ   | VDD = Max, VIH = +3.5V   |

|                    | lı∟    | -   | -5   | μA   | VDD = Max, VIL = 0V      |

| **All Count inputs | IIН    | -   | 5    | μA   | VDD = Max, VIH = +3.5V   |

| ·                  | Iı∟    | -   | 1    | μA   | VDD = Max, $VIL = 0.35V$ |

|                    |        |     |      | ·    |                          |

# DYNAMIC ELECTRICAL CHARACTERISTICS:

(VDD =  $+5V \pm 5\%$ , Vss = 0v, TA = 0°C to +70°C unless otherwise noted.)

| PARAMETER Count Frequency (All Count inputs)                                                      | SYMBOL<br>fc | MIN<br>DC | <b>MAX</b> 50 | <b>UNIT</b><br>MHz | CONDITIONS                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------|--------------|-----------|---------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Count Pulse Width (All Count Inputs)                                                              | tcpw         | 10        | -             | ns                 | Measured at 50% point,<br>Max tr, tr = 1ns                                                                                                                                                  |

| Count Ripple Time                                                                                 | <b>t</b> CR  | -         | 20            | ns                 | Transition from 32 ones to 32 zeros from negative edge of count pulse                                                                                                                       |

| Reset Pulse Width<br>(All Counter Stages<br>Fully Reset)                                          | trpw         | 20        | -             | ns                 | Measured at 50% point<br>Max tr, tf = 10ns                                                                                                                                                  |

| RESET Removal Time<br>(Reset Removed From<br>All Counter Stages)                                  | trr          | -         | 10            | ns                 | Measured from RESET signal at Vін                                                                                                                                                           |

| SCAN Frequency                                                                                    | fsc          |           | 10            | MHz                |                                                                                                                                                                                             |

| SCAN Prequency SCAN Pulse Width                                                                   | tscpw        | 50        | -             | ns                 | Measured at 50% point Max tr, tf = 10ns                                                                                                                                                     |

| SCAN RESET/LOAD Pulse Width (All latches loaded and Scan Counter Reset to Least Significant Byte) | trscpw       | 10        | -             | ns                 | Measured at 50% point Max tr, tr = 5ns                                                                                                                                                      |

| SCAN RESET/LOAD Removal Time (Reset Removed from Scan Counter; Load Command Removed From Latches) | trscr        | -         | 10            | ns                 | Measured from SCAN RESET/LOAD at VIH                                                                                                                                                        |

| Output Disable<br>Delay Time<br>(B0 - B7)                                                         | tDOD         | -         | 5             | ns                 | Transition to Output High<br>Impedance State Measured<br><u>From Sc</u> an at VIL or<br>ENABLE at VIH                                                                                       |

| Output ENABLE<br>Delay Time<br>(B0 - B7)                                                          | tdoe         | -         | 5             | ns                 | Transition to Valid On State  Measured from Scan at VIH  and ENABLE at VIL; Delay to  Valid Data Levels for CoL = 10pF  and one TTL Load or Valid Data  Currents for High Capacitance Loads |

| Output Delay Time<br>CASCADE ENABLE                                                               | toce         | -         | 10            | ns                 | Negative Transition from Scan at VIL and ST5 of Scan Counter or Positive Transition From SCAN RESET/LOAD at VIL to Valid Data Levels for CoL = 12pF and one TTL Load                        |

<sup>\*</sup>Input has internal pull-up resistor to VDD

\*\* Inputs have internal pull-down resistor to Vss

FIGURE 3A. SCAN COUNTER & DECODER OUTPUTS TIMING DIAGRAM FOR LS7060C

FIGURE 4. COUNTER TIMING DIAGRAM

FIGURE 5. ILLUSTRATION OF A 3 DEVICE CASCADE

FIGURE 6. TIMING DIAGRAM FOR THE 3 DEVICE CASCADE

FIGURE 7. SYNCHRONIZING INHIBIT WITH COUNT PULSES

# FIGURE 8. APPLICATION EXAMPLE: HIGH SPEED DIFFERENTIAL ENERGY ANALYZER

NOTE: The processor subtracts counts from successive counters to determine the differential energy spectrum

The information included herein is believed to be accurate and reliable. However, LSI Computer Systems, Inc. assumes no responsibilities for inaccuracies, nor for any infringements of patent rights of others which may result from its use.