# GDC21D003 (VSB Receiver)

# Version 1.0

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by Hyundai for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Hyundai or others.

These Hyundai products are intended for usage in general electronic equipment (office equipment, communication equipment, measuring equipment, domestic electrification, etc.).

Please make sure that you consult with us before you use these Hyundai products in equipment which require high quality and / or reliability, and in equipment which could have major impact to the welfare of human life (atomic energy control, airplane, spaceship, traffic signal, combustion control, all types of safety devices, etc.). Hyundai cannot accept liability to any damage which may occur in case these Hyundai products were used in the mentioned equipment without prior consultation with Hyundai.

Copyright 1999 Hyundai Micro Electronics Co.,Ltd.

All Rights Reserved

# **TABLE OF CONTENTS**

| 1. General Description                          | 8  |

|-------------------------------------------------|----|

| 2. Features                                     | 8  |

| 3. Internal Block Diagram                       | 11 |

| 4. Pin Description                              | 11 |

| 4.1 Pin Configuration                           |    |

| 4.2 Pin Description                             |    |

| 4.3 Pin Assignment                              |    |

| 5. I <sup>2</sup> C Bus I/F & Registers         | 17 |

| 5.1 I <sup>2</sup> C Bus I/F Description        | 17 |

| 5.1.1 Write Operation                           | 17 |

| 5.1.2 Read Operation                            | 17 |

| 5.2 I <sup>2</sup> C Bus Register Configuration | 18 |

| 5.3 I <sup>2</sup> C Bus Register Description   | 20 |

| 6. Functional Description                       | 29 |

| 6.1 ADC                                         | 29 |

| 6.1.1 Electrical Characteristics                |    |

| 6.1.2 Timing Diagram                            |    |

| 6.1.3 Application Circuits                      |    |

| 6.2 Clock Divider                               |    |

| 6.3 Synchronizer                                | 36 |

| 6.3.1 Input Control                             |    |

| 6.3.2 DC Reduction                              |    |

| 6.3.3 Auto Gain Control(AGC)                    | 39 |

| 6.3.4 Polarity Correction                       | 40 |

| 6.3.5 Data Segment Sync Recovery                |    |

| 6.3.6 Polarity Decision                         | 42 |

| 6.3.7 Timing Recovery                           | 43 |

| 6.3.8 Field Sync Recovery                       | 46 |

| 6.3.9 VSB Mode Detect                           | 47 |

| 6.3.10 NTSC Rejection                           | 48 |

| 6.4 Equalizer                                   |    |

| 6.4.1 Block Diagram                             |    |

| 6.4.2 Training/Data Mode Equalization           | 51 |

| 6.4.3 Error Estimation                          |    |

| 6.4.4 Adaptive Filter                           | 53 |

| 6.4.5 Equalizer Clock Scheme                    |    |

| 6.4.6 f C Bus I/F                               |    |

| 6.4.7 Coefficient Reading/Writing               | 56 |

|            | 6.5 Phase Tracker                                            |    |  |  |  |  |

|------------|--------------------------------------------------------------|----|--|--|--|--|

|            | 6.5.1 Error Detection                                        |    |  |  |  |  |

|            | 6.5.2 Gain & Offset Loop                                     |    |  |  |  |  |

|            | 6.5.3 Phase Loop                                             |    |  |  |  |  |

|            | 6.5.4 I2C Bus I/F                                            |    |  |  |  |  |

|            | 6.6 Channel Decoder                                          |    |  |  |  |  |

|            | 6.6.2 Segment Sync Suspension                                |    |  |  |  |  |

|            | 6.6.3 Viterbi Decoder                                        |    |  |  |  |  |

|            | 6.6.4 Symbol-to-Byte Converter                               |    |  |  |  |  |

|            | 6.6.5 Convolutional Deinterleaver                            |    |  |  |  |  |

|            | 6.6.6 Reed-Solomon Decoder                                   |    |  |  |  |  |

|            | 6.6.7 Data Derandomizer                                      |    |  |  |  |  |

|            | 6.6.8 I/F to Transport Demultiplexer                         | 67 |  |  |  |  |

|            | 6.7 PLL                                                      |    |  |  |  |  |

| _          | Floring Observatories                                        | 7. |  |  |  |  |

| <i>i</i> . | Electrical Characteristics                                   |    |  |  |  |  |

| 8.         | Package Dimensions                                           | 77 |  |  |  |  |

| n          | Application Notes                                            | 70 |  |  |  |  |

| <b>J</b> . | Application Notes                                            |    |  |  |  |  |

|            |                                                              |    |  |  |  |  |

| ΕĮ         | gures                                                        |    |  |  |  |  |

|            | Figure 3.1 Functional Block Diagram                          | 10 |  |  |  |  |

|            | Figure 5.1.1 I <sup>2</sup> C Write Operation Example        |    |  |  |  |  |

|            | Figure 5.1.2 I <sup>2</sup> C Read Operation Example         |    |  |  |  |  |

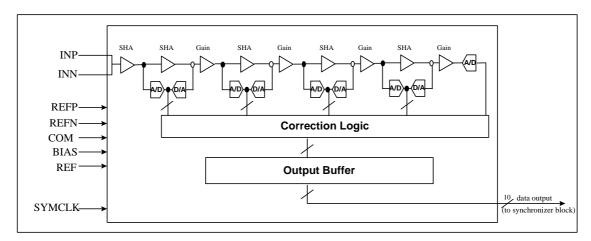

|            | Figure 6.1.1 The Block Diagram of ADC                        |    |  |  |  |  |

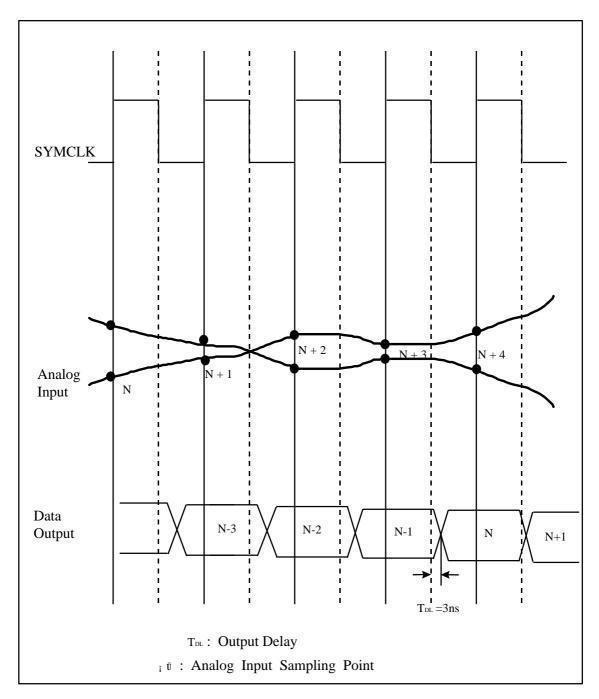

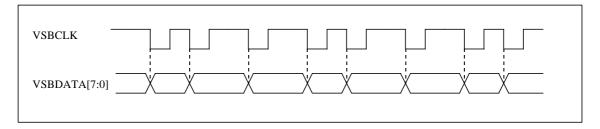

|            | Figure 6.1.2 Timing Diagram of ADC                           | 32 |  |  |  |  |

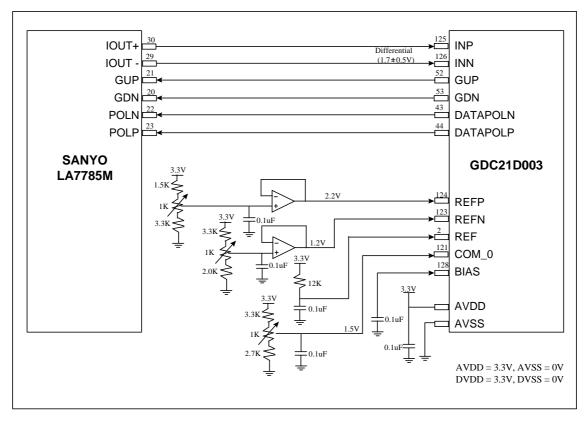

|            | Figure 6.1.3 ADC Application Circuit                         |    |  |  |  |  |

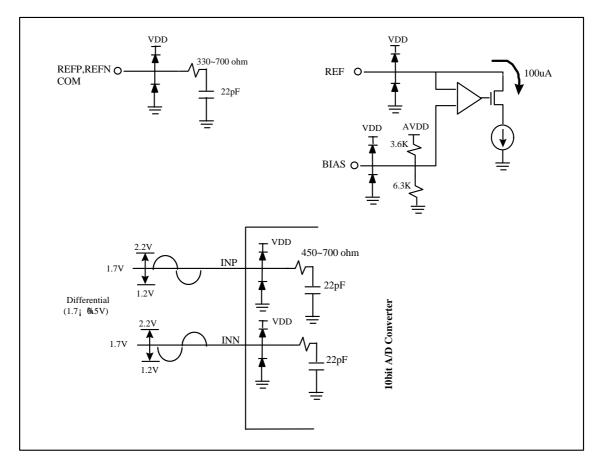

|            | Figure 6.1.4 Equivalent Circuits                             |    |  |  |  |  |

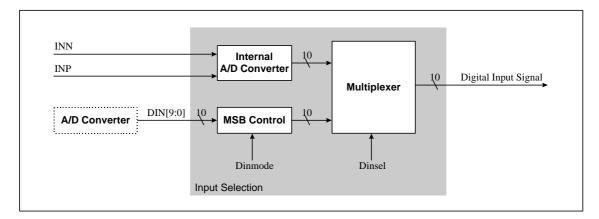

|            | Figure 6.3.1 The Block Diagram of Input Selection            |    |  |  |  |  |

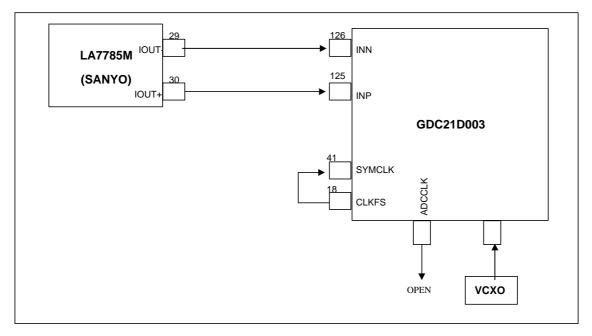

|            | Figure 6.3.2 Digital Input Setting Up & Chip I/F Circuit(1)  |    |  |  |  |  |

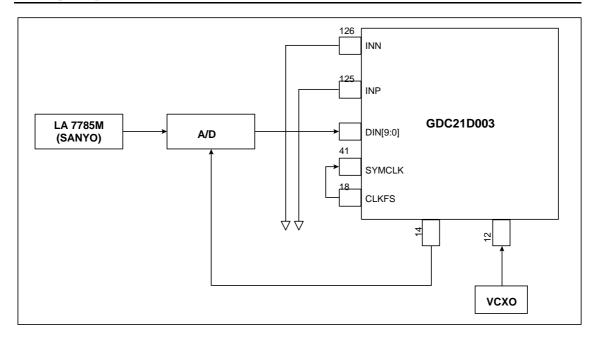

|            | Figure 6.3.3 Digital Input Setting Up & Chip I/F Circuit(2)  |    |  |  |  |  |

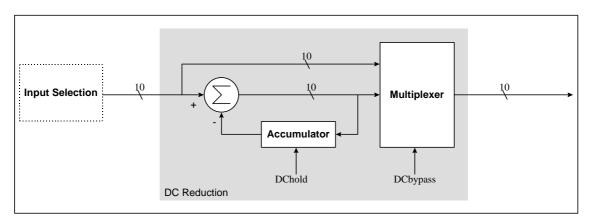

|            | Figure 6.3.4 The Block Diagram of DC Reduction               |    |  |  |  |  |

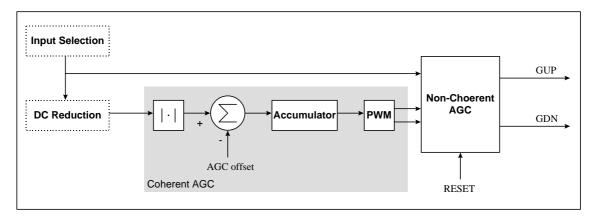

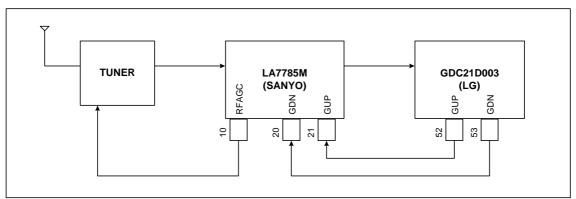

|            | Figure 6.3.5 The Block Diagram of AGC                        | 40 |  |  |  |  |

|            | Figure 6.3.6 AGC Signal I/F for DTV System                   | 40 |  |  |  |  |

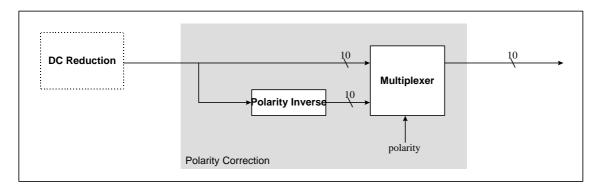

|            | Figure 6.3.7 The Block Diagram of Polarity Correction        | 41 |  |  |  |  |

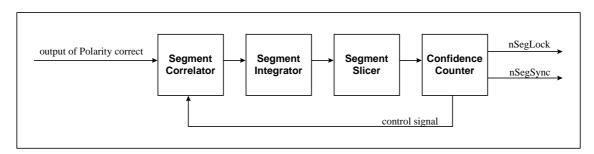

|            | Figure 6.3.8 The Block Diagram of Data Segment Sync Recovery | 41 |  |  |  |  |

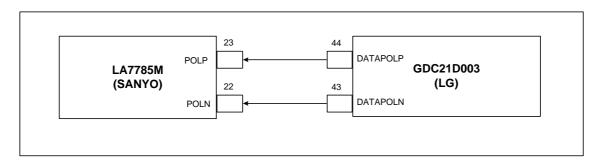

|            | Figure 6.3.9 Polarity signal I/F Circuit                     |    |  |  |  |  |

|            | Figure 6.3.10 Timing Recovery Block                          |    |  |  |  |  |

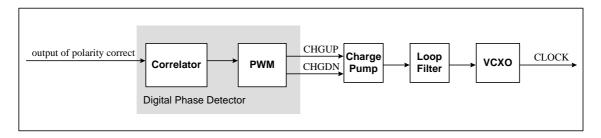

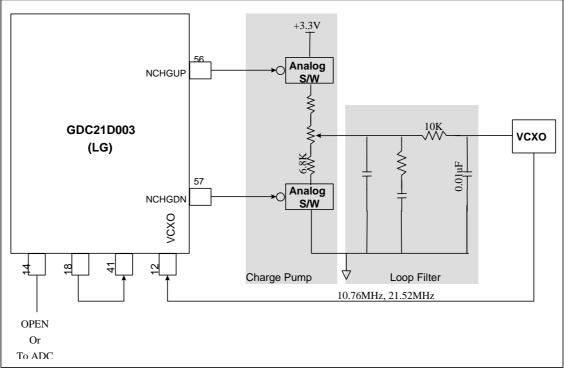

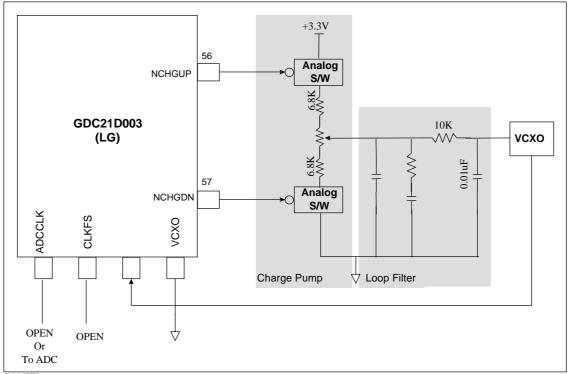

|            | Figure 6.3.11 Timing Recovery I/F Circuit(1)                 | 44 |  |  |  |  |

|            | Figure 6.3.12 Timing Recovery I/F Circuit(2)                 |    |  |  |  |  |

|            | Figure 6.3.13 Field Sync Structure                           |    |  |  |  |  |

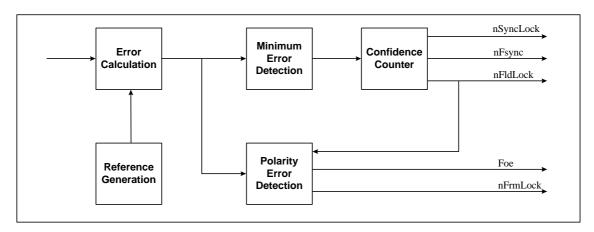

|            | Figure 6.3.14 The Block Diagram of Field Sync Recovery       |    |  |  |  |  |

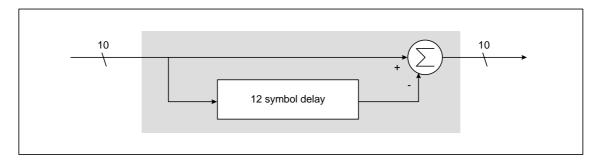

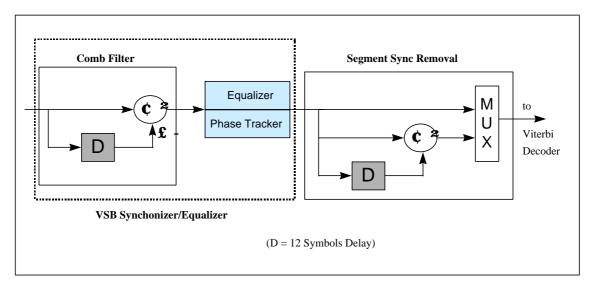

|            | Figure 6.3.15 Comb Filter Block                              |    |  |  |  |  |

|            | igure 0.5.15 Comb i iller block                              |    |  |  |  |  |

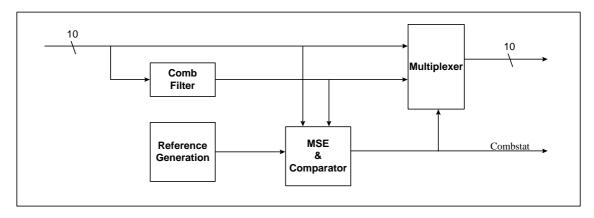

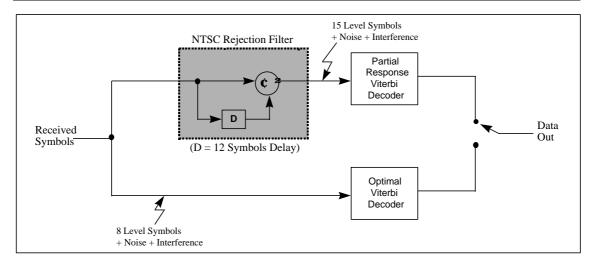

| Figure 6.3.16 | The Block Diagram of NTSC Rejection                             | 49       |

|---------------|-----------------------------------------------------------------|----------|

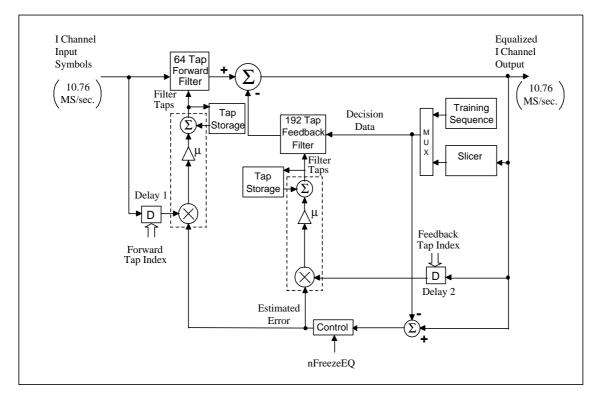

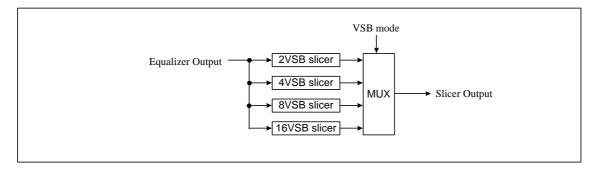

| Figure 6.4.1  | Channel Equalizer                                               | 50       |

|               | VSB Slicer                                                      |          |

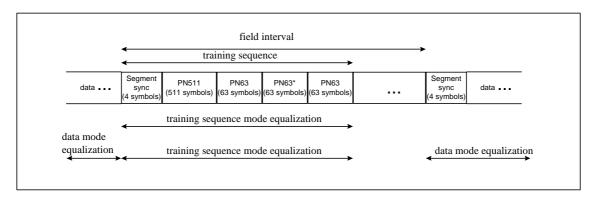

| Figure 6.4.3  | Training/Data Equalization                                      | 51       |

|               | VSB Slice Level                                                 |          |

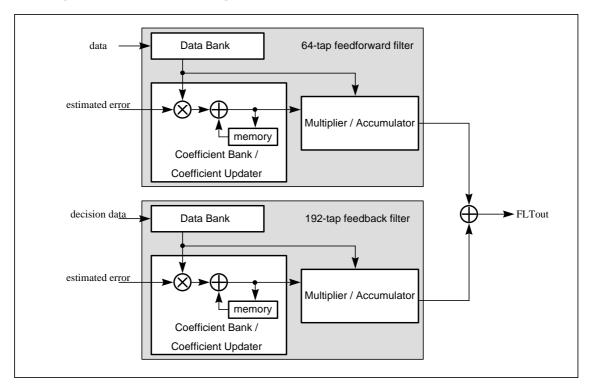

| Figure 6.4.5  | Coefficient Update Filter                                       | 53       |

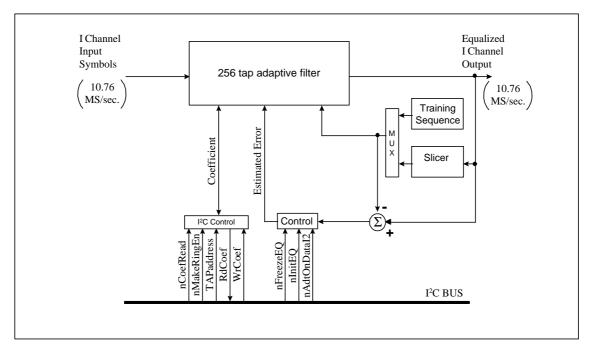

|               | I <sup>2</sup> C Bus I/F                                        |          |

| •             | Phase Tracker                                                   |          |

|               | Error Detection                                                 |          |

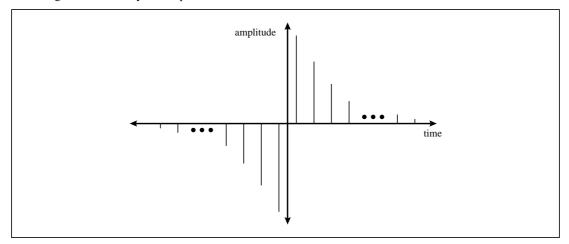

|               | Coefficients of Hilbert Transform Filter                        | 58       |

|               | Complex Multiplier                                              |          |

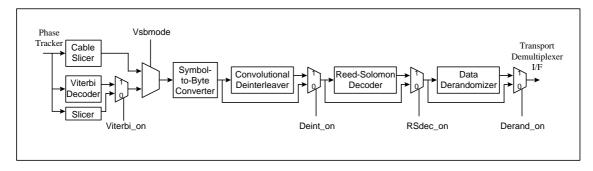

|               | Block Diagram of Channel Decoder                                |          |

|               | 12-Symbol Intrasegment Deinterleaver                            |          |

|               | Segment Sync Suspension                                         |          |

|               | Viterbi Decoding with and without NTSC Rejection Filter         |          |

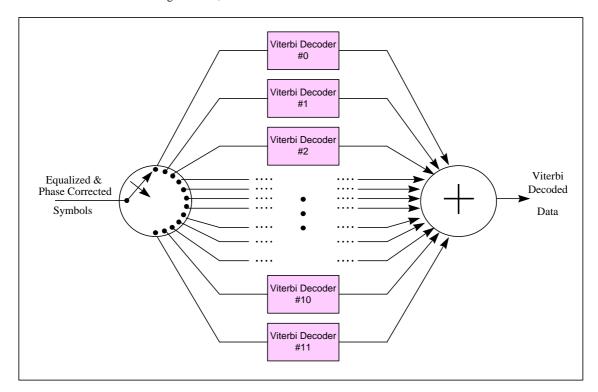

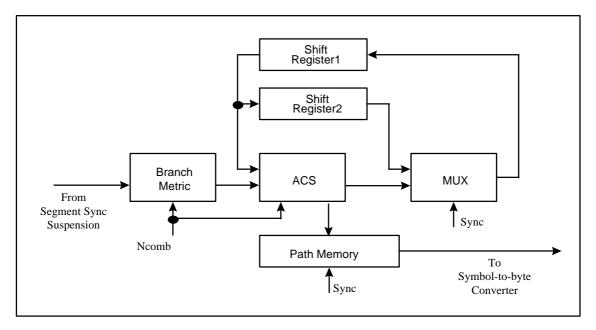

|               | Internal Block Diagram of Viterbi Decoder                       |          |

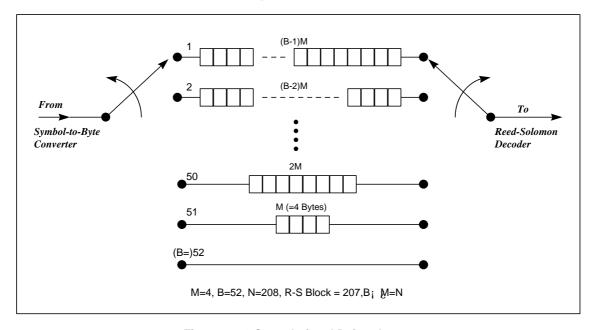

|               | Convolutional Deinterleaver                                     |          |

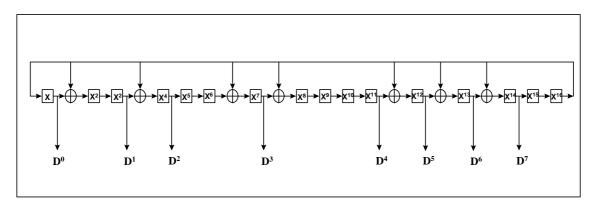

|               | Derandomizer Polynomial                                         | 66       |

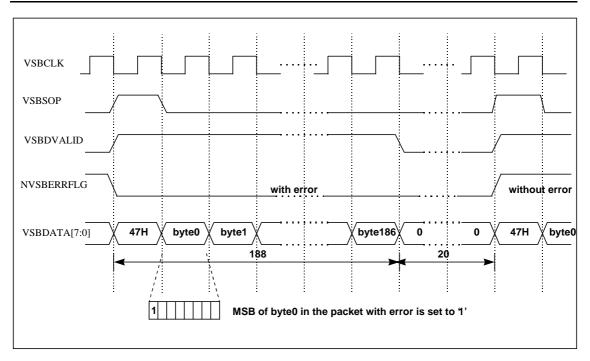

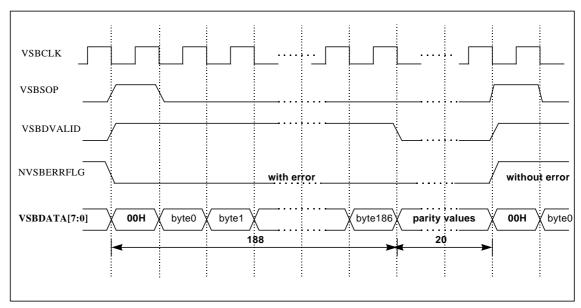

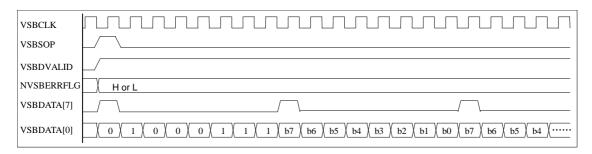

|               | I/F to Transport Demultiplexer when Register64[7:0] is set to   |          |

|               | Default Value                                                   | 68       |

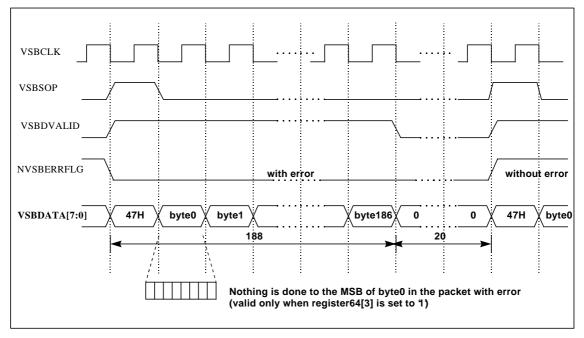

|               | I/F to Transport Demultiplexer when Register64[3] (Derand_on)   |          |

| į:            | s set to '0'                                                    | 69       |

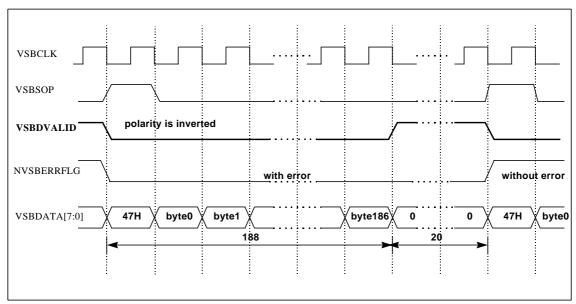

|               | I/F to Transport Demultiplexer when Register64[2](Errorflg_ins) |          |

|               | s set to '0'                                                    | 69       |

|               | /F to Transport Demultiplexer when Register64[1](Vsbdvalid_pol) |          |

|               | s set to 'O'                                                    | 70       |

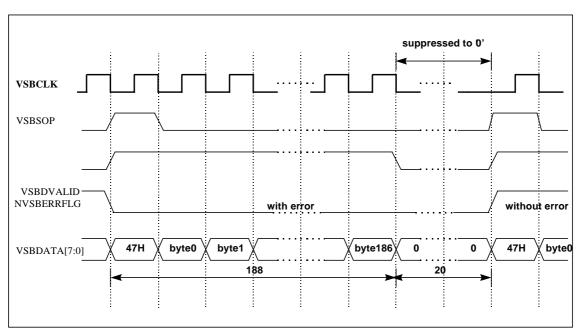

|               | I/F to Transport Demultiplexer when Register64[0](Vsbclk_sup)   |          |

|               | s set to '0'                                                    |          |

|               | I/F to Transport Demultiplexer(MMDS 8VSB Mode)                  |          |

|               | I/F to Transport Demultiplexer at Serial Output Mode            | /1       |

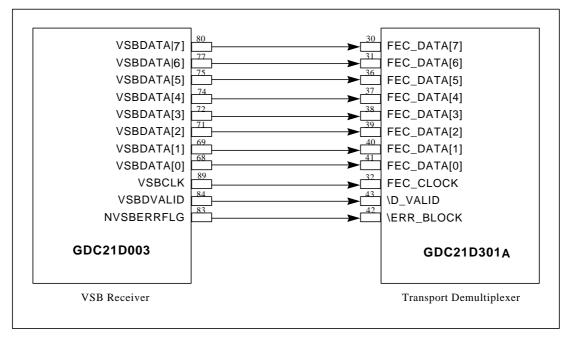

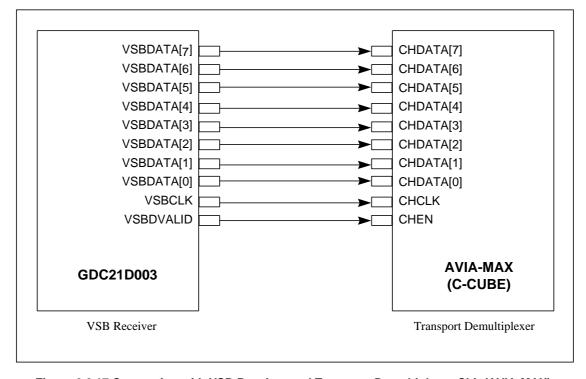

|               | Connection with VSB Receiver and Transport Demultiplexer        | 7.       |

|               | Chip(GDC21D301A)                                                | / 2      |

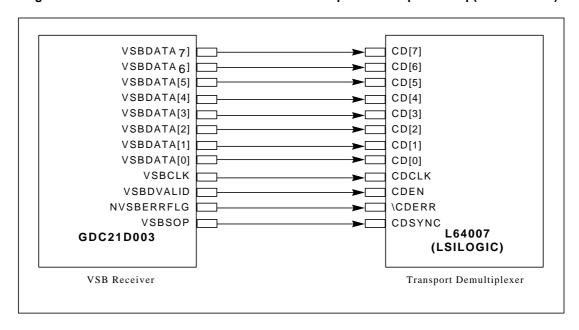

|               | Connection with VSB Receiver and Transport Demultiplexer        | 7.       |

|               | Chip(L64007)                                                    | / 2      |

|               | Connection with VSB Receiver and Transport Demultiplexer        | 7.       |

|               | Chip(AVIA-MAX)                                                  |          |

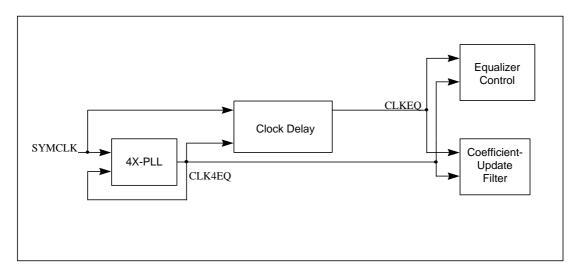

|               | Clock Scheme                                                    |          |

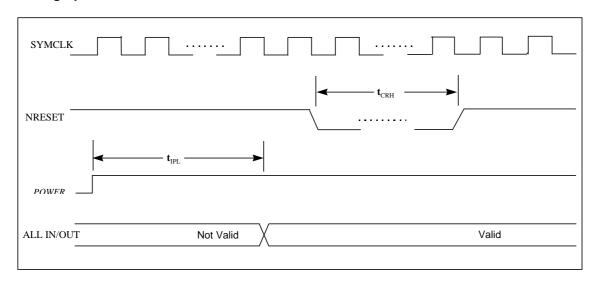

| Figure 7.1 (  | Clock Reset Stabilization Timing                                | ۰۰۰۰ / ۱ |

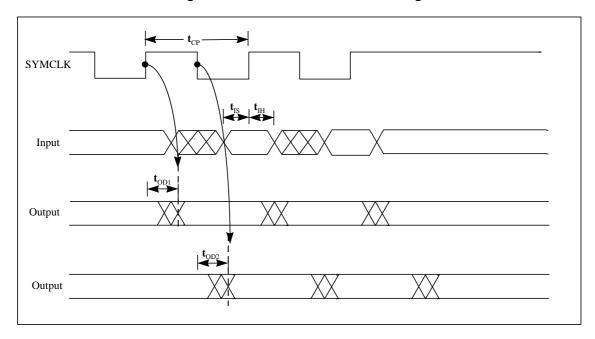

|               | nput and Output Timing                                          |          |

| •             | Physical Dimensions                                             |          |

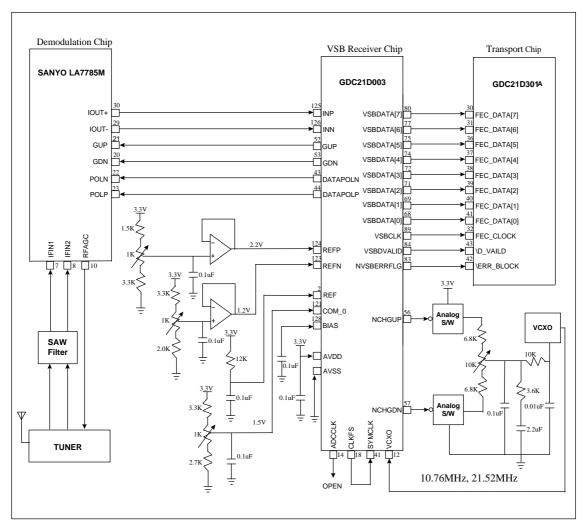

| Figure 9.1 \  | /SB Receiver Application Circuit                                | ۰۰۰۰ / ۶ |

# **Tables**

| Table 6.2.1 | Register Setting Up for Clock Divider                                     | 35 |

|-------------|---------------------------------------------------------------------------|----|

| Table 6.3.1 | Input Signal Path Setting Up                                              |    |

| Table 6.3.2 | DATAPOLP & DATAPOLN Output                                                |    |

| Table 6.3.3 | VSB Mode Data for Each VSB Mode                                           |    |

| Table 6.3.4 | VSB Mode Signal Control                                                   | 47 |

| Table 6.3.5 | Comb Filter Control through I <sup>2</sup> C Bus                          |    |

| Table 6.4.1 | Contents of I <sup>2</sup> C Bus Register33 for Equalizer                 |    |

| Table 6.4.2 | Contents of I <sup>2</sup> C Bus Register33 for Filter Control            |    |

| Table 6.5.1 | Contents of I <sup>2</sup> C Bus Register33 for Phase Tracker             |    |

| Table 6.5.2 | Contents of I <sup>2</sup> C Bus Register33 for Gain Control              |    |

| Table 6.6.1 | Bypassed Sub-blocks by the Values of I <sup>2</sup> C Bus Register64      |    |

| Table 6.6.2 | Symbol-to-Byte Conversion                                                 |    |

| Table 6.6.3 | I <sup>2</sup> C Register64 Flags controlling Transport Demultiplexer I/F |    |

#### **GDC21D003**

#### 1. General Description

The VSB Receiver(GDC21D003) is an ATSC compliant single chip communications device that synchronizes, equalizes, and corrects errors of ATSC 8/16 VSB and MMDS (Multichannel Multipoint Distribution System) 2/4/8/16 VSB modulated signal.

The on-chip 10-bit 10.76Msps Analog-to-Digital Converter has an input sample-and-hold amplifier. By implementing a multistage pipelined architecture with output correction logic, the ADC offers accurate performance and guarantees no missing codes over the full operating temperature. Clock divider divides output clock of external VCXO and generates symbol clock (CLKFS) and ADCCLK. The CLKFS has 10.76MHz frequency as symbol frequency used in DTV transmitter, ADCCLK is used for external A/D converter. At this time, if you use digital signal as input of chip, CLKFS or ADCCLK are used for external A/D converter clock.

Synchronizer removes DC entered from transmitter and DC generated by analog circuit used in receiver. Also it checks gain of input signal and sends it to demodulator, detects polarity, and corrects it. It recovers Data Segment Sync period and Field Sync period entered from transmitter. It detects VSB mode of current input signal and removes NTSC co-channel interference in channel. Equalizer corrects linear distortion created during transmission. It uses Least-Mean-Square algorithm and has decision feedback equalizer structure. It uses adaptive filter having coefficient update structure consisted of multiplier, adder, and memory structure in every tap.

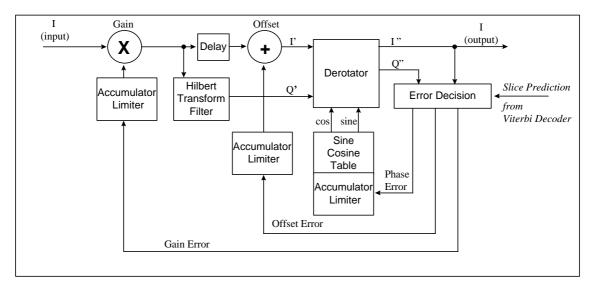

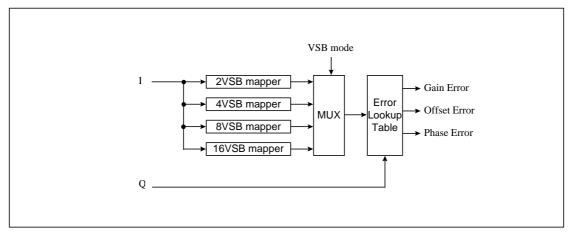

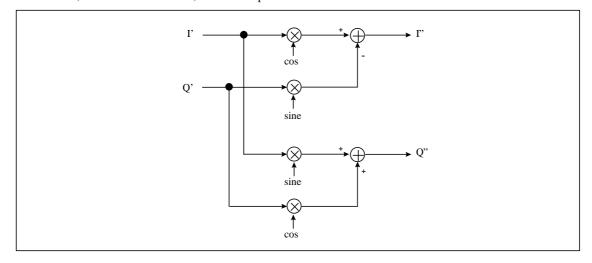

Phase Tracker compensates phase distortion due to phase noise and it consists of gain correction loop for gain error, offset correction loop for offset error, and phase correction loop for phase error.

Channel Decoder consists of Viterbi Decoder, Convolutional Deinterleaver, Reed-Solomon Decoder, Data Derandomizer, and etc. It decodes ATSC 8/16 VSB signal and MMDS 2/4/8/16 VSB signal. Also it has internal segment error counter that send out the number of segment errors per second and offers tri-state parallel/serial Transport Demultiplexer interface.

#### 2. Features

#### **General features**

- ATSC compliant 8/16 VSB receiver

- MMDS 2/4/8/16 VSB receiver

- SNR threshold 14.9 dB on AWGN channel

- Tri-state parallel/serial MPEG-2 transport interface

- Supports I<sup>2</sup>C bus interface

- Boundary Scan Test circuit complies with IEEE Std. 1149.1

ID-Code = 0D0031C1

- Operating voltage: 3.3V

- 0.35μm CMOS technology

- 128 pin HQFP package

#### ADC

• Resolution : 10bits ( $\leq \pm \frac{1}{2}$  LSB DNL error)

• Sampling rate: 10.76 Msps

• Differential input range :  $2Vpp(1.7 \pm 0.5V)$  differential)

#### **Clock Divider**

- Generates symbol clock(10.76MHz)

- Uses one of two VCXOs, fs(10.76MHz) and 2fs(21.52MHz) as input

#### **Synchronizer**

- Input control

- DC reduction and polarity correction

- Correction of polarity ambiguity caused by FPLL

- Non-coherent and coherent automatic gain control (AGC)

- Data Segment Sync and Field Sync recovery

- Timing recovery

- Polarity decision

- Polarity decision after Data Segment Sync is locked

- VSB mode detection

- Comb control

- Comb filter for the rejection of NTSC co-channel interface

#### **Equalizer**

- Decision feedback equalizer

- Supports training sequence and blind equalization

- Concurrent coefficients update in symbol time

- Available 3 different step-size

- Capability of reading equalizer coefficients

- $\bullet$  Ghost cancellation in the range from -2.86  $\mu s$  to 20.76  $\mu s$

#### **Phase Tracker**

- Intelligent loop control according to noise environment

- Phase tracking from -60° to 60° with resolution of 0.004 degree

- Phase, offset, and gain correction at a time

#### **Channel Decoder**

- Concatenated Viterbi/Reed-Solomon Decoder with Deinterleaver and Derandomizer

- Internal segment error counter

- Tri-state parallel/serial MPEG-2 Transport Demultiplexer interface

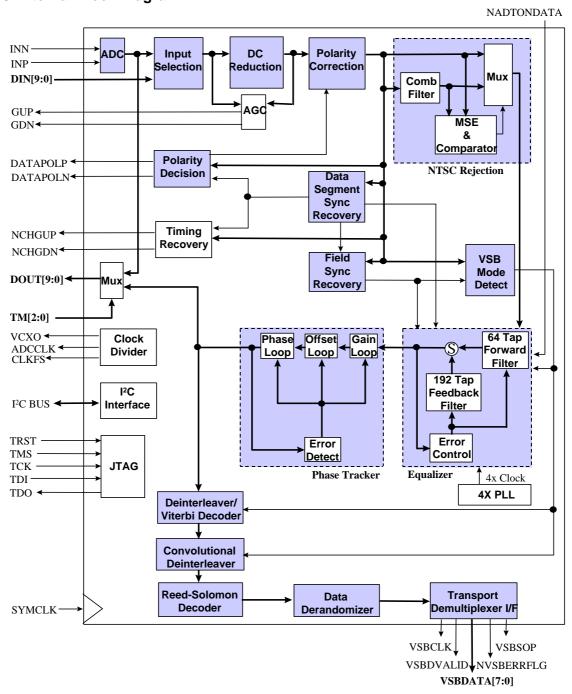

# 3. Internal Block Diagram

Figure 3.1 Functional Block Diagram

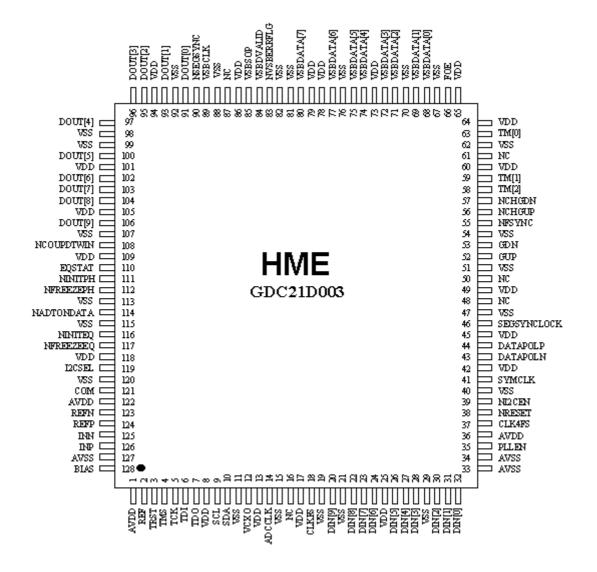

### 4. Pin Description

#### 4.1 Pin Configuration

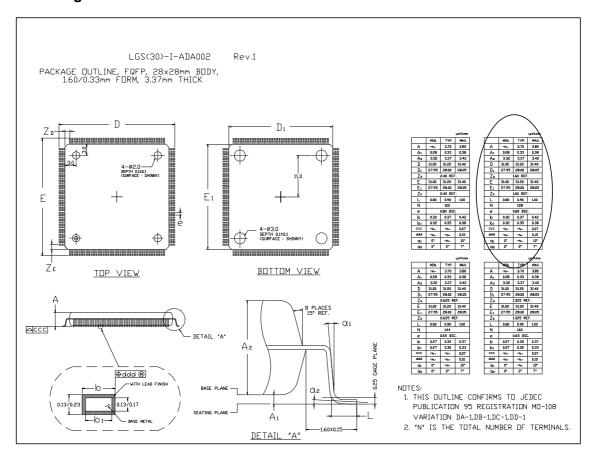

<sup>\*128</sup> PIN HQFP, 28X28 mm BODY, 1.60/0.33 mm FORM, 3.37mm THICK, 0.8 mm PITCH

# **4.2 Pin Description**

# Clock/Reset; 6 Pins

| PIN | NAME   | TYPE | DESCRIPTION                                             |

|-----|--------|------|---------------------------------------------------------|

| 38  | NRESET | I    | System reset(active low); This signal should be         |

|     |        |      | activated on channel change or power on.                |

| 12  | VCXO   | I    | Clock input generated in VCXO; This pin can be          |

|     |        |      | connected to one of two VCXOs whose output              |

|     |        |      | frequencies are fs(10.76MHz) and 2fs(21.52MHz).         |

| 14  | ADCCLK | О    | Clock for Off-chip ADC(21.52MHz or 10.76MHz);           |

|     |        |      | This clock is generated by dividing VCXO input signal.  |

| 18  | CLKFS  | 0    | System clock; This clock is generated from dividing     |

|     |        |      | VCXO input signal. Its frequency is the same of symbol  |

|     |        |      | rate(10.76MHz).                                         |

| 37  | CLK4FS | I/O  | Test clock/4x symbol clock;                             |

|     |        |      | When PLLEN(pin35) input is set to '1', this pin is used |

|     |        |      | as 4x symbol clock output.                              |

|     |        |      | When PLLEN(pin35) input is set to '0', this pin is used |

|     |        |      | as test clock(43.04MHz) input.                          |

| 41  | SYMCLK | I    | System clock input(10.76MHz)                            |

# A/D Converters; 7 Pins

| PIN | NAME | TYPE | DESCRIPTION                         |                    |

|-----|------|------|-------------------------------------|--------------------|

| 2   | REF  | I    | Bias register for internal ADC;     | This pin should be |

|     |      |      | connected to AVDD(3.3V) via 12k of  | hm register.       |

| 121 | COM  | I    | Common voltage(1.5V)                |                    |

| 123 | REFN | I    | Reference voltage(bottom: 1.2V)     |                    |

| 124 | REFP | I    | Reference voltage(top: 2.2V)        |                    |

| 125 | INN  | I    | Analog data input(negative)         | $1.65 \pm 0.5 V$   |

| 126 | INP  | I    | Analog data input(positive)         | differential       |

| 128 | BIAS | I    | Bias input(2V typical) for On-ch    | ip ADC; This pin   |

|     |      |      | should be connected to AVSS via 0.1 | μF capacitor.      |

Sync Recovery; 20 Pins

| PIN               | NAME        | TYPE    | DESCRIPTION                                                    |

|-------------------|-------------|---------|----------------------------------------------------------------|

| 20, 22-24, 26-28, | DIN[9:0]    | I       | Digital data input; This data input comes from                 |

| 30-32             | Bit9: MSB   |         | external ADC.                                                  |

| 44                | DATAPOLP    | I/O*    | Polarity signal of input data(active high); If this            |

|                   |             |         | output value is '1', it means the plus polarity.               |

|                   |             |         | This signal should be applied to demodulator IC.               |

| 43                | DATAPOLN    | I/O*    | Inverted polarity signal of input data(active high);           |

|                   |             |         | This signal should be applied to demodulator IC.               |

| 46                | SEGSYNCLOCK | I/O*    | Stability Indication of Data Segment Sync                      |

|                   |             |         | recovery(active high)                                          |

| 52                | GUP         | $I/O^*$ | Input data gain increasing signal(active high); This           |

|                   |             |         | signal should be applied to demodulator IC.                    |

| 53                | GDN         | $I/O^*$ | Input data gain decreasing signal(active high); This           |

|                   |             |         | signal should be applied to demodulator IC.                    |

| 55                | NFSYNC      | 0       | <b>Field Sync(active low);</b> If this output value is '0', it |

|                   |             |         | means Field Sync interval.                                     |

| 56                | NCHGUP      | 0       | Charging signal for charge pump in the timing                  |

|                   |             |         | recovery block(active low)                                     |

| 57                | NCHGDN      | 0       | Discharging signal for charge pump in the timing               |

|                   |             |         | recovery block(active low)                                     |

| 66                | FOE         | 0       | Field status indicator(active high); If this output value      |

|                   |             |         | is '1', it means inverted field.                               |

| 90                | NSEGSYNC    | 0       | Data Segment Sync(active low); If this output value is         |

|                   |             |         | '0', it means Data Segment Sync interval.                      |

(NOTE) \* These five I/O pins are used as input pin only for chip test.

# **Equalizer**; 6 Pins

| PIN | NAME       | TYPE | DESCRIPTION                                                       |

|-----|------------|------|-------------------------------------------------------------------|

| 35  | PLLEN      | I    | PLL enable(active high); This pin should be set to '1'.           |

| 108 | NCOUPDTWIN | 0    | Coefficient update window(active low); If this output             |

|     |            |      | value is '0', the Equalizer adapts its coefficients.              |

|     |            |      | Otherwise, it doesn't adapt its coefficients.                     |

| 110 | EQSTAT     | 0    | <b>Equalizer status;</b> If this output value is '1', the         |

|     |            |      | Equalizer is in normal status.                                    |

|     |            |      | Otherwise, the Equalizer has diverged.                            |

| 114 | NADTONDATA | I    | Data mode coefficient update(active low);                         |

|     |            |      | If this input is set to '0', the Equalizer adapts its             |

|     |            |      | coefficients during training sequence and data interval.          |

|     |            |      | Otherwise, the Equalizer adapts its coefficients during           |

|     |            |      | only training sequence interval.                                  |

| 116 | NINITEQ    | I    | <b>Equalizer initialization(active low);</b> If this input is set |

|     |            |      | to '0', the Equalizer is initialized.                             |

| 117 | NFREEZEEQ  | I    | <b>Equalizer freeze(active low);</b> If this input is set to '0', |

|     |            |      | the Equalizer coefficient does not be adapted.                    |

(NOTE) When I<sup>2</sup>C is enabled, operation is performed either using these pins or via I<sup>2</sup>C register, but when disabled, only these pins are used. If you want to control Equalizer fast, use these external input pins. Otherwise use I<sup>2</sup>C bus registers.

#### Phase Tracker; 2 Pins

| PIN | NAME      | TYPE | DESCRIPTION                                                       |

|-----|-----------|------|-------------------------------------------------------------------|

| 111 | NINITPH   | I    | Phase tracker initialization(active low); If this input           |

|     |           |      | is set to '0', the Phase Tracker is initialized.                  |

| 112 | NFREEZEPH | I    | <b>Phase tracker freeze(active low)</b> ; If this input is set to |

|     |           |      | '0', the Phase Tracker stops phase tracking                       |

(NOTE) When I<sup>2</sup>C is enabled, operation is performed either using these pins or via I<sup>2</sup>C register, but when disabled, only these pins are used. If you want to control Equalizer fast, use these external input pins. Otherwise use I<sup>2</sup>C bus registers.

#### **Channel Decoder**; 12 Pins

| PIN                   | NAME         | TYPE | DESCRIPTION                                           |

|-----------------------|--------------|------|-------------------------------------------------------|

| 68,69,71,72,74,75,77, | VSBDATA[7:0] | О    | Data output to transport multiplexer;                 |

| 80                    |              |      | VSBDATA[7]: Used as start bit indicator of a byte in  |

|                       |              |      | serial output mode.                                   |

|                       |              |      | VSBDATA[0]: Used as serial data output in serial      |

|                       | Bit7: MSB    |      | output mode.                                          |

| 83                    | NVSBERRFLG   | 0    | Packet error indication flag(active low); This output |

|                       |              |      | indicates whether the packet has error or not.        |

|                       |              |      | 0: with error                                         |

|                       |              |      | 1 : without error                                     |

| 84                    | VSBDVALID    | 0    | Valid data indication flag;                           |

|                       |              |      | 1: valid when register64[1](Vsbdvalid_pol = '1')      |

|                       |              |      | 0 :valid when register64[1](Vsbdvalid_pol = '0')      |

| 85                    | VSBSOP       | 0    | Start byte indicator of a packet                      |

| 89                    | VSBCLK       | 0    | Data clock of packet data                             |

#### I2C Bus Interface; 4 Pins

| PIN | NAME   | TYPE | DESCRIPTION                                                           |

|-----|--------|------|-----------------------------------------------------------------------|

| 9   | SCL    | I    | I <sup>2</sup> C bus serial clock input                               |

| 10  | SDA    | I/O  | I <sup>2</sup> C bus serial data input/output                         |

| 39  | NI2CEN | I    | I <sup>2</sup> C bus enable(active low); If this input is set to '0', |

|     |        |      | the chip is controlled by I <sup>2</sup> C bus.                       |

|     |        |      | Otherwise, stand alone mode.                                          |

| 119 | I2CSEL | I    | I <sup>2</sup> C bus device address selection;                        |

|     |        |      | 0: I <sup>2</sup> C device address is set to b"1011001".              |

|     |        |      | 1: I <sup>2</sup> C device address is set to b"0001110".              |

|     |        |      | (default value)                                                       |

#### **Boundary Scan Signal: 5 Pins**

| PIN | NAME | TYPE | DESCRIPTION                       |

|-----|------|------|-----------------------------------|

| 3   | TRST | I    | Boundary scan test reset          |

| 4   | TMS  | I    | Boundary scan test mode selection |

| 5   | TCK  | I    | Boundary scan test clock          |

| 6   | TDI  | I    | Boundary scan test data input     |

| 7   | TDO  | 0    | Boundary scan test data output    |

# Miscellaneous; 18 Pins

| ,                   |           |      |                                                  |

|---------------------|-----------|------|--------------------------------------------------|

| PIN                 | NAME      | TYPE | DESCRIPTION                                      |

| 58,59,63            | TM[2:0]   | I    | Tmode;                                           |

|                     |           |      | "111": normal mode with ADC output               |

|                     |           |      | "011": normal mode with Phase Tracker output     |

|                     | Bit2: MSB |      | others : reserved for chip test                  |

| 91, 93, 95-97, 100, | DOUT[9:0] | 0    | Data output; Either ADC or Phase Tracker block   |

| 102-104, 106        | Bit9: MSB |      | output is selected by tmode as dout[9:0] output. |

| 16,48,50,61,87      | NC        |      | No connection                                    |

#### **Supply Voltages : 48 Pins**

| Supply Voltages , 40   |      | =>/== | DECORIDEION                             |

|------------------------|------|-------|-----------------------------------------|

| PIN                    | NAME | TYPE  | DESCRIPTION                             |

| 8, 13, 17, 25, 42, 45, | VDD  |       | Digital positive supply voltage(3.3V)   |

| 49,60,64,65,73,78,     |      |       |                                         |

| 79,86,94,101,105,      |      |       |                                         |

| 109,118                |      |       |                                         |

| 11,15,19,21,29,40,     | VSS  |       | Digital negative supply voltage(ground) |

| 47,51,54,62,67,70,     |      |       |                                         |

| 76,81,82,88,92,98      |      |       |                                         |

| 99,107,113,115         |      |       |                                         |

| 1,36,122               | AVDD |       | Analog positive supply voltage(3.3V)    |

| 33,34,120,127          | AVSS |       | Analog negative supply voltage(ground)  |

# 4.3 Pin Assignment

| PIN | NAME     | TYPE | PIN | NAME        | TYPE | PIN | NAME       | TYPE |

|-----|----------|------|-----|-------------|------|-----|------------|------|

| 1   | AVDD     |      | 44  | DATAPOLP    | I/O  | 87  | NC         |      |

| 2   | REF      | I    | 45  | VDD         |      | 88  | VSS        |      |

| 3   | TRST     | I    | 46  | SEGSYNCLOCK | I/O  | 89  | VSBCLK     | О    |

| 4   | TMS      | I    | 47  | VSS         |      | 90  | NSEGSYNC   | О    |

| 5   | TCK      | I    | 48  | NC          |      | 91  | DOUT[0]    | О    |

| 6   | TDI      | I    | 49  | VDD         |      | 92  | VSS        |      |

| 7   | TDO      | О    | 50  | NC          |      | 93  | DOUT[1]    | О    |

| 8   | VDD      |      | 51  | VSS         |      | 94  | VDD        |      |

| 9   | SCL      | I    | 52  | GUP         | I/O  | 95  | DOUT[2]    | О    |

| 10  | SDA      | I/O  | 53  | GDN         | I/O  | 96  | DOUT[3]    | О    |

| 11  | VSS      |      | 54  | VSS         |      | 97  | DOUT[4]    | О    |

| 12  | VCXO     | I    | 55  | NFSYNC      | 0    | 98  | VSS        |      |

| 13  | VDD      |      | 56  | NCHGUP      | 0    | 99  | VSS        |      |

| 14  | ADCCLK   | О    | 57  | NCHGDN      | 0    | 100 | DOUT[5]    | О    |

| 15  | VSS      |      | 58  | TM[2]       | I    | 101 | VDD        |      |

| 16  | NC       |      | 59  | TM[1]       | I    | 102 | DOUT[6]    | О    |

| 17  | VDD      |      | 60  | VDD         |      | 103 | DOUT[7]    | О    |

| 18  | CLKFS    | О    | 61  | NC          | İ    | 104 | DOUT[8]    | 0    |

| 19  | VSS      |      | 62  | VSS         |      | 105 | VDD        |      |

| 20  | DIN[9]   | I    | 63  | TM[0]       | I    | 106 | DOUT[9]    | О    |

| 21  | VSS      |      | 64  | VDD         |      | 107 | VSS        |      |

| 22  | DIN[8]   | I    | 65  | VDD         |      | 108 | NCOUPDTWIN | О    |

| 23  | DIN[7]   | I    | 66  | FOE         | 0    | 109 | VDD        |      |

| 24  | DIN[6]   | I    | 67  | VSS         |      | 110 | EQSTAT     | О    |

| 25  | VDD      |      | 68  | VSBDATA[0]  | 0    | 111 | NINITPH    | I    |

| 26  | DIN[5]   | I    | 69  | VSBDATA[1]  | 0    | 112 | NFREEZEPH  | I    |

| 27  | DIN[4]   | I    | 70  | VSS         |      | 113 | VSS        |      |

| 28  | DIN[3]   | I    | 71  | VSBDATA[2]  | 0    | 114 | NADTONDATA | I    |

| 29  | VSS      |      | 72  | VSBDATA[3]  | 0    | 115 | VSS        |      |

| 30  | DIN[2]   | I    | 73  | VDD         |      | 116 | NINITEQ    | I    |

| 31  | DIN[1]   | I    | 74  | VSBDATA[4]  | 0    | 117 | NFREEZEEQ  | I    |

| 32  | DIN[0]   | I    | 75  | VSBDATA[5]  | 0    | 118 | VDD        |      |

| 33  | AVSS     |      | 76  | VSS         |      | 119 | I2CSEL     | I    |

| 34  | AVSS     |      | 77  | VSBDATA[6]  | 0    | 120 | AVSS       |      |

| 35  | PLLEN    | I    | 78  | VDD         |      | 121 | COM        | I    |

| 36  | AVDD     |      | 79  | VDD         |      | 122 | AVDD       |      |

| 37  | CLK4FS   | I/O  | 80  | VSBDATA[7]  | О    | 123 | REFN       | I    |

| 38  | NRESET   | I    | 81  | VSS         |      | 124 | REFP       | I    |

| 39  | NI2CEN   | I    | 82  | VSS         |      | 125 | INN        | I    |

| 40  | VSS      |      | 83  | NVSBERRFLG  | О    | 126 | INP        | I    |

| 41  | SYMCLK   | I    | 84  | VSBDVALID   | О    | 127 | AVSS       |      |

| 42  | VDD      |      | 85  | VSBSOP      | О    | 128 | BIAS       | I    |

| 43  | DATAPOLN | I/O  | 86  | VDD         |      |     |            |      |

# 5. I<sup>2</sup>C Bus I/F & Registers

#### 5.1 I2C Bus I/F Description

When NI<sup>2</sup>CEN pin is set to Low, the GDC21D003 may be controlled over I2C bus interface which consists of two signals, serial data(SDA) and serial clock(SCL) that can control a large number of devices on a common bus. The Device Address of this chip is "1011001"b or "0001110"b which can be selected by I<sup>2</sup>CSEL pin. The data on the I<sup>2</sup>C bus can be transferred at a rate up to 100 kbits/s in the standard mode, or up to 400 kbits/s in the fast mode. In the GDC21D003, SDA is bi-directional but SCL is only used as input, since the IC can only act as a slave device. In normal operations, data transfers are clocked by the SCL signal with one SCL pulse per data bit, and SDA is required to be stable during the high period of the SCL signal. Transitions of SDA while SCL is high are performed by the interface signals of start(S), stop(P), and repeated start(Sr) conditions. The start condition is defined as a high-to-low transition of SDA while SCL is high, and the stop condition is the low-to-high transition of SDA while SCL is high. Data transmissions are always proceeded by a start condition and ended with a stop condition, and may contain repeated starts within the transmission to alter the direction of the data flow or to change register base addresses. All data transmission

operations occur in 8-bit blocks with each block acknowledged through the designated receiver by the generation of an acknowledge signal(A). This signal is generated on the ninth pulse of SCL for each transferred block.

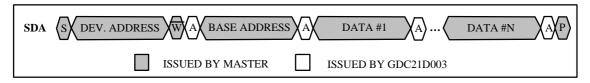

#### 5.1.1 Write Operation

In order to perform a write operation, the interface is accessed in following manner. The master first generates a start condition by pulling SDA down to low while SCL is high. The master next sends a 7bit Device Address and a one bit R/W signal, and each slave compares this address with its own address and acknowledges the master if the device address sent by the master coincides with that of its own. If not so, the slave ignores the rest of current data being transmitted. If the master is writing to the GDC21D003, the chip interprets the next data byte as a register base address. This is used as the location to store the next received data byte. This base address increases as each data byte is received allowing a contiguous register block to be programmed in a single transmission. Noncontiguous blocks may be programmed in multiple transmissions or by using a repeated start condition, which allows a new Device Address and register base address to be specified without the master giving up control of the bus. The transmission is terminated with the receipt of a stop condition.

Figure 5.1.1 I<sup>2</sup>C Write Operation Example

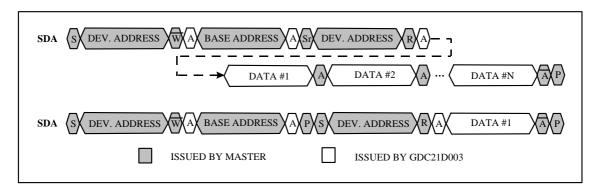

## 5.1.2 Read Operation

Read operation is performed in a manner similar to write operation. The master first generates a start condition and then sends the Device Address and R/W signal. The master will acknowledge each byte as receiving if it desires another byte to be sent. At the end of the transmission, the master will not acknowledge the slave and will then be

free to generate a stop condition to terminate the transmission. The base address register contents are used to determine the location to be read, and once again this address will be increased with each successive read. Because the base address register can only be programmed through a write operation, a general read will require two accesses or a single access with a embedded repeated start to change the direction of transmission.

Figure 5.1.2 I<sup>2</sup>C Read Operation Example

# 5.2 I<sup>2</sup>C Bus Register Configuration

| Add  |             |             |              | DATA              | BYTE         |             |              |             | Initial  |

|------|-------------|-------------|--------------|-------------------|--------------|-------------|--------------|-------------|----------|

| ress | D7          | D6          | D5           | D4                | D3           | D2          | D1           | D0          | Value    |

| 0    | Dinmode     | Dinsel      | ADCCLKSEL    | ADCCLKPH          | DCbypass     | DChold      | AGChold      | AGCoffsetW  | 11110000 |

| 1    |             |             | l .          | AGCoffs           | set[7:0]     |             |              |             | 01100000 |

| 2    |             | VSBmod[2:0] |              |                   |              | " 10010 "   |              |             | 10110010 |

| 3    |             |             |              | " 11001           | 1000 "       |             |              |             | 11001000 |

| 4    | " 0         | 0 "         | PolarityW    | Polarity          | " 1          | 10 "        | nSyncLockrst | VSBmodW     | 00001000 |

| 5    | VCXOS       | EL[1:0]     | nCombW       | nComb             | Combouthalf  | NoComb      | gain[1:0]    | "0"         | 00011010 |

| 6    |             |             |              | DCvalu            | ie[7:0]      |             |              |             |          |

| 7    |             |             |              | X                 |              |             |              |             |          |

| 8    | X           | nSyncLock   | nSegLock     | Combstat          | nVSBmodstart | DATAPOLN    | nPolLock     | nFldLock    |          |

| 9    |             |             |              | X                 |              |             |              |             |          |

| 10   | Σ           | ζ           | nFrmLock     | nVSBLock          |              | " 01        | 01 "         |             | XXXX0101 |

| 11   |             |             | X            |                   |              |             | VSBmodA[2:0] |             |          |

| 12   |             |             |              | X                 |              |             |              |             |          |

| 13   |             |             |              | X                 |              |             |              |             |          |

| 14   |             |             |              | X                 |              |             |              | nCombLock   |          |

| 15   |             |             |              | X                 |              |             |              |             |          |

| 32   | nSyncLockPH | U           | U            | nCombPH           | nSyncLockEQ  | nDSsycnEQ   | nFsyncEQ     | nCombEQ     |          |

| 33   | nFreezePHI2 | InitPHI2    |              | odeIN[1:0]        | nFreezeEQI2  | InitEQI2    | STEPsiz      | eIN[1:0]    | 10001011 |

| 34   | EQmodeIN    | TRAINme     | odeIN[1:0]   | CombOutHalfI<br>N | nDSadptIN    | nEQoutIN    | FLTtes       | tIN[1:0]    | 00010000 |

| 35   | nIIR16ONIN  | nIIRONIN    | nAdtOnDataI2 | BLIDmod           | leIN[1:0]    | nRingENIN   | nCoefRead    | nMakeRingIN | 10100101 |

| 36   | Predicl     | N[1:0]      | 1            | LoopgainIN[2:0]   |              | nOPERmodeIN | nDNgainIN    | nDNgainThIN | 11000011 |

| 37   |             |             |              | TapAddr           | ess[7:0]     |             |              |             | 00000000 |

| Add  |         |            |              | DATA             | BYTE      |               |               |            | Initial  |

|------|---------|------------|--------------|------------------|-----------|---------------|---------------|------------|----------|

| ress | D7      | D6         | D5           | D4               | D3        | D2            | D1            | D0         | Value    |

| 38   |         | WrCo       | ef[11:8]     |                  |           | RdCo          | ef[11:8]      |            | 0000XXXX |

| 39   |         |            |              | WrCoef           | f[7::0]   |               |               |            | 00000000 |

| 40   |         |            |              | RdCoe            | f[7:0]    |               |               |            |          |

| 41   | UpdtR   | ngIN[9:8]  | N            | MeanErrINE[18:16 | 5]        | Me            | anErrOUTE[18: | 16]        | 00XXXXXX |

| 42   |         |            |              | UpdtRng          | IN[7:0]   | I             |               |            | 10010000 |

| 43   |         |            |              | MeanErrI         | NE[15:8]  |               |               |            |          |

| 44   |         |            |              | MeanErrI         | NE[7:0]   |               |               |            |          |

| 45   |         |            |              | MeanErrOU        | JTE[15:8] |               |               |            |          |

| 46   |         |            |              | MeanErrO         | UTE[7:0]  |               |               |            |          |

| 47   | MenErrO | UTP[18:16] | UPlim        | itIN[9:8]        | UDlim     | itIN[9:8]     | DCinfor       | mRD[8]     | XXX0111X |

| 48   |         |            |              | MenErrOU         | TP [15:8] |               | l .           |            |          |

| 49   |         |            |              | MenErrOU         | JTP [7:0] |               |               |            |          |

| 50   |         |            |              | UPlimitI         | N[7:0]    |               |               |            | 00000000 |

| 51   |         |            |              | UDlimit          | IN[7:0]   |               |               |            | 00000000 |

| 52   |         |            |              | DCinform         | RD[7:0]   |               |               |            |          |

| 53   | U       |            | GAINcnt[2:0] |                  |           | " 1           | 101 "         |            | XXXX1101 |

| 64   | Pase    | Viterbi_on | Deint_on     | RSdec_on         | Derand_on | Errorflag_ins | Vsbdvalid_pol | Vsbclk_sup | 11111111 |

| 65   |         | 1          |              | Err_cou          | nt[7:0]   |               |               |            |          |

| 66   | U       | U          | U            | Data_out_en      |           |               | X             |            | XXX1XXXX |

| 67   |         | 1          | l .          | Err_cour         | nt[15:8]  |               |               |            |          |

| 128  | " 0 "   |            |              |                  | X         |               |               |            | 0XXXXXXX |

Where U: unused register bit, X: don't care

# 5.3 I<sup>2</sup>C Bus Register Description

# Address 0:

| 7 | Dinmode    | w | Most significant bit (MSB) inversion control signal of data input (DIN[9:0]). If data input form is unsigned, the MSB of digital data input should be inverted because all of functions in this chip use their complement data. If this bit is set                             |

|---|------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |            |   | to '1', it indicates the inversion of MSB. Initial value is '1'. (refer to table 6.3.1)                                                                                                                                                                                        |

| 6 | Dinsel     | W | Digital data input path selection signal. If this bit is set to '1', it indicates output of the internal ADC. Initial value is '1'. (refer to table 6.3.1)                                                                                                                     |

| 5 | ADCCLKSEL  | W | ADC Clock Select. When the frequency of VCXO is 2fs(21.52MHz), the output frequency of ADCCLK can be one of the two following frequencies, fs(10.76MHz) and 2fs. If this bit is set to '1', the frequency of ADCCLK is always fs. Initial value is '1'. (refer to table 6.2.1) |

| 4 | ADCCLKPH   | W | ADC Clock Phase Select. This signal can choose one of the ADCCLK output phases. If this bit is set to '0', the ADCCLK output phase is rotated 180° off with respect to CLKFS phase, and otherwise 0°. Default value is '1'. (refer to table 6.2.1)                             |

| 3 | DCbypass   | W | DC remove block bypass (active <b>high</b> ). Initial value is '0'.                                                                                                                                                                                                            |

| 2 | DChold     | W | DC remove block hold (active <b>high</b> ). Initial value is '0'.                                                                                                                                                                                                              |

| 1 | AGChold    | W | AGC block hold (active <b>high</b> ). Initial value is '0'.                                                                                                                                                                                                                    |

| 0 | AGCoffsetW | W | AGC offset write enable (active <b>high</b> ). Initial value is '0'.                                                                                                                                                                                                           |

# Address 1:

| [7,0] | AGCoffset [7:0] | W  | AGC offset value. If AGCoffsetW is set to '1', this signal is used for the |

|-------|-----------------|----|----------------------------------------------------------------------------|

| [7.0] | [7:0]           | VV | reference of AGC block. Default value is "01100000".                       |

# Address 2:

| [7:5] | VSBmod[2:0] | w | VSB mode signal. If VSBmodW is set to '1', this signal is used for VSB mode signal. Otherwise the VSBmod[2:0] signal is generated internally. Initial value is "101". |

|-------|-------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4:0] |             | W | Initial value is "10010". It would be better set to "10110".                                                                                                          |

# Address 3:

| [7:0] W Always set to "11001000". | [7:0] | W |  |  |

|-----------------------------------|-------|---|--|--|

|-----------------------------------|-------|---|--|--|

# Address 4:

| [7:6] |              | W | Initial value is "00". It would be better set to "01".                                                                                                                                                                                                                                                |

|-------|--------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5     | PolarityW    | W | Polarity signal write enable. If this bit is set to '1', it means write enable. Initial value is '0'.                                                                                                                                                                                                 |

| 4     | Polarity     | W | Polarity signal for polarity control and DATAPOLP/DATAPOLN. If PolarityW is '1', this signal is used for polarity control and the generation of DATAPOLP/DATAPOLN signal output. Otherwise the polarity control block uses internally calculated signal. Initial value is '0'. (refer to table 6.3.2) |

| [3:2] |              | W | Always set to "10".                                                                                                                                                                                                                                                                                   |

| 1     | nSyncLockrst | W | nSyncLock reset control signal. If this bit is set to '0', nSyncLock signal isn't initialized by the change of VSB mode. Otherwise, nSyncLock signal is initialized and changed to '0' for the next Field sync duration. Initial value is '0'.                                                        |

| 0     | VSBmodW      | W | VSB mode write enable. If this bit is set to '1', it means write enable. Initial value is '0'.                                                                                                                                                                                                        |

# Address 5:

| [7:6] | VCXOSEL [1:0]    | W | VCXO Selection. These pins should be set as follows according to the output frequency of VCXO.  VCXOSEL[1:0] The output frequency of VCXO  00 fs(10.76Mhz) 01 2fs(21.52Mhz)  Initial value is "00".                |

|-------|------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5     | nCombW           | W | nComb signal write enable. If this bit is set to '1', it means write enable. Initial value is '0'.                                                                                                                 |

| 4     | nComb            | W | Comb filter ON/OFF signal. If nCombW are '1', this signal is used for Comb filter ON/OFF signal. Otherwise the Comb filter ON/OFF signal is generated internally. Initial value is '1'.                            |

| 3     | Combouthalf      | W | Comb filter output gain selection signal. If this bit is set to '0', the gain of the Comb filter output is 1. Otherwise its gain is 1/2. When Comb filter is activated this signal is valid. Initial value is '1'. |

| [2:1] | NoCombgain [1:0] | W | NoComb path gain selection signal. The gain is as follows;  NoCombgain[1:0] the gain of normal path  "00" 1(0dB)  "01" 1.125(1.023dB)  "10" 1.1875(1.493dB)  "11" 1.25(1.938dB)  Initial value is "01".            |

| 0     |                  | W | Always set to '0'.                                                                                                                                                                                                 |

# Address 6:

| [7:0] DCvalue[7:0] R Calculated DC value of input data. |

|---------------------------------------------------------|

|---------------------------------------------------------|

# Address 7:

| [7:0] |  | R | don't care |

|-------|--|---|------------|

|-------|--|---|------------|

#### Address 8:

| 7 |              | R | don't care                                                                                                                                                                    |

|---|--------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 | nSyncLock    | R | Stability Indication of Data Sync Recovery block (active <b>low</b> ). If the value of this bit is '0', Data Segment Sync Recovery and Field Sync Recovery blocks are stable. |

| 5 | nSegLock     | R | Stability Indication of Data Segment Sync Recovery (active low).                                                                                                              |

| 4 | Combstat     | R | Comb filter ON/OFF status. If the value of this bit is '0', it indicates the Comb filter is ON.                                                                               |

| 3 | nVSBmodstart | R | Start indication of VSB mode detector which in the Equalizer. If the value of this bit is '1', it means detector is reset.                                                    |

| 2 | DATAPOLN     | R | Inverted polarity signal of input data.                                                                                                                                       |

| 1 | nPolLock     | R | Stability Indication of Polarity Decision (active <b>low</b> ).                                                                                                               |

| 0 | nFldLock     | R | Stability Indication of Field Sync Recovery (active <b>low</b> ).                                                                                                             |

# Address 9:

| [7.0] | D | J?4        |

|-------|---|------------|

| [7:0] | K | don't care |

| [,.0] |   | don t the  |

#### Address 10:

| [7:6] |          | R | don't care                                                                         |

|-------|----------|---|------------------------------------------------------------------------------------|

| 5     | nFrmLock | R | Stability Indication of inverted/non-inverted Field decision (active <b>low</b> ). |

| 4     | nVSBLock | R | Stability Indication of current VSB mode detection (active <b>low</b> ).           |

# Address 11:

| [7:3] |              | R | don't care                   |

|-------|--------------|---|------------------------------|

| [2:0] | VSBmodA[2:0] | R | Internally decided VSB mode. |

# Address 12, 13:

| [7:0] | R | don't care |

|-------|---|------------|

| [7:0] | R | don't care |

#### Address 14:

| [7:1] |           | R | don't care                                                                |

|-------|-----------|---|---------------------------------------------------------------------------|

| 0     | nCombLock | R | Stability Indication of Comb filter ON/OFF decision (active <b>low</b> ). |

#### Address 15:

| [7:0] | I R | R | don't care |

|-------|-----|---|------------|

| 17.01 | 1   | 1 | don t care |

# Address 32:

| 7 | nSyncLockPH | R | the state of the nSyncLock at the output of Phase Tracker                 |

|---|-------------|---|---------------------------------------------------------------------------|

| 4 | nCombPH     | R | indicates whether comb filter is on or not at the output of Phase Tracker |

| 3 | nSyncLockEQ | R | the state of the nSyncLock at the output of Equalizer                     |

| 2 | nDSsyncEQ   | R | the state of Data Segment Sync at the output of Equalizer                 |

| 1 | nFsyncEQ    | R | the state of Field Sync at the output of Equalizer                        |

| 0 | nCombEQ     | R | indicates whether Comb filter is on or not at the output of Equalizer     |

# Address 33 :

| Addre | SS 33 :             |     |                                                                                                                                                                                                          |

|-------|---------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | nFreezePHI2         | W/R | '0': Freezes the Phase Tracker in the device, which means phase tracking does not occur. '1': normal operation If you want to control Phase Tracker fast, use external input pins. Initial value is '1'. |

| 6     | InitPHI2            | W/R | '1': Initialize the Phase Tracker in the device. '0': normal operation If you want to control Phase Tracker fast, use external input pins. Initial value is '0'.                                         |

| [5:4] | PHASmodeIN<br>[1:0] | W/R | There are three loops in the Phase, which are gain, offset, and phase loop Tracker.  00: all loops on 01: offset loop off 10: offset and gain loops off 11: all loops off Initial value is "00".         |

| 3     | nFreezeEQI2         | W/R | '0': Freezes the Equalizer in the device, which means coefficient update does not occur. '1': normal operation If you want to control Equalizer fast, use external input pins. Initial value is '1'.     |

| 2     | InitEQI2            | W/R | '1': Initializes the Equalizer in the device. '0': normal operation If you want to control Equalizer fast, use external input pins. Initial value is '0'.                                                |

| [1:0] | STEPsizeIN<br>[1:0] | W/R | There are three available step-sizes in the Equalizer.  10,11: smallest step-size 01: middle step-size 00: largest step-size Initial value is "11".                                                      |

# Address 34:

| 7     | EQmodeTIN          | W/R | Updating range of the training sequence. The range value can be changed with                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6:5] | TRAINmodeIN [1: 0] | W/R | combination of these three bits. Initial value is "000".  EQmodeTIN is '0'  00: 574 symbols of field sync are used for equalization.  01: 637 symbols of field sync are used for equalization.  10: 700 symbols of field sync are used for equalization.  11: 820 symbols of field sync are used for equalization.  EQmodeTIN is '1'  00: 574 symbols of field sync are used for equalization.  01: 637 symbols of field sync are used for equalization.  10,11: 700 symbols of field sync are used for equalization. |

| 4     | CombOutHalfIN      | W/R | Comb filter output gain selection signal.  '0': the gain of the Comb filter output is <b>0</b> '1': the gain of the Comb filter output is <b>1/2</b> When Comb filter is activated this signal is valid.  Initial value is '1'.                                                                                                                                                                                                                                                                                       |

| 3     | nDSadptIN          | W/R | '0': uses data segment during equalization. '1': not uses data segment during equalization. Default value is '0'.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2     | nEQoutIN           | W/R | '0': noise removed output from Equalizer '1': bypassed output Initial value is '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| [1:0] | FLTtestIN[1:0]     | W/R | The location of center tap can be changed using these two bits. Initial value is "00". $00: \text{Center tap is } 32^{\text{nd}} \text{ tap} \\ 01: \text{Center tap is } 44^{\text{th}} \text{ tap} \\ 10: \text{Center tap is } 52^{\text{nd}} \text{ tap} \\ 11: \text{Center tap is } 60^{\text{th}} \text{ tap}$                                                                                                                                                                                                 |

#### Address 35:

| Addic | :SS JJ .            |     |                                                                                                                                                                                                                                 |

|-------|---------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | nIIR16ONIN          | W/R | '0' : feedback filter is on in 16 VSB mode '1' : feedback filter is off Initial value is '1'.                                                                                                                                   |

| 6     | nIIRONIN            | W/R | '0': feedback filter is on in 2, 4 and 8 VSB mode '1': feedback filter is on only in 8 VSB mode Initial value is '0'.                                                                                                           |

| 5     | nAdtOnDataI2        | W/R | '0': coefficient adaptation during training sequence and data interval '1': coefficient adaptation during training sequence interval only Initial value is '1'. If you want to control Equalizer fast, use external input pins. |

| [4:3] | BLNDmodeIN<br>[1:0] | W/R | "00": does not use blind equalization "01": uses blind equalization with 4-level data "10", "11": uses blind equalization with 2-level data Initial value is "00".                                                              |

| 2     | nRingENIN           | W/R | '1' : can not change nMakeRingIN '0' : can change nMakeRingIN Initial value is '1'.                                                                                                                                             |

| 1     | nCoefRead           | W/R | '0' : read coefficient '1' : write coefficient Initial value is '1'.                                                                                                                                                            |

| 0     | nMakeRingIN         | W/R | '0' : can read and write the coefficients '1' : normal operation Initial value is '1'.                                                                                                                                          |

# Address 36:

| [7:6] | PredicIN[1: 0]      | W/R | Determines whether to use slice predictor in Phase Tracker. Initial value is "11". "00": Slice Prediction is OFF. "01": not use. "10": not use. "11": Slice Prediction is ON.                                                           |  |  |  |

|-------|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [5:3] | LOOPgainIN<br>[2:0] | W/R | Determines use of automatic gain routine and type of loop gain to be used in Phase Tracker. Initial value is "000". "000": Automatic gain change. "001": phase tracker is OFF. "010": smaller gain. "011": normal gain. "1xx": not use. |  |  |  |

| 2     | nOPERmodeIN         | W/R | Sets the operation mode<br>'0': $-60^{\circ} \sim 60^{\circ}$<br>'1': $-45^{\circ} \sim 45^{\circ}$<br>Initial value is '0'.                                                                                                            |  |  |  |

| 1     | nDNgainIN           | W/R | Choose the value of loop gain. Initial value is '1'.                                                                                                                                                                                    |  |  |  |

| 0     | nDNgainThIN         | W/R | Choose the threshold value of loop gain when gain loop is used in automatic mode. Initial value is '1'.                                                                                                                                 |  |  |  |

# Address 37:

|       | TapAddress |     | Filter tap address in Equalizer | r. Initial value is "00000000". |

|-------|------------|-----|---------------------------------|---------------------------------|

| [7:0] | [7: 0]     | W/R | address 0 to address 63         | : feed forward filter           |

|       |            |     | address 64 to address 255       | : feed back filter              |

# Address 38:

| [7:4] | WrCoef[11: 8] | W/R | Coefficients to write to the Equalizer. Default value is "0000". |

|-------|---------------|-----|------------------------------------------------------------------|

| [3:0] | RdCoef[11: 8] | R   | Coefficients to be read from the Equalizer filter.               |

#### Address 39:

| [7:0] | WrCoef[7: 0]                            | W/R  | Coefficients to write to the Equalizer filter. Initial value is "00000000". |

|-------|-----------------------------------------|------|-----------------------------------------------------------------------------|

| 17.01 | *************************************** | **/1 | Coefficients to write to the Equalizer filter. Illitial value is 00000000.  |

# Address 40:

| [7:0] | RdCoef[7: 0] | R | Coefficients to be read from the Equalizer filter. |

|-------|--------------|---|----------------------------------------------------|

| [,.0] | 1100001[//0] |   | Coefficients to ce read from the Equalizer finter. |

# Address 41:

| [7:6] | UpdtRngIN[9: 8]        | W/R | Data range to be updated when nAdtOnDataI2 is '0'. Initial value is "00". This is 10-bit number. |

|-------|------------------------|-----|--------------------------------------------------------------------------------------------------|

| [5:3] | MeanErrINE<br>[18: 16] | R   | Mean squared error at the input of equalizer. This is 19-bit number.                             |

| [2:1] | MeanErrOUTE[ 18: 16]   | R   | Mean squared error at the output of equalizer. This is 19-bit number.                            |

# Address 42, 43, 44, 45, 46:

| [7:0] | UpdtRngIN[7:0]      | W/R | Data range to be updated when nAdtOnDataI2 is set Initial value is "10010000". |

|-------|---------------------|-----|--------------------------------------------------------------------------------|

| [7:0] | MeanErrINE [15:8]   | R   | Mean squared error at the input of Equalizer                                   |

| [7:0] | MeanErrINE [7:0]    | R   |                                                                                |

| [7:0] | MeanErrOUTE[ 15: 8] | R   | Mean squared amon at the output of Equalizar                                   |

| [7:0] | MeanErrOUTE[ 7: 0]  | R   | Mean squared error at the output of Equalizer                                  |

#### Address 47:

| [7:5] | MeanErrOUTP [18:16] | R   | Mean squared error at the output of Phase Tracker. This is 19-bit number.                                                                                             |

|-------|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4:3] | UPlimitIN<br>[9:8]  | W/R | 10-bit 2's complementary number and this should be positive number. If error of equalizer is larger than this limit, forces error to zero. Default value is "01".     |

| [2:1] | UDlimitIN[9:8]      | W/R | 10-bit 2's complementary number and this should be negative number. If error of equalizer is smaller than this limit, it is forced to be zero. Default value is "11". |

| 0     | DcinformRD[8]       | R   | Information of DC value. This shows the current DC value in DC reduction.                                                                                             |

| 0     | DcinformRD[8]       | R   | Information of DC value. This shows the current DC value in DC reduction.                                                                                             |

# Address 48, 49, 50, 51, 52:

| [7:0] | MeanErrOUTP[15:8] | R   |                                                                                                                                   |

|-------|-------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | MeanErrOUTP [7:0] | R   | Mean squared error at the output of Phase Tracker                                                                                 |

| [7:0] | UPlimitIN[7:0]    | W/R | 2's complementary number. If error of Equalizer is larger than this limit, it is forced to be zero. Initial value is "00000000".  |

| [7:0] | UDlimitIN[7:0]    | W/R | 2's complementary number. If error of Equalizer is smaller than this limit, it is forced to be zero. Initial value is "00000000". |

| [7:0] | DcinformRD [7:0]  | R   | Information of DC value. This shows the currently DC value in DC reduction.                                                       |

#### Address 53:

| ,     | 1441 000 001  |   |                                                                                                                                                                                                        |  |  |  |

|-------|---------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [6:4] | GAINcnt [2:0] | R | Shows the type of loop gain used in Phase Tracker. These bits are the results of gain loop setting in LOOPgainIN "001": phase tracker is OFF. "010": smaller gain is used. "011": normal gain is used. |  |  |  |

| [3:0] |               | W | Always set to "1101".                                                                                                                                                                                  |  |  |  |

# Address 64:

| 710011 | <del>5</del> 33 04. |   |                                                                                                                                                                                                                                                                                                                                              |

|--------|---------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | Pase                | W | Parallel/serial output selection '1': parallel '0': serial If this bit is set to '0', VSBDATA[0] pin is used as serial data output and VSBDATA[7] is used as start bit indicator of a byte. Initial value is '1'.                                                                                                                            |

| 6      | Viterbi_on          | W | Viterbi Decoder on/off selection '1': on '0': off If this bit is set to '0', hard decision decoding is performed instead of viterbi decoding. Initial value is '1'.                                                                                                                                                                          |

| 5      | Deint_on            | W | Deinterleaver on/off selection '1': on '0': off If this bit is set to '0', deinterleaver is bypassed. Initial value is '1'.                                                                                                                                                                                                                  |

| 4      | RSdec_on            | W | RS Decoder on/off selection '1': on '0': off If this bit is set to '0', RS decoder is bypassed. Initial value is '1'.                                                                                                                                                                                                                        |

| 3      | Derand_on           | W | Derandomizer on/off selection '1': on '0': off If this bit is set to '0', derandomizer is bypassed. Initial value is '1'.                                                                                                                                                                                                                    |

| 2      | Errorflag_ins       | W | Error flag bit insertion on/off selection. Valid only when Derand_on is set to '1'. '1': MSB of first data byte is set to '1' when the packet has an uncorrected errors(when NVSBERFLG is '0') '0': nothing is done at the MSB of first data byte although the packet has an uncorrected errors(when NVSBERFLG is '0') Initial value is '1'. |