## FAIRCHILD

SEMICONDUCTOR

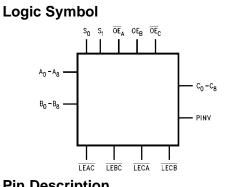

## 74FR900 9-Bit, 3-Port Latchable Datapath Multiplexer

#### **General Description**

The 74FR900 is a data bus multiplexer routing any of three 9-bit ports to any other one of the three ports. Readback of data latched from any port onto itself is also possible. The 74FR900 maintains separate control of all latch-enable, output enable and select inputs for maximum flexibility. PINV allows inversion of the data from the  $C_8$  to  $A_8$  or  $B_8$ path. This is useful for control of the parity bit in systems diagnostics.

Fairchild's 74FR25900 includes 25Ω resistors in series with port A and B outputs. Resistors minimize undershoot and ringing which may damage or corrupt sensitive device inputs driven by these ports.

#### **Features**

- 9-bit data ports for systems carrying parity bits

- Readback capability for system self checks.

- Independent control lines for maximum flexibility

- Guaranteed multiple output switching and 250 pF load delavs

May 1992

Revised August 1999

- Outputs optimized for dynamic bus drive capability

- PINV parity control facilitates system diagnostics

- FR25900 resistor option for driving MOS inputs such as DRAM arrays

#### **Ordering Code:**

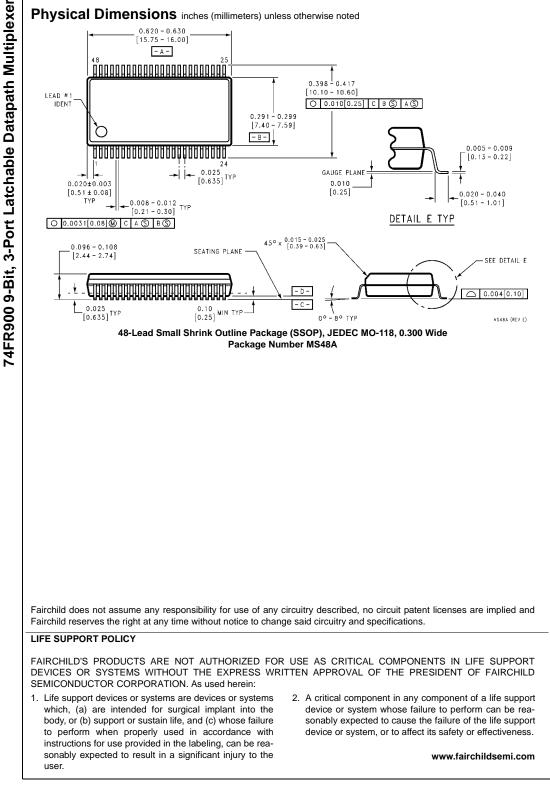

| Order Number           | Package Number           | Package Description                                                   |

|------------------------|--------------------------|-----------------------------------------------------------------------|

| 74FR900SSC             | MS48A                    | 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300 Wide |

| Devices also available | in Tape and Reel Specify | y by appending the suffix letter "X" to the ordering code             |

#### **Pin Description**

| Pin Names                       | Description                      |

|---------------------------------|----------------------------------|

| LExx                            | Latch Enable Inputs              |

| OEx                             | Output Enable Inputs             |

| PINV                            | Parity Invert Input              |

| S <sub>0</sub> , S <sub>1</sub> | Select Inputs                    |

| A <sub>0</sub> -A <sub>8</sub>  | Port A Inputs or 3-STATE Outputs |

| B <sub>0</sub> -B <sub>8</sub>  | Port B Inputs or 3-STATE Outputs |

| C <sub>0</sub> –C <sub>8</sub>  | Port C Inputs or 3-STATE Outputs |

#### **Connection Diagram**

S<sub>0</sub> GND A<sub>8</sub> Α7

A<sub>1</sub> Ao PINV ŌĒĄ

LECA

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                          |                   | agram      |    |                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|----|-------------------|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           |                   | $\bigcirc$ |    |                   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           | с <sub>4</sub> —  | 1          | 48 | - v <sub>cc</sub> |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           | GND -             | 2          | 47 | — c <sub>5</sub>  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           | с <sub>3</sub> —  | 3          | 46 |                   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           | c <sub>2</sub> —  | 4          | 45 |                   |

|                                                                                                                                                                                |                   | 5          | 44 | — с <sub>8</sub>  |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                          | с <sub>о</sub> —  | 6          | 43 |                   |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                          |                   | 7          | 42 | - OE <sub>C</sub> |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                          | s <sub>0</sub> —  | 8          | 41 | OEB               |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           |                   | 9          | 40 | – v <sub>cc</sub> |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           | A <sub>8</sub> —  | 10         | 39 | — в <sub>о</sub>  |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                          | A7 -              | 11         | 38 |                   |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                          | A <sub>6</sub> —  | 12         | 37 | — в <sub>2</sub>  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           | A5 —              | 13         | 36 |                   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           |                   | 14         | 35 |                   |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                          |                   | 15         | 34 | — B <sub>4</sub>  |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                          |                   | 16         | 33 |                   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           | A3 -              | 17         | 32 | — B <sub>5</sub>  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                           | A2 -              | 18         | 31 | — в <sub>6</sub>  |

| $\begin{array}{c c} PINV &= 21 & & 28 & - \overline{LECB} \\ \hline \overline{OE}_{A} &= 22 & & 27 & - \overline{LEBC} \\ V_{CC} &= 23 & & 26 & - \overline{LEAC} \end{array}$ |                   | 19         | 30 |                   |

| $\begin{array}{c c} PINV &= 21 & & 28 & - \overline{LECB} \\ \hline \overline{OE}_{A} &= 22 & & 27 & - \overline{LEBC} \\ V_{CC} &= 23 & & 26 & - \overline{LEAC} \end{array}$ | A <sub>0</sub> —  | 20         | 29 | — в <sub>8</sub>  |

| V <sub>CC</sub> - 23 26 - LEAC                                                                                                                                                 |                   | 21         | 28 |                   |

| V <sub>CC</sub> - 23 26 - LEAC                                                                                                                                                 | OE <sub>A</sub> - | 22         | 27 | LEBC              |

|                                                                                                                                                                                |                   | 23         | 26 | LEAC              |

|                                                                                                                                                                                |                   | 24         | 25 | - GND             |

|                                                                                                                                                                                | l                 |            |    | I                 |

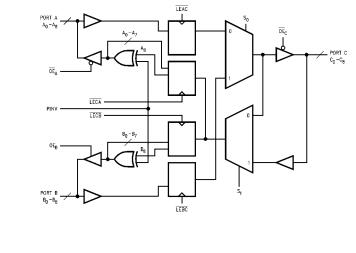

#### **Functional Description**

The 74FR900 allows 9-bit data to be transferred from any of three 9-bit I/O ports to either of the two remaining I/O ports. The device employs latches in all paths for either transparent or synchronous operation. Readback capability from any port to itself is also possible.

Data transfer within the 74FR900 is controlled through use of the select (S<sub>0</sub> and S<sub>1</sub>) and output-enable ( $\overline{OE}_A, OE_B$  and  $\overline{OE}_C$ ) inputs as described in Table 1. Additional control is available by use of the latch-enable inputs ( $\overline{LEAC}, LECA, LEBC, LECB$ ) allowing either synchronous or transparent transfers (see Table 2). Table 1 indicates several readback conditions. By latching data on a given port and initiating the readback control configuration, previous data may be read for system verification or diagnostics. This mode may be useful in implementing system diagnostics.

Data at the port to be readback must be latched prior to enabling the outputs on that port. If this is not done, a closed data loop will result causing possible data integrity problems. Note that the A and B ports allow readback without affecting any other port. Port C, however, requires interruption of either port A or B to complete its readback path.

PINV controls inversion of the C<sub>8</sub> bit. A low on PINV allows C<sub>8</sub> data to pass unaltered. A high causes inversion of the data. See Table 3. This feature allows forcing of parity errors for use in system diagnostics. This is particularly helpful in 486 processor designs as the 486 does not provide odd/even parity selection internally.

|                |                | Inputs |     |     |                                  |

|----------------|----------------|--------|-----|-----|----------------------------------|

| S <sub>0</sub> | S <sub>1</sub> | OEA    | OEB | OEC | Function                         |

| L              | Х              | Н      | L   | L   | Port A to Port C                 |

| L              | L              | н      | н   | н   | Port A to Port B                 |

| L              | 0              | Н      | н   | L   | Port A to B+C                    |

| Н              | L              | L      | L   | н   | Port B to Port A                 |

| Н              | Х              | Н      | L   | L   | Port B to Port C                 |

| н              | 0              | L      | L   | L   | Port B to A+C                    |

| Х              | н              | L      | L   | н   | Port C to Port A                 |

| Х              | Н              | Н      | н   | н   | Port C to Port B                 |

| Х              | Н              | L      | н   | н   | Port C to A+B                    |

| Х              | Х              | н      | L   | н   | Outputs Disabled                 |

| L              | L              | L      | Х   | Х   | (Readback to A)<br>(Note 1)      |

| L              | Н              | L      | Х   | L   | (Readback to A or C)<br>(Note 1) |

| н              | L              | х      | Н   | х   | (Readback to B)<br>(Note 1)      |

| н              | н              | Х      | Н   | L   | (Readback to B or C)<br>(Note 1) |

**TABLE 1. Datapath Control**

Note 1: Readback operation in latched mode only. Transparent operation could result in unpredictable results.

TABLE 2. Latch-Enable Control

H = HIGH Voltage Level

| LExx | Input | Output         |

|------|-------|----------------|

| L    | L     | L              |

| L    | н     | н              |

| Н    | Х     | Q <sub>0</sub> |

L = LOW Voltage

TABLE 3. PINV Control

| PINV | C <sub>8</sub> | A <sub>8</sub> or B <sub>8</sub> |

|------|----------------|----------------------------------|

| L    | L              | L                                |

| L    | н              | н                                |

| н    | L              | н                                |

| н    | н              | L                                |

Q<sub>0</sub> = Output state prior to LExx LOW-to-HIGH transition

#### Logic Diagram

www.fairchildsemi.com

#### Absolute Maximum Ratings(Note 2)

| Storage Temperature                         | $-65^{\circ}C$ to $+150^{\circ}C$    |

|---------------------------------------------|--------------------------------------|

| Ambient Temperature under Bias              | $-55^{\circ}C$ to $+125^{\circ}C$    |

| Junction Temperature under Bias             | -55°C to +150°C                      |

| V <sub>CC</sub> Pin Potential to Ground Pin | -0.5V to +7.0V                       |

| Input Voltage (Note 3)                      | -0.5V to +7.0V                       |

| Input Current (Note 3)                      | -30 mA to +5.0 mA                    |

| Voltage Applied to Output                   |                                      |

| in HIGH State (with $V_{CC} = 0V$ )         |                                      |

| Standard Output                             | –0.5V to V <sub>CC</sub>             |

| 3-STATE Output                              | -0.5V to +5.5V                       |

| Current Applied to Output                   |                                      |

| in LOW State (Max)                          | twice the rated I <sub>OL</sub> (mA) |

| ESD Last Passing Voltage (Min)              | 4000V                                |

|                                             |                                      |

# Recommended Operating Conditions

Free Air Ambient Temperature Supply Voltage 74FR900

0°C to +70°C +4.5V to +5.5V

Note 2: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 3: Either voltage limit or current limit is sufficient to protect inputs.

### **DC Electrical Characteristics**

| Symbol                             | Parameter                                  | Min  | Тур | Max  | Units | V <sub>cc</sub> | Conditions                                                                 |

|------------------------------------|--------------------------------------------|------|-----|------|-------|-----------------|----------------------------------------------------------------------------|

| V <sub>IH</sub>                    | Input HIGH Voltage                         | 2.0  |     |      | V     |                 | Recognized HIGH Signal                                                     |

| V <sub>IL</sub>                    | Input LOW Voltage                          |      |     | 0.8  | V     |                 | Recognized LOW Signal                                                      |

| V <sub>CD</sub>                    | Input Clamp Diode Voltage                  |      |     | -1.2 | V     | Min             | I <sub>IN</sub> = -18 mA                                                   |

| V <sub>OH</sub>                    | Output HIGH Voltage                        | 2.4  |     |      | V     | Min             | $I_{OH} = -3 \text{ mA} (A_n, B_n, C_n)$                                   |

|                                    |                                            | 2.0  |     |      | V     | Min             | $I_{OH} = -15 \text{ mA} (A_n, B_n, C_n)$                                  |

| V <sub>OL</sub>                    | Output LOW Voltage                         |      |     | 0.50 | V     | Min             | $I_{OL} = 24 \text{ mA} (A_n, B_n, C_n)$                                   |

| IIH                                | Input HIGH Current                         |      |     | 5    | μA    | Max             | V <sub>IN</sub> = 2.7V (Control Inputs)                                    |

| I <sub>BVI</sub>                   | Input HIGH Current<br>Breakdown Test       |      |     | 7    | μΑ    | Max             | V <sub>IN</sub> = 7.0V (Control Inputs)                                    |

| I <sub>BVIT</sub>                  | Input HIGH Current<br>Breakdown Test (I/O) |      |     | 100  | μΑ    | Max             | $V_{IN} = 5.5V (A_n, B_n, C_n)$                                            |

| IIL                                | Input LOW Current                          |      |     | -150 | μΑ    | Max             | V <sub>IN</sub> = 0.5V (Control Inputs)                                    |

| V <sub>ID</sub>                    | Input Leakage Test                         | 4.75 |     |      | v     | 0.0             | I <sub>ID</sub> = 1.9 μA,<br>All Other Pins Grounded                       |

| I <sub>OD</sub>                    | Output Circuit Leakage Test                |      |     | 3.75 | V     | 0.0             | V <sub>IOD</sub> = 150 mV,<br>All Other Pins Grounded                      |

| I <sub>IH</sub> + I <sub>OZH</sub> | Output Leakage Current                     |      |     | 25   | μA    | Max             | V <sub>OUT</sub> =2.7V (A <sub>n</sub> , B <sub>n</sub> , C <sub>n</sub> ) |

| $I_{IIL} + I_{OZL}$                | Output Leakage Current                     |      |     | -150 | μΑ    | Max             | $V_{OUT} = 0.5V (A_n, B_n, C_n)$                                           |

| I <sub>OS</sub>                    | Output Short Circuit Current               | -100 |     | -225 | mA    | Max             | $V_{OUT} = 0.0V (A_n, B_n, C_n)$                                           |

| I <sub>CEX</sub>                   | Output HIGH Leakage Current                |      |     | 50   | μΑ    | Max             | $V_{OUT} = V_{CC} (A_n, B_n, C_n)$                                         |

| I <sub>ZZ</sub>                    | Bus Drainage Test                          |      |     | 100  | μA    | 0.0             | $V_{OUT} = 5.25V (A_n, B_n, C_n)$                                          |

| I <sub>CCH</sub>                   | Power Supply Current                       |      | 115 | 150  | mA    | Max             | All Outputs HIGH (Note 4)                                                  |

| I <sub>CCL</sub>                   | Power Supply Current                       |      | 170 | 200  | mA    | Max             | All Outputs LOW (Note 4)                                                   |

| I <sub>CCZ</sub>                   | Power Supply Current                       |      | 147 | 175  | mA    | Max             | Outputs in 3-STATE                                                         |

Note 4: 2 ports active only

|                  |                                                                                         |     | $T_A = +25^{\circ}C$    |      | $T_A = 0^\circ C$       | to +70°C |       |

|------------------|-----------------------------------------------------------------------------------------|-----|-------------------------|------|-------------------------|----------|-------|

| Cumb al          | Parameter                                                                               |     | V <sub>CC</sub> = +5.0V | 1    | V <sub>CC</sub> =       | +5.0V    | Units |

| Symbol           | Parameter                                                                               |     | $C_L = 50 \ pF$         |      | <b>C</b> <sub>L</sub> = | 50 pF    | Units |

|                  |                                                                                         | Min | Тур                     | Max  | Min                     | Max      | -     |

| t <sub>PLH</sub> | Propagation Delay                                                                       |     |                         |      |                         |          |       |

| t <sub>PHL</sub> | A <sub>n</sub> or B <sub>n</sub> to C <sub>n</sub>                                      | 2.0 | 4.2                     | 7.0  | 2.0                     | 7.0      | ns    |

|                  | C <sub>n</sub> to A <sub>n</sub> or B <sub>n</sub>                                      |     |                         |      |                         |          |       |

| t <sub>PLH</sub> | Propagation Delay                                                                       | 2.5 | 4.8                     | 7.5  | 2.5                     | 7.5      | ns    |

| t <sub>PHL</sub> | C <sub>8</sub> to A <sub>8</sub> or B <sub>8</sub> (PINV HIGH)                          | 2.0 | 4.0                     | 1.5  | 2.0                     | 1.5      | ns    |

| t <sub>PLH</sub> | Propagation Delay                                                                       | 4.5 | 6.4                     | 10.0 | 4.5                     | 10.0     | ns    |

| t <sub>PHL</sub> | A <sub>n</sub> to B <sub>n</sub> , B <sub>n</sub> to A <sub>n</sub>                     | 4.0 |                         |      |                         |          |       |

| t <sub>PLH</sub> | Propagation Delay                                                                       | 4.5 | 6.8                     | 10.0 | 4.5                     | 10.0     | ns    |

| t <sub>PHL</sub> | LEAC to $C_n$ , LEBC to $C_n$                                                           | 4.0 | 0.0                     | 10.0 | 4.5                     |          |       |

| t <sub>PLH</sub> | Propagation Delay                                                                       | 3.0 | 6.0                     | 9.5  | 3.0                     | 9.5      | ns    |

| t <sub>PHL</sub> | $\overline{\text{LECA}}$ to A <sub>n</sub> , $\overline{\text{LECB}}$ to B <sub>n</sub> |     | 0.0                     | 9.5  |                         |          |       |

| t <sub>PLH</sub> | Propagation Delay                                                                       | 3.0 | 6.0                     | 10.0 | 3.0                     | 10.0     | ns    |

| t <sub>PHL</sub> | S <sub>0</sub> to C <sub>n</sub>                                                        | 3.0 | 0.0                     | 10.0 | 3.0                     | 10.0     | 115   |

| t <sub>PLH</sub> | Propagation Delay                                                                       | 3.5 | 6.5                     | 11.0 | 3.5                     | 11.0     | ns    |

| t <sub>PHL</sub> | S <sub>1</sub> to A <sub>n</sub> or B <sub>n</sub>                                      | 5.5 | 0.5                     | 11.0 | 5.5                     | 11.0     | 115   |

| t <sub>PLH</sub> | Propagation Delay                                                                       | 2.0 | 5.0                     | 9.0  | 2.0                     | 9.0      | ns    |

| t <sub>PHL</sub> | PINV to A <sub>8</sub> or B <sub>8</sub>                                                | 2.0 | 0.0                     | 3.0  | 2.0                     | 3.0      | 115   |

| t <sub>PZH</sub> | Output Enable Time                                                                      | 2.0 | 4.0                     | 6.5  | 2.0                     | 6.5      | ns    |

| t <sub>PZL</sub> | A <sub>n</sub> , C <sub>n</sub>                                                         | 2.0 | 4.0                     | 0.0  | 2.0                     | 0.0      | 113   |

| t <sub>PHZ</sub> | Output Disable Time                                                                     | 1.5 | 4.0                     | 6.0  | 1.5                     | 6.0      | ns    |

| t <sub>PLZ</sub> | A <sub>n</sub> , C <sub>n</sub>                                                         | 1.5 | 4.0                     | 0.0  | 1.0                     | 0.0      | 113   |

| t <sub>PZH</sub> | Output Enable Time                                                                      | 2.0 | 5.0                     | 7.0  | 2.0                     | 7.0      | ns    |

| t <sub>PZL</sub> | B <sub>n</sub>                                                                          | 2.0 | 5.0                     |      | 2.0                     |          | 113   |

| t <sub>PHZ</sub> | Output Disable Time                                                                     | 2.0 | 5.0                     | 7.0  | 2.0                     | 7.0      | ns    |

| t <sub>PLZ</sub> | B <sub>n</sub>                                                                          | 2.0 | 0.0                     | 7.0  | 2.0                     | 7.0      | 113   |

# AC Operating Requirements

| Symbol             |                                |     | $T_A = +25^{\circ}C$ $V_{CC} = +5.0V$ $C_L = 50 \text{ pF}$ |     |     | $T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C$ $V_{CC} = +5.0V$ $C_{L} = 50 \text{ pF}$ |     |

|--------------------|--------------------------------|-----|-------------------------------------------------------------|-----|-----|----------------------------------------------------------------------------------------|-----|

|                    |                                | Min | Тур                                                         | Max | Min | Max                                                                                    |     |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW        | 4.0 | 2.0                                                         |     | 4.0 |                                                                                        | ns  |

| t <sub>S</sub> (L) | $A_n$ to LEAC, $B_n$ to LEBC   | 4.0 | 2.0                                                         |     | 4.0 |                                                                                        | 115 |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW         | 1.0 | 2.0                                                         |     | 1.0 |                                                                                        |     |

| t <sub>H</sub> (L) | $A_n$ to LEAC, $B_n$ to LEBC   | 1.0 | -2.0                                                        |     | 1.0 |                                                                                        | ns  |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW        | 2.0 | 1.0                                                         |     | 2.0 |                                                                                        |     |

| t <sub>S</sub> (L) | C <sub>n</sub> to LECA or LECB | 3.0 | 1.0                                                         |     | 3.0 |                                                                                        | ns  |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW         | 1.0 | 1.0                                                         |     | 1.0 |                                                                                        |     |

| t <sub>H</sub> (L) | C <sub>n</sub> to LECA or LECB | 1.0 | -1.0                                                        |     | 1.0 |                                                                                        | ns  |

| t <sub>W</sub> (H) | LE Pulse Width LOW             | 8.0 | 4.0                                                         |     | 8.0 |                                                                                        | ns  |

### **Extended AC Electrical Characteristics**

|                  | $T_A = 0^\circ C$      | to +70°C               | $T_A = 0^\circ C$ |                         |     |       |

|------------------|------------------------|------------------------|-------------------|-------------------------|-----|-------|

|                  | $V_{CC} = +5.0V$       |                        | $V_{CC} = +5.0V$  |                         |     |       |

| Symbol           | Symbol Parameter       | C <sub>L</sub> = 50 pF |                   | C <sub>L</sub> = 250 pF |     | Units |

|                  | Nine Outputs Switching |                        | (Note 6)          |                         |     |       |

|                  |                        | (No                    | te 5)             |                         |     |       |

|                  |                        | Min                    | Max               | Min                     | Max |       |

| t <sub>PLH</sub> | Propagation Delay      |                        |                   |                         |     |       |

www.fairchildsemi.com

| Symbol           | Parameter                                                           | $T_{A} = 0^{\circ}C$ $V_{CC} =$ $C_{L} =$ Nine Output (Not | T <sub>A</sub> = 0°C<br>V <sub>CC</sub> =<br>C <sub>L</sub> = 2<br>(No | Units |      |     |

|------------------|---------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------|-------|------|-----|

|                  |                                                                     | Min                                                        | Max                                                                    | Min   | Max  |     |

| t <sub>PHL</sub> | A <sub>n</sub> or B <sub>n</sub> to C <sub>n</sub>                  | 2.0                                                        | 9.0                                                                    | 2.5   | 10.5 | ns  |

|                  | C <sub>n</sub> to A <sub>n</sub> or B <sub>n</sub>                  |                                                            |                                                                        |       |      |     |

| t <sub>PLH</sub> | Propagation Delay                                                   |                                                            |                                                                        | 3.5   | 11.0 | ns  |

| t <sub>PHL</sub> | C <sub>8</sub> to A <sub>8</sub> or B <sub>8</sub> (PINV HIGH)      |                                                            |                                                                        | 0.0   |      |     |

| t <sub>PLH</sub> | Propagation Delay                                                   | 4.5                                                        | 12.0                                                                   | 5.5   | 13.5 | ns  |

| t <sub>PHL</sub> | A <sub>n</sub> to B <sub>n</sub> , B <sub>n</sub> to A <sub>n</sub> |                                                            | .2.0                                                                   | 0.0   | 10.0 |     |

| t <sub>PLH</sub> | Propagation Delay                                                   | 4.5                                                        | 12.0                                                                   | 5.5   | 13.5 | ns  |

| t <sub>PHL</sub> | LEAC to C <sub>n</sub> , LEBC to C <sub>n</sub>                     |                                                            | 12.0                                                                   | 0.0   | 10.0 |     |

| t <sub>PLH</sub> | Propagation Delay                                                   | 3.0                                                        | 11.5                                                                   | 4.0   | 13.5 | ns  |

| t <sub>PHL</sub> | LECA to A <sub>n</sub> , LECB to B <sub>n</sub>                     | 5.0                                                        | 11.5                                                                   | 4.0   | 15.5 | 115 |

| t <sub>PLH</sub> | Propagation Delay                                                   | 3.0                                                        | 11.0                                                                   | 3.0   | 14.0 | ns  |

| t <sub>PHL</sub> | S <sub>0</sub> to C <sub>n</sub>                                    | 5.0                                                        | 11.0                                                                   | 5.0   | 14.0 | 115 |

| t <sub>PLH</sub> | Propagation Delay                                                   | 3.5                                                        | 12.0                                                                   | 4.5   | 15.0 | ns  |

| t <sub>PHL</sub> | S <sub>1</sub> to A <sub>n</sub> or B <sub>n</sub>                  | 3.5                                                        | 12.0                                                                   | 7.5   | 10.0 | 115 |

| t <sub>PLH</sub> | Propagation Delay                                                   |                                                            |                                                                        | 2.5   | 12.0 | ns  |

| t <sub>PHL</sub> | PINV to A <sub>8</sub> or B <sub>8</sub>                            |                                                            |                                                                        | 2.5   | 12.0 | 115 |

| t <sub>PZH</sub> | Output Enable Time                                                  | 2.0                                                        | 8.0                                                                    |       |      | ns  |

| t <sub>PZL</sub> | A <sub>n</sub> , C <sub>n</sub>                                     | 2.0                                                        | 0.0                                                                    |       |      | 113 |

| t <sub>PHZ</sub> | Output Disable Time                                                 | 1.5                                                        | 6.0                                                                    |       |      | ns  |

| t <sub>PLZ</sub> | A <sub>n</sub> , C <sub>n</sub>                                     | 1.0                                                        | 0.0                                                                    |       |      |     |

| t <sub>PZH</sub> | Output Enable Time                                                  | 2.0                                                        | 8.0                                                                    |       |      | ns  |

| t <sub>PZL</sub> | B <sub>n</sub>                                                      | 2.0                                                        | 0.0                                                                    |       |      |     |

| t <sub>PHZ</sub> | Output Disable Time                                                 | 2.0                                                        | 7.0                                                                    |       |      | ns  |

| t <sub>PLZ</sub> | Bn                                                                  | 2.0                                                        |                                                                        |       |      |     |

Note 5: This specification is guaranteed but not tested. The limits apply to propagation delays for all paths described switching in phase, i.e., all LOW-to-HIGH, HIGH-to-LOW, 3-STATE-to-HIGH, etc.

Note 6: This specification is guaranteed but not tested. The limits represent propagation delays with 250 pF load capacitors in place of the 50 pF load capacitors standard AC load. This specification pertains to single output switching only.

74FR900

www.fairchildsemi.com