## **SPEAR-09-H022**

SPEAr™ Head200

## ARM 926, 200K customizable eASIC™ gates, large IP portfolio SoC

PRELIMINARY DATA

#### **Features**

- ARM926EJ-S f<sub>MAX</sub> 266 MHz,

32 KI 16 KD cache, 8 KI KD TCM, ETM9 and JTAG interfaces

- 200K customizable equivalent ASIC gates (16K LUT equivalent) with 8 channels internal DMA high speed accelerator function and 112 dedicated general purpose I/Os

- Multilayer AMBA 2.0 compliant Bus with f<sub>MAX</sub> 133 MHz

- Programmable internal clock generator with enhanced PLL function, specially optimized for E.M.I. reduction

- 16 KB single port SRAM embedded

- Dynamic RAM interface:16 bit DDR, 32 / 16 bit SDRAM

- SPI interface connecting serial ROM and Flash devices

- 2 USB 2.0 Host independent ports with integrated PHYs

- USB 2.0 Device with integrated PHY

- Ethernet MAC 10/100 with MII management interface

- 3 independent UARTs up to 115 Kbps (Software Flow Control mode)

- I<sup>2</sup>C Master mode Fast and Slow speed

- 6 General Purpose I/Os

- ADC 8 bits, 230 Ksps, 16 analog input channels

- Real Time Clock

- WatchDog

- 4 General Purpose Timers

- Operating temperature: 40 to 85 °C

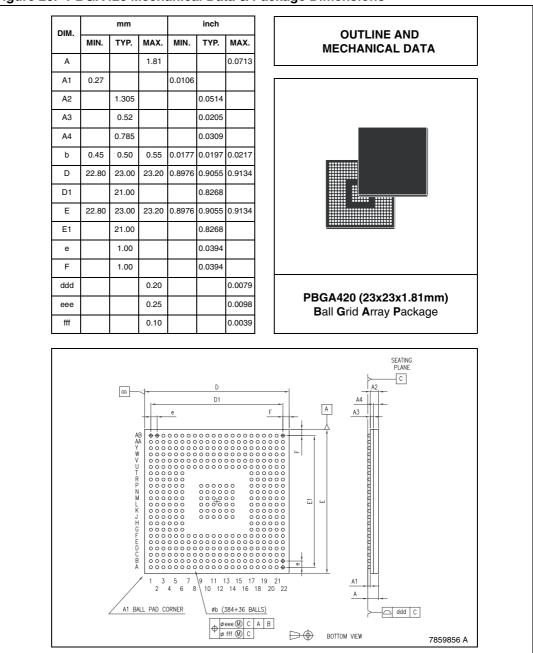

- Package: PBGA 384+36 6R (23x23x1.81 mm)

#### **Overview**

SPEAr Head200 is a powerful digital engine belonging to SPEAr family, the innovative customizable System on Chips.

The device integrates an ARM core with a large set of proven IPs (Intellectual Properties) and a configurable logic block that allows very fast customization of unique and/or proprietary solutions, with low effort and low investment.

Optimized for embedded applications.

#### **Order codes**

| Part number   | Op. Temp. range, °C | Package                 | Packing |

|---------------|---------------------|-------------------------|---------|

| SPEAR-09-H022 | -40 to 85           | PBGA420 (23x23x1.81 mm) | Tray    |

Contents SPEAR-09-H022

## **Contents**

| 1 | Refe  | rence documentation8               |

|---|-------|------------------------------------|

| 2 | Prod  | uct Overview9                      |

| 3 | Feat  | ures11                             |

|   | 3.1   | CPU 11                             |

|   | 3.2   | Internal bus structures            |

|   | 3.3   | Clock system                       |

|   | 3.4   | Interrupt controller 11            |

|   | 3.5   | Memory system                      |

|   |       | 3.5.1 Memory on chip               |

|   |       | 3.5.2 SPI                          |

|   |       | 3.5.3 Multi-port memory controller |

|   | 3.6   | High speed connectivity            |

|   |       | 3.6.1 USB 2.0 host                 |

|   |       | 3.6.2 USB 2.0 device               |

|   |       | 3.6.3 Ethernet 10/100              |

|   | 3.7   | Low speed connectivity             |

|   |       | 3.7.1 UART                         |

|   |       | 3.7.2 I <sup>2</sup> C             |

|   | 3.8   | General purpose I/Os               |

|   | 3.9   | Analog to Digital Converter        |

|   | 3.10  | Real time clock                    |

|   | 3.11  | Watchdog timer                     |

|   | 3.12  | General purpose timers             |

|   | 3.13  | Customizable logic                 |

| 4 | Bloc  | k diagram15                        |

| 5 | Pin c | lescription                        |

|   | 5.1   | Functional pin groups              |

|   | 5.2   | Special I/Os                       |

|   |       | 5.2.1 USB 2.0 Transceiver          |

SPEAR-09-H022 Contents

|             |                               | 5.2.2             | DRAM                               | 27   |  |  |  |  |  |  |

|-------------|-------------------------------|-------------------|------------------------------------|------|--|--|--|--|--|--|

| 6           | Mem                           | ory map           | р                                  | 28   |  |  |  |  |  |  |

| 7           | Powe                          | Power on sequence |                                    |      |  |  |  |  |  |  |

|             | 7.1                           | SPEAr             | Head200 software architecture      | 30   |  |  |  |  |  |  |

|             |                               | 7.1.1             | Boot process                       | 30   |  |  |  |  |  |  |

|             |                               |                   | Memory mapping                     |      |  |  |  |  |  |  |

|             |                               |                   | Serial Flash at 0x0                |      |  |  |  |  |  |  |

|             |                               | 7.1.2             | Booting sequence                   |      |  |  |  |  |  |  |

| 8           | ARM                           | 926EJ-\$          | s                                  | 32   |  |  |  |  |  |  |

| 9           | Cloc                          | k and re          | eset system                        | 33   |  |  |  |  |  |  |

|             | 9.1                           | Overvi            | ew                                 | 33   |  |  |  |  |  |  |

|             | 9.2                           | Reset a           | and PLL change parameters sequence | 35   |  |  |  |  |  |  |

|             | 9.3                           | Crystal           | I connection                       | 36   |  |  |  |  |  |  |

| 10          | Vectored interrupt controller |                   |                                    |      |  |  |  |  |  |  |

|             | 10.1                          | Overvie           | ew                                 | 37   |  |  |  |  |  |  |

|             | 10.2                          | Vector            | interrupt controller flow sequence | 38   |  |  |  |  |  |  |

|             | 10.3                          | Simple            | interrupt flow sequence            | 38   |  |  |  |  |  |  |

|             | 10.4                          | Interrup          | pt sources in SPEAr Head200        | 39   |  |  |  |  |  |  |

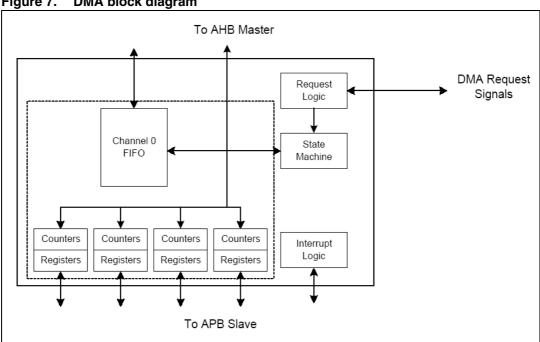

| 11          | DMA                           | control           | ller block                         | 40   |  |  |  |  |  |  |

|             | 11.1                          | Functio           | onal description                   | 40   |  |  |  |  |  |  |

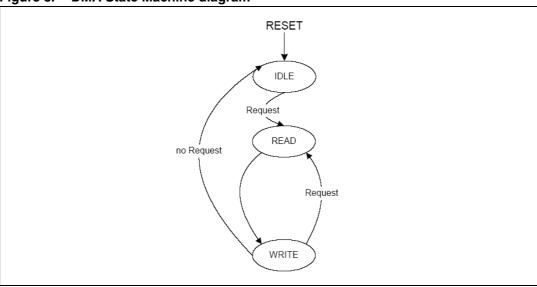

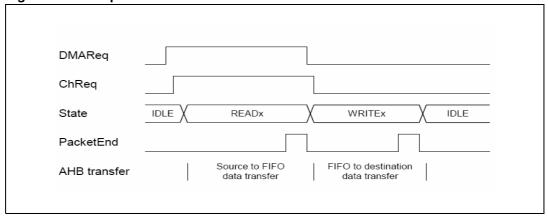

|             | 11.2                          | DMA co            | control state machine              | 41   |  |  |  |  |  |  |

| 12          | Multi                         | i-Port M          | lemory Controller                  | 42   |  |  |  |  |  |  |

|             | 12.1                          | Overvi            | ew                                 | 42   |  |  |  |  |  |  |

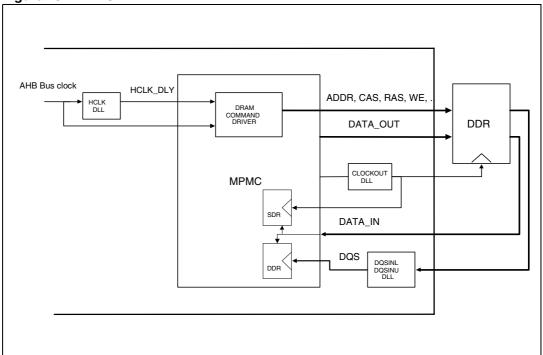

|             | 12.2                          | МРМС              | DELAY LINES                        | 44   |  |  |  |  |  |  |

|             | 12.3                          | SSTLL             | PAD CONFIGURATION                  | 45   |  |  |  |  |  |  |

| 13          | SPI r                         | nemorie           | es                                 | 46   |  |  |  |  |  |  |

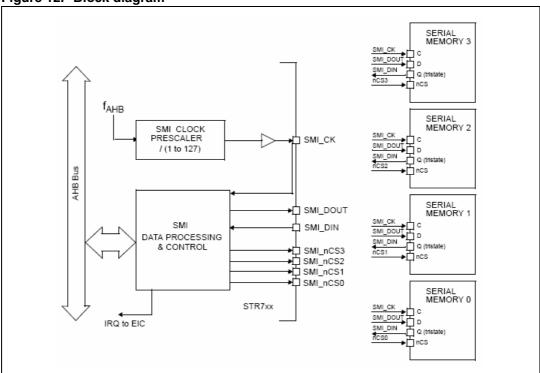

|             | 13.1                          | Overvi            | ew                                 | 46   |  |  |  |  |  |  |

|             | 13.2                          | SMI de            | escription                         | 47   |  |  |  |  |  |  |

| <b>\7</b> / |                               |                   | 3                                  | 3/71 |  |  |  |  |  |  |

|    |                    | 13.2.1    | Transfer rules               | . 48 |

|----|--------------------|-----------|------------------------------|------|

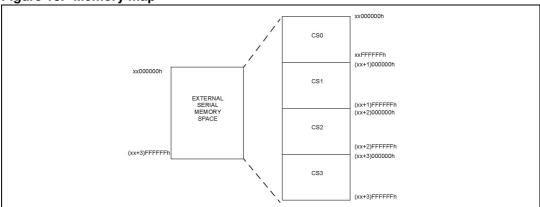

|    |                    | 13.2.2    | Memory map                   | . 48 |

|    |                    | 13.2.3    | Operation mode               | . 49 |

|    |                    |           | Hardware mode                |      |

|    |                    |           | Software mode                |      |

|    |                    | 13.2.4    | Booting from external memory | . 49 |

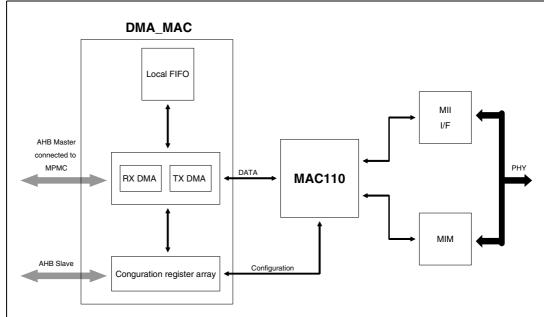

| 14 | Ethe               | rnet MA   | C 110                        | 50   |

|    | 14.1               | Overvie   | ew                           | . 50 |

| 15 | USB                | 2.0 Hos   | t                            | . 51 |

|    | 15.1               | Overvie   | ew                           | . 51 |

|    |                    | 15.1.1    | USB2.0PHY                    | . 51 |

|    |                    | 15.1.2    | UHC                          | . 51 |

| 16 | USB                | 2.0 Devi  | ice                          | . 52 |

|    | 16.1               | Overvie   | ew                           | . 52 |

|    |                    | 16.1.1    | USB2.0PHY                    | . 52 |

|    |                    | 16.1.2    | UDC                          | . 52 |

|    |                    | 16.1.3    | DMA                          | . 52 |

|    |                    | 16.1.4    | USB plug detect              | . 52 |

| 17 | UAR                | г         |                              | . 53 |

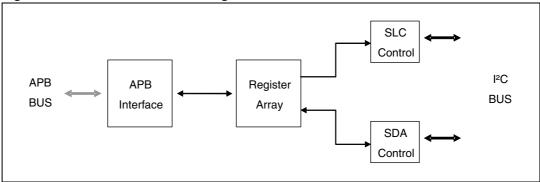

| 18 | I <sup>2</sup> C c | ontrolle  | r                            | . 54 |

|    | 18.1               |           | ew                           |      |

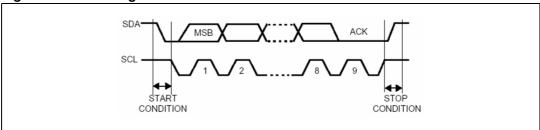

|    | 18.2               | Operati   | ing mode                     | . 55 |

|    |                    |           | ctional description          |      |

| 19 | Gene               | eral purp | oose I/Os                    | . 58 |

| 20 | ADC                |           |                              | . 59 |

|    | 20.1               |           | ew                           |      |

|    | 20.2               | Functio   | nal description              | . 59 |

| 21 | Real               | time clo  | ock                          | . 60 |

SPEAR-09-H022 Contents

| 22 | Watc  | hdog ti  | mer                           | 61 |

|----|-------|----------|-------------------------------|----|

| 23 | Gene  | eral pur | pose timers                   | 62 |

| 24 | Cust  | omizabl  | le logic                      | 63 |

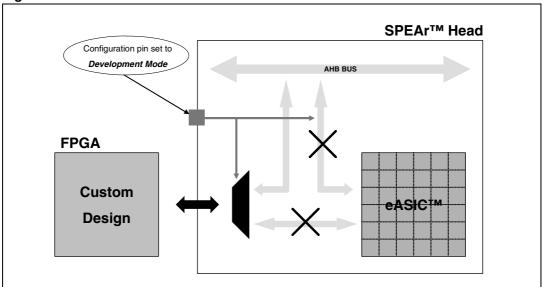

|    | 24.1  | Overvi   | ew                            | 63 |

|    | 24.2  | Custon   | m project development         | 63 |

|    |       | 24.2.1   | SPEAr Head behavioral model   | 63 |

|    |       | 24.2.2   | External FPGA                 | 63 |

|    | 24.3  | Custon   | mization process              | 64 |

|    | 24.4  | Power    | on sequence                   | 65 |

|    |       | 24.4.1   | Bitstream download            | 65 |

|    |       | 24.4.2   | Connection startup            | 65 |

|    |       | 24.4.3   | Programming interface         | 65 |

| 25 | Elect | rical ch | naracteristics                | 66 |

|    | 25.1  | Absolu   | ite maximum ratings           | 66 |

|    | 25.2  | DC ele   | ectrical characteristics      | 67 |

|    |       | 25.2.1   | Supply voltage specifications | 67 |

|    |       | 25.2.2   | I/O voltage specifications    | 67 |

| 26 | Pack  | age info | ormation                      | 69 |

| 27 | Revi  | sion his | story                         | 70 |

List of tables SPEAR-09-H022

## List of tables

| Table 1.  | Pin description by functional groups                                    | 16 |

|-----------|-------------------------------------------------------------------------|----|

| Table 2.  | Pins belonging to POWER group                                           | 25 |

| Table 3.  | Memory map                                                              | 28 |

| Table 4.  | Memory mapping at reset (REMAP = 0)                                     | 30 |

| Table 5.  | Memory Mapping after reset after remapping                              | 30 |

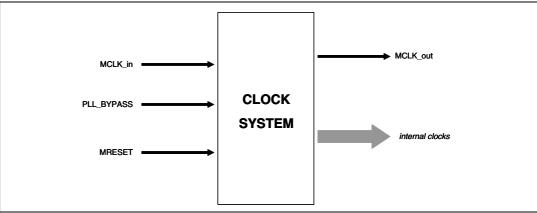

| Table 6.  | Clock system I/O off-chip interface                                     | 34 |

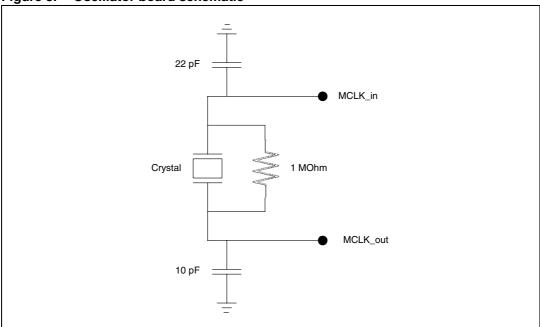

| Table 7.  | Parameters for 12 MHz crystal                                           | 36 |

| Table 8.  | Interrupt sources in SPEAr Head200                                      | 39 |

| Table 9.  | Supported memory cuts                                                   | 42 |

| Table 10. | Multi-Port Memory Controller AHB port assignment                        | 42 |

| Table 11. | Multi-Port Memory Controller off-chip interfaces                        | 43 |

| Table 12. | Output impedance configuration                                          | 45 |

| Table 13. | SPI signal interfaces description                                       | 46 |

| Table 14. | SMI Supported instructions                                              | 48 |

| Table 15. | External pins of ADC macro                                              |    |

| Table 17. | Recommended operating conditions                                        | 67 |

| Table 18. | Low Voltage TTL DC input specification (3 < VDD < 3.6)                  | 67 |

| Table 19. | Low Voltage TTL DC output specification (3 < VDD < 3.6)                 | 67 |

| Table 20. | Pull-up and Pull-down characteristics                                   |    |

| Table 21. | LVCMOS DC input specification (3 < VDD < 3.6)                           |    |

| Table 22. | LVCMOS DC output specification (3 < VDD < 3.6)                          | 68 |

| Table 23. | DC input specification of bidirectional SSTL pins (2.3 < VDD DDR < 2.7) |    |

| Table 24. | DC input specification of bidirectional differential SSTL pins          |    |

| Table 25. | Document revision history                                               | 70 |

|           |                                                                         |    |

SPEAR-09-H022 List of figures

# **List of figures**

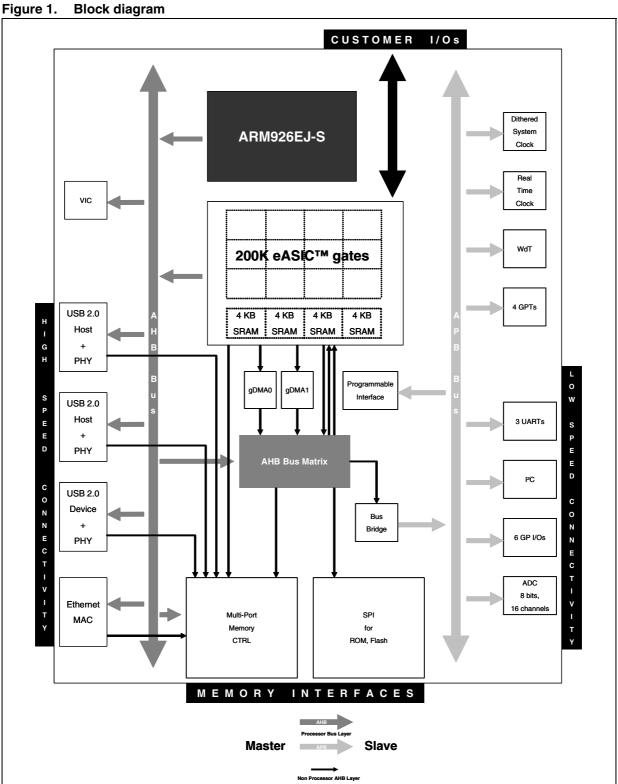

| Figure 1.  | Block diagram                                | 15 |

|------------|----------------------------------------------|----|

| Figure 2.  | ARM926EJ-S block diagram                     |    |

| Figure 3.  | Clock system block interfaces                | 34 |

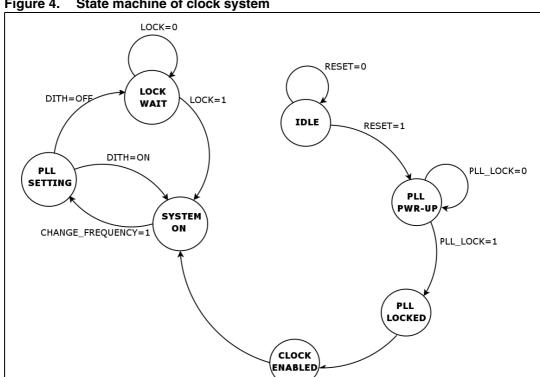

| Figure 4.  | State machine of clock system                | 35 |

| Figure 5.  | Oscillator board schematic                   | 36 |

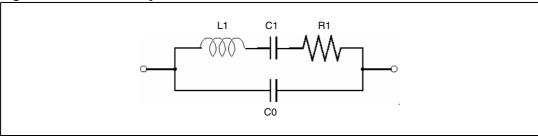

| Figure 6.  | Model for crystal                            | 36 |

| Figure 7.  | DMA block diagram                            | 40 |

| Figure 8.  | DMA State Machine diagram                    | 41 |

| Figure 9.  | Data packet transfer                         | 41 |

| Figure 10. | MPMC DLL                                     | 44 |

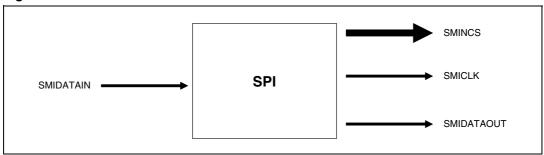

| Figure 11. | SPI Interfaces                               | 46 |

| Figure 12. | Block diagram                                | 47 |

| Figure 13. | Memory map                                   | 48 |

| Figure 14. | Ethernet MAC Controller block diagram        | 50 |

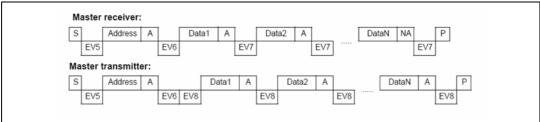

| Figure 15. | I <sup>2</sup> C Controller block diagram    | 54 |

| Figure 16. | I <sup>2</sup> C timing                      | 55 |

| Figure 17. | Transfer sequencing                          | 57 |

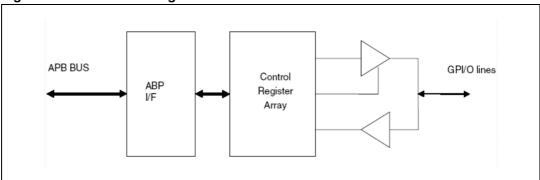

| Figure 18. | GPIO block diagram                           | 58 |

| Figure 19. | Emulation with external FPGA                 | 64 |

| Figure 20. | PBGA420 Mechanical Data & Package Dimensions | 69 |

## 1 Reference documentation

- 1. ARM926EJ-S Technical Reference Manual

- 2. AMBA 2.0 Specification

- 3. EIA/JESD8-9 Specification

- 4. USB2.0 Specification

- 5. OCHI Specification

- 6. ECHI Specification

- 7. UTMI Specification

- 8. USB Specification

- 9. IEEE 802.3 Specification

- 10. I<sup>2</sup>C Bus Specification

SPEAR-09-H022 Product Overview

### 2 Product Overview

SPEAr Head200 is a powerful System on Chip based on 110nm HCMOS and consists of 2 main parts: an ARM based architecture and an embedded customizable logic block. The high performance ARM architecture frees the user from the task of developing a complete RISC system.

The customizable logic block allows user to design custom logic and special functions. SPEAr Head200 is optimized for embedded applications and thanks to its high performance can be used for a wide range of different purposes.

### Main blocks description:

- CPU: ARM926EJ-S running at 266 MHz.

- It has:

- MMU

- 32 KB of instruction CACHE

- 16 KB of data CACHE

- 8 KB of instruction TCM (Tightly Coupled Memory)

- 8 KB of data TCM

- AMBA Bus interface

- Coprocessor interface

- JTAG

- ETM9 (Embedded Trace Macro-cell) for debug; large size version.

- Main Bus System: a complete AMBA Bus 2.0 subsystem connects different masters and slaves.

The subsystem includes:

- AHB Bus, for high performance devices

- APB Bus, for low power / lower speed devices connectivity

- Bus Matrix, for improving connection between the peripherals

Bus System supports two masters: the ARM926EJ-S and the Customizable Logic block, connected to AHB Bus. All others blocks are slaves.

- 3. Clock and Reset System: fully programmable block with:

- Separated set-up between clocks of AHB Bus and APB Bus peripherals

- E.M.I. reduction mode, replacing all traditional drop methods for Electro-Magnetic Interference

- Debug mode, compliant with ARM debug status

- 4. Interrupt Controller: the Interrupt Controller has 32 interrupt sources which are prioritized and vectorized.

- 5. On-chip memory: 4 independent static RAM cuts, 4 KB each, are available. They can be used on AHB Bus or directly by the custom logic.

- 6. Dynamic Memory Controller: it is a Multi-Port Memory Controller which is able to connect directly to memory sizes from 16 to 512 Mbits; the data size can be 8 or 16 bits for both DDR and SDRAM, also 32 bits for SDRAM. The external data bus can be maximum 32 bit wide at maximum clock frequency of 133 MHz and have up to 4 chip selects; the accessible memory is 256 MB.

- Internally it handles 7 ports supporting the following masters: AHB Bus, Bus Matrix, 2 USB 2.0 Hosts, USB 2.0 Device, Ethernet MAC, eASIC™ MacroCell.

Product Overview SPEAR-09-H022

The Multi-Port Memory Controller block has a programmable arbitration scheme and the transactions happen on a different layer from the main bus.

- 7. Serial Peripheral Interface: it allows a serial connection to ROM and Flash.

The block is connected as a slave on the main AHB Bus, through the Bus Matrix.

The default bus size is 32 bit wide and the accessible memory is 64 MB at a maximum speed of 50 MHz

- 8. USB 2.0 Hosts: these peripherals are compatible with USB 2.0 High-Speed specification. They can work simultaneously either in Full-Speed or in High-Speed mode.

The peripherals have dedicated channels to the Multi-Port Memory Controller and 4 slave ports for CPU programming.

The PHYs are embedded.

USB 2.0 Device: the peripheral is compatible with USB 2.0 High-Speed specifications.

A dedicated channel connects the peripheral with the Multi-Port Memory Controller and registers.

An USB-Plug Detector block is also available to verify the presence of the VBUS voltage.

The port is provided with the following endpoints on the top of the endpoint 0:

- 3 bulkin / bulkout endpoints

- 2 isochronous endpoints

The PHY is integrated.

10. Ethernet Media Access Control (MAC) 10/100: this peripheral is compatible with IEEE 802.3 standard and supports the MII management interface for the direct configuration of the external PHY.

It is connected to the Multi-Port Memory Controller through a dedicated channel. The Ethernet controller and the configuration registers are accessible from the main AHB Bus.

- 11. ADC: 8 bit resolution, 230 Ksps (Kilo-sample per second), with 16 analog input channels. Connected to APB bus.

- 12. UART's: 3 independent interfaces, up to 115 Kbps each, support Software Flow Control.

Connected to APB bus.

- 13. I<sup>2</sup>C supports Master mode protocol in Low and Full speed. Connected to APB bus.

- 14. 6 General Purpose I/O signals are available for user configuration. Connected to APB bus.

- 15. Embedded features: Real Time Clock, Watchdog, 4 General Purpose Timers. All blocks are interfaced with APB Bus.

- 16. Customizable Logic: it consists of an embedded macro where it is possible to map up to 200K equivalent ASIC gates. The same logic can be alternatively used to implement 32 KBytes of SRAM. Logic gates and RAM bits can be mixed in the same configuration so that processing elements, tightly coupled with embedded memories, can be easily implemented.

The MacroCell has 2 dedicated buses, each of them connected with a 4 channel DMA in order to speed up the data flow with the main memories.

8 interrupt lines and 112 dedicated general purpose I/Os are available.

To allow a simple development of project, customizable logic can be emulated by an external FPGA, where customer can map his logic; FPGA is easy linkable and keeps the access to all on-chip and I/Os interfaces of the macro.

SPEAR-09-H022 Features

### 3 Features

### 3.1 CPU

It is an ARM926EJ-S RISC Processor

- ARM926EJ-S RISC Processor

- f<sub>MAX</sub> 266 MHz (downward scalable)

- Virtual address support with MMU

- 32 KB instruction CACHE (4 way set associative)

- 16 KB data CACHE (4 way set associative)

- 8 KB instruction TCM

- 8 KB data TCM

- Coprocessor interface

- JTAG

- ETM9 (rev 2.2), large size FIFO

### 3.2 Internal bus structures

- Multilayer structure AMBA 2.0 compliant

- f<sub>MAX</sub> 133 MHz

- High speed I/Os with embedded DMA function

## 3.3 Clock system

- Programmable clock generator

- PLL with E.M.I. reduction

- Low Jitter PLL for USB 2.0

## 3.4 Interrupt controller

- IRQ and FIQ interrupt generations

- Support up to 32 standard interrupts

- Support up to 16 vectored interrupts

- Software interrupt generation

## 3.5 Memory system

### 3.5.1 Memory on chip

16 KBytes single-port SRAM embedded in the eASIC™ MacroCell.

It can be used on AHB Bus or directly by the custom logic.

Features SPEAR-09-H022

#### 3.5.2 SPI

- 4 chip selects for asynchronous devices (ROM, Flash)

- Supports Normal mode 20 MHz and Fast mode 50 MHz

- AHB slave

- Accessible memory: 64 MB

- 8 / 16 / 32 bit widths

- Programmable wait states

### 3.5.3 Multi-port memory controller

- Maximum clock frequency 133 MHz

- Support up to 7 AHB master requests

- AHB slave

- Support for 8, 16 and 32 bit wide SDRAM

- Support for 8 and 16 bit wide DDR

- 4 chip selects

- Physical addressable memory up to 256 MB

- Memory clock tuning to match the timing of different memory vendors

## 3.6 High speed connectivity

#### 3.6.1 USB 2.0 host

- 2 USB 2.0 Host controllers with their UTMI PHY port embedded

- High-Speed / Full-Speed / Low-Speed modes USB 2.0 complaint

- DMA FIFO

- 2 AHB slaves for configuration and FIFO access

- 2 AHB masters for data transfer

#### 3.6.2 USB 2.0 device

- UDC 2.0 controller with embedded PHY

- High-Speed / Full-Speed / Low-Speed modes USB 2.0 complaint

- USB Self-Power mode

- DMA FIFO

- Master interface for DMA transfer to DRAM memory

- AHB slaves for: configuration, Plug autodetect

- Endpoints on the top of endpoint 0: 3 bulkin / bulkout, 2 isochronous

SPEAR-09-H022 Features

#### 3.6.3 Ethernet 10/100

- MAC110 controller compliant with IEEE 802.3 standard

- Supporting MII 10/100 Mbits/s

- MII management protocol interface

- TX FIFO (512x36 Dual Port)

- RX FIFO (512x36 Dual Port)

- Master interface for DMA transfer to DRAM memory

- AHB slave for configuration

## 3.7 Low speed connectivity

#### 3.7.1 UART

- Support for 8 bit serial data TX and RX

- Selectable 2 / 1 Stop bits

- Selectable Even, Odd and No Parity

- Parity, Overrun and Framing Error detector

- Max transfer rate: 115 Kbps

### 3.7.2 $I^2C$

- Standard I<sup>2</sup>C mode (100 KHz) / Fast I<sup>2</sup>C mode (400 KHz)

- Master interface only

- Master functions control all I<sup>2</sup>C bus specific sequencing, protocol, arbitration and timing

- Detection of bus errors during transfers

## 3.8 General purpose I/Os

6 programmable GP I/Os

## 3.9 Analog to Digital Converter

- 8 bit resolutions

- 230 Ksps

- 16 analog input channels (0 3.3 V)

- INL ± 1 LSB

- DNL ± 0.5 LSB

- Programmable conversion speed minimum conversion time 4.3 μs

Features SPEAR-09-H022

#### 3.10 Real time clock

- Real time clock-calendar (RTC)

- 14 digit (YYYY MM DD hh mm ss) precision

- Clocked by 32.768 KHz low power clock input

- Separated power supply (1.2 V)

## 3.11 Watchdog timer

- Programmable 16 bit Watchdog timer with reset output signal (more than 200 system clock period to initial peripheral devices)

- Programmable period 1 ~ 10 sec.

- For recovery from unexpected system Hang-up

## 3.12 General purpose timers

- Four 16 bit timers with 8 bit prescaler

- Frequency range: 3.96 Hz 66.5 MHz

- Operating mode: Auto Reload and Single Shot

## 3.13 Customizable logic

- 200K equivalent ASIC gate (16K LUT equivalent) configurable either custom logic or 32 KBytes single-port SRAM or mixing logic and RAM

- 2 dedicated buses, each of them connected with a 4 channel DMA

- 8 interrupt lines (level type) available

- 112 dedicated GP I/Os

- Single VIA mask configurable interconnections

- Emulation by an external FPGA, keeping on-chip and I/O interfaces

SPEAR-09-H022 **Block diagram**

#### **Block diagram** 4

Pin description SPEAR-09-H022

# 5 Pin description

## 5.1 Functional pin groups

With reference to *Figure 20*. Package schematic -*Section 26*, here follows the pin list, sorted by their belonging IP. All supply and ground pins are classified as power signals and gathered in the *Table 2*.

Table 1. Pin description by functional groups

| Group | Signal Name   | Ball | Direction | Function                                         | Pin Type                                           |  |

|-------|---------------|------|-----------|--------------------------------------------------|----------------------------------------------------|--|

|       | AIN[0]        | V20  |           |                                                  |                                                    |  |

|       | AIN[1]        | V19  |           |                                                  |                                                    |  |

|       | AIN[2]        | V18  |           |                                                  |                                                    |  |

|       | AIN[3]        | V17  |           |                                                  |                                                    |  |

|       | AIN[4]        | V16  |           |                                                  |                                                    |  |

|       | AIN[5]        | T22  |           |                                                  |                                                    |  |

|       | AIN[6]        | T21  |           |                                                  |                                                    |  |

|       | AIN[7]        | T19  | loout     | ADC analog input shannel                         |                                                    |  |

| ADC   | AIN[8]        | P18  | Input     | ADC analog input channel                         | Analog buffer,<br>3.3 V capable                    |  |

|       | AIN[9]        | N18  |           |                                                  |                                                    |  |

|       | AIN[10]       | M18  |           |                                                  |                                                    |  |

|       | AIN[11]       | L18  |           |                                                  |                                                    |  |

|       | AIN[12]       | U22  |           |                                                  |                                                    |  |

|       | AIN[13]       | U21  |           |                                                  |                                                    |  |

|       | AIN[14]       | U20  |           |                                                  |                                                    |  |

|       | AIN[15]       | U19  |           |                                                  |                                                    |  |

|       | TEST_OUT      | T20  | Output    | ADC output test pad                              |                                                    |  |

|       | TEST0         | E22  |           |                                                  |                                                    |  |

|       | TEST1         | E21  | lanat     | Test configuration port.                         | TTL input buffer,                                  |  |

|       | TEST2         | D22  | Input     | For the functional mode they have to be set to 0 | 3.3 V capable,<br>with Pull Down                   |  |

| DEBUG | TEST3         | D21  |           |                                                  |                                                    |  |

|       | PLL_BYPASS    | H5   | Input     | Enable / disable PLL bypass                      | TTL Schmitt trigger input buffer, 3.3 V capable    |  |

|       | eASICGP_IO[0] | E1   |           |                                                  | TTL bidirectional                                  |  |

| eASIC | eASICGP_IO[1] | F2   | I/O       | eASIC general purpose IO                         | buffer,<br>3.3 V capable,<br>4 mA drive capability |  |

SPEAR-09-H022 Pin description

Table 1. Pin description by functional groups (continued)

| Group | Signal Name    | Ball | Direction | Function                 | Pin Type                  |

|-------|----------------|------|-----------|--------------------------|---------------------------|

|       | eASICGP_IO[2]  | G3   | I/O       |                          |                           |

|       | eASICGP_IO[3]  | D1   |           |                          |                           |

|       | eASICGP_IO[4]  | E2   |           |                          |                           |

|       | eASICGP_IO[5]  | C1   |           |                          |                           |

|       | eASICGP_IO[6]  | F3   |           |                          |                           |

|       | eASICGP_IO[7]  | D2   |           |                          |                           |

|       | eASICGP_IO[8]  | B1   |           |                          |                           |

|       | eASICGP_IO[9]  | G4   |           |                          |                           |

|       | eASICGP_IO[10] | E3   |           |                          |                           |

|       | eASICGP_IO[11] | C2   |           |                          |                           |

|       | eASICGP_IO[12] | A1   |           |                          |                           |

|       | eASICGP_IO[13] | F4   |           |                          |                           |

|       | eASICGP_IO[14] | D3   |           |                          |                           |

|       | eASICGP_IO[15] | B2   |           |                          |                           |

|       | eASICGP_IO[16] | A2   |           |                          |                           |

|       | eASICGP_IO[17] | СЗ   |           |                          | TTL bidirectional         |

| eASIC | eASICGP_IO[18] | E4   |           | eASIC general purpose IO | buffer,<br>3.3 V capable, |

|       | eASICGP_IO[19] | G5   |           |                          | 4 mA drive capability     |

|       | eASICGP_IO[20] | В3   |           |                          |                           |

|       | eASICGP_IO[21] | D4   |           |                          |                           |

|       | eASICGP_IO[22] | F5   |           |                          |                           |

|       | eASICGP_IO[23] | А3   |           |                          |                           |

|       | eASICGP_IO[24] | E5   |           |                          |                           |

|       | eASICGP_IO[25] | C4   |           |                          |                           |

|       | eASICGP_IO[26] | A4   |           |                          |                           |

|       | eASICGP_IO[27] | B4   |           |                          |                           |

|       | eASICGP_IO[28] | C5   |           |                          |                           |

|       | eASICGP_IO[29] | D5   |           |                          |                           |

|       | eASICGP_IO[30] | B5   |           |                          |                           |

|       | eASICGP_IO[31] | A5   |           |                          |                           |

|       | eASICGP_IO[32] | E6   |           |                          |                           |

|       | eASICGP_IO[33] | D6   |           |                          |                           |

|       | eASICGP_IO[34] | B6   |           |                          |                           |

Pin description SPEAR-09-H022

Table 1. Pin description by functional groups (continued)

| Group | Signal Name    | Ball | Direction   | Function                 | Pin Type                                                       |

|-------|----------------|------|-------------|--------------------------|----------------------------------------------------------------|

|       | eASICGP_IO[35] | C6   |             |                          |                                                                |

|       | eASICGP_IO[36] | A7   |             |                          |                                                                |

|       | eASICGP_IO[37] | A6   |             |                          |                                                                |

|       | eASICGP_IO[38] | C7   |             |                          |                                                                |

|       | eASICGP_IO[39] | В7   |             |                          |                                                                |

|       | eASICGP_IO[40] | E7   |             |                          |                                                                |

|       | eASICGP_IO[41] | D7   |             |                          |                                                                |

|       | eASICGP_IO[42] | E8   |             |                          |                                                                |

|       | eASICGP_IO[43] | A8   |             |                          |                                                                |

|       | eASICGP_IO[44] | B8   |             |                          |                                                                |

|       | eASICGP_IO[45] | C8   |             |                          |                                                                |

|       | eASICGP_IO[46] | D8   |             |                          |                                                                |

|       | eASICGP_IO[47] | В9   |             |                          |                                                                |

|       | eASICGP_IO[48] | A9   | -<br>-<br>- | eASIC general purpose IO | TTL bidirectional buffer, 3.3 V capable, 4 mA drive capability |

|       | eASICGP_IO[49] | A10  |             |                          |                                                                |

| eASIC | eASICGP_IO[50] | C9   | I/O         |                          |                                                                |

|       | eASICGP_IO[51] | D9   |             |                          |                                                                |

|       | eASICGP_IO[52] | B10  |             |                          |                                                                |

|       | eASICGP_IO[53] | A11  |             |                          |                                                                |

|       | eASICGP_IO[54] | E9   |             |                          |                                                                |

|       | eASICGP_IO[55] | C10  |             |                          |                                                                |

|       | eASICGP_IO[56] | B11  |             |                          |                                                                |

|       | eASICGP_IO[57] | D10  |             |                          |                                                                |

|       | eASICGP_IO[58] | A12  |             |                          |                                                                |

|       | eASICGP_IO[59] | C11  |             |                          |                                                                |

|       | eASICGP_IO[60] | B12  |             |                          |                                                                |

|       | eASICGP_IO[61] | A13  |             |                          |                                                                |

|       | eASICGP_IO[62] | E10  |             |                          |                                                                |

|       | eASICGP_IO[63] | D11  |             |                          |                                                                |

|       | eASICGP_IO[64] | C12  |             |                          |                                                                |

|       | eASICGP_IO[65] | B13  |             |                          |                                                                |

SPEAR-09-H022 Pin description

Table 1. Pin description by functional groups (continued)

| Group | Signal Name    | Ball | Direction | Function                 | Pin Type                                                       |

|-------|----------------|------|-----------|--------------------------|----------------------------------------------------------------|

|       | eASICGP_IO[66] | A14  |           |                          |                                                                |

|       | eASICGP_IO[67] | A15  | =         |                          |                                                                |

|       | eASICGP_IO[68] | B14  |           |                          |                                                                |

|       | eASICGP_IO[69] | C13  |           |                          |                                                                |

|       | eASICGP_IO[70] | D12  | -         |                          |                                                                |

|       | eASICGP_IO[71] | E11  |           |                          |                                                                |

|       | eASICGP_IO[72] | A16  |           |                          |                                                                |

|       | eASICGP_IO[73] | B15  |           |                          |                                                                |

|       | eASICGP_IO[74] | C14  |           |                          |                                                                |

|       | eASICGP_IO[75] | D13  |           |                          |                                                                |

|       | eASICGP_IO[76] | A17  |           |                          |                                                                |

|       | eASICGP_IO[77] | B16  |           |                          |                                                                |

|       | eASICGP_IO[78] | E12  |           |                          |                                                                |

|       | eASICGP_IO[79] | C15  |           |                          |                                                                |

|       | eASICGP_IO[80] | A18  |           | eASIC general purpose IO | TTL bidirectional buffer, 3.3 V capable, 4 mA drive capability |

|       | eASICGP_IO[81] | B17  |           |                          |                                                                |

| eASIC | eASICGP_IO[82] | D14  | I/O       |                          |                                                                |

|       | eASICGP_IO[83] | A19  |           |                          |                                                                |

|       | eASICGP_IO[84] | C16  |           |                          |                                                                |

|       | eASICGP_IO[85] | E13  |           |                          |                                                                |

|       | eASICGP_IO[86] | B18  |           |                          |                                                                |

|       | eASICGP_IO[87] | D15  |           |                          |                                                                |

|       | eASICGP_IO[88] | C17  |           |                          |                                                                |

|       | eASICGP_IO[89] | B19  |           |                          |                                                                |

|       | eASICGP_IO[90] | C18  |           |                          |                                                                |

|       | eASICGP_IO[91] | E14  |           |                          |                                                                |

|       | eASICGP_IO[92] | D16  |           |                          |                                                                |

|       | eASICGP_IO[93] | B21  |           |                          |                                                                |

|       | eASICGP_IO[94] | C19  |           |                          |                                                                |

|       | eASICGP_IO[95] | D17  |           |                          |                                                                |

|       | eASICGP_IO[96] | E15  |           |                          |                                                                |

|       | eASICGP_IO[97] | C20  |           |                          |                                                                |

|       | eASICGP_IO[98] | D18  |           |                          |                                                                |

Pin description SPEAR-09-H022

Table 1. Pin description by functional groups (continued)

| Group    | Signal Name     | Ball | Direction | Function                          | Pin Type                                                       |

|----------|-----------------|------|-----------|-----------------------------------|----------------------------------------------------------------|

|          | eASICGP_IO[99]  | E16  |           |                                   |                                                                |

|          | eASICGP_IO[100] | D19  |           |                                   |                                                                |

|          | eASICGP_IO[101] | E17  |           |                                   |                                                                |

|          | eASICGP_IO[102] | D20  |           |                                   |                                                                |

|          | eASICGP_IO[103] | E18  |           |                                   |                                                                |

|          | eASICGP_IO[104] | E19  |           |                                   | TTL bidirectional                                              |

|          | eASICGP_IO[105] | F18  |           | eASIC general purpose IO          | buffer,                                                        |

|          | eASICGP_IO[106] | E20  |           | eAolo general purpose lo          | 3.3 V capable,                                                 |

|          | eASICGP_IO[107] | F20  | I/O       |                                   | 4 mA drive capability                                          |

| eASIC    | eASICGP_IO[108] | F19  |           |                                   |                                                                |

|          | eASICGP_IO[109] | G19  |           |                                   |                                                                |

|          | eASICGP_IO[110] | G20  |           |                                   |                                                                |

|          | eASICGP_IO[111] | G18  |           |                                   | TTL bidirectional buffer, 3.3 V capable, 8 mA drive capability |

|          | eASIC_EXT_CLOCK | H18  |           |                                   |                                                                |

|          | eASIC_PI_CLOCK  | R18  |           | eAISC Program Interface out clock |                                                                |

|          | eASIC_CLK       | G2   |           | eASIC output clock                |                                                                |

|          | CONFIG_DEVEL    | A20  | Input     | External FPGA emulation mode      | TTL input buffer, 3.3 V capable with Pull Down                 |

|          | TX_CLK          | H19  | Input     | Ethernet input TX clock           |                                                                |

|          | TXD[0]          | J18  |           | Ethernet TX output data           |                                                                |

|          | TXD[1]          | J19  |           |                                   |                                                                |

|          | TXD[2]          | K18  | Output    |                                   |                                                                |

|          | TXD[3]          | J20  |           |                                   |                                                                |

|          | TX_EN           | J21  |           | Ethernet TX enable                | 1                                                              |

|          | CRS             | J22  |           | Carrier sense input               | TTL bidirectional buffer,                                      |

| Ethernet | COL             | K19  |           | Collision detection input         | 3.3 V capable,                                                 |

|          | RX_CLK          | K20  | Input     | Ethernet input RX clock           | 4 mA drive capability, with Pull Down                          |

|          | RXD[0]          | K21  | Прис      |                                   | Will I dii Down                                                |

|          | RXD[1]          | K22  |           | Ethernet RX input data            |                                                                |

|          | RXD[2]          | L19  |           | Ememer na input data              |                                                                |

|          | RXD[3]          | L20  | Input     |                                   |                                                                |

|          | RX_DV           | L21  | Input     | Data valid on RX                  |                                                                |

|          | RX_ER           | L22  | Input     | Data error detected               |                                                                |

SPEAR-09-H022 Pin description

Table 1. Pin description by functional groups (continued)

| Group            | Signal Name | Ball                | Direction | Function                                                                | Pin Type                                                                                   |

|------------------|-------------|---------------------|-----------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Ethernet         | MDC         | M19                 | Output    | Output timing reference for MDIO                                        | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>4 mA drive capability,<br>with Pull Down |

|                  | MDIO        | M20                 | I/O       | I/O data to PHY                                                         |                                                                                            |

|                  | GP_IO[0]    | R22                 |           |                                                                         |                                                                                            |

|                  | GP_IO[1]    | R21                 |           |                                                                         | TTL bidirectional                                                                          |

| GPI/Os           | GP_IO[2]    | R20                 | I/O       | Canaval Duranaa IO                                                      | buffer,                                                                                    |

| GPI/OS           | GP_IO[3]    | R19                 | 1/0       | General Purpose IO                                                      | 3.3 V capable,                                                                             |

|                  | GP_IO[4]    | P22                 |           |                                                                         | 8 mA drive capability                                                                      |

|                  | GP_IO[5]    | P21                 |           |                                                                         |                                                                                            |

|                  | SDA         | M21                 |           |                                                                         | TTL bidirectional                                                                          |

| I <sub>2</sub> C | SCL         | M22                 | I/O       | I <sup>2</sup> C serial data                                            | buffer, 3.3 V capable, 4 mA drive capability, with Pull Up                                 |

|                  | TDO         | A21 Output Jtag TDO |           | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>4 mA drive capability |                                                                                            |

| JTAG             | TDI         | A22                 | Input     | Jtag TDI                                                                | TTI hidiractional                                                                          |

| 01710            | TMS         | B20                 | Input     | Jtag TMS                                                                | TTL bidirectional buffer,                                                                  |

|                  | RTCK        | B22                 | Output    | Jtag output clock                                                       | 3.3 V capable,                                                                             |

|                  | тск         | C21                 | Input     | Jtag clock                                                              | 4 mA drive capability, with Pull Up                                                        |

|                  | nTRST       | C22                 | Output    | Jtag reset                                                              | with all Op                                                                                |

| MASTER           | MCLK_in     | T1                  | Input     | 12 MHz input crystal                                                    | Oscillator                                                                                 |

| CLOCK            | MCLK_out    | U1                  | Output    | 12 MHz output crystal                                                   | 3.3 V capable                                                                              |

| MASTER<br>RESET  | MRESET      | H4                  | Input     | Master reset                                                            | TTL Schmitt trigger input buffer, 3.3 V capable                                            |

|                  | MPMCDATA[0] | AA12                |           |                                                                         |                                                                                            |

|                  | MPMCDATA[1] | Y12                 |           |                                                                         |                                                                                            |

| MPMC             | MPMCDATA[2] | W12                 | I/O       |                                                                         | LVTTL / SSTL                                                                               |

| INITINIC         | MPMCDATA[3] | AB13                | 1/0       | DDR / SDRAM data                                                        | ClassII bidirectional buffer                                                               |

|                  | MPMCDATA[4] | AA13                |           |                                                                         |                                                                                            |

|                  | MPMCDATA[5] | Y13                 |           |                                                                         |                                                                                            |

21/71

Pin description SPEAR-09-H022

Table 1. Pin description by functional groups (continued)

| Group | Signal Name    | Ball | Direction | Function           | Pin Type                                                                |

|-------|----------------|------|-----------|--------------------|-------------------------------------------------------------------------|

|       | MPMCDATA[6]    | W13  |           |                    |                                                                         |

|       | MPMCDATA[7]    | AA14 |           |                    |                                                                         |

|       | MPMCDATA[8]    | AA16 |           |                    |                                                                         |

|       | MPMCDATA[9]    | AB18 |           |                    |                                                                         |

|       | MPMCDATA[10]   | AB19 | I/O       | DDR / SDRAM data   | LVTTL / SSTL<br>ClassII bidirectional                                   |

|       | MPMCDATA[11]   | AB20 | 1/0       | DDH / SDHAIVI data | buffer                                                                  |

|       | MPMCDATA[12]   | AB21 |           |                    |                                                                         |

|       | MPMCDATA[13]   | AA21 |           |                    |                                                                         |

|       | MPMCDATA[14]   | AB22 |           |                    |                                                                         |

|       | MPMCDATA[15]   | AA22 |           |                    |                                                                         |

|       | MPMCDATA[16]   | AA18 |           |                    |                                                                         |

|       | MPMCDATA[17]   | AA17 |           |                    |                                                                         |

|       | MPMCDATA[18]   | Y22  | 1/0       | SDRAM data         | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>8 mA drive capability |

|       | MPMCDATA[19]   | Y21  |           |                    |                                                                         |

|       | MPMCDATA[20]   | Y20  |           |                    |                                                                         |

|       | MPMCDATA[21]   | Y19  |           |                    |                                                                         |

|       | MPMCDATA[22]   | Y18  |           |                    |                                                                         |

| MPMC  | MPMCDATA[23]   | Y17  |           |                    |                                                                         |

|       | MPMCDATA[24]   | Y16  | 1/0       |                    |                                                                         |

|       | MPMCDATA[25]   | W22  |           |                    |                                                                         |

|       | MPMCDATA[26]   | W21  |           |                    |                                                                         |

|       | MPMCDATA[27]   | W20  | 1         |                    |                                                                         |

|       | MPMCDATA[28]   | W19  |           |                    |                                                                         |

|       | MPMCDATA[29]   | W18  |           |                    |                                                                         |

|       | MPMCDATA[30]   | W17  |           |                    |                                                                         |

|       | MPMCDATA[31]   | W16  |           |                    |                                                                         |

|       | MPMCADDROUT[0] | AB8  |           |                    |                                                                         |

|       | MPMCADDROUT[1] | AA8  |           |                    |                                                                         |

|       | MPMCADDROUT[2] | Y8   |           |                    |                                                                         |

|       | MPMCADDROUT[3] | W8   |           |                    | LVTTL / SSTL                                                            |

|       | MPMCADDROUT[4] | AB9  | Output    | DDR / SDRAM data   | ClassII bidirectional                                                   |

|       | MPMCADDROUT[5] | AA9  |           |                    | buffer                                                                  |

|       | MPMCADDROUT[6] | Y9   |           |                    |                                                                         |

|       | MPMCADDROUT[7] | W9   |           |                    |                                                                         |

|       | MPMCADDROUT[8] | AB10 |           |                    |                                                                         |

SPEAR-09-H022 Pin description

Table 1. Pin description by functional groups (continued)

| Group | Signal Name     | Ball       | Direction | Function                                                                                              | Pin Type                                                                |

|-------|-----------------|------------|-----------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

|       | MPMCADDROUT[9]  | AA10       |           |                                                                                                       |                                                                         |

|       | MPMCADDROUT[10] | Y10        |           |                                                                                                       |                                                                         |

|       | MPMCADDROUT[11] | W10        |           | DDR / SDRAM data                                                                                      |                                                                         |

|       | MPMCADDROUT[12] | AB11       |           | DDN / SDNAIVI dala                                                                                    |                                                                         |

|       | MPMCADDROUT[13] | AA11       |           |                                                                                                       |                                                                         |

|       | MPMCADDROUT[14] | Y11        |           |                                                                                                       | LVTTL / SSTL<br>ClassII bidirectional                                   |

|       | nMPMCDYCSOUT[0] | AB6        |           |                                                                                                       | buffer                                                                  |

|       | nMPMCDYCSOUT[1] | AA6        |           | DDR / SDRAM chip select                                                                               |                                                                         |

|       | nMPMCDYCSOUT[2] | Y6         |           | DDIT/ ODITANI CITIP Select                                                                            |                                                                         |

|       | nMPMCDYCSOUT[3] | W6         |           |                                                                                                       |                                                                         |

|       | MPMCCKEOUT[0]   | W11        |           | DDR / SDRAM clock enable                                                                              |                                                                         |

|       | MPMCCKEOUT[1]   | AB12       |           | output                                                                                                |                                                                         |

|       | MPMCCLKOUT[0]   | AB17       |           | DDR / SDRAM output clock 1                                                                            | LVTTL / SSTL<br>ClassII bidirectional<br>differential<br>buffer         |

|       | nMPMCCLKOUT[0]  | AB16       | Output    | DDR / SDRAM output clock 1 neg.                                                                       |                                                                         |

| MPMC  | MPMCCLKOUT[1]   | AB15       |           | DDR / SDRAM output clock 2                                                                            |                                                                         |

|       | nMPMCCLKOUT[1]  | AB14       |           | DDR / SDRAM output clock 2 neg.                                                                       | buller                                                                  |

|       | MPMCDQMOUT[0]   | Y14        |           | DDR / SDRAM data mask out                                                                             | LVTTL / SSTL<br>ClassII bidirectional                                   |

|       | MPMCDQMOUT[1]   | W15        |           |                                                                                                       | buffer                                                                  |

|       | MPMCDQMOUT[2]   | AA19       |           | SDRAM data mask out                                                                                   | TTL bidirectional buffer,                                               |

|       | MPMCDQMOUT[3]   | AA20       |           |                                                                                                       | 3.3 V capable,<br>8 mA drive capability                                 |

|       | MPMCDQS[0]      | AA15       |           | DDR data strobe                                                                                       |                                                                         |

|       | MPMCDQS[1]      | Y15        |           | DDN data strobe                                                                                       | LVTTL / SSTL                                                            |

|       | nMPMCCASOUT     | <b>Y</b> 7 |           | DDR / SDRAM CAS output strobe                                                                         | ClassII bidirectional                                                   |

|       | nMPMCRASOUT     | AA7        |           | DDIT/ 3DITANI OAS output strobe                                                                       | buffer                                                                  |

|       | nMPMCWEOUT      | AB7        |           | DDR / SDRAM write enable                                                                              |                                                                         |

|       | SSTL_VREF       | W14        | Input     | Voltage reference<br>SSTL / CMOS mode.<br>This pin is used both as logic state<br>and as power supply | Analog buffer, 3.3 V capable                                            |

| RTC   | RTCXO           | AB5        | Output    | 32 KHz output crystal                                                                                 | Oscillator 1.2 V                                                        |

| HIC   | RTCXI           | AB4        | Input     | 32 KHz input crystal                                                                                  | capable                                                                 |

| SMI   | SMINCS[0]       | G22        | Output    | Serial Flash chip select                                                                              | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>4 mA drive capability |

Pin description SPEAR-09-H022

Table 1. Pin description by functional groups (continued)

| Group | Signal Name            | Ball       | Direction | Function                  | Pin Type                                                                                   |

|-------|------------------------|------------|-----------|---------------------------|--------------------------------------------------------------------------------------------|

|       | SMINCS[1]<br>SMINCS[2] | G21<br>F22 |           | Serial Flash chip select  | TTL bidirectional buffer,                                                                  |

|       | SMINCS[3]              | F21        |           | ·                         | <ul><li>3.3 V capable,</li><li>4 mA drive capability</li></ul>                             |

|       | SMICLK                 | H20        | Output    | Serial Flash output clock | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>8 mA drive capability                    |

| SMI   | SMIDATAIN              | H21        | Input     | Serial Flash data in      | TTL bidirectional buffer, 3.3 V capable, 8 mA drive capability, with Pull Up               |

|       | SMIDATAOUT             | H22        | Output    | Serial Flash data out     | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>8 mA drive capability                    |

|       | UART1_RXD              | N19        | Input     | Uart1 RX data             | TTL bidirectional buffer, 3.3 V capable, 4 mA drive capability, with Pull Down             |

|       | UART1_TXD              | N20        | Output    | Uart1 TX data             | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>4 mA drive capability                    |

| UARTs | UART2_RXD              | N21        | Input     | Uart2 RX data             | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>4 mA drive capability,<br>with Pull Down |

|       | UART2_TXD              | N22        | Output    | Uart2 TX data             | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>4 mA drive capability                    |

|       | UART3_RXD              | P19        | Input     | Uart3 RX data             | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>4 mA drive capability,<br>with Pull Down |

|       | UART3_TXD              | P20        | Output    | Uart3 TX data             | TTL bidirectional<br>buffer,<br>3.3 V capable,<br>4 mA drive capability                    |

SPEAR-09-H022 Pin description

Table 1. Pin description by functional groups (continued)

| Group | Signal Name | Ball                             | Direction             | Function                                                       | Pin Type                                                                       |

|-------|-------------|----------------------------------|-----------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|

|       | DMNS        | W1                               | I/O                   | D - port of USB device                                         |                                                                                |

|       | DPLS        | V1                               | I/O                   | D + port of USB device                                         |                                                                                |

|       | HOST1_DP    | P1                               | I/O                   | D - port of USB host1                                          | Analog buffer, 5 V                                                             |

|       | HOST1_DM    | N1                               | I/O                   | D + port of USB host1                                          | tolerant                                                                       |

|       | HOST2_DP    | L1                               | I/O                   | D - port of USB host2                                          |                                                                                |

|       | HOST2_DM    | K1                               | I/O                   | D + port of USB host2                                          |                                                                                |

|       | HOST1_VBUS  | H2                               | Output                | USB host1 VBUS signal                                          | TTL bidirectional                                                              |

|       | HOST2_VBUS  | H1                               | Output                | USB host2 VBUS signal                                          | buffer, 3.3 V capable, 4 mA drive capability                                   |

| USBs  | OVERCURH1   | G1                               | I/O                   | USB host1 overcurrent                                          | TTL bidirectional buffer, 3.3 V capable, 4 mA drive capability, with Pull Down |

|       | OVERCURH2   | RH2 F1 I/O USB host2 overcurrent | USB host2 overcurrent | TTL bidirectional buffer, 3.3 V capable, 4 mA drive capability |                                                                                |

|       | VBUS        | НЗ                               | I/O                   | USB device VBUS signal                                         | TTL bidirectional buffer, 3.3 V capable, 4 mA drive capability, with Pull Down |

|       | RREF        | K5                               | Input                 | USB reference resistor                                         | Analog buffer,<br>3.3 V capable                                                |

Table 2. Pins belonging to POWER group

| Group | Signal Name    | Ball                | Function                                    |  |

|-------|----------------|---------------------|---------------------------------------------|--|

|       | vdde3v3        | Note <sup>(1)</sup> | Digital 3.3 V power                         |  |

|       | vdd            | Note (2)            | Digital 1.2 V power                         |  |

|       | gnde           | Note (3)            | Digital ground                              |  |

|       | vdd2v5         | Note (4)            | DDR / SDR digital 3.3 / 2.5V power          |  |

|       | thermal_gnd    | Note (5)            | Thermal Pad                                 |  |

| POWER | anavdd_3v3_adc | V22                 | Dedicated ADC 3.3 V power                   |  |

|       | anagnd_3v3_adc | U18                 | Dedicated ADC ground                        |  |

|       | VREFP_adc      | V21                 | ADC positive reference Voltage              |  |

|       | VREFN_adc      | T18                 | ADC pegative reference Voltage              |  |

|       | vdd_dith       | W7                  | DDR / SDR dedicated digital PLL 3.3 V power |  |

|       | vss_dith       | V7                  | DRR / SDR dedicated digital PLL ground      |  |

5/

Pin description SPEAR-09-H022

Table 2. Pins belonging to POWER group (continued)

| Group | Signal Name        | Ball  | Function                                                 |

|-------|--------------------|-------|----------------------------------------------------------|

|       | CCTI VDEE          | W14   | Voltage reference SSTL / CMOS mode.                      |

|       | SSTL_VREF          | VV 14 | This pin is used both as logic state and as power supply |

|       | vdd1v2_date_osci   | AB2   | 1.2 V dedicated power for RTC                            |

|       | vdd_date_osci      | AA5   | 1.2 V dedicated power for RTC                            |

|       | gnd_date_osci      | AA4   | Dedicated digital ground for RTC                         |

|       | gnde_date_osci     | AB3   | Dedicated digital ground for RTC                         |

|       | anavdd_3v3_pll1600 | R2    | Dedicated USB PLL analog 3.3 V power                     |

|       | anagnd_3v3_pll1600 | P4    | Dedicated USB PLL analog ground                          |

|       | digvdd_1v2_pll1600 | R4    | Dedicated USB PLL digital 1.2 V power                    |

|       | diggnd_1v2_pll1600 | U2    | Dedicated USB PLL digital ground                         |

|       | vddl_1v2_d         | W3    | Dedicated USB 1.2 V power                                |

|       | vddb_1v2_d         | U4    | Dedicated USB 1.2 V power                                |

|       | vddc_1v2_d         | U3    | Dedicated USB 1.2 V power                                |

|       | vdd_usb            | P2    | Dedicated USB 1.2 V power                                |

|       | vddc_1v2_h1        | N5    | Dedicated USB 1.2 V power                                |

|       | vddb_1v2_h1        | N3    | Dedicated USB 1.2 V power                                |

|       | vddl_1v2_h1        | L4    | Dedicated USB 1.2 V power                                |

| POWER | vddc_1v2_h0        | K4    | Dedicated USB 1.2 V power                                |

|       | vddb_1v2_h0        | K3    | Dedicated USB 1.2 V power                                |

|       | vddl_1v2_h0        | J4    | Dedicated USB 1.2 V power                                |