intersil

# EL1056A, EL1056

contact our Technical Support Center at Contact out recurrical Support Verner at 1-888-INTERSIL or WWW.intersil.com/tsc March 1993, Rev. A

FN7035

# Monolithic High-Speed Pin Driver

The EL1056 is designed to drive highquality test signals into close or terminated loads. It has a dispersion of

OBSOLETE PRODUCT NO RECOMMENDED REPLACEMENT

250ps or less — whether due to signal size or direction of edge. It can output a very wide 24V output span, encompassing all logic families as well as analog levels. The EL1056 is fabricated in Elantec's oxide isolated process, which eliminates the possibility of latch-up and provides a very durable circuit.

The output can be turned off in two ways; the OE pins allow the output to be put in a high-impedance state which makes the output look like a large resistance in parallel with 3pF, even for back-driven signals with as much as  $2.5V/\mu s$  slew rate. The E pins put the output in an even higher impedance state, guaranteed to 150nA leakage in the EL1056A. This allows accurate measurements on the bus without disconnecting the EL1056 with a relay.

The EL1056 incorporates an output current sense which can warn the system controller that excessive output current is flowing. The trip point is set by two external resistors.

EL1056A, EL1056

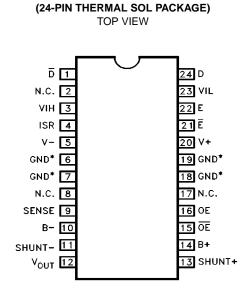

## Pinout

\*and Heat-spreader

### Features

- Wide ±12V output levels

- 250ps dispersion

- 3ns delay times

- 1V/ns slew rate—adjustable

- Low overshoot and aberrations in 50Ω systems

- Three-state output

- Power-down mode reduces output leakage to nanoamperes

- Overcurrent sense flag available to protect internal output devices

- · Buffered analog inputs

- · Differential logic inputs are compatible with ECL, TTL, and CMOS

# Applications

- Memory testers

- · ASIC testers

- Functional board testers

- Analog/digital incoming component verifiers

- Logic emulators

# Ordering Information

| PART<br>NUMBER | TEMP.<br>RANGE | PACKAGE            | PKG. NO. |  |

|----------------|----------------|--------------------|----------|--|

| EL1056CM       | 0°C to +75°C   | 24-Pin Thermal SOL | MDP0027  |  |

| EL1056ACM      | 0°C to +75°C   | 24-Pin Thermal SOL | MDP0027  |  |

### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| VS              | Voltage between V+ and V                  | Е, <u>Е</u>     | Input Voltages V- to V+ or                      |

|-----------------|-------------------------------------------|-----------------|-------------------------------------------------|

| V-              | Supply Voltage18V                         |                 |                                                 |

| B+              | Supply VoltageVINH to V+                  | Sense           | Output Voltage V- to V+                         |

| B-              | Supply VoltageV- to V <sub>INL</sub>      | VINH            | Input VoltageV <sub>INL</sub> -0.3V to B+       |

| I <sub>SR</sub> | Input Current                             | VINL            | Input Voltage B- to V <sub>INH</sub> +0.3V      |

| V <sub>SR</sub> | Input Voltage, Power-Down Mode0.3V to +6V | IOUT            | Output Current                                  |

| Shunt+          | Input Voltage (B+) -5V to B+              | TJ              | Junction Temperature150°C                       |

| Shunt-          | Input VoltageB- to (B-) +5V               | TA              | Operating Ambient Temperature Range0°C to +75°C |

| Data, Data      | Input Voltages V- to V+ or                | T <sub>ST</sub> | Storage Temperature65°C to +150°C               |

|                 | ±6V Differential                          | PD              | Power Dissipation ( $T_A = 25^{\circ}C$ )       |

| OE, OE          | Input Voltages V- to V+ or                |                 | (See Curves)                                    |

|                 | ±6V Differential                          |                 |                                                 |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$ .

### **DC Electrical Specifications**

$T_A = 25^{\circ}C$ , V+ = B+ =15V, V- = B- = -10V, Rshunt+ = Rshunt- =  $6.5\Omega$ , no load. Data, E, and OE from

| PARAMETER            | DESCRIPTION                                                                                                                                    | MIN          | TYP          | MAX       | UNITS    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|-----------|----------|

| IS                   | (V+) + (B+), (V-) + (B-) Supply Currents                                                                                                       |              | 52           | 60        | mA       |

| I <sub>S</sub> , dis | (V+) + (B+), (V-) + (B-) Supply Currents, Disabled                                                                                             |              | 17           | 25        | mA       |

| I <sub>VINH</sub>    |                                                                                                                                                | -20          | -3           | 20        | μA       |

| I <sub>VINL</sub>    |                                                                                                                                                | -20          | 2            | 20        | μA       |

| IDATA                |                                                                                                                                                | -30          | -15          | 30        | μA       |

| I <sub>OE</sub>      | OE Input Current                                                                                                                               | -30          | -14          | 30        | μA       |

| IE                   | E Input Current                                                                                                                                | -20          | 7            | 20        | μA       |

| V <sub>SR</sub>      | Voltage at I <sub>SR</sub> Pin                                                                                                                 | 0            | 20           | 40        | mV       |

| Ishunt+, Ishunt-     |                                                                                                                                                |              | 4            | 7         | mA       |

| Vshunt+, Vshunt-     | Sense Threshold at Shunts                                                                                                                      | 160          | 200          | 250       | mV       |

| ISENSE               | Sense Output Currents                                                                                                                          | 1            | 1.5          | 2         | mA       |

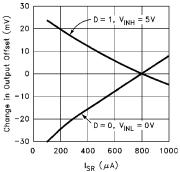

| V <sub>OS</sub>      | Output Offset, Data High, $V_{INH} = 0V$ , $V_{INL} = -1.6V$<br>Data Low, $V_{INL} = 0V$ , $V_{INH} = 5V$                                      | -50<br>-100  |              | 50<br>100 | m∨<br>mV |

| Eg                   | Gain Error Data High, $V_{INH}$ from 0V to 5V, $V_{INL}$ = -1.6V, No Load Data Low, $V_{INH}$ = 5V, $V_{INL}$ from -5V to 0V, No Load          | -1.5<br>-1.5 | -0.6<br>-0.6 | 0<br>0    | %<br>%   |

| NL                   | Gain Nonlinearity Data High, $V_{INH}$ from 0V to 10V, $V_{INL}$ = -1.6V, No Load Data Low, $V_{INH}$ = 5V, $V_{INL}$ from -10V to 0V, No Load |              | 0.04<br>0.06 |           | %<br>%   |

| PSRR                 | Power Supply Rejection Ratio of $V_{\mbox{OUT}}$ with Respect to B+, B-, Shunt+, or Shunt- Potential                                           |              | 2.2          |           | mV/V     |

| R <sub>O</sub> , en  | Output Resistance, Enabled, II = ±20mA                                                                                                         | 4.5          | 6            | 7.5       | Ω        |

| R <sub>O</sub> , dis | Output Resistance, Output Disabled, $V_O = -1.6V$ to -5V, EL1056 EL1056A                                                                       | 20K<br>100K  | 100K<br>200K |           | Ω        |

| I <sub>O</sub> , dis | Output Current, Output, Disabled, V <sub>O</sub> = 0V                                                                                          | -20          | 5            | 20        | μA       |

| I <sub>O</sub> , off | Output Leakage, E Low, (Shut-Down), V <sub>O</sub> = 0V, EL1056<br>EL1056A                                                                     | -20<br>-150  |              | 20<br>150 | μA<br>nA |

-1.6V to -0.8V. I\_{SR} = 800 $\mu$ A. V<sub>INH</sub> = 5V, V<sub>INL</sub> = -1.6V

### **AC Electrical Specifications**

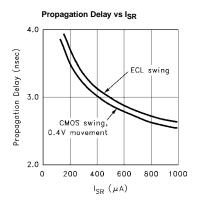

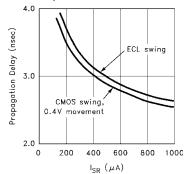

$T_A = 25^{\circ}C$ , V+ = B+ = +15V, V- = B- = -10V, Rshunt+ = Rshunt- =  $6.5\Omega$ . R<sub>L</sub> =  $500\Omega$ .  $50\Omega$  + 22pF snubber included at output. Data E, and OE from -1.6V to -0.8V. I<sub>SR</sub> =  $800\mu$ A. ECL swing is defined by V<sub>INH</sub> = - 0.8V and V<sub>INL</sub> = -1.6V, CMOS swing defined by V<sub>INH</sub> = 5V and V<sub>INL</sub> = 0V. Propagation delay is measured at 0.4V movement of output.

| PARAMETER            | DESCRIPTION                                                                                                       | MIN | TYP              | MAX        | UNITS          |

|----------------------|-------------------------------------------------------------------------------------------------------------------|-----|------------------|------------|----------------|

| T <sub>PD</sub>      | Propagation Delay, CMOS Swing                                                                                     | 1.0 | 3.0              | 4.5        | ns             |

| Dis                  | Propagation Delay Dispersion<br>Due to Output Edge Direction<br>From ECL to CMOS Swings<br>Due to Repetition Rate |     | 250<br>250<br>80 | 450<br>450 | ps<br>ps<br>ps |

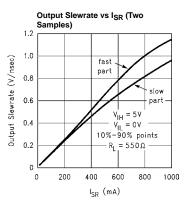

| SR                   | Output Slew Rate, CMOS Swing, 20%-80%                                                                             | 0.8 | 1                | 1.2        | V/ns           |

| SR <sub>SYM</sub>    | Slew Rate Symmetry                                                                                                |     | 3                | 10         | %              |

| TR                   | Output Rise Time, ECL Swing, 20%-80%                                                                              |     | 2.2              |            | ns             |

| OS                   | Output Overshoot<br>CMOS Swing<br>ECL Swing (I <sub>SR</sub> = 350μA)                                             |     | 190<br>65        | 500        | mV<br>mV       |

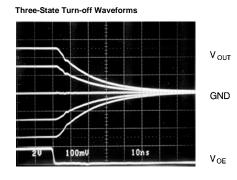

| T <sub>DIS</sub>     | Output Disable Delay Time                                                                                         |     | 4.7              | 6.5        | ns             |

| T <sub>EN</sub>      | Output Enable Delay Time                                                                                          |     | 6.0              | 8.5        | ns             |

| C <sub>O</sub> , dis | Output Capacitance in Disable                                                                                     |     | 3                |            | pF             |

| T <sub>OFF</sub>     | Power-Down Delay Time                                                                                             |     | 0.5              |            | μs             |

| T <sub>ON</sub>      | Power-On Delay Time                                                                                               |     | 90               |            | ns             |

| C <sub>O</sub> , off | Output Capacitance in Power-Down                                                                                  |     | 50               |            | pF             |

| T <sub>SENSE</sub>   | Comparator Delay Time — Switching ON<br>Switching OFF                                                             |     | 1.5<br>0.4       |            | μs<br>μs       |

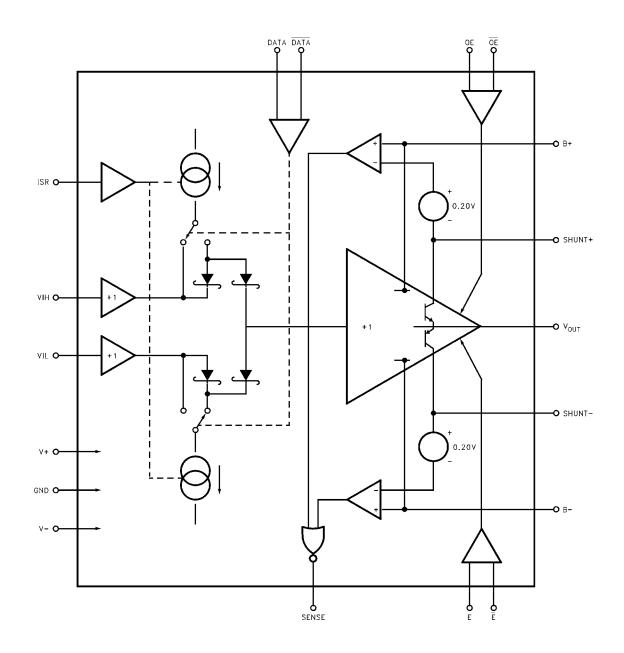

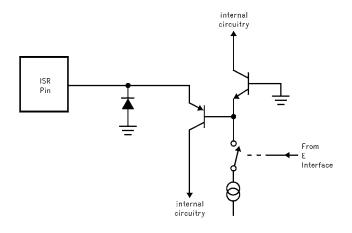

# Block Diagram

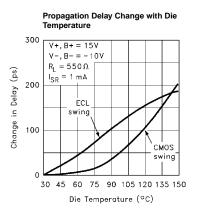

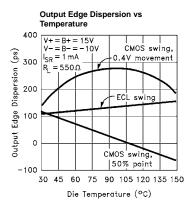

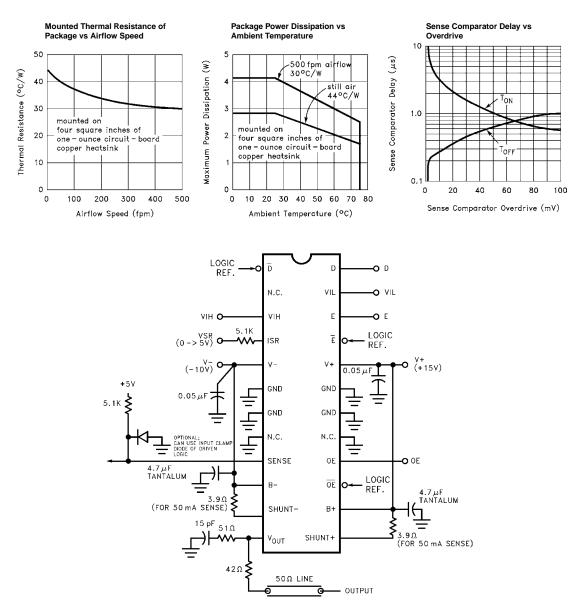

# **Typical Performance Curves**

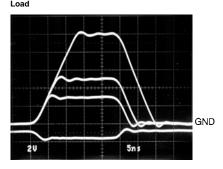

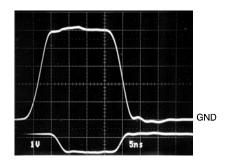

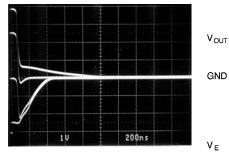

10V, CMOS, TTL, and ECL Outputs into  $\text{550}\Omega$  Load

CMOS Output at  $I_{SR}$  = 100µA, 200µA, 400µA, and 1000µA

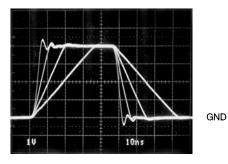

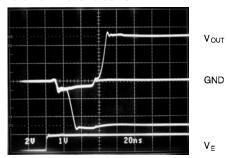

CMOS and ECL Outputs As Seen at the End of an Unterminated Cable, Backmatched at Driver

# Typical Performance Curves (Continued)

### Typical Performance Curves (Continued)

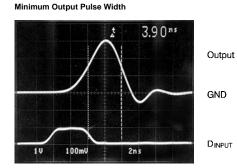

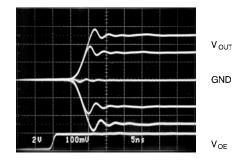

Three-State Turn-on Waveforms

Power-Down Enable Waveforms

#### Typical Performance Curves (Continued)

# **Applications Information**

#### **Functional Description**

The EL1056 is a fully integrated pin driver for automatic test systems. Pin drivers are essentially pulse generators whose high and low levels can be externally programmed and accurately switched in time, as well as incorporating an output switch to disconnect the driver from a measurement bus. Additionally, the EL1056 has programmable slewrate.

### **Control Voltage Inputs**

The analog level inputs are named  $V_{\text{INH}}$  and  $V_{\text{INL}},$  and the output replicates them as controlled by logic inputs. The analog inputs are buffered and have bandwidths of 35MHz

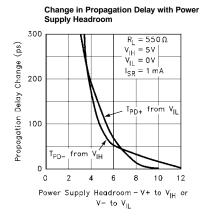

and slewrates of 25V/µs. For full slewrate, 4V of headroom should be given to the inputs, that is V<sub>INH</sub> should be 4V less than V+ or B+, and V<sub>INL</sub> should be 4V more positive than V- or B-. At lower slewrates (I<sub>SR</sub> = 500µA or less), 3V of headroom will suffice. Insufficient headroom causes distorted output waveforms or delay errors in output transitions. V<sub>INH</sub> may be lower in voltage than V<sub>INL</sub>, but the output will not follow the control logic correctly. Furthermore, V<sub>INH</sub> should be 200mV more positive than V<sub>INL</sub> (the minimum output amplitude) for accurate switching.

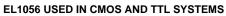

### Logic Inputs

The logic inputs are all differential types, with both NPN and PNP transistors connected to each terminal. They are optimized for differential ECL drive, which optimizes + to - edge delay time matching. Larger logic levels can introduce feedthrough glitches into the output waveform. For CMOS input logic levels, an ECL output waveform will show feedthrough when the input risetime is shorter than 8ns, differential or single-ended. CMOS output swings show less aberration, and the EL1056 can tolerate a 4ns single-ended risetime or 2ns risetime for differential inputs. Attenuating CMOS or TTL inputs to  $1V_{PP}$  will eliminate all logic feedthrough as shown in Figure 1.

#### FIGURE 1. ALTERNATE LOGIC INTERFACE

#### Slewrate Control

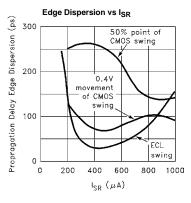

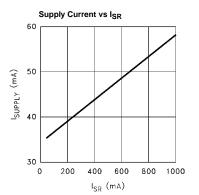

The slewrate is controlled by the  $I_{SR}$  input. This is a current input and scales the output slewrate by a nominal 1.25V/ns/mA. The slewrate maintains calibration and symmetry to at least as slow as 0.2V/ns. The practical upper end of  $I_{SR}$  is 1mA, and supply current increases with increasing  $I_{SR}.$

The  $I_{SR}$  control can be used to adjust individual pin drivers to a system standard, by adjusting the value of its series resistor. Slewrate can also be slowed to reduce output ringing and crosstalk.

With ECL output swings, there is not enough voltage excursion to incur slewrate delays to 50% logic threshold. The risetime, delays, and dispersions do not degrade with reasonably reduced  $I_{SR}$ , and overshoot will reduce markedly. An  $I_{SR}$  of 350µA produces a very good ECL output, and driver dissipation is also reduced.

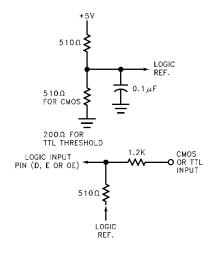

The I<sub>SR</sub> pin is connected to the emitter of a PNP transistor whose base is biased a diode below ground (see Figure 2). Thus, the I<sub>SR</sub> input looks like a low impedance for positive input currents, and is biased close to ground. A protection diode absorbs negative currents, and the input PNP will not conduct. In power-down mode, the PNP releases its current sink and the external circuit must not present more than 6V to the disabled I<sub>SR</sub> input, or emitter-base damage to the

9

NPN will occur within the driver. A signal diode or zener can be used to clamp the  $I_{SR}$  input for positive input voltages if the voltage on the  $I_{SR}$  resistor is potentially greater than 6V when the driver is in power-down mode.

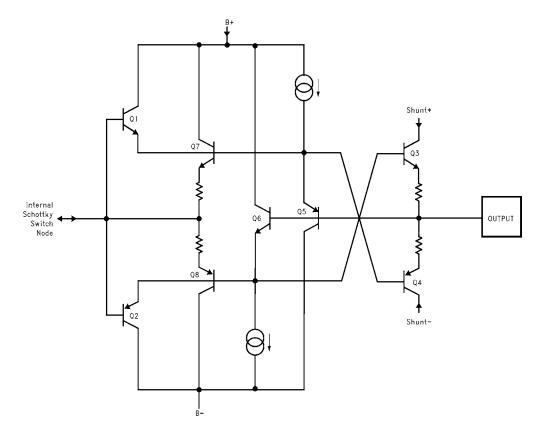

#### Output Stage-Three-State Mode

In three-state mode (OE low) the output transistors have their emitter-base junctions reverse-biased by a diode voltage. This turn-off voltage is in fact provided by an internal buffer whose input is connected to the output pin (see Figure 3). Transistors Q1–Q4 form the output buffer in normal mode. The three-state mode buffer Q5–Q8 replicates externally impressed voltages from the output pin onto the internal schottky switch node. They also turn off Q1–Q4 by a reverse diode voltage between bases and emitters, effectively bootstrapping the internal voltages, so that no transistor's base-emitter junction is reverse-biased by a damaging potential. Another benefit is that the capacitance seen at the output in three-state mode is reduced.

Because the three-state buffer's input is connected to the output terminal, the output is quite "alive" during three-state. For instance, the input bias current of the buffer is seen as the three-state "leakage", and its variation with applied voltage becomes three-state input impedance.

The three-state input current is like a current source, and it can drag an output to unpredictable voltages. It is not a danger to connect a three-stated output that has drifted to, say, -6V to a logic pin of a device to be tested. The three-state output current will simply comply with whatever voltage the connected part normally establishes.

The three-state input impedance is also quite active over frequency. The output can oscillate when presented with resonant or inductive impedances. To prevent this, a snubber should be connected from output to ground, consisting of a resistor in series with a small capacitor. The snubber can also reduce the reflections of the coaxial line when driven from the far end, since the line appears to have an open termination during three-state. Typical values for the resistor are  $50\Omega$  to  $75\Omega$ , and 12pF to 22pF for the series capacitor. The effect of the snubber is to "de-Q" resonances at the output.

FIGURE 2. ISR PIN CIRCUITRY

#### Output Stage–Normal Mode

Capacitive loads can cause the output stage to ring. Little ringing occurs for loads less than 25pF, but substantial ringing for more than 40pF. Terminated transmission lines cause no ringing, and actually suppress it as a snubber does. A terminated line draws heavy DC current, however, and greatly raises dissipation.

Driving a back-terminated line also causes little ringing and does not cause DC dissipation. The series matching resistor between the EL1056 output and a back-terminated line also serves to isolate the driver from capacitive loads and shortcircuits. The slewrate of the driver slows by about 10% when driving a  $50\Omega$  back-matched line, as seen at the end of the line. The snubber can be on either side of the back-match resistor. When placed on the line side it creates a high-frequency termination for the line when the driver is three-stated, but it slows the output small-signal risetime by about 10% (although not slewrate). When placed on the driver side of the backmatch resistor, no speed reduction occurs in normal mode but the cable is more poorly terminated in three-state.

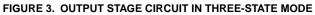

The transient currents that occur when driving capacitive or back-matched loads can be very high, approaching 100mA. The driver is capable of outputting a peak of 140mA, but long-term load currents must be limited to 60mA. Shortcircuits can rapidly destroy the EL1056, although the part will survive for 20ms periods. If there is the possibility of output load fault the overcurrent sense circuitry should be used to signal alarm to the controlling system, which should ultimately activate the three-state mode to relieve the output stage. Driving large static currents also raises internal dissipation and should be part of the thermal budget. The collectors of the output transistors are connected to the Shunt terminals, and the output stage drivers' collectors are connected to the B+ and B- terminals (see Figure 4). The Shunt lines can have transient currents as high as 120mA and are separated from the V+ and V- terminals to keep switching noise out of the control and logic circuitry. A bypass capacitor should be connected to the B+ and Bterminals.

FIGURE 4. OUTPUT STAGE IN NORMAL MODE

### **Overcurrent Protection**

The sense comparators are available to alert the test system's controller that the driver is outputting excessive current. Shunt resistors are connected from B+ to Shunt+ and B- to Shunt-. When the internal comparators sense more than a nominal 200mV drop on the shunts, they cause a 1.5mA current to be sunk from the Sense terminal. The comparators are of "slow attack, fast decay" design, so that transient load currents will not trigger a sense output; only a sustained over-current will.

The sense resistors must not be inductive, and the skin resistance of long, narrow connections between Shunt and B+ or B- can cause transient voltages that produce output overshoot (but not ringing).

The Sense output is simply a switched current source connected to V-. It can be used to interface to CMOS, TTL, or ECL inputs. For CMOS and TTL, it can be connected to a pull-up resistor to +5V of 10K value. This establishes a logic high value, and a clamp diode (internal to TTL) establishes a low level of -0.6V. For ECL, a gate should be available to provide a static logic high level. An 820 $\Omega$  pull-up resistor is wired to that output. The logic low will be more negative than is usual for ECL, but this will cause no problem. In all cases, multiple Sense outputs may be connected together from many drivers to effect a wired-or function.

A further protection scheme is to provide a series resistor from B+ to V+ and B- to V-. The resistor serves to limit the output fault current by allowing B+ and B- voltages to sag under heavy load. This also reduces the dissipation on the output transistors for valid loads. Because B+ and B- are separately bypassed, these voltages will sustain under transient loads and dynamics will not be affected.

### **Output Accuracy**

The accuracy of the output voltage depends on several factors. The first is the gain error from V<sub>INH</sub> or V<sub>INL</sub> to the output, unloaded. The gain error is nominally -0.6%, and has a few tenths of a percent variation between parts. The second is supply rejection. If the B+, B-, Shunt+, or Shunt-voltages are different from those used by Elantec to test the part, there will be about 2.2mV systematic shift in output offset per volt of supply variation. The V+ and V- supplies have much less influence on output error. Finally, there is a random V<sub>OS</sub> error as specified in the data table.

Of course, the finite output impedance of the EL1056 will cause additional output error when the driver is loaded.

### Power-Down

The EL1056 incorporates a power-down feature that drastically reduces power consumption of an unused driver and also drops the output leakage current to nanoamperes ("A" grade only). The output is not a low capacitance in this mode, however, and transients driven from the cable can momentarily turn on the output transistors. Power-down is intended to allow the switching of accurate DC meters onto the bus without having to relay out the driver's leakage current. It takes about 40µs for the output leakage to sag to nanoamperes, but this is still much faster than relays or voltmeters.

Power-down is controlled by the E and  $\overline{E}$  differential inputs. There is no problem with logic amplitude or slewrate, and input resistor networks are not needed.

### Supply and Input Bypassing

The V+, B+, V-, and B- leads should be bypassed very closely with 0.1 $\mu$ F capacitors, preferably chip type. There should be a wide ground plane between bypasses, and this can be the heatsink copper. It is wise to also have a 4.7 $\mu$ F tantalum bypass capacitor within a couple of inches to the driver.

The logic inputs are active device bases, and can oscillate if presented with inductive lines. A local resistor of  $1000\Omega$  or less to ground will suffice in de-Q'ing any resonance. A 100pF or larger capacitor can also serve as a bypass.

### **Thermal Considerations**

The package of the EL1056 includes two fused leads on each side which are connected to the internal die mounting metal. Heat generated in the die flows through the mounting pad to the fused leads, and then to the circuit-board copper, achieving a thermal resistance to air around 40°/W. Characterization curves show the thermal resistance versus airflow rate. Consult the EL1056 Demonstration Board literature for a suggested board pattern. Note that thicker layers of copper than we used improves the thermal resistance further, to a limit of 22°C/W for an "infinite heatsink" directly soldered to the fused leads.

As a practical limit, the die temperature should be kept to 125°C rather than the allowable 150°C to retain optimum timing accuracies.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com