# PRODUCT OVERVIEW

# SAM8 PRODUCT FAMILY

Samsung's SAM87 family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-programmable ROM sizes. Important CPU features include:

- Efficient register-oriented architecture

- Selectable CPU clock sources

- Idle and Stop power-down mode release by interrupt

- Built-in basic timer with watchdog function

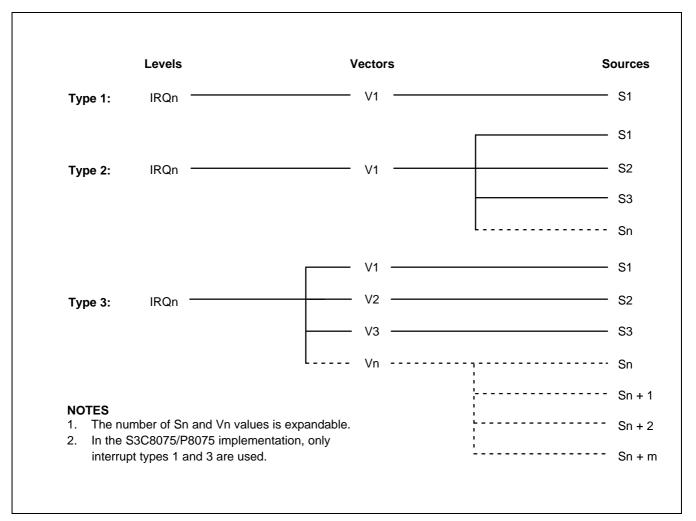

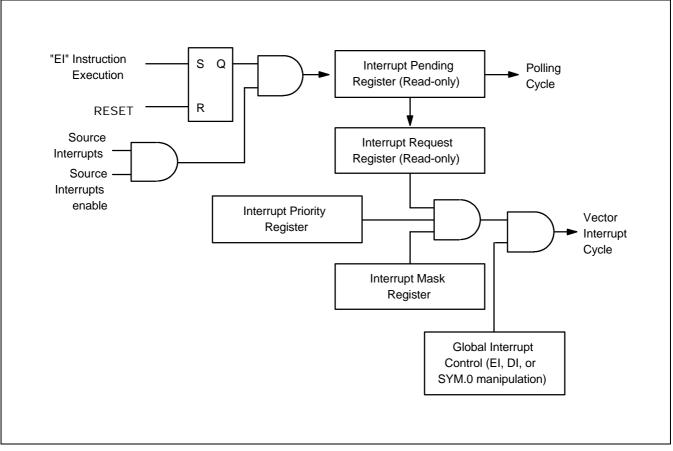

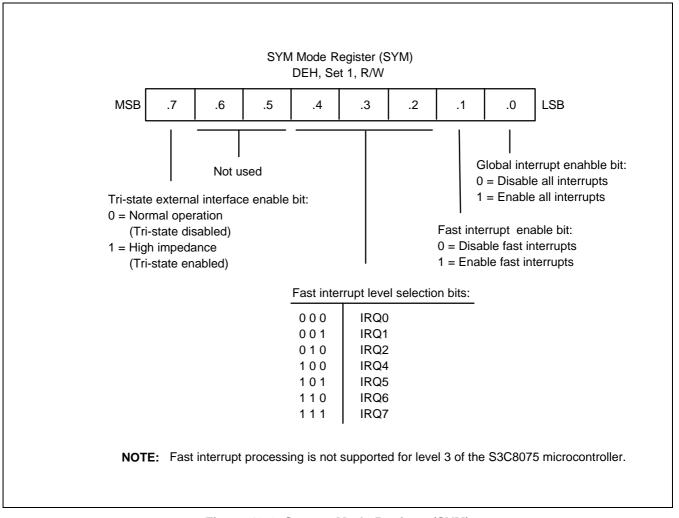

A sophisticated interrupt structure recognizes up to eight interrupt levels. Each level can have one or more interrupt sources and vectors. Fast interrupt processing (within a minimum of six CPU clocks) can be assigned to specific interrupt levels.

# S3C8075/P8075 MICROCONTROLLERS

S3C8075/P8075 single-chip 8-bit microcontrollers are based on the powerful SAM87 CPU architecture. The internal register file is logically expanded to increase the on-chip register space. The S3C8075 has 16-Kbyte mask-programmable ROM. The S3P8075 has 16-Kbyte one-time-programmable EPROM.

Following Samsung's modular design approach, the following peripherals are integrated with the SAM87 core:

- Seven programmable I/O ports (total 56 pins)

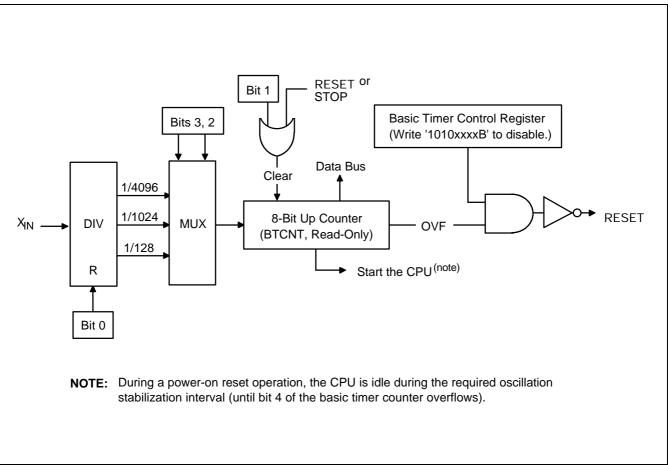

- One 8-bit basic timer for oscillation stabilization and watchdog functions

- One synchronous operating mode and three full-duplex asynchronous UART modes

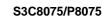

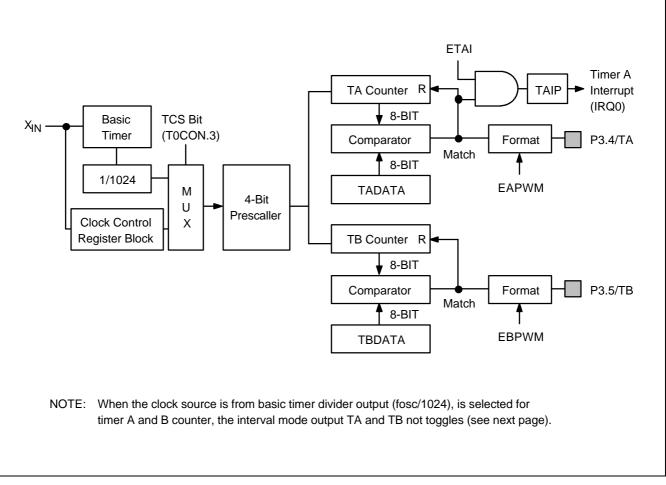

- Two 8-bit timers with interval timer and PWM modes

- Two 16-bit general-purpose timer/counters

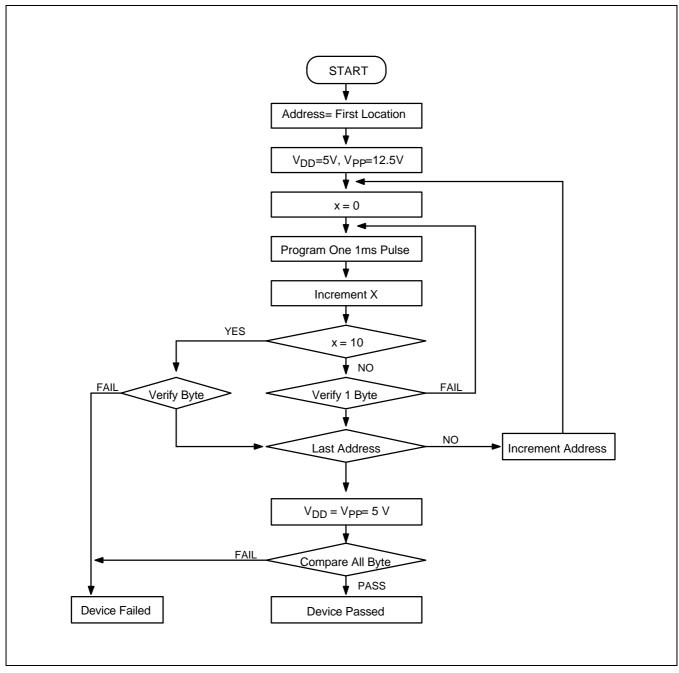

# OTP

The S3C8075 microcontroller is also available in OTP (One Time Programmable) version, S3P8075. S3P8075 microcontroller has an on-chip 16-Kbyte one-time-programmable EPROM instead of masked ROM. The S3P8075 is comparable to S3C8075, both in function and in pin configuration.

# FEATURES

## CPU

• SAM87 CPU core

# Memory

- 272-byte general purpose register area

- 16-Kbyte internal program memory

- ROM-less operating mode

# **External Interface**

- 64-Kbyte external data memory area

- 64-Kbyte external program memory area (ROMless mode)

## **Instruction Set**

- 78instructions

- IDLE and STOP instructions for power-down mode

# **Instruction Execution Time**

• 500 ns at 12 MHz f<sub>CPU</sub> (Min.)

# Interrupts

- 17 interrupt sources

- 17 interrupt vectors

- Eight interrupt levels

- Fast interrupt processing

# General I/O

- Four nibble-programmable ports

- One bit-programmable port

- Two bit-programmable ports for external interrupts

## Timers

Two 8-bit timers with interval timer and PWM modes

# **Timer/Counters**

• Two 16-bit general-purpose timer/counters

## **Basic Timer**

• One 8-bit basic timer (BT) for oscillation stabilization control and watch dog timer function.

# **Serial Port**

One synchronous operating mode and three fullduplex asynchronous UART modes

## **Operating Temperature Range**

•  $-40^{\circ}C$  to  $+85^{\circ}C$

# **Operating Voltage Range**

• 2.7 V to 5.5 V

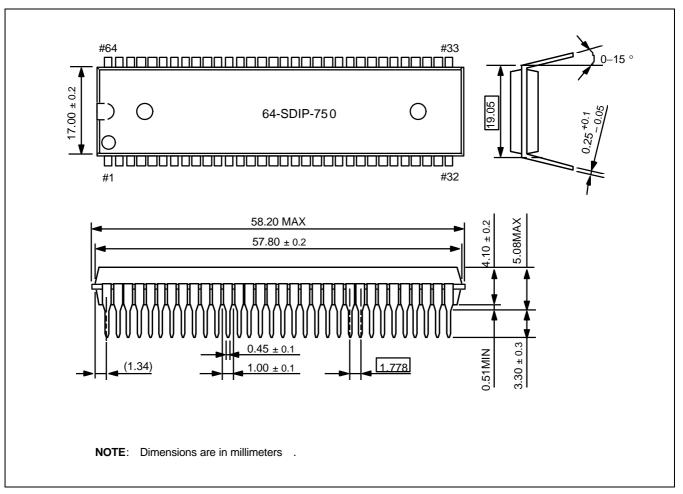

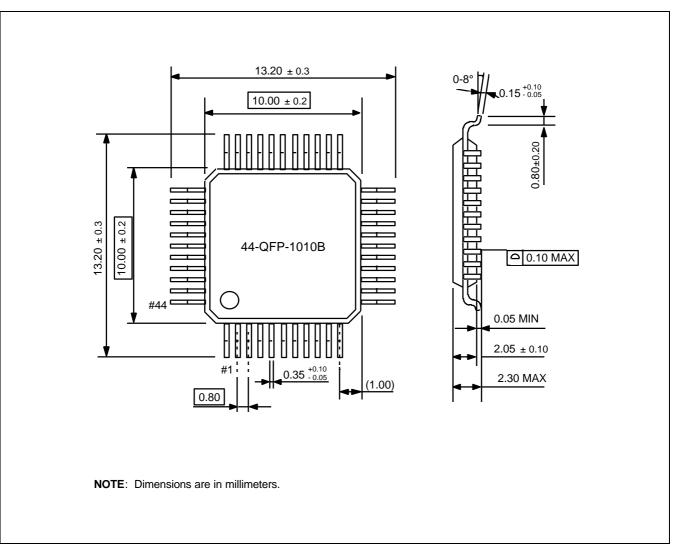

## Package Types

• 64-pin SDIP, 64-pin QFP

| Feature                     | S3C80B5                                                                   | S3C8075                                                        |

|-----------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------|

| Core                        | SAM8                                                                      | SAM87                                                          |

| ROM                         | 16 K bytes                                                                | Same                                                           |

| RAM                         | 272 bytes                                                                 | Same                                                           |

| I/O                         | 54                                                                        | 56 (add two pins)                                              |

| Port 6                      | Open drain (9 V drive)                                                    | Normal C-MOS output                                            |

| I/O option                  | None                                                                      | Same                                                           |

| Timer                       | 8-bit back-up timer                                                       | None                                                           |

|                             | Timer A, B<br>— 8-bit<br>— Interval/PWM mode<br>— Timer A match interrupt | Same<br>(some differ in interval mode,<br>see manual)          |

|                             | Timer C, D<br>— Gate function<br>— Timer/counter                          | Same                                                           |

| Watchdog timer              | None                                                                      | Watchdog timer (with BT)                                       |

| SIO                         | UART<br>— 8-bit/9-bit UART<br>— SIO                                       | Same                                                           |

| Interrupt                   | External × 12<br>— P2.4–P2.7, P4.0–P4.7                                   | Same                                                           |

|                             | Internal × 6<br>— Timer A, C, D, SI, SO, Back-up                          | Internal × 5<br>— Timer A, C, D, SI, SO                        |

| Power down                  | Stop/idle                                                                 | Same                                                           |

| Oscillator                  | Crystal, ceramic                                                          | Same                                                           |

| CPU clock divider           | 1/2                                                                       | 1/1, 1/2, 1/8, 1/16                                            |

| Execution time (Min.)       | 0.6 μs at 20 MHz (f <sub>CPU</sub> = 10 MHz)                              | 0.5 μs at 12 MHz (f <sub>CPU</sub> = 12 MHz)                   |

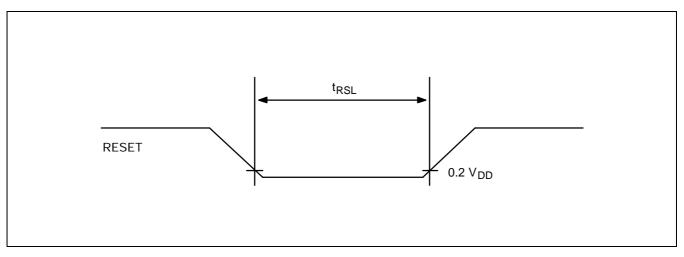

| Operating frequency         | Max. 20 MHz (f <sub>CPU</sub> = 10 MHz)                                   | Max. 12 MHz (at 4.5 V) <sup>(2)</sup><br>Max. 4 MHz (at 2.7 V) |

| Operating voltage           | 4.5–5.5 V                                                                 | 2.7–5.5 V at 4 MHz<br>4.5–5.5 V at 12 MHz                      |

| OTP/MTP                     | MTP                                                                       | OTP                                                            |

| Pin assignment              | _                                                                         | Different                                                      |

| Package                     | 64SDIP/64QFP                                                              | Same                                                           |

| Start address               | 0020h                                                                     | 0100h                                                          |

| P5CON, P6CON                | BANK0                                                                     | BANK1                                                          |

| Interrupt pending bit clear | Write "1"                                                                 | Write "0"                                                      |

Table 1-1. Comparison Table

#### NOTES:

1. The S3C8075 can replace the S3C80B5. Their functions are mostly the same, but there are some differences. Table 1-1 shows the comparison of S3C8075 and S3C80B5.

2. Operating frequency is maximum CPU clock; the maximum oscillation frequency is 22.1184 MHz.

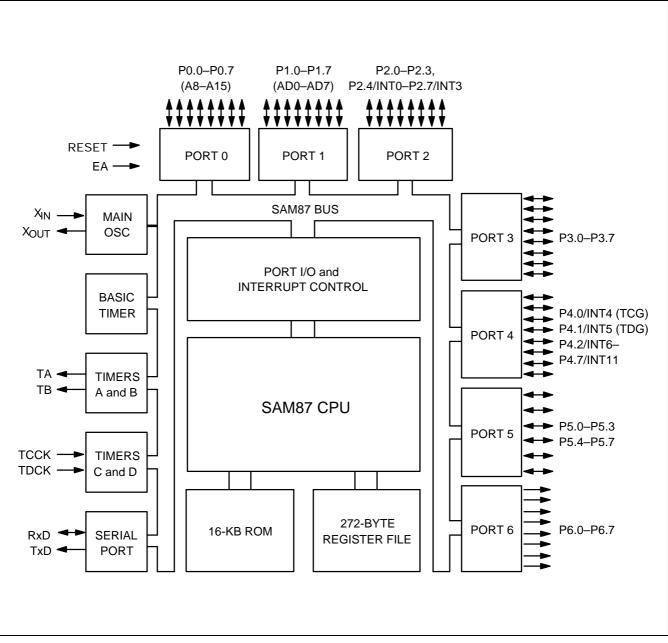

# **BLOCK DIAGRAM**

Figure 1-1. S3C8075 Block Diagram

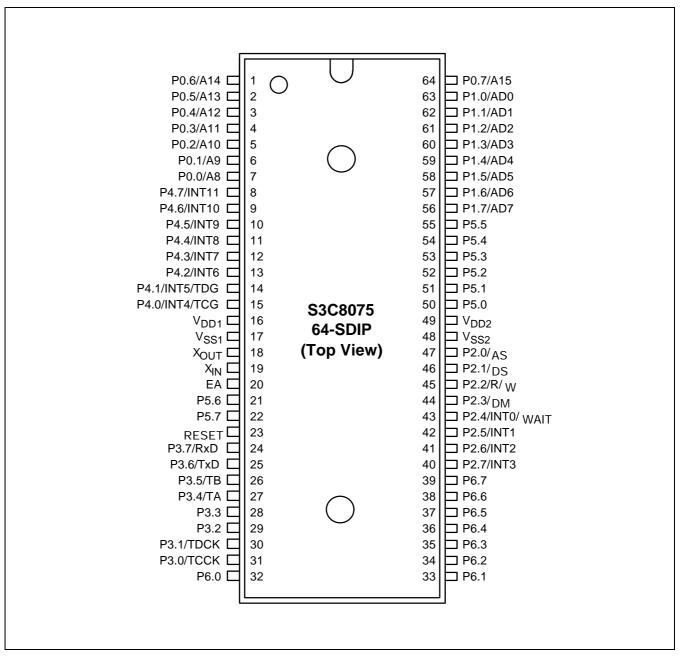

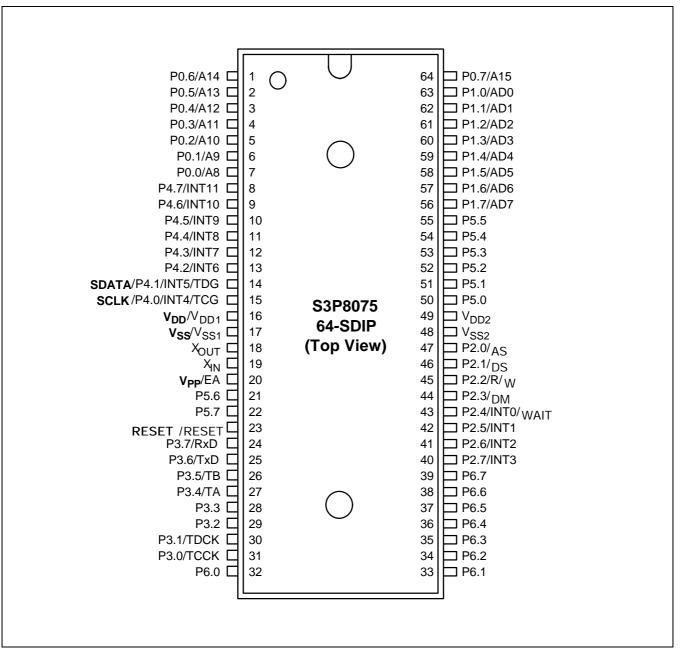

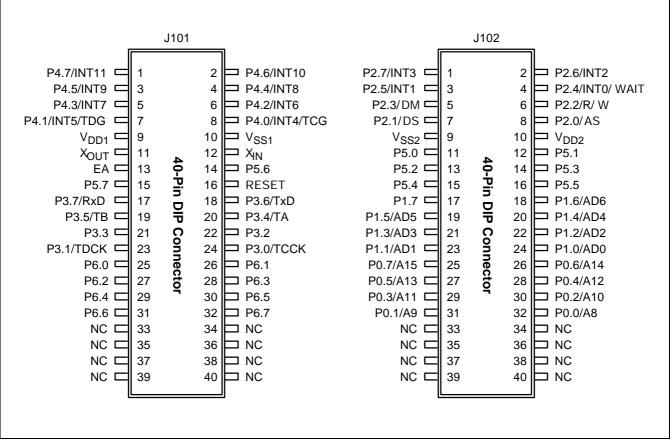

Figure 1-2. S3C8075 Pin Assignments (64-SDIP)

S3C8075/P8075

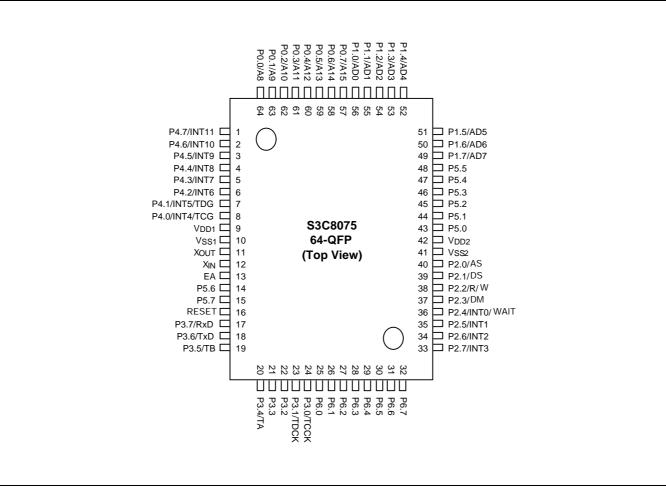

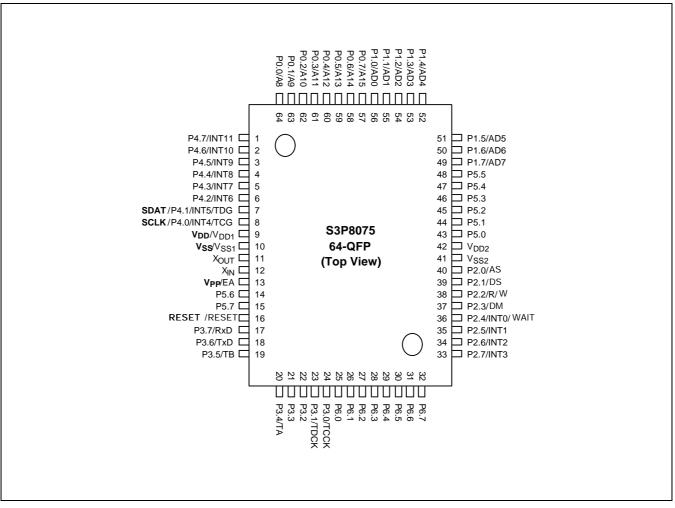

Figure 1-3. S3C8075 Pin Assignments (64-QFP)

| Pin<br>Name            | Pin<br>Type | Pin<br>Description                                                                                                                                                                                                                                                                      | Circuit<br>Number                                                     | SDIP Pin<br>Number | Share<br>Pins                            |  |

|------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|------------------------------------------|--|

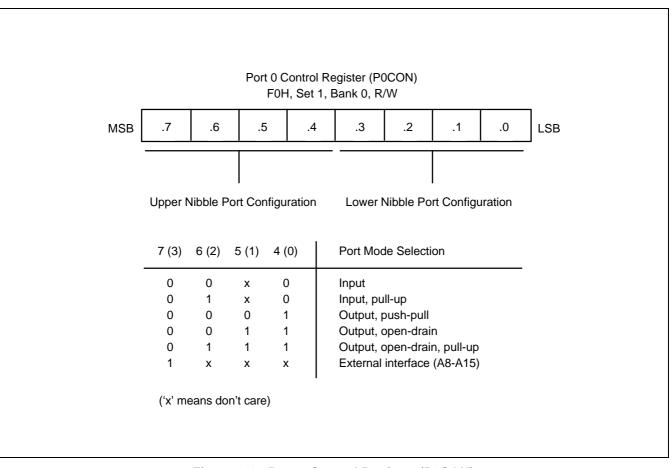

| P0.0-P0.7              | I/O         | I/O port with nibble-programmable pins;<br>Input or push-pull, open-drain output and<br>software assignable pull-ups; also<br>configurable as external interface address<br>lines A8-A15.                                                                                               | E                                                                     | 1–7, 64            | A8–A15                                   |  |

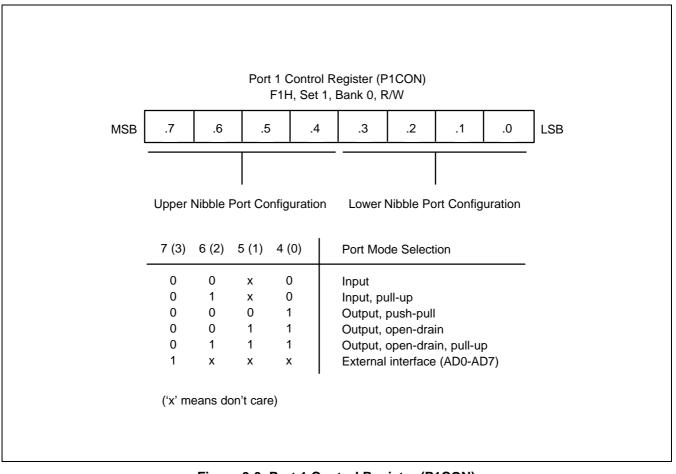

| P1.0–P1.7              | I/O         | Same general characteristics as port 0; also configurable as external interface address/data lines AD0–AD7.                                                                                                                                                                             | E                                                                     | 56–63              | AD0–AD7                                  |  |

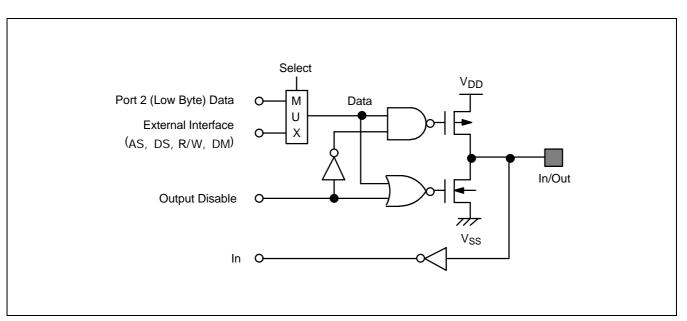

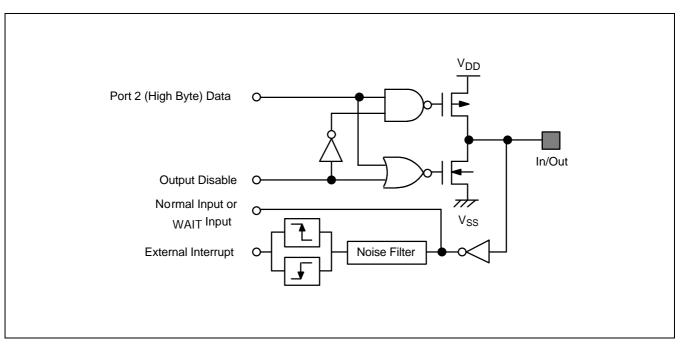

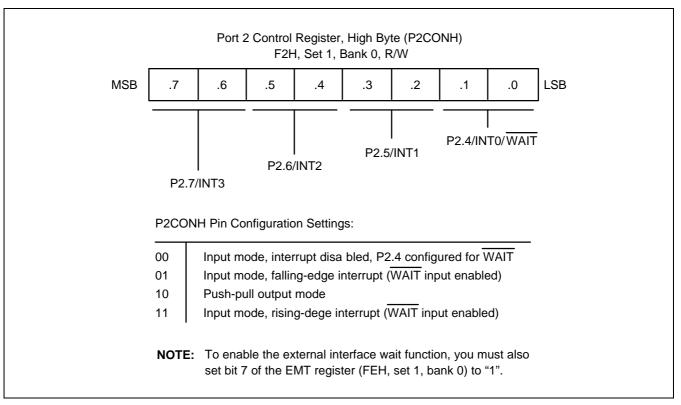

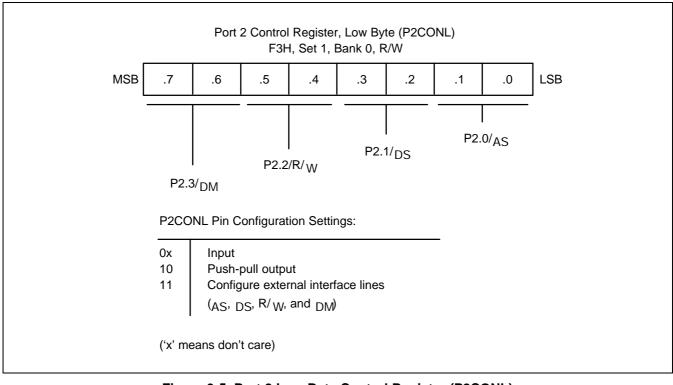

| P2.0–P2.3<br>P2.4–P2.7 | I/O         | I/O port with bit-programmable pins; Input<br>or push-pull output. Lower nibble pins 0–3<br>are configurable for external interface<br>signals; upper nibble pins 4–7 are bit-<br>programmable for external interrupts INT0–<br>INT3. P2.4 can also be used for external<br>WAIT input. | D-1 (lower<br>nibble);<br>D-1 (upper<br>nibble; with<br>noise filter) | 40–47              | AS, DS,<br>DM, R/W<br>INT0–INT3,<br>WAIT |  |

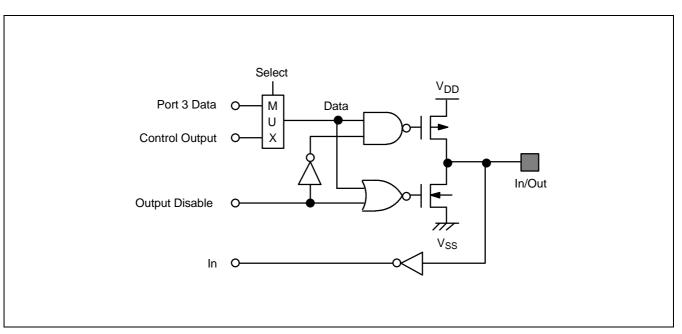

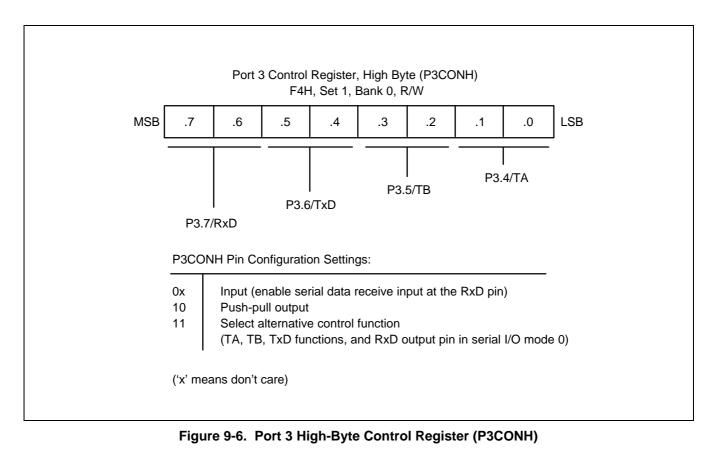

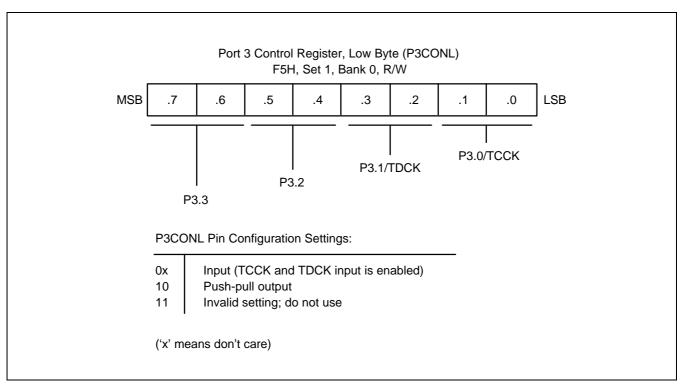

| P3.0–P3.7              | I/O         | I/O port with bit-programmable pins; Input<br>or push-pull output. Alternate functions<br>include software-selectable UART transmit<br>and receive on pins 3.7 and 3.6, timer B<br>and timer A outputs at pins 3.5 and 3.4, and<br>timer D and C clock inputs at pins 3.1 and<br>3.0.   | D-1                                                                   | 24– 31             | TCCK,<br>TDCK, TA,<br>TB, TxD,<br>RxD    |  |

| P4.0-P4.7              | I/O         | I/O port with bit-programmable pins; Input<br>or push-pull output; software-assignable<br>pull-ups. Alternate functions include<br>external interrupt inputs INT4-INT11 (with<br>interrupt enable and pending control) and<br>timer C and D gate input at P4.0 and P4.1.                | D<br>(with noise<br>filter)                                           | 8–15               | INT4–<br>INT11,<br>TCG, TDG              |  |

| P5.0–P5.7              | I/O         | I/O port with nibble-programmable pins;<br>Input or push-pull, open-drain output;<br>software-assignable pull-ups.                                                                                                                                                                      | E                                                                     | 21, 22,<br>50–55   | -                                        |  |

| P6.0–P6.7              | 0           | Output port with nibble-programmable pins;<br>push-pull, open-drain output; software-<br>assignable pull-ups.                                                                                                                                                                           | E-8                                                                   | 32–39              | -                                        |  |

| RxD                    | I/O         | Bi-directional serial data input pin                                                                                                                                                                                                                                                    | _                                                                     | 24                 | P3.7                                     |  |

| TxD                    | I/O         | Serial data output pin                                                                                                                                                                                                                                                                  | _                                                                     | 25                 | P3.6                                     |  |

| TA, TB                 | I/O         | Timer A and B output pins                                                                                                                                                                                                                                                               | 4                                                                     | 27, 26             | P3.4, P3.5                               |  |

| TCCK, TDCK             | I/O         | Timer C and D external clock input pins                                                                                                                                                                                                                                                 | D-1                                                                   | 30, 31             | P3.0, P3.1                               |  |

| INT0-INT3              | I/O         | External interrupts. I/O pin 2.4 (share pin with INT0) is also configurable as a WAIT signal input pin for the external interface.                                                                                                                                                      | D-1<br>(with noise<br>filter)                                         | 40–43              | P2.4–P2.7                                |  |

| Table 1-2. S3C8075 Pin Descriptions (64-SDIP) |

|-----------------------------------------------|

|-----------------------------------------------|

| Pin<br>Name                         | Pin<br>Type | Pin<br>Description                                                                                                                 | Circuit<br>Number           | SDIP Pin<br>Number | Share<br>Pins |

|-------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|---------------|

| INT4–INT11                          | I/O         | Bit-programmable external interrupt input<br>pins with interrupt pending and enable<br>/disable control                            | D<br>(with noise<br>filter) | 8–15               | P4.0–P4.7     |

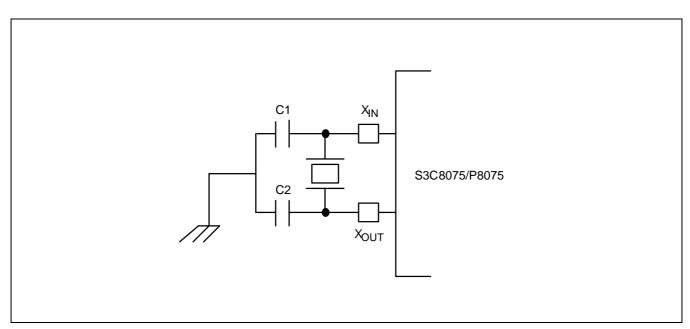

| X <sub>IN</sub> , X <sub>OUT</sub>  | _           | System clock input and output pins                                                                                                 | -                           | 18, 19             | -             |

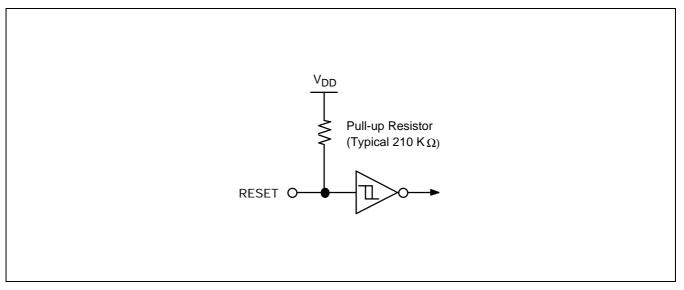

| RESET                               | I           | System reset pin<br>(internal pull-up: 280 KΩ)                                                                                     | В                           | 23                 | -             |

| EA                                  | Ι           | External access (EA) pin with three modes:<br>0 V: Normal operation (internal ROM)<br>5 V: ROM-less operation (external interface) | _                           | 20                 | _             |

| V <sub>DD2</sub> , V <sub>SS2</sub> | -           | Power input pins for port output (external)                                                                                        | -                           | 49, 48             | -             |

| V <sub>DD1</sub> , V <sub>SS1</sub> | _           | Power input pins for CPU (internal)                                                                                                | _                           | 16, 17             | _             |

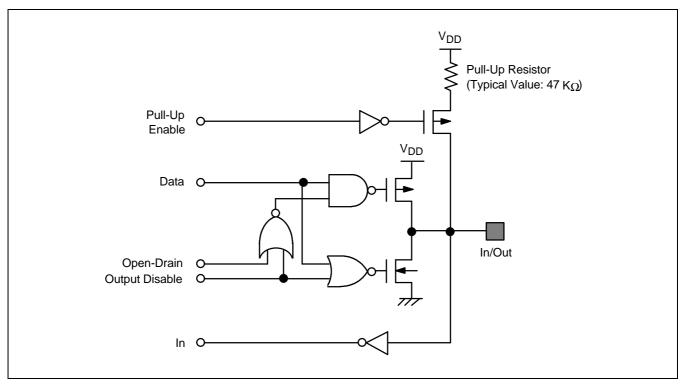

# **PIN CIRCUIT**

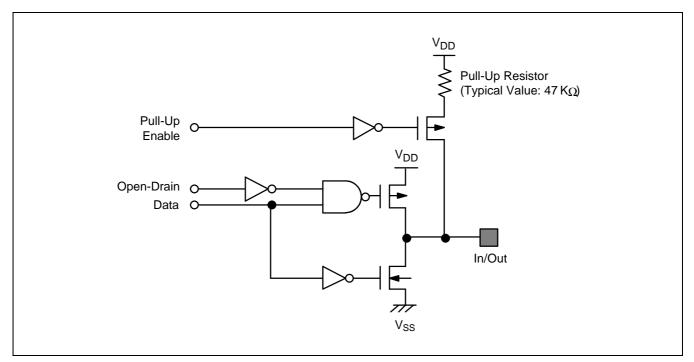

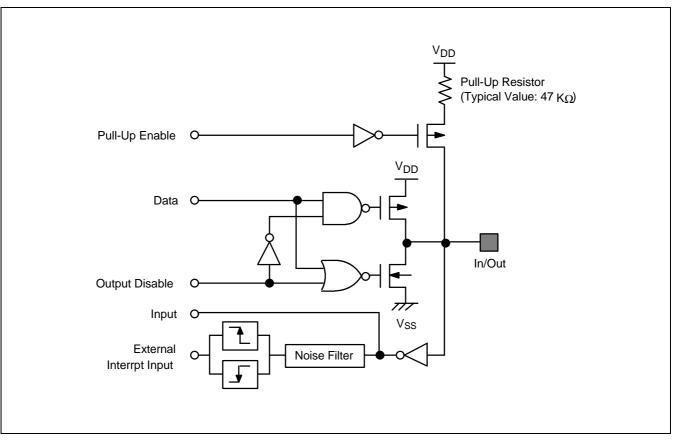

Figure 1-4. Pin Circuit Type E (Ports 0, 1, 5)

Figure 1-5. Pin Circuit Type E-8 (Ports 6)

Figure 1-6. Pin Circuit Type D-1 (P2.0–P2.3)

Figure 1-7. Pin Circuit Type D-1 (P2.4–P2.7)

Figure 1-8. Pin Circuit Type D-1 (Port 3)

Figure 1-9. Pin Circuit Type D (Port 4)

Figure 1-10. Pin Circuit Type B (RESET)

# **2** ADDRESS SPACES

# **OVERVIEW**

S3C8075 microcontroller has three kinds of address space:

- Program memory (internal and/or external)

- Internal register file

- External data memory

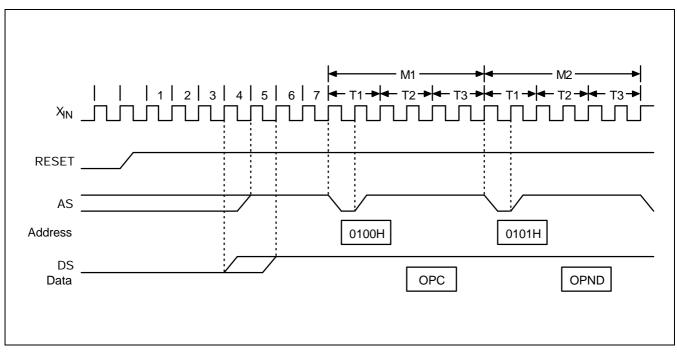

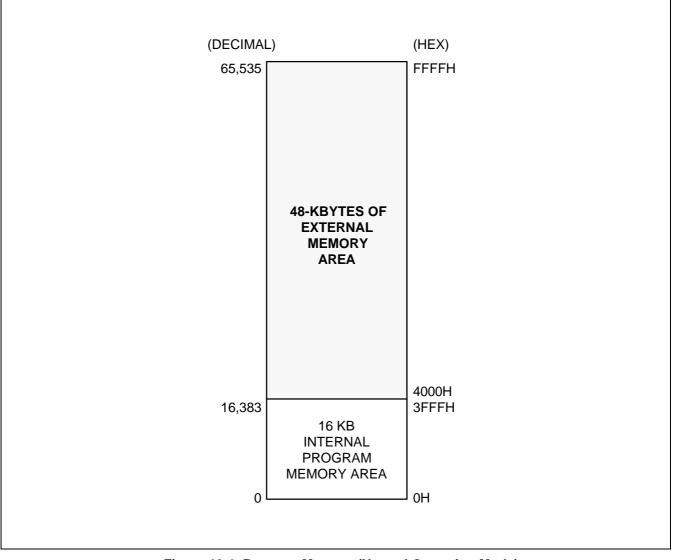

A 16-bit address bus and an 8-bit data bus support program memory and data memory operations. A separate 8-bit address bus and an 8-bit data bus carry addresses and data between the CPU and the register file. The SAM87 bus architecture therefore supports up to 64 Kbytes of program memory. S3C8075 has 16 K bytes of mask-programmable program memory on-chip.

There are two ROM configuration options: normal internal ROM mode and ROM-less mode.

S3C8075 microcontroller has 272 general-purpose registers in its internal register file. Forty-nine bytes of the register file are mapped for system and peripheral control functions.

#### **PROGRAM MEMORY (ROM)**

#### Normal Operating Mode (Internal ROM)

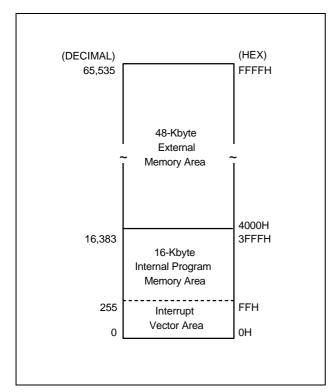

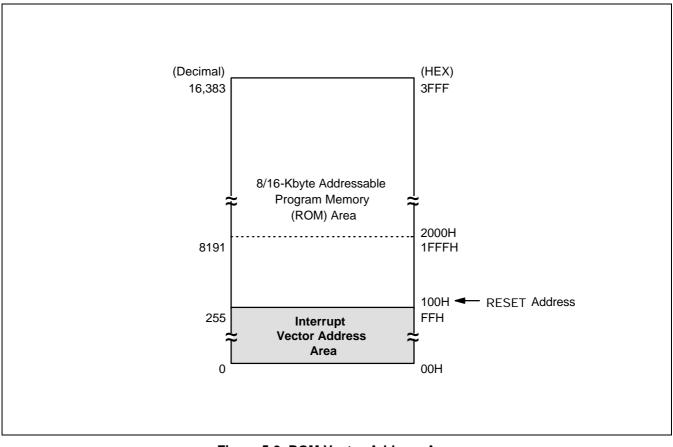

S3C8075 has 16 Kbytes (locations 0H–3FFFH) of internal mask-programmable program memory. For normal internal ROM operation, the EA pin should be connected to  $V_{SS}$ .

The first 256 bytes of the ROM (0H–FFH) are reserved as an interrupt vector area. Unused locations in this address range can be used as normal program memory.

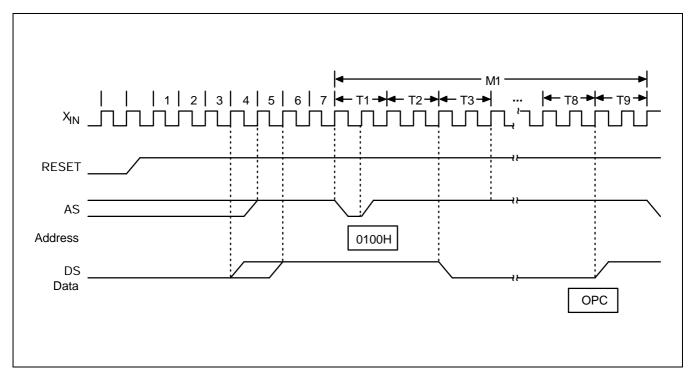

The reset address in the ROM is 0100H.

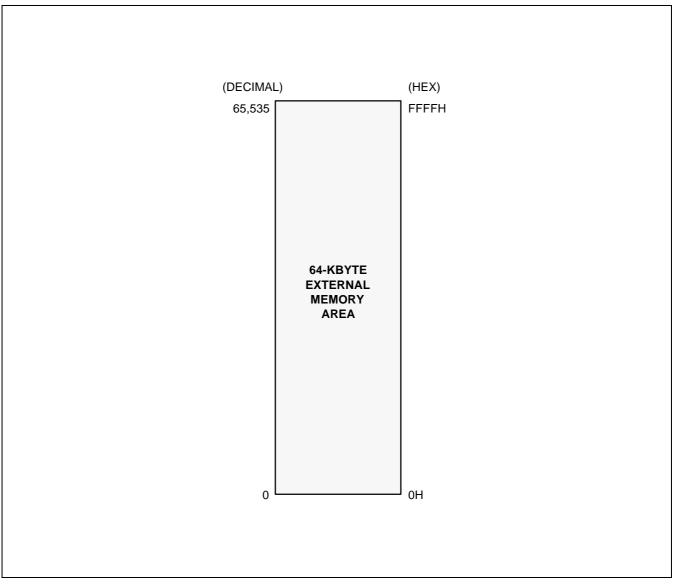

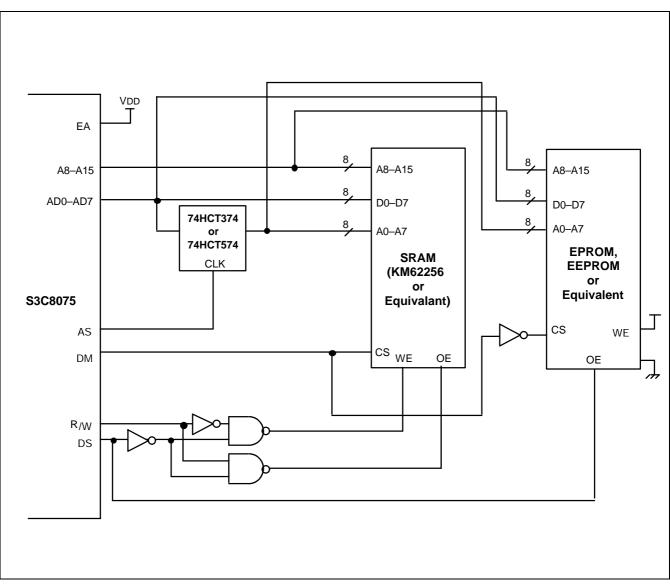

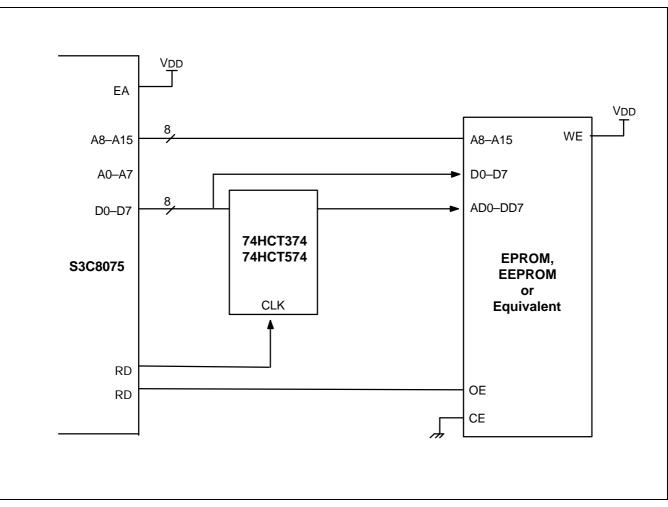

#### **ROM-Less Operating Mode (External ROM)**

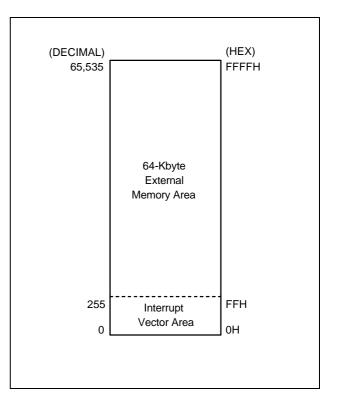

For applications that require more than 16 Kbytes of program memory, ROM-less operating mode can be used to configure an external area of up to 64-Kbyte. Access to the internal 16-Kbyte program memory area is disabled in ROM-less mode.

In normal operating mode, it is also possible to access external program memory of up to 48-Kbyte through the external memory interface. The 16-Kbyte on-chip ROM is accessed when program memory locations 0H–3FFFH are addressed at 0H–3FFFH and the external interface is used whenever locations are addressed 4000H–FFFFH. This configuration however, may not, be practical or cost-effective.

Mode selection (internal ROM or ROM-less) depends on the voltage applied to the EA pin during a reset operation:

- When 0 V is applied to the EA pin, the S3C8075's internal ROM is configured normally and the 16-Kbyte space (0H–3FFFH) is addressed.

- When 5 V is applied to the EA pin, S3C8075 operates in ROM-less mode. External memory locations 0000H–FFFFH are accessed over the 16-bit address/data bus.

When 5 V is applied to the EA pin during a power-on reset, the external peripheral interface is automatically configured as follows:

- Port 0 and port 1 control registers are cleared to their initial value (00H), but the corresponding address and data lines are configured.

- The lower-nibble pins of port 2 (P2CONL) are set to '11B', configuring the interface signals (DM, R/W, DS, and AS) at P2.0–P2.3.

Figure 2-1. Program Memory Map in Normal Operating Mode (EA = "0")

Figure 2-2. Program Memory Map in ROM-less Operating Mode (EA = "1")

# **REGISTER ARCHITECTURE (RAM)**

## **INTERNAL REGISTER FILE**

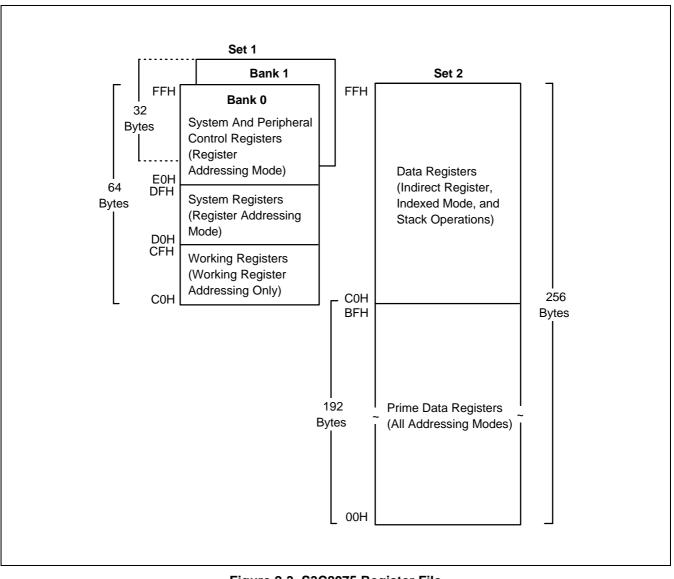

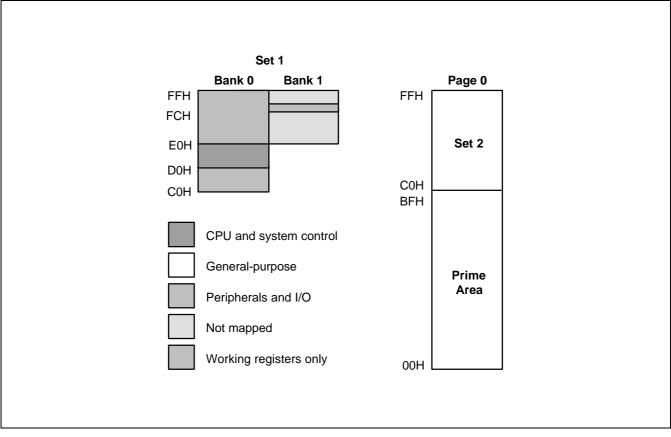

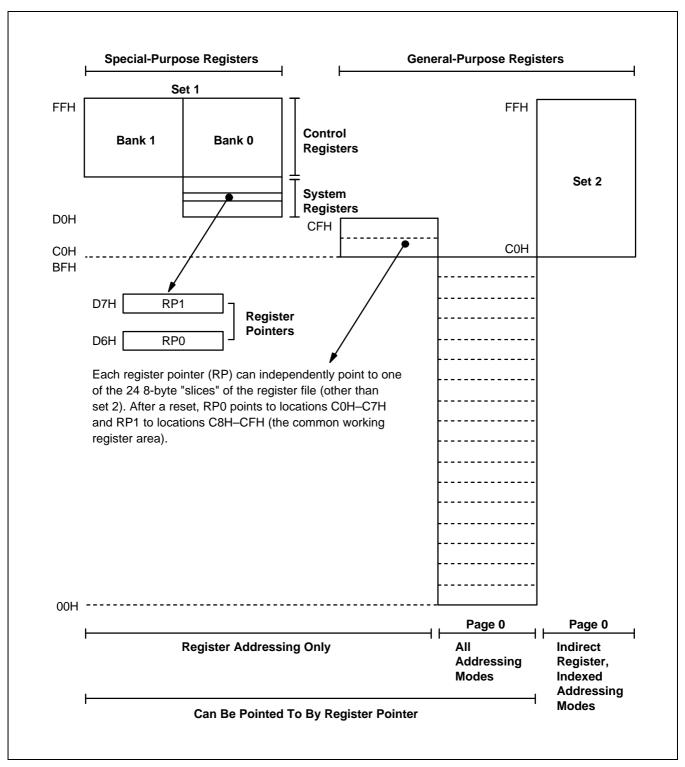

The 256-byte register file is logically extended by duplicating its upper 64-byte area. This creates two 64-byte address space, set1 and set2. The duplication divides the upper 32 bytes of set1 into two parts (bank0 and bank1).

This register file extension is supported by specific addressing mode restrictions. The total addressable internal register space is thereby expanded from 256 bytes to 352 bytes.

S3C8075 can access 321 8-bit registers in the 352-byte space. Of the 272 general-purpose registers, 208 can be used as accumulators, address pointers, index registers, data registers, or stack registers.

| Register Type                                                                          | Number of Bytes         |

|----------------------------------------------------------------------------------------|-------------------------|

| General-purpose registers<br>(Including the 16-byte common working registers)          | 272                     |

| CPU and system control register<br>(Including system and peripheral control registers) | 47 (bank0)<br>2 (bank1) |

| Total address bytes                                                                    | 321                     |

# Table 2-1. Register Type Summary

## **REGISTER PAGE POINTER (PP)**

For many SAM87 microcontrollers, the addressable area of the internal register file can further be expanded by a register page implementation. This register file expansion, however, is not used for S3C8075.

Page addressing is normally controlled by the register page pointer (PP, DFH). As the page pointer is not used in the S3C8075 implementation, it always points to page 0.

## **REGISTER SET 1**

The term *set 1* refers to the upper 64 bytes of the internal register file (C0H–FFH). The upper 32-byte(E0H– FFH) is divided into two 32-byte register banks (bank0 and bank1). Of these 96 bytes, the upper 80 bytes [(D0H– FFH) + (E0–FFH)] contain system and peripheral control registers. Of these 80 bytes, S3C8075 use 49 byte registers.

The lower 16 bytes (C0H–CFH) of set 1 are used for working register addressing. This 16-byte area is called the *working register common area* because registers in these locations can serve as buffers for data transfers between register locations.

The register pointers RP0 and RP1 always point to the working register common area after a reset operation. You can access set 1 registers at all times using the register addressing mode. You can access the 16-byte working register common area using working register addressing only.

Section 2 of this document explains the difference between register addressing mode and working register addressing.

# **REGISTER SET 2**

The same 64-byte physical space that is used for set 1 register locations C0H–FFH is logically duplicated to add 64 bytes of register space. This expanded area of the register file is called *set 2*.

The logical division of set 1 and set 2 is maintained by means of addressing mode restrictions: Set 1 can be accessed using Register addressing mode only; set 2 can only be accessed indirectly using Register Indirect or Indexed addressing mode.

# **192-BYTE PRIME REGISTER SPACE**

The lower 192 bytes of the register file (00H–BFH) is called the *prime register space*. You can access registers in these locations at any time using any addressing mode. Registers in the prime register space are immediately addressable after a reset.

Figure 2-3. S3C8075 Register File

## PRIME REGISTER SPACE

The lower 192 bytes of the 256-byte physical internal register file (00H–BFH) is called the *prime register space* or, more simply, the *prime area*. You can access registers in this address range as page 0, and using any of the seven explicit addressing modes (see Section 3, Addressing Modes). All registers in the prime area are addressable immediately following a reset.

Figure 2-4. Set 1, Set 2, and Prime Area Register Map

## WORKING REGISTERS

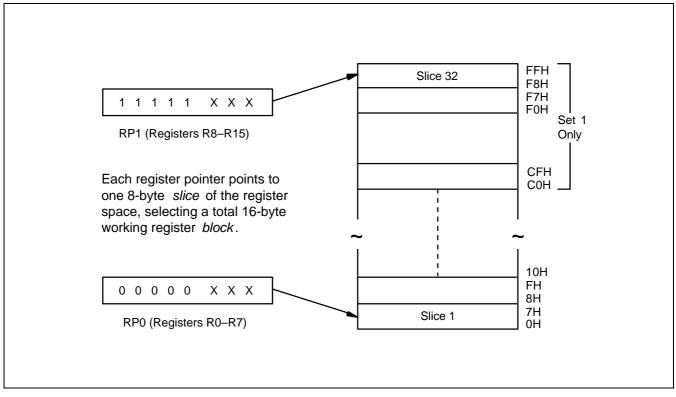

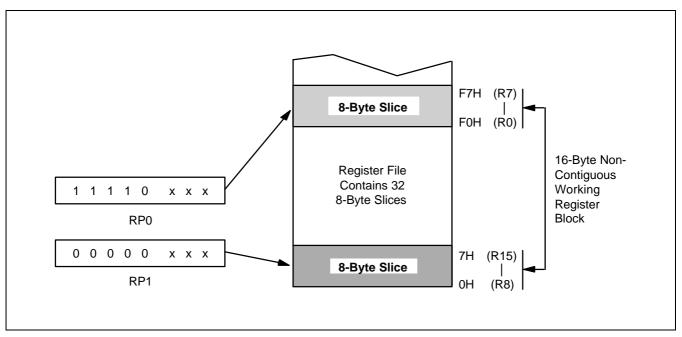

Instructions can access specific 8-bit registers or 16-bit register pairs using either 4-bit or 8-bit address fields. When 4-bit working register addressing is used, the 256-byte register file can be viewed by the programmer as 32 8-byte register groups or "slices". Each slice consists of eight 8-bit registers.

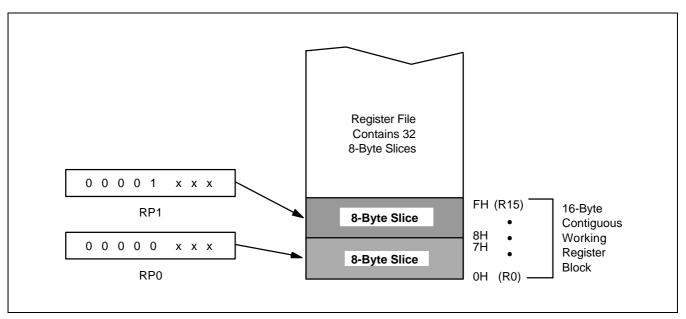

Using the two 8-bit register pointers, RP1 and RP0, two working register slices can be selected at any time to form a 16-byte working register block. Using the register pointers, you can move this 16-byte register block to anywhere in the addressable register file, except for the set 2 area.

The terms *slice* and *block* are used in this manual to help you visualize the size and relative locations of selected working register spaces:

- One working register *slice* is 8 bytes (eight 8-bit working registers; R0–R7 or R8–R15)

- One working register *block* is 16 bytes (sixteen 8-bit working registers; R0–R15)

All the registers in an 8-byte working register slice have the same binary value for their five most significant address bits. This makes it possible for each register pointer to point to one of the 24 slices in the register file. The base addresses for the two selected 8-byte register slices are contained in register pointers RP0 and RP1.

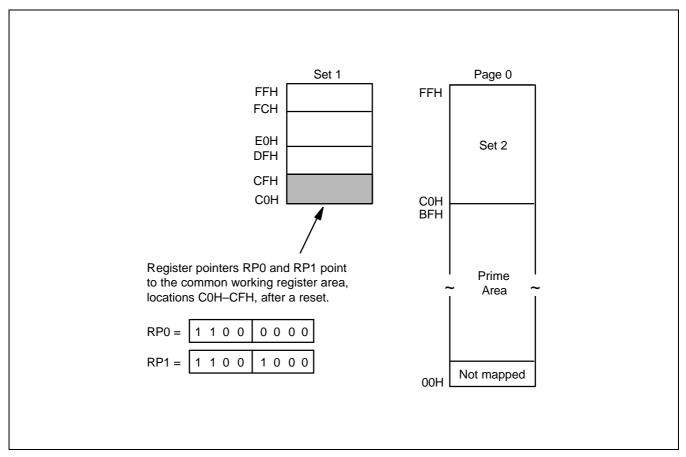

After a reset, RP0 and RP1 always point to the 16-byte common area in set 1 (C0H–CFH).

Figure 2-5. 8-Byte Working Register Areas (Slices)

#### **USING THE REGISTER POINTERS**

Register pointers RP0 and RP1, mapped to addresses D6H and D7H in set 1, are used to select two movable 8-byte working register slices in the register file. After a reset, they point to the working register common area: RP0 points to addresses C0H–C7H, and RP1 points to addresses C8H–CFH.

To change a register pointer value, you load a new value to RP0 and/or RP1 using an SRP or LD instruction (see Figures 2-6 and 2-7).

With working register addressing, you can only access those two 8-bit slices of the register file that are currently pointed to by RP0 and RP1. You cannot, however, use the register pointers to select a working register area in set 2, C0H–FFH, because these locations can be accessed only using the Indirect Register or Indexed addressing modes.

The selected 16-byte working register block usually consists of two contiguous 8-byte slices. As a general programming guideline, we recommend that RP0 point to the "lower" slice and RP1 point to the "upper" slice (see Figure 2-6). In some cases, it may be necessary to define working register areas in different (non-contiguous) areas of the register file. In Figure 2-7, RP0 points to the "upper" slice and RP1 to the "lower" slice.

Because a register pointer can point to either of the two 8-byte slices in the working register block, you can define the working register area very flexibly to support program requirements.

#### PROGRAMMING TIP — Setting the Register Pointers

| SRP #70H ;     | RP0 ← 70H, RP1 ← 78H                            |

|----------------|-------------------------------------------------|

| SRP1 #48H ;    | $RP0 \leftarrow no change, RP1 \leftarrow 48H,$ |

| SRP0 #0A0H ;   | $RP0 \leftarrow A0H, RP1 \leftarrow no change$  |

| CLR RP0 ;      | $RP0 \leftarrow 00H, RP1 \leftarrow no change$  |

| LD RP1,#0F8H ; | $RP0 \leftarrow no change, RP1 \leftarrow 0F8H$ |

Figure 2-6. Contiguous 16-Byte Working Register Block

Figure 2-7. Non-Contiguous 16-Byte Working Register Block

# PROGRAMMING TIP — Using the RPs to Calculate the Sum of a Series of Registers

Calculate the sum of registers 80H–85H using the register pointer and working register addressing. The register addresses 80H through 85H contain the values 10H, 11H, 12H, 13H, 14H, and 15 H, respectively:

| SRP0 | #80H  | ; RP0 ← 80H                   |

|------|-------|-------------------------------|

| ADD  | R0,R1 | ; R0 $\leftarrow$ R0 + R1     |

| ADC  | R0,R2 | ; $R0 \leftarrow R0 + R2 + C$ |

| ADC  | R0,R3 | ; $R0 \leftarrow R0 + R3 + C$ |

| ADC  | R0,R4 | ; $R0 \leftarrow R0 + R4 + C$ |

| ADC  | R0,R5 | ; $R0 \leftarrow R0 + R5 + C$ |

The sum of these six registers, 6FH, is located in the register R0 (80H). The instruction string used in this example takes 12 bytes of instruction code and its execution time is 36 cycles. If the register pointer is not used to calculate the sum of these registers, the following instruction sequence would have to be used:

| ADD | 80H,81H | ; 80H ← (80H) + (81H)                |

|-----|---------|--------------------------------------|

| ADC | 80H,82H | ; 80H $\leftarrow$ (80H) + (82H) + C |

| ADC | 80H,83H | ; 80H $\leftarrow$ (80H) + (83H) + C |

| ADC | 80H,84H | ; 80H $\leftarrow$ (80H) + (84H) + C |

| ADC | 80H,85H | ; 80H $\leftarrow$ (80H) + (85H) + C |

Now, the sum of the six registers is also located in register 80H. However, this instruction string takes 15 bytes of instruction code instead of 12 bytes, and its execution time is 50 cycles instead of 36 cycles.

# **REGISTER ADDRESSING**

The SAM8 register architecture provides an efficient method of working register addressing that takes full advantage of shorter instruction formats to reduce execution time.

With Register (R) addressing mode, in which the operand value is the content of a specific register or register pair, you can access all locations in the register file except for set 2. With working register addressing, you use a register pointer to specify an 8-byte working register space in the register file and an 8-bit register within that space.

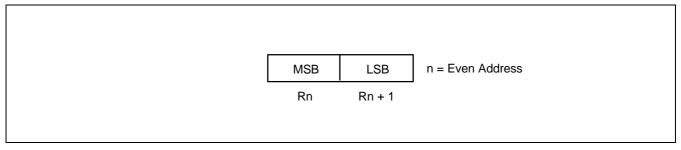

Registers are addressed either as a single 8-bit register or as a paired 16-bit register space. In a 16-bit register pair, the address of the first 8-bit register is always an even number and the address of the next register is always an odd number. The most significant byte of the 16-bit data is always stored in the even-numbered register; the least significant byte is always stored in the next (+ 1) odd-numbered register.

Working register addressing differs from Register addressing because it uses a register pointer to specify an 8-byte working register space in the register file and an 8-bit register within that space (see Figure 2-8).

Figure 2-8. 16-Bit Register Pair

## Figure 2-9. Register File Addressing

## COMMON WORKING REGISTER AREA (C0H-CFH)

After a reset, register pointers RP0 and RP1 automatically select two 8-byte register slices in set 1, locations C0H–CFH, as the active 16-byte working register block:

$\begin{array}{rrr} \text{RP0} \ \rightarrow \ \text{C0H-C7H} \\ \text{RP1} \ \rightarrow \ \text{C8H-CFH} \end{array}$

This16-byte address range is called *common working register area*. That is, locations in this area can be used as working registers by operations that address any location on any page in the register file. Typically, these working registers serve as temporary buffers for data operations between different pages. However, because S3C8075 uses only page 0, you can use the common working register area for any internal data operation.

Figure 2-10. Common Working Register Area

## PROGRAMMING TIP — Addressing the Common Working Register Area

As the following examples show, you should access working registers in the common area, locations C0H–CFH, using working register addressing mode only.

| Examples | 1. | LD                                       | 0C2H,40H                   | ;   | Invalid addressing mode!                        |

|----------|----|------------------------------------------|----------------------------|-----|-------------------------------------------------|

|          |    | Use wo                                   | orking register addressing | ins | tead:                                           |

|          |    | SRP<br>LD                                | #0C0H<br>R2,40H            | ;   | R2 (C2H) $\leftarrow$ the value in location 40H |

|          | 2. | ADD                                      | 0C3H,#45H                  | ;   | Invalid addressing mode!                        |

|          |    | Use working register addressing instead: |                            |     |                                                 |

|          |    | SRP<br>ADD                               | #0C0H<br>R3,#45H           | ;   | R3 (C3H) ← R3 + 45H                             |

#### **4-BIT WORKING REGISTER ADDRESSING**

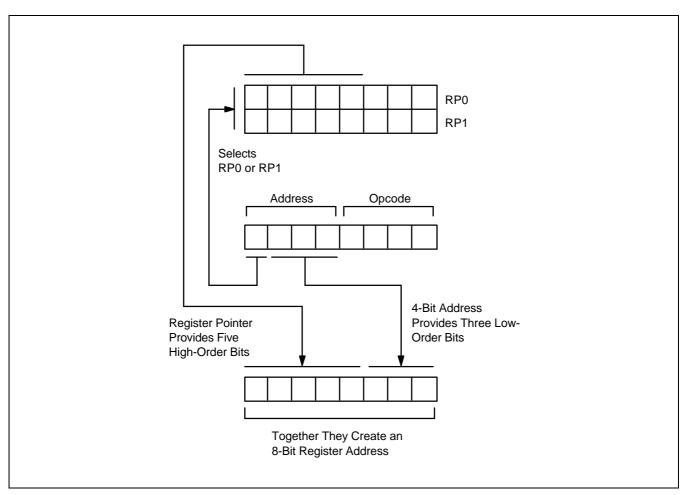

Each register pointer defines a movable 8-byte slice of working register space. The address information stored in a register pointer serves as an addressing "window" that makes it possible for instructions to access working registers very efficiently using short 4-bit addresses. When an instruction addresses a location in the selected working register area, the address bits are concatenated in the following way to form a complete 8-bit address:

- The high-order bit of the 4-bit address selects one of the register pointers ("0" selects RP0; "1" selects RP1);

- The five high-order bits in the register pointer select an 8-byte slice of the register space;

- The three low-order bits of the 4-bit address select one of the eight registers in the slice.

As shown in Figure 2-11, the result of this operation is that the five high-order bits from the register pointer are concatenated with the three low-order bits from the instruction address to form the complete address. As long as the address stored in the register pointer remains unchanged, the three bits from the address will always point to an address in the same 8-byte register slice.

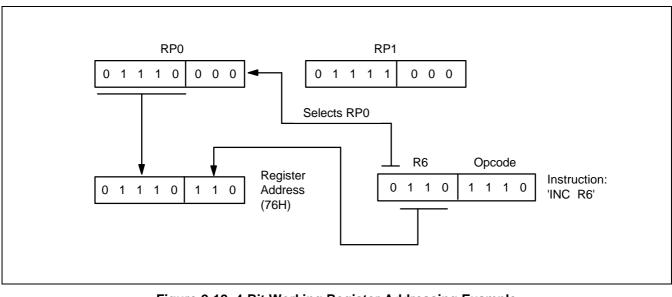

Figure 2-12 shows a typical example of 4-bit working register addressing: The high-order bit of the instruction 'INC R6' is "0", which selects RP0. The five high-order bits stored in RP0 (01110B) are concatenated with the three low-order bits of the instruction's 4-bit address (110B) to produce the register address 76H (01110110B).

Figure 2-11. 4-Bit Working Register Addressing

Figure 2-12. 4-Bit Working Register Addressing Example

## 8-BIT WORKING REGISTER ADDRESSING

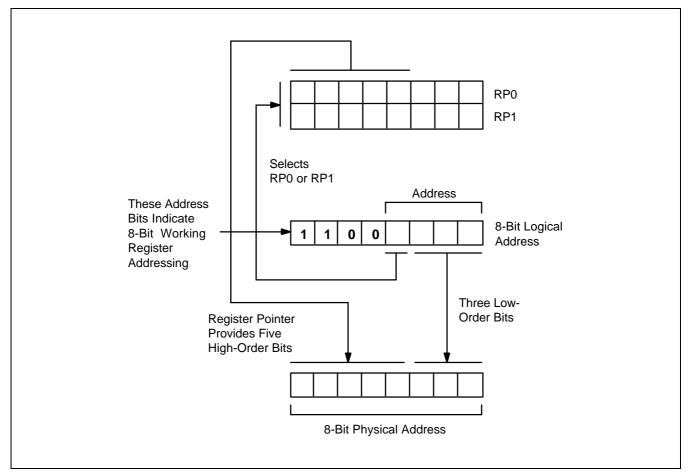

You can also use 8-bit working register addressing to access registers in a selected working register area. To initiate 8-bit working register addressing, the upper four bits of the instruction address must contain the value 1100B. This 4-bit value (1100B) indicates that the remaining four bits have the same effect as 4-bit working register addressing.

As shown in Figure 2-13, the lower nibble of the 8-bit address is concatenated in much the same way as for 4-bit addressing: Bit 3 selects either RP0 or RP1, which then supplies the five high-order bits of the final address; the three low-order bits of the complete address are provided by the original instruction.

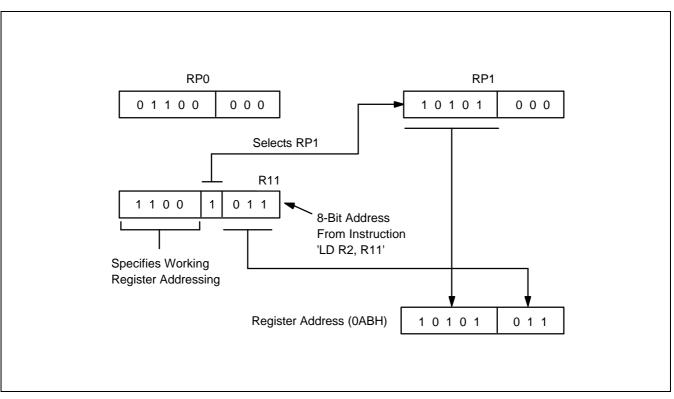

Figure 2-14 shows an example of 8-bit working register addressing: The four high-order bits of the instruction address (1100B) specify 8-bit working register addressing. Bit 4 ("1") selects RP1 and the five high-order bits in RP1 (10101B) become the five high-order bits of the register address. The three low-order bits of the register address (011) are provided by the three low-order bits of the 8-bit instruction address. The five address bits from RP1 and the three address bits from the instruction are concatenated to form the complete register address, 0ABH (101011B).

Figure 2-13. 8-Bit Working Register Addressing

Figure 2-14. 8-Bit Working Register Addressing Example

# SYSTEM AND USER STACKS

S3C8-series microcontrollers use the system stack for to implementing subroutine calls and returns and for dynamic data storage. The PUSH and POP instructions support system stack operations.

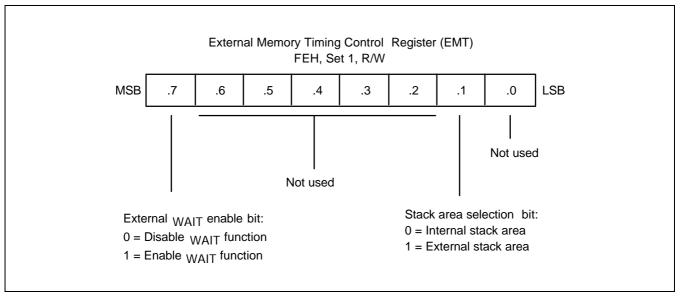

Stack operations in the internal register file and in external data memory are supported by hardware. Bit 1 in the external memory timing register EMT selects an internal or external stack area.

The 16-bit stack pointer register (SPH, SPL) is used for external stack access. An 8-bit stack pointer (SPL) is sufficient for internal stack addressing.

## **Stack Operations**

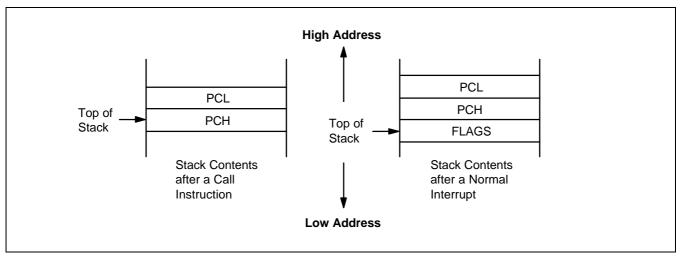

Return addresses for procedure calls, interrupts, and data are stored on the stack. The contents of the PC are saved to stack by a CALL instruction and restored by the RET instruction. When an interrupt occurs, the contents of the PC and the FLAGS register are pushed to the stack. The IRET instruction then pops these values back to their original locations. The stack address is always decremented *before* a push operation and incremented *after* a pop operation. The stack pointer (SP) always points to the stack frame stored on the top of the stack, as shown in Figure 2-15.

Figure 2-15. Stack Operations

## **User-Defined Stacks**

You can freely define stacks in the internal register file as data storage locations. The instructions PUSHUI, PUSHUD, POPUI, and POPUD support user-defined stack operations.

## Stack Pointers (SPL, SPH)

Register locations D8H and D9H contain the 16-bit stack pointer (SP) that is used for system stack operations. The most significant byte of the SP address, SP15–SP8, is stored in the SPH register (D8H); the least significant byte, SP7–SP0, is stored in the SPL register (D9H). After a reset, the SP value is undetermined.

Because only internal memory space is implemented in S3C8075/P8075, the SPL must be initialized to an 8-bit value in the range 00H–FFH; the SPH register is not needed but can be used as a general-purpose register, if necessary.

When the SPL register contains the stack pointer value only (that is, when it points to a system stack in the register file), you can use the SPH register as a general-purpose data register. However, if an overflow or underflow condition occurs as the result of incrementing or decrementing the stack address in the SPL register during normal stack operations, the value in the SPL register will overflow (or underflow) to the SPH register, overwriting any other data that is currently stored there. To avoid overwriting data in the SPH register, you can initialize the SPL value to 'FFH' instead of '00H'.

## PROGRAMMING TIP — Standard Stack Operations Using PUSH and POP

| The following example shows you how to perform stack operations in the internal register file using PUSH and |

|--------------------------------------------------------------------------------------------------------------|

| POP instructions:                                                                                            |

| LD<br>• | SPL,#0FFH | <ul> <li>; SPL ← FFH</li> <li>; (Normally, the SPL is set to 0FFH by the initialization</li> <li>; routine)</li> </ul> |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------|

| •       |           |                                                                                                                        |

| PUSH    | PP        | ; Stack address 0FEH $\leftarrow$ PP                                                                                   |

| PUSH    | RP0       | ; Stack address 0FDH $\leftarrow$ RP0                                                                                  |

| PUSH    | RP1       | ; Stack address 0FCH ← RP1                                                                                             |

| PUSH    | R3        | ; Stack address 0FBH $\leftarrow$ R3                                                                                   |

| •       |           |                                                                                                                        |

| •       |           |                                                                                                                        |

| •       |           |                                                                                                                        |

| POP     | R3        | ; R3 ← Stack address 0FBH                                                                                              |

| POP     | RP1       | ; RP1 $\leftarrow$ Stack address 0FCH                                                                                  |

| POP     | RP0       | $RP0 \leftarrow Stack address 0FDH$                                                                                    |

| POP     | PP        | $PP \leftarrow Stack address 0FEH$                                                                                     |

|         |           | , <u> </u>                                                                                                             |

# **3** ADDRESSING MODES

# **OVERVIEW**

The program counter is used to fetch instructions that are stored in program memory for execution. Instructions indicate the operation to be performed and the data to be operated on. *Addressing mode* is the method used to determine the location of the data operand. The operands specified in SAM8 instructions may be condition codes, immediate data, or a location in the register file, program memory, or data memory.

The SAM8 instruction set supports seven explicit addressing modes. Not all of these addressing modes are available for each instruction:

- Register (R)

- Indirect Register (IR)

- Indexed (X)

- Direct Address (DA)

- Indirect Address (IA)

- Relative Address (RA)

- Immediate (IM)

# **REGISTER ADDRESSING MODE (R)**

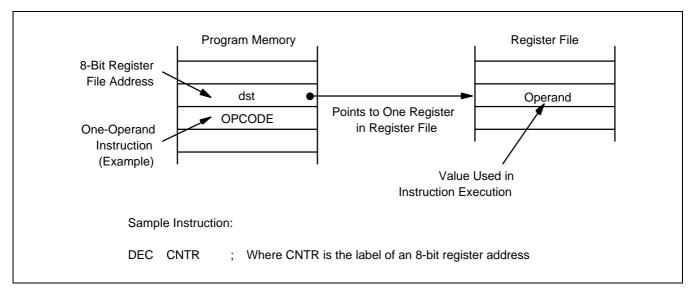

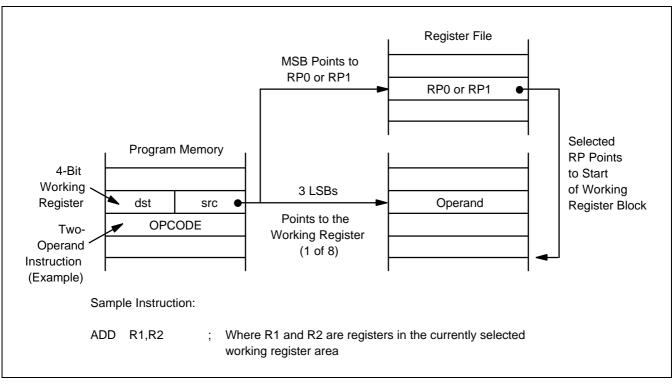

In Register addressing mode, the operand is the content of a specified register or register pair (see Figure 3-1). Working register addressing differs from Register addressing because it uses a register pointer to specify an 8-byte working register space in the register file and an 8-bit register within that space (see Figure 3-2).

Figure 3-1. Register Addressing

Figure 3-2. Working Register Addressing

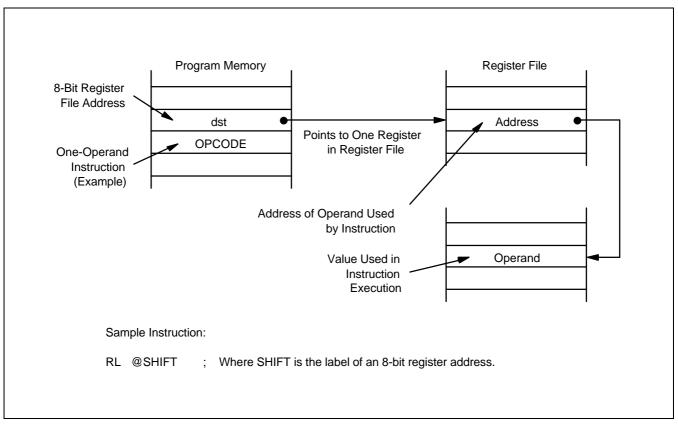

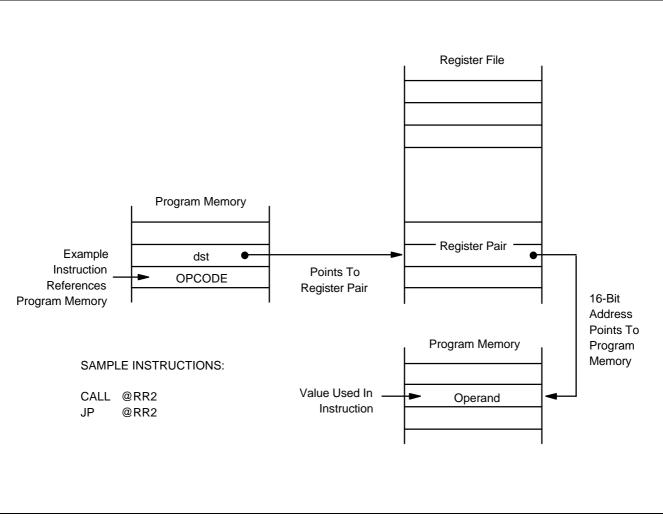

#### **INDIRECT REGISTER ADDRESSING MODE (IR)**

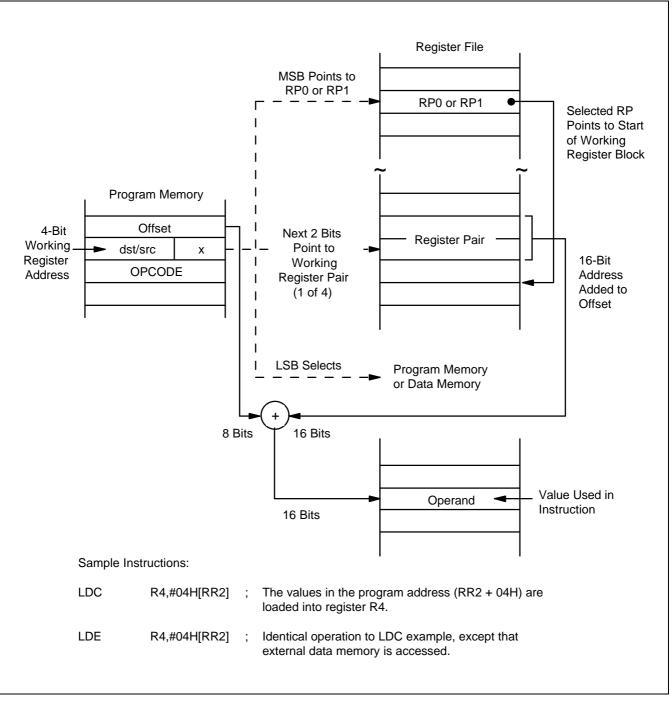

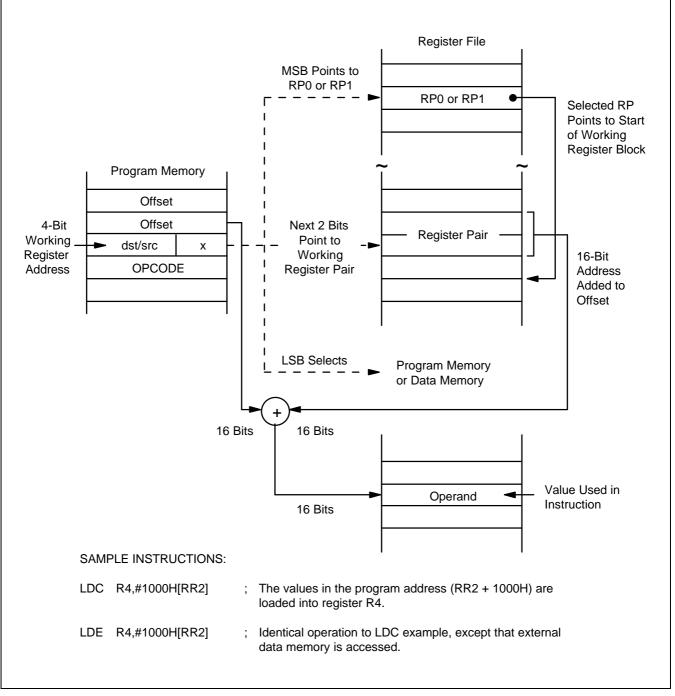

In Indirect Register (IR) addressing mode, the content of the specified register or register pair is the address of the operand. Depending on the instruction used, the actual address may point to a register in the register file, to program memory (ROM), or to an external memory space, if implemented (see Figures 3-3 through 3-6).

You can use any 8-bit register to indirectly address another register. Any 16-bit register pair can be used to indirectly address another memory location. Remember, however, that locations C0H–FFH in set 1 cannot be accessed using Indirect Register addressing mode.

Figure 3-3. Indirect Register Addressing to Register File

Figure 3-4. Indirect Register Addressing to Program Memory

INDIRECT REGISTER ADDRESSING MODE (Continued)

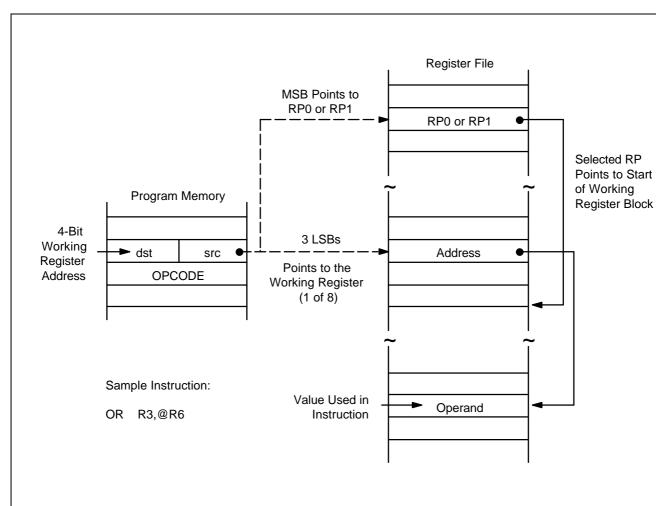

Figure 3-5. Indirect Working Register Addressing to Register File

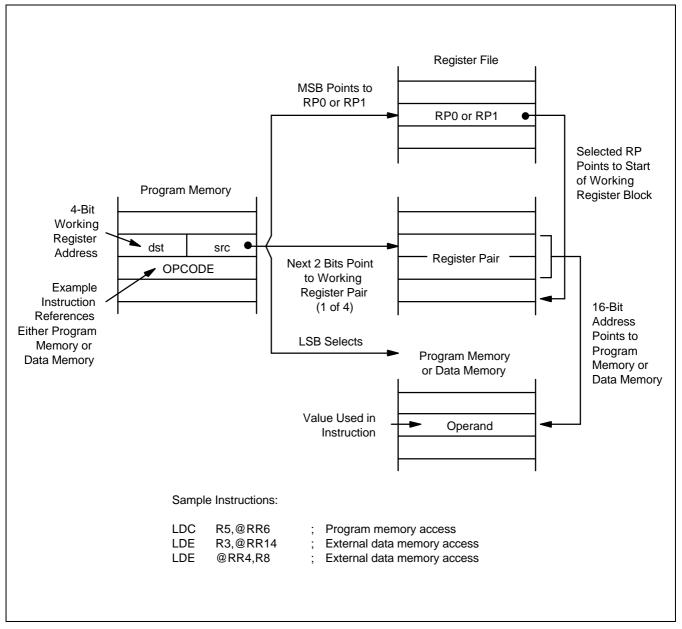

Figure 3-6. Indirect Working Register Addressing to Program or Data Memory

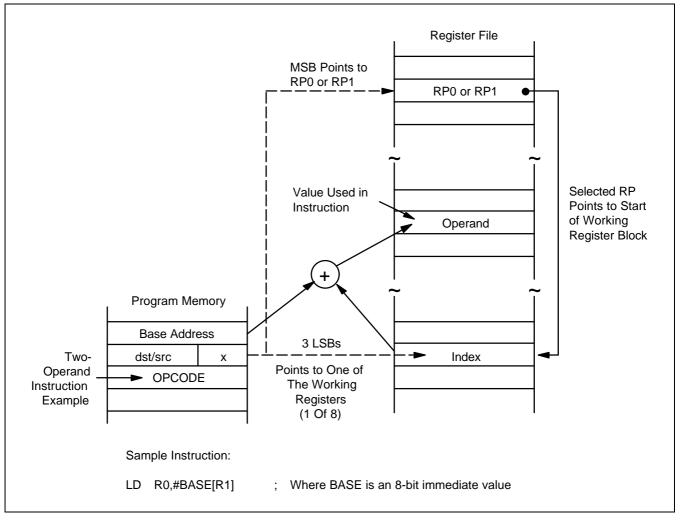

#### **INDEXED ADDRESSING MODE (X)**

Indexed (X) addressing mode adds an offset value to a base address during an instruction execution in order to calculate the effective operand address (see Figure 3-7). You can use Indexed addressing mode to access locations in the internal register file or in external memory (if implemented). You cannot, however, access locations C0H–FFH in set 1 using Indexed addressing.

In short offset Indexed addressing mode, the 8-bit displacement is treated as a signed integer in the range –128 to +127. This applies to external memory accesses only (see Figure 3-8).

For register file addressing, an 8-bit base address provided by the instruction is added to an 8-bit offset contained in a working register. For external memory accesses, the base address is stored in the working register pair designated in the instruction. The 8-bit or 16-bit offset given in the instruction is then added to the base address (see Figure 3-9).

The only instruction that supports Indexed addressing mode for the internal register file is the Load instruction (LD). The LDC and LDE instructions support Indexed addressing mode for internal program memory and for external data memory (if implemented).

Figure 3-7. Indexed Addressing to Register File

#### INDEXED ADDRESSING MODE (Continued)

Figure 3-8. Indexed Addressing to Program or Data Memory with Short Offset

Figure 3-9. Indexed Addressing to Program or Data Memory

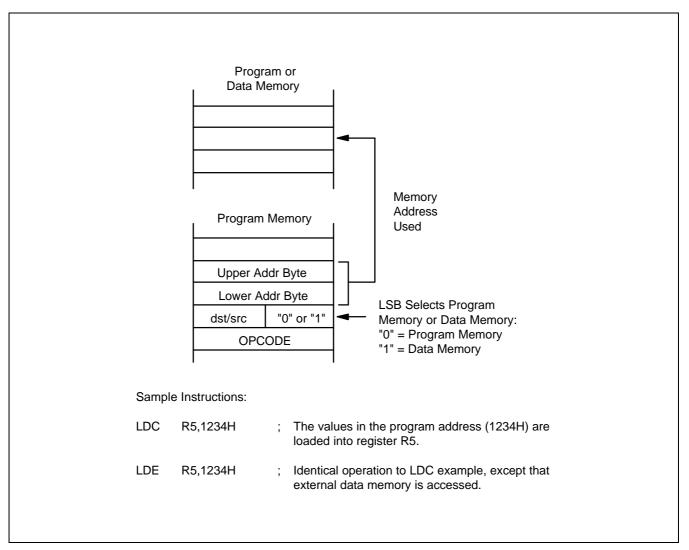

#### **DIRECT ADDRESS MODE (DA)**

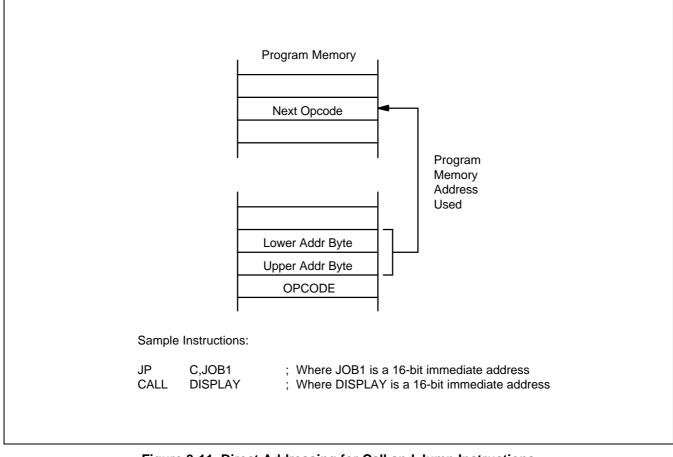

In Direct Address (DA) mode, the instruction provides the operand's 16-bit memory address. Jump (JP) and Call (CALL) instructions use this addressing mode to specify the 16-bit destination address that is loaded into the PC whenever a JP or CALL instruction is executed.

The LDC and LDE instructions can use Direct Address mode to specify the source or destination address for Load operations to program memory (LDC) or to external data memory (LDE), if implemented.

Figure 3-10. Direct Addressing for Load Instructions

#### **DIRECT ADDRESS MODE (Continued)**

Figure 3-11. Direct Addressing for Call and Jump Instructions

#### **INDIRECT ADDRESS MODE (IA)**

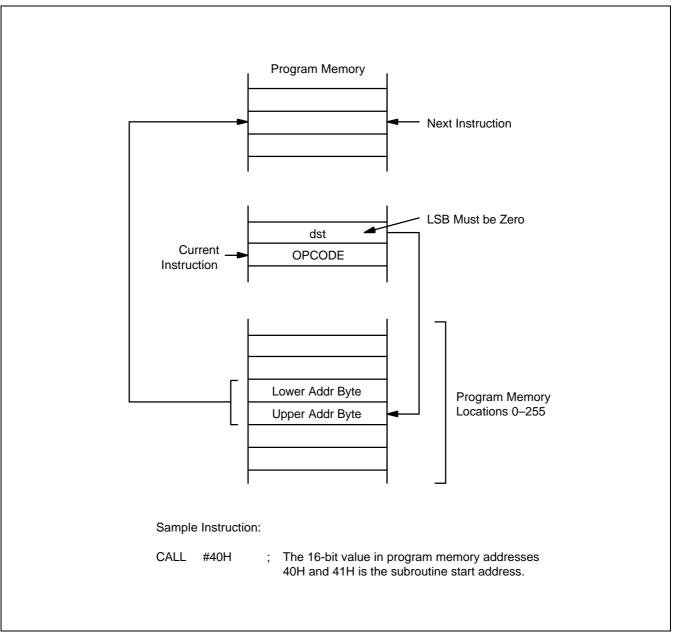

In Indirect Address (IA) mode, the instruction specifies an address located in the lowest 256 bytes of the program memory. The selected pair of memory locations contains the actual address of the next instruction to be executed. Only the CALL instruction can use the Indirect Address mode.

Because the Indirect Address mode assumes that the operand is located in the lowest 256 bytes of program memory, only an 8-bit address is supplied in the instruction; the upper bytes of the destination address are assumed to be all zeros.

Figure 3-12. Indirect Addressing

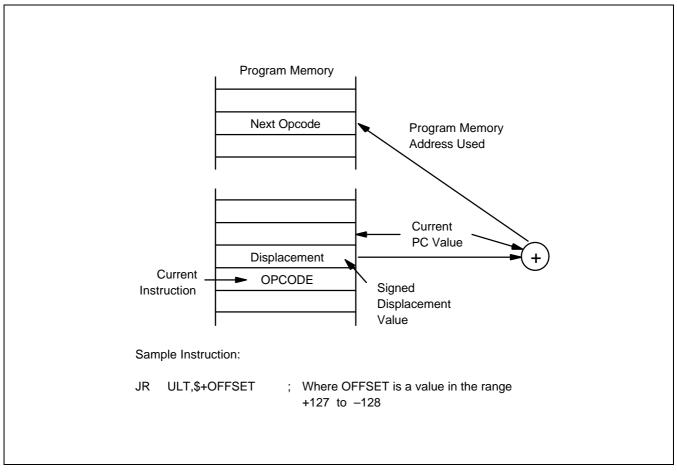

#### **RELATIVE ADDRESS MODE (RA)**

In Relative Address (RA) mode, a two's-complement signed displacement between -128 and +127 is specified in the instruction. The displacement value is then added to the current PC value. The result is the address of the next instruction to be executed. Before this addition occurs, the PC contains the address of the instruction immediately following the current instruction.

Several program control instructions use the Relative Address mode to perform conditional jumps. The instructions that support RA addressing are BTJRF, BTJRT, DJNZ, CPIJE, CPIJNE, and JR.

Figure 3-13. Relative Addressing

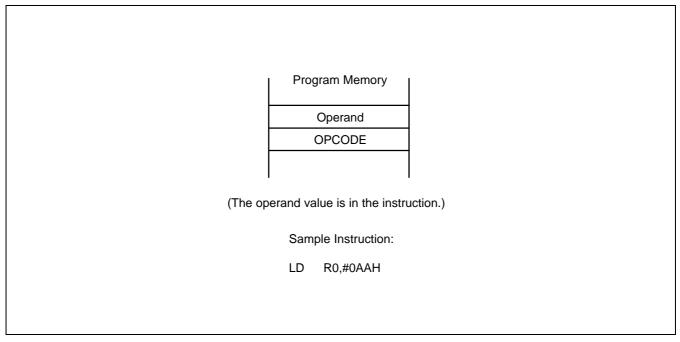

### **IMMEDIATE MODE (IM)**

In Immediate (IM) mode, the operand value used in the instruction is the value supplied in the operand field itself. The operand may be one byte or one word in length, depending on the instruction used. Immediate addressing mode is useful for loading constant values into registers.

Figure 3-14. Immediate Addressing

# 4 CONTROL REGISTERS

# OVERVIEW

In this section, detailed descriptions of the S3C8075/P8075 control registers are presented in an easy-to-read format. You can use this section as a quick-reference source when writing application programs.

The locations and read/write characteristics of all mapped registers in the S3C8075/P8075 register files are presented in Tables 4-1, 4-2, and 4-3. The hardware reset values for these registers are described in Section 8, "RESET and Power-Down."

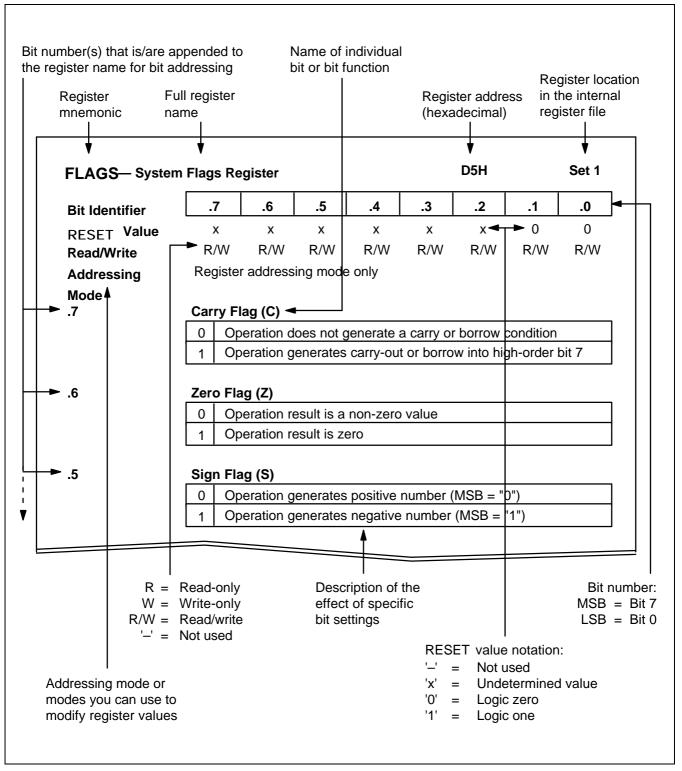

Figure 4-1 illustrates the important features of the standard register description format.

Control register descriptions are arranged in alphabetical order according to register mnemonic. More detailed information about control registers is presented in the context of the specific peripheral hardware descriptions in Part II of this manual.

| Register Name                           | Mnemonic | Decimal | Hex | R/W      |  |  |  |  |  |  |  |

|-----------------------------------------|----------|---------|-----|----------|--|--|--|--|--|--|--|

| Timer C Counter Register (High Byte)    | ТСН      | 208     | D0H | R/W      |  |  |  |  |  |  |  |

| Timer C Counter Register (Low Byte)     | TCL      | 209     | D1H | R/W      |  |  |  |  |  |  |  |

| Location D2H is not mapped.             |          |         |     |          |  |  |  |  |  |  |  |

| Basic Timer Control Register (watchdog) | BTCON    | 211     | D3H | R/W      |  |  |  |  |  |  |  |

| Clock Control Register                  | CLKCON   | 212     | D4H | R/W      |  |  |  |  |  |  |  |

| System Flags Register                   | FLAGS    | 213     | D5H | R/W      |  |  |  |  |  |  |  |

| Register Pointer 0                      | RP0      | 214     | D6H | R/W      |  |  |  |  |  |  |  |

| Register Pointer 1                      | RP1      | 215     | D7H | R/W      |  |  |  |  |  |  |  |

| Stack Pointer (High Byte)               | SPH      | 216     | D8H | R/W      |  |  |  |  |  |  |  |

| Stack Pointer (Low Byte)                | SPL      | 217     | D9H | R/W      |  |  |  |  |  |  |  |

| Instruction Pointer (High Byte)         | IPH      | 218     | DAH | R/W      |  |  |  |  |  |  |  |

| Instruction Pointer (Low Byte)          | IPL      | 219     | DBH | R/W      |  |  |  |  |  |  |  |

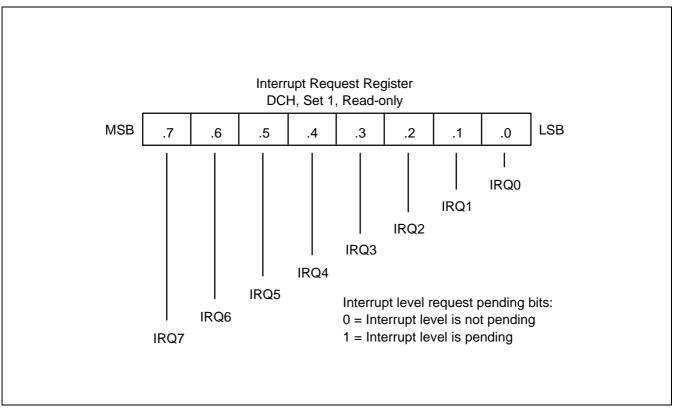

| Interrupt Request Register              | IRQ      | 220     | DCH | R (note) |  |  |  |  |  |  |  |

| Interrupt Mask Register                 | IMR      | 221     | DDH | R/W      |  |  |  |  |  |  |  |

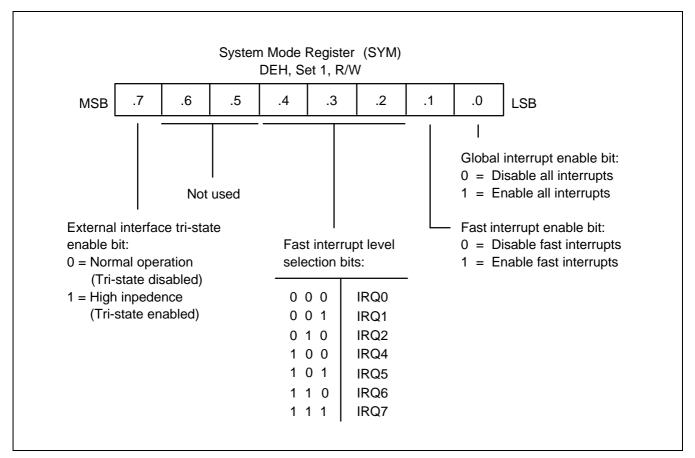

| System Mode Register                    | SYM      | 222     | DEH | R/W      |  |  |  |  |  |  |  |

| Register Page Pointer                   | PP       | 223     | DFH | R/W      |  |  |  |  |  |  |  |

Table 4-1. Set 1 Registers

**NOTE**: You cannot use a read-only register (IRQ) as a destination field for the instructions OR, AND, LD, or LDB.

| Register Name                          | Mnemonic | Decimal | Hex | R/W |

|----------------------------------------|----------|---------|-----|-----|

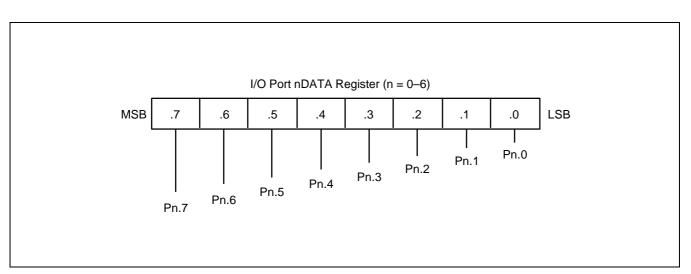

| Port 0 Data Register                   | P0       | 224     | E0H | R/W |

| Port 1 Data Register                   | P1       | 225     | E1H | R/W |

| Port 2 Data Register                   | P2       | 226     | E2H | R/W |

| Port 3 Data Register                   | P3       | 227     | E3H | R/W |

| Port 4 Data Register                   | P4       | 228     | E4H | R/W |

| Port 5 Data Register                   | P5       | 229     | E5H | R/W |

| Port 6 Data Register                   | P6       | 230     | E6H | R/W |

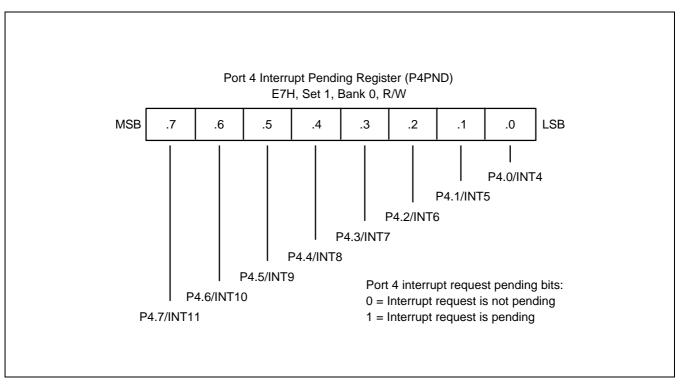

| Port4 Interrupt Pending Register       | P4PND    | 231     | E7H | R/W |

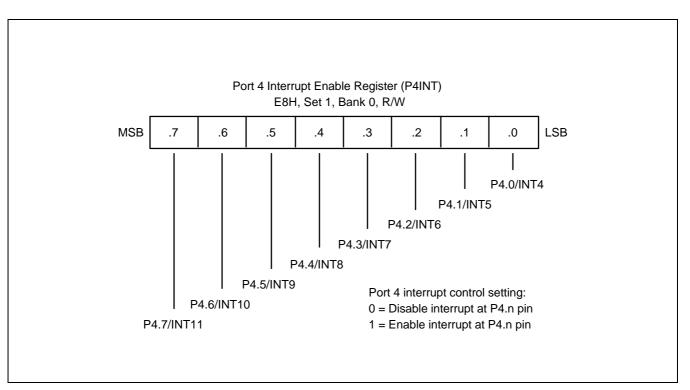

| Port 4 Interrupt Enable Register       | P4INT    | 232     | E8H | R/W |

| Serial Port Shift Register             | SIO      | 233     | E9H | R/W |

| Serial Port Control Register           | SIOCON   | 234     | EAH | R/W |

| Serial Port Interrupt Pending Register | SIOPND   | 235     | EBH | R/W |

| Table 4-2. | Set 1. | Bank 0 | Registers |

|------------|--------|--------|-----------|

|            |        | Dann V |           |

| Register Name                       | Mnemonic            | Decimal       | Hex | R/W      |

|-------------------------------------|---------------------|---------------|-----|----------|

| U U                                 |                     |               |     |          |

| Timer A Data Register               | TADATA              | 236           | ECH | R/W      |

| Timer B Data Register               | TBDATA              | 237           | EDH | R/W      |

| Timer Module 0 Control Register     | TOCON               | 238           | EEH | R/W      |

| Timer B Interrupt Register          | TBINT               | 239           | EFH | W        |

| Port 0 Control Register             | POCON               | 240           | F0H | R/W      |

| Port 1 Control Register             | P1CON               | 241           | F1H | R/W      |

| Port 2 Control Register (High Byte) | P2CONH              | 242           | F2H | R/W      |

| Port 2 Control Register (Low Byte)  | P2CONL              | 243           | F3H | R/W      |

| Port 3 Control Register (High Byte) | P3CONH              | 244           | F4H | R/W      |

| Port 3 Control Register (Low Byte)  | P3CONL              | 245           | F5H | R/W      |

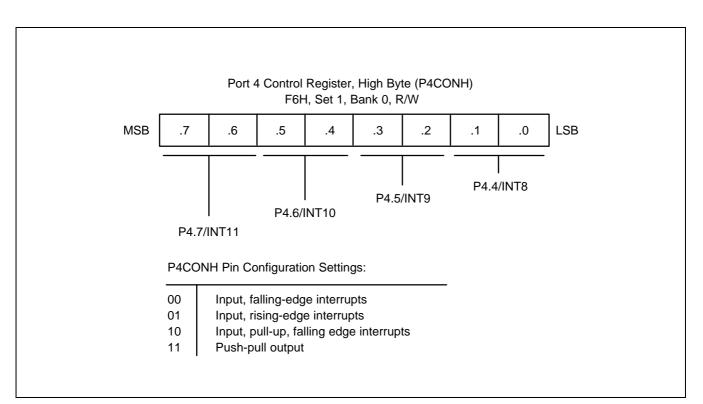

| Port 4 Control Register (High Byte) | P4CONH              | 246           | F6H | R/W      |

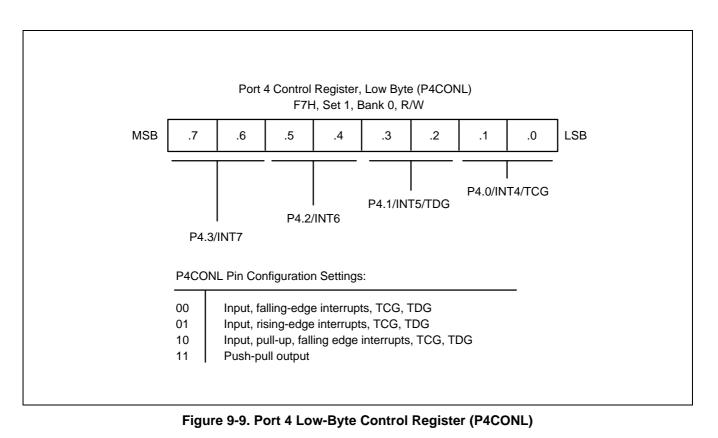

| Port 4 Control Register (Low Byte)  | P4CONL              | 247           | F7H | R/W      |

| Timer D Counter Register(High Byte) | TDH                 | 248           | F8H | R/W      |

| Timer D Counter Register(Low Byte)  | TDL                 | 249           | F9H | R/W      |

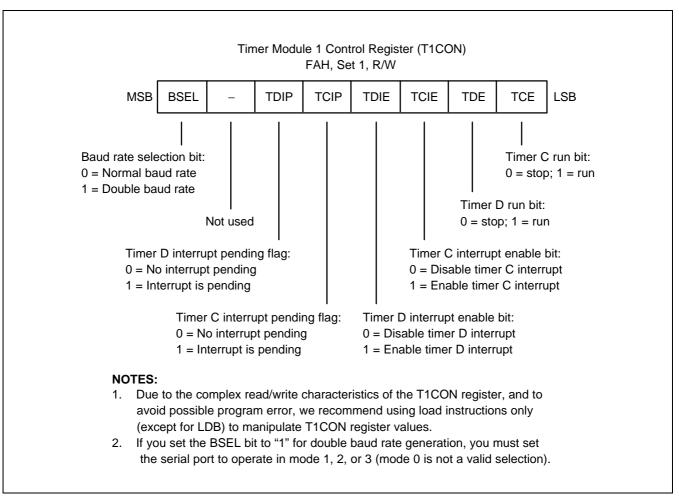

| Timer Module 1 Control Register     | T1CON               | 250           | FAH | R/W      |

| Timer Module 1 Mode Register        | T1MOD               | 251           | FBH | R/W      |

| Location                            | FCH is reserved for | factory test. | ·   | ·        |

| Basic Timer counter                 | BTCNT               | 253           | FDH | R (note) |

| External Memory Timing Register     | EMT                 | 254           | FEH | R/W      |

| Interrupt Priority Register         | IPR                 | 255           | FFH | R/W      |

Table 4-2. Set 1, Bank 0 Registers (Continued)

NOTE: You cannot use a read-only register (BTCNT) as a destination field for the instructions OR, AND, LD, or LDB.

| Register Name           | Mnemonic | Decimal | Hex | R/W |

|-------------------------|----------|---------|-----|-----|

| Port 5 Control Register | P5CON    | 248     | F8H | R/W |

| Port 6 Control Register | P6CON    | 249     | F9H | R/W |

Table 4-3. Set 1, Bank 1 Registers

Figure 4-1. Register Description Format

| STCON — Basi    |                                                  |                                                                                             |        |        | 913131                          |                  |              | D3H        |           | Set |

|-----------------|--------------------------------------------------|---------------------------------------------------------------------------------------------|--------|--------|---------------------------------|------------------|--------------|------------|-----------|-----|

| Bit Identifier  | -                                                | 7                                                                                           | -      | 6      | .5                              | .4               | .3           | .2         | .1        | .0  |

| RESET Value     |                                                  | 0                                                                                           | (      | 0      | 0                               | 0                | 0            | 0          | 0         | 0   |

| Read/Write      | R                                                | /W                                                                                          | R/     | /W     | R/W                             | R/W              | R/W          | R/W        | R/W       | R/W |

| Addressing Mode | Reg                                              | Register addressing mode only                                                               |        |        |                                 |                  |              |            |           |     |

| 7 – .4          | Watchdog Timer Function Disable Code (for Reset) |                                                                                             |        |        |                                 |                  |              |            |           |     |

|                 | 1                                                | 0                                                                                           | 1      | 0      | Disable watchdog timer function |                  |              |            |           |     |

|                 | Ar                                               | Any other value Enable wat                                                                  |        |        |                                 | atchdog tim      | ner functior | ı          |           |     |

| 3 and .2        | Bas                                              | ic Tir                                                                                      | ner In | nout ( | Clock Sele                      | ction Bits       |              |            |           |     |

|                 | 0                                                | Basic Timer Input Clock Selection Bits           0         0         f <sub>OSC</sub> /4096 |        |        |                                 |                  |              |            |           |     |

|                 | 0                                                | 1 f <sub>OSC</sub> /1024                                                                    |        |        |                                 |                  |              |            |           |     |

|                 | 1                                                | 0                                                                                           |        |        |                                 |                  |              |            |           |     |

|                 | 1                                                | 1                                                                                           |        |        |                                 |                  |              |            |           |     |

|                 |                                                  |                                                                                             |        |        |                                 |                  |              |            |           |     |

| 1               |                                                  | r –                                                                                         |        | ount   | er Clear Bi                     | t <sup>(1)</sup> |              |            |           |     |

|                 | 0                                                |                                                                                             | effect |        |                                 |                  |              |            |           |     |

|                 | 1                                                | Clea                                                                                        | ir the | basic  | timer cour                      | iter value       |              |            |           |     |

|                 | Clo                                              | :k Fre                                                                                      | aner   | ncv D  | ivider Clea                     | ar Bit for B     | asic Time    | r and Time | er () (2) |     |

| 0               |                                                  | r                                                                                           | -      |        |                                 |                  |              |            |           |     |

| 0               | 0                                                | No e                                                                                        | meor   |        |                                 |                  |              |            |           |     |

2. When you write a "1" to BTCON.0, the corresponding frequency divider is cleared to '00H'. Immediately following the write operation, the BTCON.0 value is automatically cleared to "0".

| CLKCON – sy                                                        | stem ( | Cloc                                       | k Contro     | l Registe                | er           |                   | D4H        |           | Set 1 |  |  |

|--------------------------------------------------------------------|--------|--------------------------------------------|--------------|--------------------------|--------------|-------------------|------------|-----------|-------|--|--|

| Bit Identifier                                                     | -      | 7                                          | .6           | .5                       | .4           | .3                | .2         | .1        | .0    |  |  |

| RESET Value                                                        | (      | 0                                          | 0            | 0                        | 0            | 0                 | 0          | 0         | 0     |  |  |

| Read/Write                                                         | R      | /W                                         | R/W          | R/W                      | R/W          | R/W               | R/W        | R/W       | R/W   |  |  |

| Addressing Mode                                                    | Reg    | Register addressing mode only              |              |                          |              |                   |            |           |       |  |  |

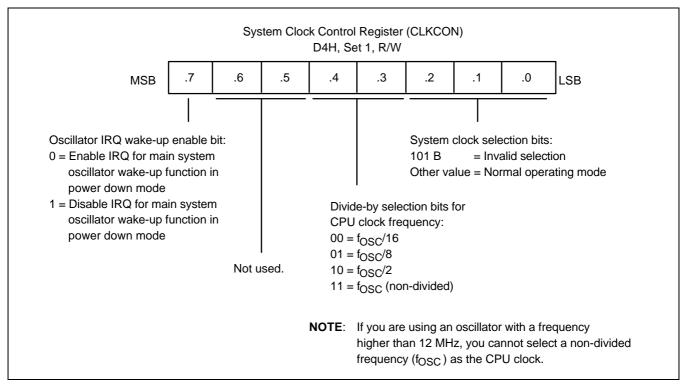

| .7                                                                 | Osc    | Oscillator IRQ Wake-up Function Enable Bit |              |                          |              |                   |            |           |       |  |  |

| 0 Enable IRQ for main system oscillator wake-up in power-down mode |        |                                            |              |                          |              |                   |            |           |       |  |  |

|                                                                    | 1      | Disa                                       | able IRQ for | main syste               | em oscillato | or wake-up        | in power-c | down mode |       |  |  |

|                                                                    |        |                                            |              |                          |              |                   |            |           | 1     |  |  |

| .6 and .5                                                          | Not    | used                                       | for S3C807   | 75/P8075.                |              |                   |            |           |       |  |  |

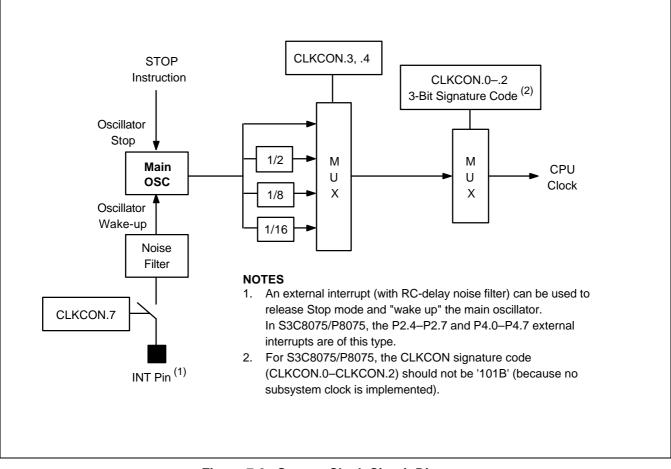

| .4 and .3                                                          | CPL    | J Clo                                      | ck (System   | ı Clock) Se              | election Bi  | ts <sup>(1)</sup> |            |           |       |  |  |

|                                                                    | 0      | 0                                          | Divide by    | 16 (f <sub>OSC</sub> /1  | 6)           |                   |            |           |       |  |  |

|                                                                    | 0      | 1                                          | Divide by    | 8 (f <sub>OSC</sub> /8)  |              |                   |            |           |       |  |  |

|                                                                    | 1      | 0                                          | Divide by    | 2 (f <sub>OSC</sub> /2)  |              |                   |            |           |       |  |  |

|                                                                    | 1      | 1                                          | Non-divid    | ed clock (f <sub>(</sub> | osc) (2)     |                   |            |           |       |  |  |

.2 – .0

#### Subsystem Clock Selection Bits (3)

| 1     | 0 | 1   | Invalid setting for S3C8075/P8075. |

|-------|---|-----|------------------------------------|

| - I I |   | lue | Select main system clock (MCLK)    |

#### NOTES:

- 1. After a reset, the slowest clock (divided by 16) is selected as the system clock. To select faster clock speeds, load the appropriate values to CLKCON.3 and CLKCON.4.

- 2. If the oscillator frequency is higher than 12 MHz, this selection is invalid.

- These selection bits are required only for systems that have a main clock and a subsystem clock. S3C8075/P8075 use only the main oscillator clock circuit. For this reason, the setting '101B' is invalid.

| EMT — External I | Memo                                                                                                    | ry Tin  | ning reg    | ister         |              |            | FEH | Set 1 | , Bank 0 |

|------------------|---------------------------------------------------------------------------------------------------------|---------|-------------|---------------|--------------|------------|-----|-------|----------|

| Bit Identifier   | · ·                                                                                                     | 7       | .6          | .5            | .4           | .3         | .2  | .1    | .0       |

| RESET Value      | (                                                                                                       | 0       | -           | -             | -            | -          | -   | 0     | _        |

| Read/Write       | R                                                                                                       | /W      | _           | _             | _            | _          | _   | R/W   | _        |

| Addressing Mode  | Reg                                                                                                     | ister a | ddressing   | mode only     |              |            |     |       |          |

| .7               | External WAIT Input Function Enable Bit         0       Disable WAIT input function for external device |         |             |               |              |            |     |       |          |

|                  | 1                                                                                                       | Enab    | le WAIT i   | nput functio  | on for exter | nal device | •   |       |          |

| .6 – .2          | <u> </u>                                                                                                |         | or S3C807   |               |              |            |     |       |          |

| .1               | Stac                                                                                                    |         | a Selectio  | -             |              |            |     |       |          |

|                  | 0                                                                                                       |         |             | register file |              |            |     |       |          |

|                  | 1                                                                                                       | Selec   | ct external | data mem      | ory area     |            |     |       |          |

| .0               | Not                                                                                                     | used f  | or S3C807   | 75/P8075.     |              |            |     |       |          |

| FLAGS — Syste   | em Flag                                                   | ıs Register                                         |              |              | D5H          |              |             |            |  |  |  |  |

|-----------------|-----------------------------------------------------------|-----------------------------------------------------|--------------|--------------|--------------|--------------|-------------|------------|--|--|--|--|

| Bit Identifier  | .7                                                        | .6                                                  | .5           | .4           | .3           | .2           | .1          | .0         |  |  |  |  |

| RESET Value     | x                                                         | x                                                   | x            | х            | х            | х            | 0           | 0          |  |  |  |  |

| Read/Write      | R/                                                        | W R/W                                               | R/W          | R/W          | R/W          | R/W          | R/W         | R/W        |  |  |  |  |

| Addressing Mode | Regi                                                      | ster addressing                                     | mode only    |              |              |              |             |            |  |  |  |  |

| .7              | Carry Flag (C)                                            |                                                     |              |              |              |              |             |            |  |  |  |  |

|                 | 0 Operation does not generate a carry or borrow condition |                                                     |              |              |              |              |             |            |  |  |  |  |

|                 | 1                                                         | Operation gene                                      | erates a ca  | rry-out or b | orrow into   | high-order   | bit 7       |            |  |  |  |  |

| .6              | Zero                                                      | Flag (Z)                                            |              |              |              |              |             |            |  |  |  |  |

|                 | 0                                                         | Operation resu                                      | lt is a non- | zero value   |              |              |             |            |  |  |  |  |

|                 | 1                                                         |                                                     |              |              |              |              |             |            |  |  |  |  |

| .5              | Sign Flag (S)                                             |                                                     |              |              |              |              |             |            |  |  |  |  |

|                 | 0                                                         | Operation gene                                      | erates a po  | sitive numb  | per (MSB =   | "0")         |             |            |  |  |  |  |

|                 | 1                                                         | 1 Operation generates a negative number (MSB = "1") |              |              |              |              |             |            |  |  |  |  |

| .4              | Overflow Flag (V)                                         |                                                     |              |              |              |              |             |            |  |  |  |  |

|                 | 0                                                         | 0 Operation result is $\leq$ +127 or $\geq$ -128    |              |              |              |              |             |            |  |  |  |  |

|                 | 1                                                         | Operation resu                                      | lt is > +12  | 7 or < -1    | 28           |              |             |            |  |  |  |  |

| .3              | Decimal Adjust Flag (D)                                   |                                                     |              |              |              |              |             |            |  |  |  |  |

|                 | 0                                                         |                                                     |              |              |              |              |             |            |  |  |  |  |

|                 | 1                                                         | Subtraction op                                      | eration con  | npleted      |              |              |             |            |  |  |  |  |

| .2              | Half-Carry Flag (H)                                       |                                                     |              |              |              |              |             |            |  |  |  |  |

|                 | 0                                                         | No carry-out of                                     | bit 3 or no  | borrow inte  | o bit 3 by a | ddition or s | subtraction |            |  |  |  |  |

|                 | 1                                                         | Addition generation                                 | ated carry-  | out of bit 3 | or subtract  | ion genera   | ted borrow  | into bit 3 |  |  |  |  |

| .1              | Fast                                                      | Fast Interrupt Status Flag (FIS)                    |              |              |              |              |             |            |  |  |  |  |

|                 | 0                                                         | Cleared autom                                       |              | •            | rrupt return | (IRET)       |             |            |  |  |  |  |

|                 | 1                                                         | Automatically s                                     | set to logic | one during   | a fast inter | rupt servic  | e routine   |            |  |  |  |  |

| .0              | Bank Address Selection Flag (BA)                          |                                                     |              |              |              |              |             |            |  |  |  |  |

|                 | 0                                                         |                                                     |              |              | instruction  | SB0)         |             |            |  |  |  |  |

|                 | 1                                                         |                                                     |              |              |              |              |             |            |  |  |  |  |

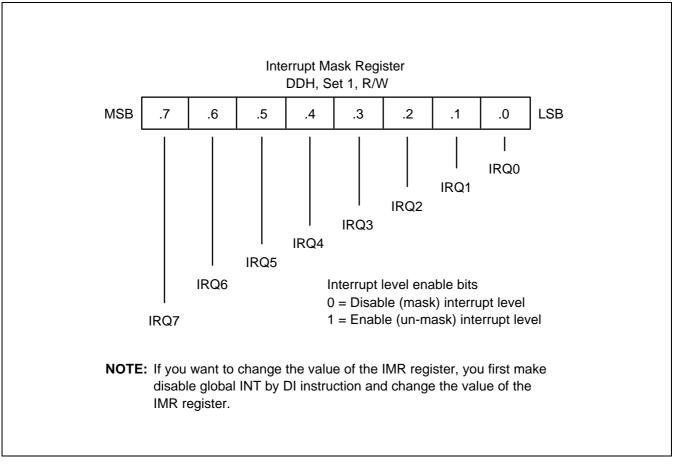

| IMR — Interrupt | Mask                                                                           | Register                 |         |           |              |             | DDH          |              | Set 1    |  |  |  |

|-----------------|--------------------------------------------------------------------------------|--------------------------|---------|-----------|--------------|-------------|--------------|--------------|----------|--|--|--|

| Bit Identifier  |                                                                                | 7.6                      | 5       | .5        | .4           | .3          | .2           | .1           | .0       |  |  |  |

| RESET Value     | _                                                                              |                          |         | х         | х            | х           | х            | х            | х        |  |  |  |

| Read/Write      | -                                                                              | - –                      |         | R/W       | R/W          | R/W         | R/W          | R/W          | R/W      |  |  |  |

| Addressing Mode | Regi                                                                           | ster addres              | sing m  | node only |              |             |              |              |          |  |  |  |

| .7              | Interrupt Level 7 (IRQ7) Enable Bit; P4.4–P4.7 External Interrupt (INT8–INT11) |                          |         |           |              |             |              |              |          |  |  |  |

|                 | 0                                                                              | Disable IR               | -       | -         |              |             |              | • •          | ,        |  |  |  |

|                 | 1                                                                              | Enable IRC               | Q7 inte | errupt    |              |             |              |              |          |  |  |  |

|                 | L1                                                                             |                          |         |           |              |             |              |              |          |  |  |  |

| .6              | Inter                                                                          | rupt Level               | •       |           | e Bit; P4.2  | or P4.3 E   | xternal Inte | errupt (INT  | 6, INT7) |  |  |  |

|                 | 0                                                                              | 0 Disable IRQ6 interrupt |         |           |              |             |              |              |          |  |  |  |

|                 | 1                                                                              | Enable IRC               | Q6 inte | errupt    |              |             |              |              |          |  |  |  |

| .5              | Interrupt Level 5 (IRQ5) Enable Bit; P4.1 External Interrupt (INT5)            |                          |         |           |              |             |              |              |          |  |  |  |

|                 | 0                                                                              | Disable IR               | Q5 int  | errupt    |              |             |              |              |          |  |  |  |

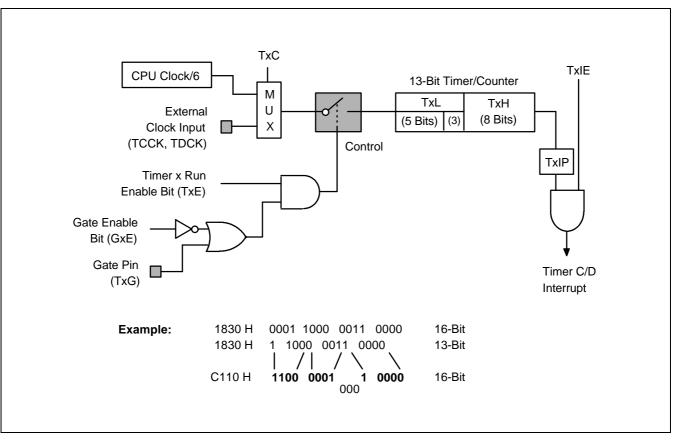

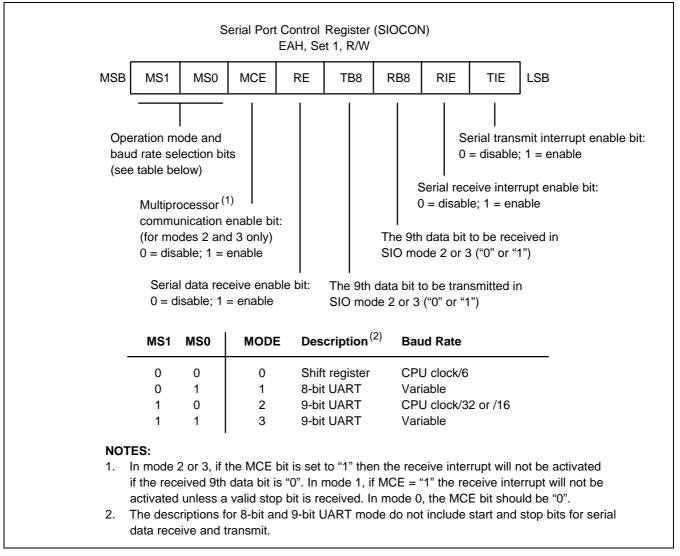

|                 | 1                                                                              | Enable IRC               | Q5 inte | errupt    |              |             |              |              |          |  |  |  |