## **BCM8021**

## 4-CHANNEL MULTIRATE 1.0-3.2-GBPS TRANSCEIVER WITH HIGH-SPEED REDUNDANCY

## **FEATURES**

- 4 independent transceivers supporting multiple data rates from 1.0 Gbps to 3.2 Gbps including 1.06 Gbps, 1.25 Gbps, 2.12 Gbps, 2.488 Gbps, 2.667 Gbps, 3.125 Gbps, and 3.1875 Gbps

- Multiconfigurable to support various operating modes

- 4 Independent 1.0 to 3.2-Gbps SerDes transceivers

- IEEE 802.3ae compliant XAUI to XGMII transceiver

- XAUI-to-XAUI retiming

- Low power dissipation

- Less than 300 mW per transceiver channel including I/O

- SONET/SDH-quality jitter performance

- Less than 3 picoseconds rms jitter generation

- Exceeds SONET jitter tolerance mask

- High performance programmable Rx equalization and Tx preemphasis

- Tx pre-emphasis for interoperability with CML SerDes

- Rx equalization for copper interconnects

- Enhanced test capability

- Full loopback and on-chip PRBS generator/checker

- IEEE (1149.1) JTAG

- Compact 21-mm × 21-mm BGA package

- No requirement for heat sink or airflow

## SUMMARY OF BENEFITS

- One device supports a variety of applications including Gigabit Ethernet, 1× and 2× Fibre Channel, OC-48 SONET (with/without FEC), Infiniband, 10-Gigabit Ethernet, 10-Gigabit Fibre Channel, or others.

- Advanced 0.13-μ CMOS process technology provides unparalleled performance while achieving the lowest possible power consumption.

- IEEE 802.3ae 10-Gigabit Ethernet physical coding sublayer (PCS) has a selectable 8B/10B encoding/decoding block onchip that can be configured to support the 10-Gbps Attachment Unit Interface (XAUI).

- Superior jitter characteristics enable the serializing/ deserializing (SerDes) of data signals transmitted through front panel or backplane networking equipment supporting both primary and protection circuits.

- Drive PMD devices or backplane directly with no external clean-up circuit required.

- Simplifies manufacturability with itegrated Built-in self-test (BIST), high-speed and low-speed loopbacks, and programmable PRBS generator/checker.

- Decreases complexity and reduces board space on multichannel linecard designs.

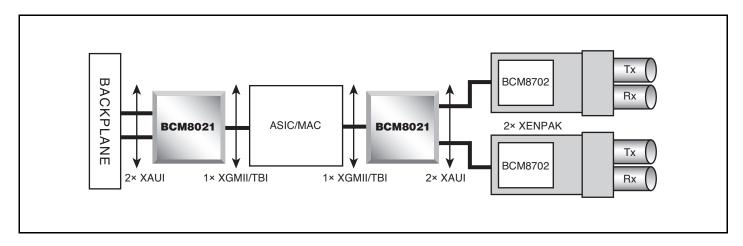

**Independent Quad SerDes Application Diagram**