## 5

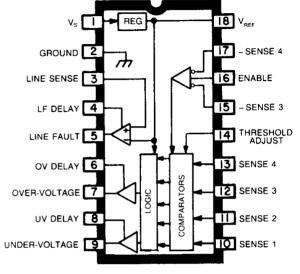

# ULN-8130A PRECISION SUPERVISORY SYSTEMS MONITOR Quad Voltage and Line Monitor

#### **FEATURES**

- 10 V to 35 V Operation

- · Low Standby Current

- Reference Trimmed to 1%

- Monitors 4 Separate DC Levels

- Separate Under-Voltage Comparators

- · Fixed Under-Voltage Threshold

- Line Sense Input

- · Pull-Up Clamped Outputs

- Programmable Output Delays

- V<sub>s</sub> Under-Voltage Lockout

Dwg. No. A-13,221

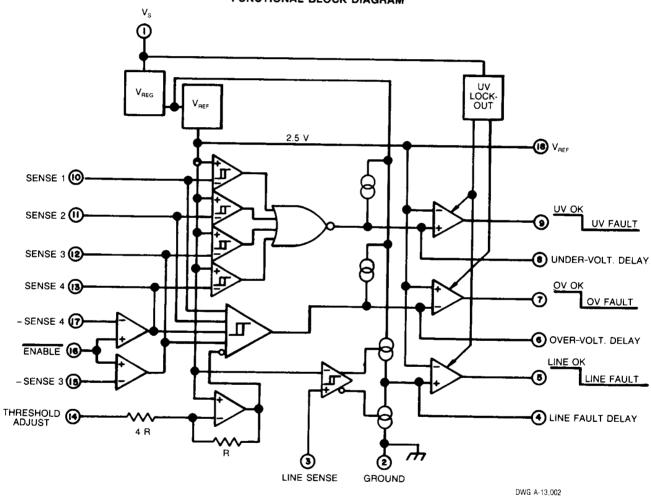

Capable of monitoring four dc power lines, the ULN-8130A is a power fault monitor for both under-voltage and over-voltage conditions. Two of the four inputs are designed to monitor positive voltages while the other two inputs can be used to monitor two positive or two negative voltages. An additional comparator is used to monitor the primary power line and will provide early warning of line voltage drop-out.

An under-voltage lockout, monitoring the ULN-8130A internal supply, prevents false outputs from occurring during low supply-voltage operation. The logic outputs can be used to operate LEDs or other low-voltage indicators.

The circuit configuration of the ULN-8130A allows easy programming of over-voltage thresholds which are referenced to a 1% trimmed 2.5 V bandgap reference. The UV FAULT (pin 9) is initiated by one or more of the four sense inputs fall-

ing below the UV trip point (the internal reference voltage). The OV FAULT (pin 7) is activated by one or more of the sense inputs rising above the externally set (pin 14) OV trip point. The LINE OK output (pin 5) will remain high as long as the LINE SENSE input (pin 3) is above the internal reference voltage. The LINE SENSE will accept a positive do voltage proportional to either the high-voltage master bus or the ac line.

Output delays can be introduced by adding capacitors from the appropriate DELAY pins to ground. The LINE FAULT DELAY capacitor value should be large enough to prevent false shutdowns due to short line transients.

The ULN-8130A is supplied in an 18-pin dual in-line plastic package with a copper lead frame that gives it enhanced power dissipation ratings. It is rated for continuous operation over the temperature range of  $0^{\circ}$ C to  $+70^{\circ}$ C.

### ABSOLUTE MAXIMUM RATINGS at $T_A = +25$ °C

| Supply Voltage, V <sub>cc</sub>       | 35 V            |

|---------------------------------------|-----------------|

| Power Dissipation, P <sub>D</sub>     | 2.3 W*          |

| Operating Temperature, T <sub>A</sub> | 0°C to +70°C    |

| Storage Temperature, $T_s$ –          | 65°C to + 150°C |

| Junction Temperature, T <sub>J</sub>  |                 |

<sup>\*</sup>Derate at the rate of 18.2 mW/°C above  $T_A = 25$ °C

#### **FUNCTIONAL BLOCK DIAGRAM**

## ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}C$ , $V_S = 15 \text{ V}$

| Characteristic                     |           |                                                         | Limits |             |       |

|------------------------------------|-----------|---------------------------------------------------------|--------|-------------|-------|

|                                    | Test Pin  | Test Conditions                                         | Min.   | Max.        | Units |

| Functional V <sub>s</sub> Range    | 1         |                                                         | 10     | 35          | V     |

| Quiescent Current                  | 1         | $V_s = 35 \text{ V}, V_{16} = V_{18}, \text{ No Fault}$ |        | 15          | mA    |

| REFERENCE VOLTAGE SECTION          |           |                                                         |        |             |       |

| Reference Voltage                  | 18        | No Load, $T_A = +25^{\circ}C$                           | 2.47   | 2.53        | V     |

|                                    |           | No Load, Change Over Temp.                              | _      | 25          | mV    |

| Load Regulation                    | 18        | $I_{REF} = 0 \text{ to } 10 \text{ mA}$                 |        | 20          | mV    |

| Line Regulation                    | 18        | $V_s = 10 \text{ to } 35 \text{ V}$                     |        | 10          | mV    |

| Ripple Rejection                   | 18        | f = 120 Hz                                              | 60     |             | dB    |

| Short-Circuit Current Protection   | 18        |                                                         |        | 40          | mA    |

| COMPARATOR SECTION                 |           |                                                         |        |             |       |

| Under-Voltage Trip Points          | 10-13*    | $T_A = +25^{\circ}C$                                    | 2.47   | 2.53        | ٧     |

|                                    |           | Over Temperature                                        | 2.46   | 2.54        | ٧     |

| Under-Voltage Trip Hysteresis      | 10-13*    | Over Temperature                                        | 10     | 25          | m۷    |

| Over-Voltage Trip Points           | 10-13*    | $V_{14} = 0$                                            | 3.08   | 3.17        | ٧     |

| Over-Voltage Trip Hysteresis       | 14        | $V_{14} = 0$ to 2.5 V, Over Temp.                       | 10     | 25          | m۷    |

| Line Monitor Trip Threshold        | 3         |                                                         | 2.40   | 2.54        | ٧     |

| Under-Voltage Lockout Enable       | 1         | V <sub>s</sub> Decreasing                               | 8.5    | <del></del> | ٧     |

| Under-Voltage Lockout Disable      | 1         | V <sub>s</sub> Increasing                               |        | 10.5        | ٧     |

| Input Bias Current                 | 3, 10, 11 | $V_{IN} = 2.0 \text{ V}$                                | _      | -6.0        | μΑ    |

|                                    |           | $V_{IN} = 3.0 \text{ V}$                                | _      | 6.0         | μΑ    |

|                                    | 14        | $V_{iN} = 0$                                            |        | <b>–</b> 50 | μΑ    |

|                                    | 15, 17    | $V_{1N} = -2.0 \text{ V}, V_{16} = 0 \text{ V}$         |        | - 2.0       | μΑ    |

| OUTPUT DRIVERS                     | <u> </u>  |                                                         |        |             |       |

| Output Saturation Voltage          | 5, 9      | $I_{SINK} = 5.0 \text{ mA}$                             |        | 0.5         | ٧     |

|                                    | 7         | $I_{SINK} = 10 \text{ mA}$                              |        | 0.5         | ٧     |

|                                    | 5, 7, 9   | $I_{SOURCE} = 500 \mu\text{A}$                          | 4.0    | 5.25        | ٧     |

| Output Leakage Current             | 5, 7, 9   | $V_{out} = 35 V$                                        |        | 50          | μΑ    |

| Line Fault Delay Current Source    | 4         | $V_4 = 2.0 \text{ V}$                                   | 160    | 350         | μΑ    |

| Line Fault Delay Current Sink      | 4         | $V_4 = 2.0 V$                                           | 3.2    | 7.0         | mA    |

| Over-Voltage Delay Current Source  | 6         | $V_6 = 2.0 \text{ V}$                                   | 160    | 300         | μΑ    |

| Under-Voltage Delay Current Source | 8         | $V_8 = 2.0 \text{ V}$                                   | 35     | 75          | μΑ    |

<sup>\*</sup>All inputs connected to 2.75 V except input being tested.

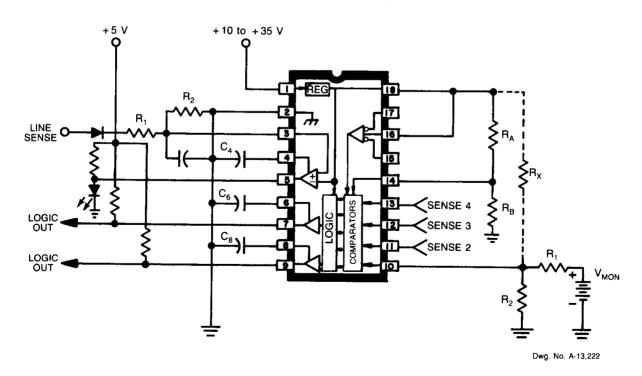

#### **APPLICATIONS**

The basic voltage monitors are based on a 2.5 V precision bandgap reference. External resistive dividers are used to present a nominal 2.5 V level to each under-voltage comparator at the minimum allowable under-voltage condition. The over-voltage reference is set up by another resistive divider at pin 14 determined by the tightest over-voltage tolerance requirement.

#### **BASIC FORMULAS:**

(1) An under-voltage fault is detected, (pin 9 goes low), when the positive input voltage being monitored is less than:

$$V_{MON(LO)} = 2.5 (R_1 + R_2)/R_2$$

(2) The internal over-voltage threshold is defined as:

$$V_{OVT} = 2.5 \left[ 1 + \frac{R_A}{4(R_A + R_B)} \right]$$

where  $R_A$  //  $R_B$  << 100 k $\Omega$

(3) An over-voltage fault is detected when the positive input voltage being monitored exceeds:

$$V_{MON(HI)} = V_{OVT} (R_1 + R_2)/R_2$$

(4) Individual over-voltage thresholds can be in-

creased by the addition of Rx with

$$R_{X} = R_{1} \frac{V_{OVT} - 2.5}{V_{MON(HI)} - V_{OVT} \left(\frac{R_{1} + R_{2}}{R_{2}}\right)}$$

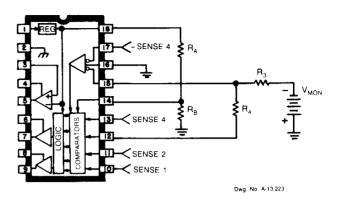

(5) To monitor negative supplies at SENSE 3 and SENSE 4, pin 16 is connected to ground. In this condition, an under-voltage fault indication will occur when either negative supply being monitored falls below:

$$V_{MON(LO)} = 2.5 R_3/R_4$$

Note that for monitor purposes, under-voltage means the negative supply is actually going net positive, or toward ground.

(6) For negative supplies, an over-voltage fault indication will occur when:

$$V_{MON(HI)} = V_{OVT} R_3/R_4$$

(7) Fault delay capacitor values are determined by:

$$C_4 \text{ or } C_6 = \frac{200 \times 10^{-6} \times t}{2.5}$$

$$C_9 = \frac{55 \times 10^{-6} \times t}{2.5}$$

where t is the output delay in seconds.

## LINE SENSE AND POSITIVE SUPPLY MONITORING (SENSE 1, 2, 3, and 4)

#### **UNUSED INPUTS**

Unused positive sense channel inputs (pins 3, 10-13) must not be left unconnected. Neither can they be tied high (over-voltage fault indication), tied low (under-voltage fault indication), or tied to the internal reference (susceptible to noise and voltage offsets). Unused sense channel inputs should be connected to any operating sense channel input. For example, if channels 1, 2, and 4 are being used, the unused channel 3 sense input (pin 12) should be connected to the sense 2 or sense 4 input.

Unused negative sense channel inputs (pins 15 and 17) can be left open-circuited *provided* the associated enable input (pin 16) is tied high and the associated positive sense channel inputs (pins 12 and 13) are utilized to monitor positive supplies or are connected as described above.

#### **DESIGN EXAMPLE**

As an example, consider the following set of monitoring conditions:

$$V_1 = +5 V + 10\%, -5\%$$

$V_2 = +12 \text{ V} \pm 10\%$

$V_3 = +15 V \pm 5\%$

$V_4 = +24 \text{ V } \pm 10\%$

The required input dividers are calculated per (1) to yield the resistor divider ratios,  $R_2$  ( $R_1$  +  $R_2$ ), of: 0.5263, 0.2315, 0.1754 (Note 1), and 0.1157 respectively. The over-voltage threshold,  $V_{\text{OVT}}$ , would be dictated by the tightest tolerance supply which gives the lowest  $V_{\text{OVT}}$  from (3). Therefore,  $V_{\text{MON(HI)}}$  = 15 x 1.05 = 15.75 volts and  $V_{\text{OVT}}$  = 15.75 x 0.1754 = 2.763 volts¹. This is the voltage appearing at the SENSE terminal and is equal to the over-voltage threshold to be

#### NEGATIVE SENSE MONITORING SENSE 3 and 4 Only

set via the resistor ratio at pin 14. From (2),  $R_A/(R_A + R_B)$  is calculated to be 0.4096. It is good practice to keep the equivalent external impedances as low as possible, in order to minimize bias current and offset errors. For the purpose of this example, all resistor dividers will be taken to have an equivalent impedance of 1000 ohms. This being the case, the final values are:  $R_A = 1.7 \ k\Omega$  and  $R_B = 2.44 \ k\Omega$ .

In order to provide accurate over-voltage sensing for the  $V_1$ ,  $V_2$ , and  $V_4$  supplies, resistors are connected from the respective input sense nodes and returned to the 2.5 V reference. Calculation is made by first picking values for the input dividers and then calculating the required value of  $R_{\rm x}$  from (4). Again, assuming 1 k $\Omega$  equivalent divider impedances and making the calculations, a summary of results is given below.

| MONITORED SUPPLY  | V <sub>MON(HI)</sub> | $V_{MON(EO)}$ | $R_1$                   | $R_2$                   | $R_{x}$      |

|-------------------|----------------------|---------------|-------------------------|-------------------------|--------------|

| + 5 V (+10%, -5%) | 5.5 V                | 4.75 V        | 1.90 kΩ                 | 2.11 kΩ                 | 2.0 kΩ       |

| + 12 V ( ± 10%)   | 13.2 V               | 10.8 V        | $4.32~\mathrm{k}\Omega$ | $1.30~\mathrm{k}\Omega$ | $900 \Omega$ |

| + 15 V (± 5%)     | 15.75 V              | 14.25 V       | $5.70~\mathrm{k}\Omega$ | $1.21~\mathrm{k}\Omega$ | œ            |

| + 24 V ( ± 10%)   | 26.4 V               | 21.6 V        | $8.64~\mathrm{k}\Omega$ | $1.13~\mathrm{k}\Omega$ | $900 \Omega$ |

1. Note that the number 0.1754 is rounded off. Due to required accuracies in the external dividers, round off numbers only after final resistor values are calculated. For the same reason, use stable high-accuracy metal film resistors. Many applications may benefit from combining the ULN-8130A and functionally trimmed Sprague resistor-capacitor networks.