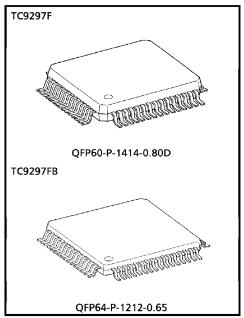

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9297F, TC9297FB

# LCD DRIVER WITH ON-CHIP KEY INPUT

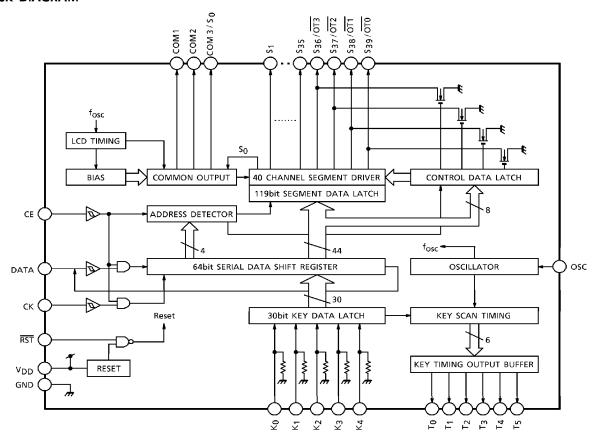

TC9297F/FB are an LCD driver IC with on-chip key input, which is serial data controlled.

#### **FEATURES**

- Supports switching between 1/2 and 1/3 duty, and between 1/2 and 1/3 bias.

- Displays up to 80 segments in 1/2-duty mode and up to 117 segments in 1/3-duty mode.

- All display segments can be either off or on. Outputs of pins S<sub>36</sub>-S<sub>39</sub> can be switched between segment output and LED driver output.

- Supports key input from up to 30 keys.

- 3-wire configuration for controller connection.

Weight

QFP60-P-1414-0.80D : 1.10g (Typ.) QFP64-P-1212-0.65 : 0.45g (Typ.)

The products described in this document are subject to foreign exchange and foreign trade control laws. The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

1997-06-06 1/17

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

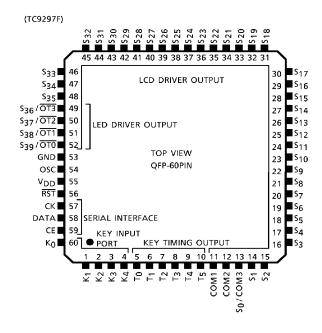

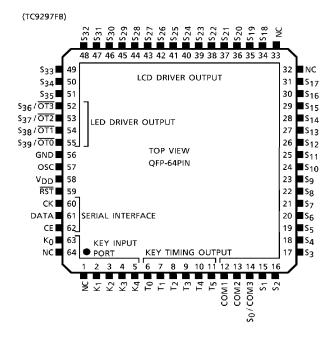

#### PIN CONNECTION

1997-06-06 2/17

## **BLOCK DIAGRAM**

PIN FUNCTIONS (Data in parenthesizes are for TC9297FB)

| PIN No.                        | SYMBOL                                                  | PIN NAME                                        | FUNCTION AND OPERATION                                                                                                                                                                                                                           | REMARKS                                   |  |  |

|--------------------------------|---------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|

| 55 (58)                        | v <sub>DD</sub>                                         | Power supply input pin                          | Power supply input pin. Normally supplied with VRST-5.5V. Power-on reset function resets system when powered up and                                                                                                                              | _                                         |  |  |

| 53 (56)                        | GND                                                     | Ground pin                                      | when V <sub>DD</sub> drops below 3V (Typ.).                                                                                                                                                                                                      |                                           |  |  |

| 60 (63)<br>1 (2)<br>5<br>4 (5) | K <sub>0</sub><br>K <sub>1</sub><br>s<br>K <sub>4</sub> | Key-scan input pin                              | Key-scan input pins. Data from up to $6 \times 5 = 30$ keys can be input by a key matrix with key scan output pins $T_0$ - $T_5$ . When high is input to pins, key scan begins. These are I/O pins with built-in pull-down resistors.            | V <sub>DD</sub>                           |  |  |

| 5 (6)                          | T <sub>0</sub>                                          | Key scan timing<br>output pin                   | Key scan timing output pins. Due to key matrix configured using load resistor RON on the N-channel, no diodes are required. Output is normally high. When high is input to key scan input pins K <sub>0</sub> -K <sub>4</sub> , key scan begins. | Ron Ron                                   |  |  |

| 11 (12)<br>12 (13)             | COM1<br>COM2                                            | LCD common output<br>pin                        | LCD segment output/common output pins. When set to 1/2-duty, can display up to 80 segments in a matrix of pins COM1, 2 and S <sub>0</sub> -S <sub>39</sub> ; when set to 1/3-                                                                    | ¶V <sub>DD</sub><br>∓⊢                    |  |  |

| 13 (14)                        | S <sub>0</sub> /<br>COM3                                | LCD segment output<br>/common output<br>pin     | duty, up to 117 segments in a matrix of COM1-3 and $S_1$ - $S_3$ 9. In 1/3-duty mode, pin $S_0$ is used as COM3.                                                                                                                                 |                                           |  |  |

| 14(15~31)<br>(48(34~51)        | S <sub>1</sub><br>S <sub>35</sub>                       | LCD segment output<br>pin                       | LCD segment output/LED driver output pins. When set to 1/2-duty, can display up to 80 segments in a matrix of pins COM1, 2 and S <sub>0</sub> -S <sub>39</sub> ; when set to 1/3-duty, up to 117 segments in a matrix of                         | Y V D D T T T T T T T T T T T T T T T T T |  |  |

| 49 (52)<br>5<br>52 (55)        | S <sub>36</sub> /<br>OT3                                | LCD segment output<br>/LED driver output<br>pin | COM1-3 and S <sub>1</sub> -S <sub>39</sub> . Pins S <sub>36</sub> -S <sub>39</sub> also serve as LED driver pins. The LED driver output becomes N-ch open driver output, and large-current drive allows direct LED display.                      | T V D D                                   |  |  |

| PIN No.      | SYMBOL | PIN NAME                         | FUNCTION AND OPERATION                                                                                                                                                                                                                                          | REMARKS                       |

|--------------|--------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 54 (57)      | osc    | Crystal oscillator<br>output pin | Oscillates when connected to an external crystal.  The oscillation frequency is expressed by the frequency expression : $f_{OSC} \approx 1.5 / (C.R) \ [Hz]$ For instance, when $C = 0.01 \mu F$ , $R = 30 k\Omega$ : $f_{OSC} \approx 5 kHz$                   | V <sub>DD</sub>               |

| 56 (59)      | RST    | System reset input pin           | System reset input pin. While RST input is low, the oscillator stops, all internal data are reset, and the LCD output and key scan output pins are fixed to high.  There is a built-in power-on reset circuit, so this pin should normally be connected to VDD. | VDD VDD                       |

| 57 (60)      | ск     | Clock input pin                  | Serial interface pins that send to and receive from the controller display data                                                                                                                                                                                 | 0                             |

| 58 (61) DATA |        | Data I/O pin                     | and key input data, and the data to control these.  Data send/receive is not performed while pin CE is low, but when CE goes high, begins at the DATA pins in sync with the clock input of the CK input pin.                                                    |                               |

| 59 (62)      | CE     | Chip enable input<br>pin         | All these pins have built-in Schmitt input circuits.                                                                                                                                                                                                            | $\bigcirc - \triangleright -$ |

| CONTENT OF ADDRESS DAT | TENT | Ö        | ADE  | )RES | S DATA        |                |                                     |          |                |                      |                      |                |        |                     |                        |         |

|------------------------|------|----------|------|------|---------------|----------------|-------------------------------------|----------|----------------|----------------------|----------------------|----------------|--------|---------------------|------------------------|---------|

| DUTY                   | A3   | A2       | A1 / | A0   | ADDRESS (HEX) | 0 <sub>Q</sub> | ١a                                  | ζQ       | E <sub>Q</sub> | D4                   | D5                   | 9 <sub>Q</sub> | LQ     | D8~D32              | D8~D32 D33~D39 D40~D59 | D40~D59 |

|                        |      |          |      |      |               |                |                                     |          |                | 50~519 Display Data  | splay Data           |                |        |                     |                        |         |

|                        |      |          |      | ,    |               | S              | 20                                  | ۱s       | 1              | S2                   | 2                    | S3             |        | ~Þs                 | 54~519                 |         |

|                        |      | *        | k    | _    | 1, 5, 5, 7    | COM2           | COM1                                | COM2     | COM1           | COM2                 | COM1                 | COM2           | COM1   | motary 1 CMCD       | Curtom                 | 1       |

| 1 / 2                  |      |          |      |      |               | System         | System                              | System   | System         | System               | System               | System         | System | COIVIE,             | ) ystelli              |         |

| 7/-                    |      |          |      |      |               |                |                                     |          | S              | 520~539 Display Data | isplay Data          | _              |        |                     |                        |         |

|                        | -    | +        |      |      |               | \$20           | 0.0                                 | 521      |                | \$22                 | 2                    | 523            | 3      | \$24~539            | -539                   |         |

|                        | >    | *        | _    | k    | 7' 2' 0' 1    | COM2           | COM1                                | COM2     | COM1           | COM2                 | COM1                 | COM2           | COM1   | , (1/10)            | Cuctom                 | I       |

|                        |      |          |      |      |               | System         | System                              | System   | System         | System               | System               | System         | System | COIVIZ, I SYSTEM    | ) system               |         |

|                        |      |          |      |      |               |                |                                     |          |                | S-0S                 | So~S19 Display Data  | Data           |        |                     |                        |         |

|                        |      |          |      | ,    | Γ<br>(        |                | ος                                  |          |                | 51                   |                      |                |        | 52~519              |                        |         |

|                        | >    | *        | *    |      | 1, 5, 5, 7    |                |                                     |          | COM3           | COM2                 | COM1                 |                | (      |                     |                        |         |

|                        |      |          |      |      |               |                | I                                   |          | System         | System               | System               |                | 3      | COIMS, 2, 1 system  | mem                    |         |

| 2                      |      |          |      |      |               |                |                                     |          |                | \$20~5               | 520~539 Display Data | Data           |        |                     |                        |         |

|                        |      |          | *    | -    | ר א כ ר       |                | \$20                                |          |                | 521                  |                      | -              |        | 522~539             |                        |         |

|                        | >    | k        |      | k    | 7' 0' '7      | COM3           | COM2                                | COM1     | COM3           | COM2                 | COM1                 |                | 1      |                     |                        |         |

|                        |      |          |      | -    |               | System         | System                              | System   | System         | System               | System               |                | 5      | COIMIS, 2, 1 System | rem                    |         |

|                        | ,    |          |      |      | c             | SET SEG        | SET SEGMENT OUTPUT/LED DRIVER       | TPUT/LED | DRIVER         | LCD CONTROL          | NTROL                | "0"            | ,0,,   |                     |                        |         |

|                        | -    |          | >    | >    | 0             | S39/OT0        | \$39/OT0 \$38/OT1 \$37/OT2 \$36/OT3 | \$37/OT2 | S36/OT3        | Duty                 | Bias                 | >              | >      |                     | l                      |         |

|                        | •    | -        |      | -    | c             | 7              | LED DRIVER CONTROL                  | CONTROL  |                | DISPI                | DISPLAY CONTROL      | 30F            | "U"    |                     |                        |         |

| *                      |      |          | >    | _    | n             | OT0            | 07.1                                | 012      | OT3            | OP                   | BL                   | LT             | 5      |                     | l                      |         |

|                        |      | -        | ,    | ,    | 2             |                |                                     |          | KEY D          | KEY DATA (OUTPUT)    | PUT)                 |                |        |                     | "                      | 11      |

|                        | _    | <u> </u> | _    | >    | ₹             | Kon            | KWK                                 | K01      | K02            | K03                  | K04                  | K05            | K06    | K07~K30             | •                      |         |

: Don't care - : Invalid data

TC9297F/FB - 6

#### **OPERATING INSTRUCTIONS**

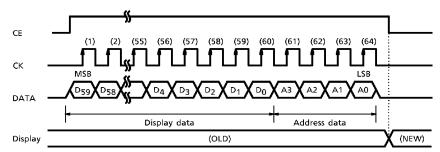

- 1. Input format for display data and mode data

- Display data input timing is as shown below (when set to 1/3-duty):

For rise and fall times, see Electrical Characteristics

- The last 4 bits of data are the address data.

- For segment data and control data corresponding to the segment data output being used, set all bits used.

- Segment data corresponding to the unused segment outputs of the MSB may be omitted.

- Segment data may be set to either address 1H or 2H.

- Do not set segment data until the data at address 8H have been set. Otherwise, it may be impossible to set segment data correctly.

- Data input is synchronized with the clock rising edge.

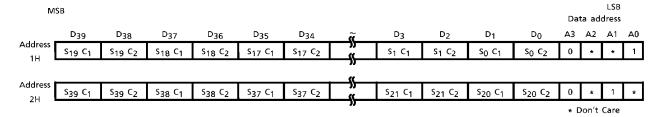

- (1) 1/2-duty (80-segment) data format

The format for display data in 1/2-duty mode is as shown below:

- In this case, segment data controlled by COM3 are invalid, and data need not be set.

- Pins S<sub>0</sub>-S<sub>39</sub> can be used for segment output.

1997-06-06 7/17

(2) 1/3-duty (80-segment) data format

The format for display data in 1/3-duty mode is as shown below:

- In this case, the pin is used as COM3, but set data as for the S<sub>0</sub> pin. (Note that the set data are non-functional.)

- Pins S<sub>1</sub>-S<sub>39</sub> can be used for segment output.

These data bits control on/off switching of the display corresponding to the common outputs. A waveform corresponding to display on/off is output to the segment output corresponding to common/segment data. Set "1" for display on and "0" for off. To set data for pins S<sub>0</sub>-S<sub>19</sub> and S<sub>20</sub>-S<sub>39</sub> independently, specify the address to 1H and 2H respectively.

When data for pins S<sub>0</sub>-S<sub>19</sub> and S<sub>20</sub>-S<sub>39</sub> overlap, identical data can be transferred simultaneously with a single serial data transfer by specifying 3H as the address. When there are unused segments of the MSB, the data setting for unused segments of the MSB omit and it can possible to set from used segment data of the MSB.

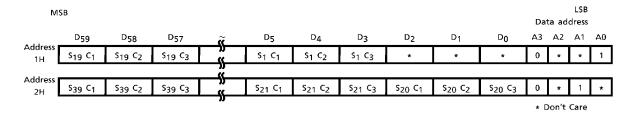

(Example) When up to 24 segments are used in 1/3-duty mode.

1997-06-06 8/17

# (3) Duty and bias bits

| _          | D <sub>7</sub> D <sub>6</sub> |   | D <sub>5</sub> D <sub>4</sub> |      | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | А3 | A2 | Α1 | A0 |

|------------|-------------------------------|---|-------------------------------|------|----------------|----------------|----------------|----------------|----|----|----|----|

| Address 8H | 0                             | 0 | Bias                          | Duty |                |                |                |                | 1  | 0  | 0  | 0  |

| •          |                               |   |                               |      |                |                |                |                |    |    |    |    |

|            |                               |   | BIAS                          | DUTY | BIAS           | DUTY           |                |                |    |    |    |    |

|            |                               | * | 0                             | 0    | 1/2            | 1/2            |                |                |    |    |    |    |

|            |                               |   | 0                             | 1    | 1/2            | 1/3            |                |                |    |    |    |    |

|            |                               |   | 1                             | 0    | 1/3            | 1/2            |                |                |    |    |    |    |

|            |                               |   | 1                             | 1    | 1/3            | 1/3            |                |                |    |    |    | 0  |

\* (Note) These data are reset to "0" at reset.

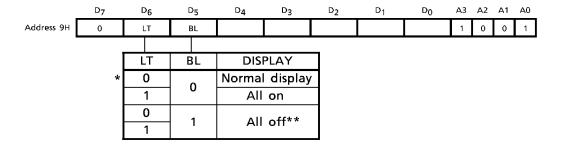

# (4) BL and LT bits

Even when the display is set to all on or all off, the display data prior to setting is retained and no resetting of display data is required.

It is also possible to set new data while all on or all off.

- \* (Note) These data are reset to "0" at reset.

- \*\* (Note) When both BL and LT are "1", BL takes priority.

1997-06-06 9/17

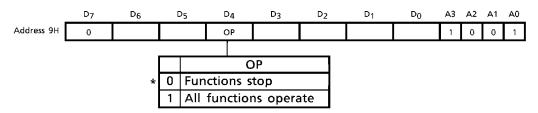

#### (5) OP bit

The OP bit controls the operating and stopping of the LCD driver, key scan and other functions. When it is reset to "0", all operations stop, the LCD driver output and key scan output pins are fixed to high, and the oscillator stops.

The data of control bits prior to setting is retained, and new data can be set. When this pin is set to "1", the oscillator, LCD driver and key scan operate.

At reset, this bit is reset to "0". Initialize control data and display data in this state.

- \* (Note) These data are reset to "0" at reset.

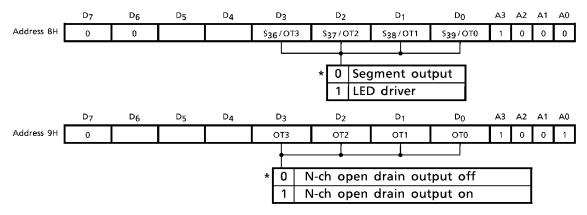

- (6) Segment output/LED driver switching bits and LED driver control bits

The segment output/LED driver switching bits switch between segment output and the LED driver output. Resetting these bits to "0" selects segment output; setting to "1" selects LED driver output. When set to segment output, display data are output and the LCD display is turned on and off; when set to LED driver output, output is turned on and off by the LED driver control bit.

The LED driver is of N-ch open-drain structure. Setting the LED driver control bit to "0" turns off N-ch open output; setting to "1" turns off N-ch open output.

When set to segment output, the corresponding LED driver control data are invalid; conversely, when set to LED driver, the corresponding segment output display data are invalid.

When S<sub>36</sub>-S<sub>39</sub> are used for LED driver output, data must not be set to address 9H until the segment/LED switching bit of the corresponding address 8H has been set to "1".

\* (Note) These data are reset to "0" at reset.

1997-06-06 10/17

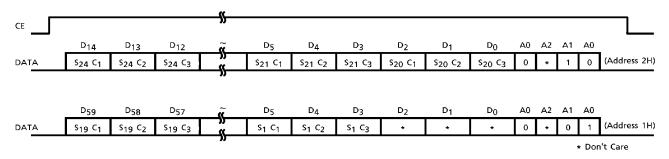

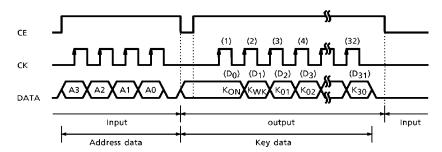

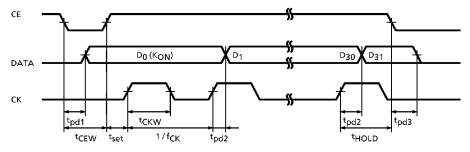

## 2. Key data output format

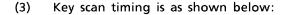

(1) Key data output timing is as shown below:

For rise and fall times, see Electrical Characteristics.

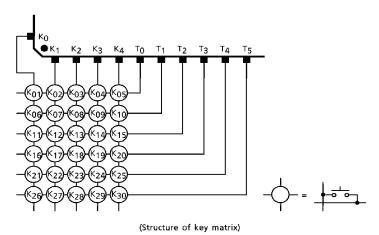

# (2) Structure of key matrix

- At key input, K<sub>ON</sub> = "1"; when multiple strikes occur, K<sub>WK</sub> = "1".

- After address input, the data pin is set to output at CE = "L", and key requests (K<sub>ON</sub> = "1") can be accepted.

- Setting the CE pin from high to low returns the data pin to input; key data detection can be suspended.

(Note) When fosc is 5kHz.

When high is input to the key input pin, key scanning begins within not more than one cycle (4.8ms when  $f_{OSC}$  is 5kHz), and the key data corresponding to the key timing is input. After one more cycle of key scanning,  $K_{ON}$  is set to "1" and key data are entered and upgraded every cycle. When the key is released, key scanning stops within not more than two cycles (9.6ms when  $f_{OSC}$  is 5kHz), and all key data are reset to "0".

To access key data, pin CE may be held low after input of address data.

Thus, key data must be accessed during key scanning.

The result is standby until key input occurs. In this state, the  $K_{\mbox{ON}}$  bit is output to the data pin as-is, so that it is "1" when there is key input and "0" when there is not. If key data are continuously accessed based on the state of  $K_{\mbox{ON}}$ , key data can be effectively fetched.

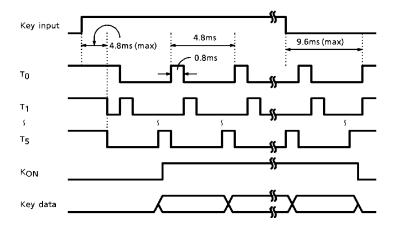

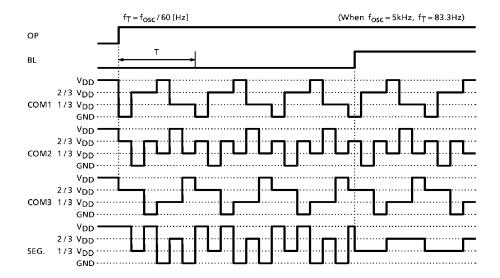

- 3. The output waveforms of the LCD driver are as shown below.

- 1/2 duty, 1/2 bias (COM1 system off, COM2 system on)

• 1/3 duty, 1/3 bias (COM1 system on, COM2 system off, COM3 system on)

1997-06-06 13/17

# **MAXIMUM RATINGS** (Ta = $25^{\circ}$ C)

| CHARACTERISTIC        | SYMBOL           | RATING                   | UNIT |

|-----------------------|------------------|--------------------------|------|

| Supply Voltage        | $V_{DD}$         | -0.3~7.0                 | V    |

| Input Voltage         | $v_{IN}$         | $-0.3 \sim V_{DD} + 0.3$ | ٧    |

| Power Dissipation     | PD               | 300                      | mW   |

| Operating Temperature | T <sub>opr</sub> | - 40~85                  | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>-65∼150</b>           | °C   |

# **ELECTRICAL CHARACTERISTICS** (Unless otherwise specified, $V_{DD} = 4.5 \sim 5.5 \text{V}$ , $T_0 = -40 \sim 85 \text{°C}$ )

| CHARAC                 | TERISTIC    | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                                 | MIN.                       | TYP.               | MAX.                                   | UNIT     |

|------------------------|-------------|------------------|----------------------|------------------------------------------------------------------------------------------------|----------------------------|--------------------|----------------------------------------|----------|

| Operating S<br>Voltage | Supply      | V <sub>DD</sub>  | _                    | _                                                                                              | V <sub>RST</sub>           | 5.0                | 5.5                                    | V        |

| Power On R<br>Voltage  | Reset       | V <sub>RST</sub> | _                    | _                                                                                              | 2.5                        | 3.0                | 3.5                                    | <b>v</b> |

| Operating S<br>Current | Supply      | l <sub>DD1</sub> | _                    | $V_{DD} = 5V$ , $f_{OSC} = 5kHz$ ,<br>No load                                                  | _                          | 0.4                | 1.0                                    | mA       |

| Stand-by Cu            | ırrent      | I <sub>DD2</sub> | _                    | OP = "0", V <sub>DD</sub> = 5V                                                                 | _                          | 120                | 250                                    | $\mu$ A  |

| Input                  | "H" Level   | VIH              | _                    | K <sub>0</sub> ∼K <sub>3</sub> , CE, DATA, CK, RST                                             | V <sub>DD</sub><br>× 0.8   | ~                  | V <sub>DD</sub>                        | V        |

| Voltage                | "L" Level   | V <sub>IL</sub>  |                      | $K_0 \sim K_3$ , CE, DATA, CK, $\overline{RST}$                                                | 0                          | <b>\</b>           | ∨ <sub>DD</sub><br>×0.2                | <        |

| SCHMITT Vo             | oltage      | V <sub>SCH</sub> | _                    | V <sub>DD</sub> = 5V, CE, DATA, CK                                                             | _                          | 1.0                | _                                      | >        |

| Input Leak             | "H" Level   | lіН              | _                    | $V_{IN} = V_{DD}$ , CE, DATA, CK, $\overline{RST}$                                             | _                          | }                  | ± 1.0                                  | μΑ       |

| Current                | "L" Level   | Ι <sub>Ι</sub> L | _                    | V <sub>IN</sub> = 0V, CE, DATA, CK, RST                                                        | _                          | ~                  | ± 1.0                                  | $\mu$ A  |

|                        | 1/2 Level   | V <sub>1/2</sub> | _                    | $V_{DD} = 5V$<br>COM1, COM2                                                                    | 1/2V <sub>DD</sub><br>-0.5 | 1/2V <sub>DD</sub> | 1/2V <sub>DD</sub><br>+ 0.5            | >        |

| Output<br>Voltage      | 1/3 Level   | V <sub>1/3</sub> | _                    | $V_{DD} = 5V$<br>COM1~COM3, $S_0 \sim S_{39}$                                                  | 1/3V <sub>DD</sub><br>-0.5 | 1/3V <sub>DD</sub> | 1/3V <sub>DD</sub><br>+0.5             | >        |

|                        | 2/3 Level   | V <sub>2/3</sub> | _                    | $V_{DD} = 5V$<br>COM1~COM3, $S_0 \sim S_{39}$                                                  | 2/3V <sub>DD</sub><br>-0.5 | 2/3V <sub>DD</sub> | 5.5  1.0  1.0  1.0  1.0  1.0  1.0  1.0 | <        |

| 4                      | "H" Level   | <sup>1</sup> ОН1 | _                    | $V_{DD} = 5V$ , $V_{OH} = 4.5V$ , $T_0 \sim T_5$<br>COM1 $\sim$ COM3, $S_0 \sim S_{39}$ , DATA | - 0.5                      | - 3.0              | _                                      | mA       |

| Output<br>Current      | "L" Level 1 | lOL1             | _                    | $V_{DD} = 5V$ , $V_{OL} = 0.5V$<br>COM1~ COM3, $S_0 \sim S_{39}$ , DATA                        | 0.5                        | 3.0                | _                                      | mA       |

|                        | "L" Level 2 | lOL2             | _                    | $V_{DD} = 5V$ , $V_{OL} = 1.0V$ , $OT0 \sim OT3$                                               | 10                         | 20                 | _                                      | mA       |

| OFF-LEAK C             | urrent      | lLO              | _                    | OT0~OT3                                                                                        | _                          | ~                  | ± 1.0                                  | $\mu$ A  |

| N-ch Outpu<br>Resistor |             | RON              |                      | $Ta = 25^{\circ}C, T_0 \sim T_5$                                                               | 75                         | 150                | 300                                    | kΩ       |

| Pull-Down F            | Resistor    | R <sub>IN</sub>  | _                    | Ta = 25°C, $K_0 \sim K3$                                                                       |                            |                    |                                        |          |

1997-06-06 14/17

| CHARACTERISTIC                     | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                 | MIN. | TYP. | MAX. | UNIT |

|------------------------------------|------------------|----------------------|--------------------------------|------|------|------|------|

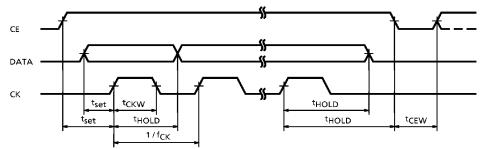

| Oscillation Frequency              | fosc             | _                    | <del>_</del>                   | _    | 5    | 20   | kHz  |

| Operating Clock<br>Frequency Range | fск              |                      |                                | _    | ~    | 2.0  | MHz  |

| Clock Pulse Width                  | <sup>t</sup> CKW |                      | Bofor to timing chart of holow | 250  | ~    | _    |      |

| Data Set Time                      | t <sub>set</sub> | _                    | Refer to timing chart as below | 250  | ~    | _    | 200  |

| Data Hold Time                     | tHOLD            |                      |                                | 250  | ~    | _    | ns   |

| CE Pulse Width                     | <sup>t</sup> CEW |                      |                                | 250  | {    | _    |      |

# CE, CK, DATA-IN TIMING

| CHARACTERISTIC                     | SYMBOL            | TEST<br>CIR-<br>CUIT | TEST CONDITION                 | MIN. | TYP. | MAX. | UNIT |

|------------------------------------|-------------------|----------------------|--------------------------------|------|------|------|------|

| Operating Clock<br>Frequency Range | fcK               |                      |                                | _    | ~    | 2.0  | MHz  |

| Clock Pulse Width                  | <sup>t</sup> CKW  |                      |                                | 250  | ~    | _    |      |

|                                    | t <sub>pd1</sub>  |                      |                                | _    | ~    | 250  |      |

| Data Delay Time                    | t <sub>pd2</sub>  | <b>]</b> —           | Refer to timing chart as below | _    | ~    | 250  |      |

|                                    | t <sub>pd3</sub>  |                      |                                | _    | ~    | 250  | ns   |

| CE Pulse Width                     | tCEW              |                      |                                | 250  | ~    | _    |      |

| Data Set Time                      | t <sub>set</sub>  |                      |                                | 250  | ~    | _    |      |

| Data Hold Time                     | t <sub>HOLD</sub> |                      |                                | 250  | ~    | _    |      |

# CE, CK, DATA-OUT TIMING

1997-06-06 15/17

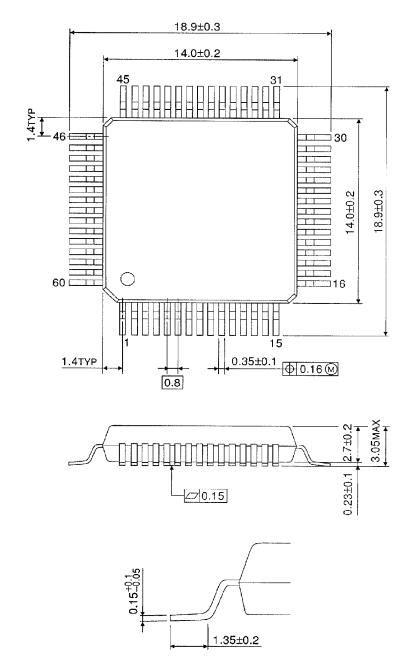

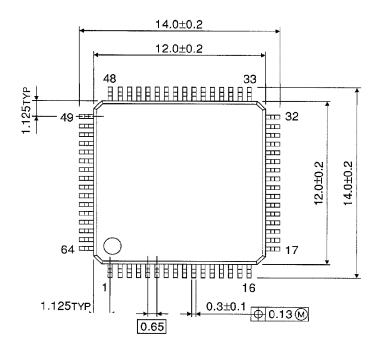

# OUTLINE DRAWING QFP60-P-1414-0.80D

Unit: mm

Weight: 1.10g (Typ.)

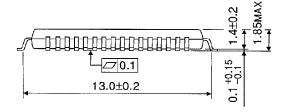

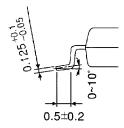

# OUTLINE DRAWING QFP64-P-1212-0.65

Unit: mm

Weight: 0.45g (Typ.)