## Domosys

## ODVay PL-One

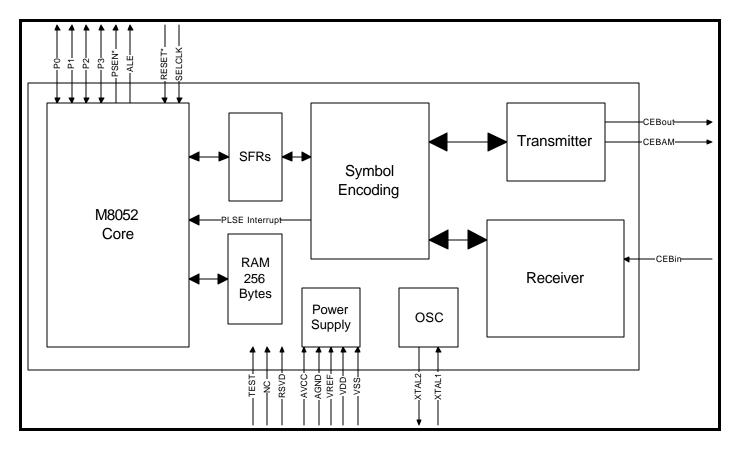

CEWay™ is a family of chips developed by DOMOSYS Corporation to meet the requirements of the residential and commercial local area networks (LANs). The CEWay PL-One is the ideal device for simple nodes, such as switches, actuators and sensors. It integrates the complete Physical Layer of the CEBus® standard (EIA-600) and an M8052 core microcontroller. It provides you with all of the resources you need to embed the upper layers of the CEBus standard and the user application into a single-chip solution. The CEWay PL-One is designed for superior performance in noisy power line environments.

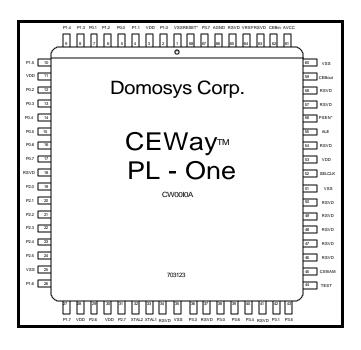

Figure 1 Pin-out for CEWay PL-One

## **Features**

- CEBus power line Physical Layer

- Power line medium dependent Physical and Symbol Encoding Sublayers

- Proprietary DSP for superior signal Reception in noisy environments

- M8052 core microcontroller

- 4 SFRs for communication between PLSES and M8052

- Up to 64 KB of external data memory

- 256 bytes of internal data memory

- Up to 64 KB of external code memory (can be extended with bank switching)

- Three 16-bit timer/counters

- Full-duplex serial port

- 15 I/O pins

- 68-pin PLCC package

- Industrial operating temperature range

D-CW-0100-04 Page 1 of 56

## **CEWay PL-One Block Diagram**

Figure 2 CEWay PL-One Block Diagram

## **Pin Descriptions**

Table 1 CEWay PL-One Pin Descriptions

| Symbol      | PIN             | Descripti    | on                                   |                          |

|-------------|-----------------|--------------|--------------------------------------|--------------------------|

| P0.0 – P0.7 | 5, 7, 12, 13,   |              | -bit bi-directional I/O port         |                          |

|             | 14, 15, 16, 17  |              | Alternative Function                 |                          |

|             |                 | P0.0         | A/D0                                 |                          |

|             |                 | P0.1         | A/D1                                 |                          |

|             |                 | P0.2         | A/D2                                 |                          |

|             |                 | P0.3         | A/D3                                 |                          |

|             |                 | P0.4         | A/D4                                 |                          |

|             |                 | P0.5         | A/D5                                 |                          |

|             |                 | P0.6         | A/D6                                 |                          |

| D4 0 D4 7   | 0.4.0.0.0       | P0.7         | A/D7                                 |                          |

| P1.0 – P1.7 | 2, 4, 6, 8, 9,  |              | -bit bi-directional I/O port         |                          |

|             | 10, 26, 27      | Port Pin     | Alternative Function                 |                          |

|             |                 | P1.0         | T2                                   |                          |

|             |                 | P1.1<br>P1.2 | T2EX                                 |                          |

|             |                 | P1.2<br>P1.3 | -                                    |                          |

|             |                 | P1.4         | -                                    |                          |

|             |                 | P1.5         | _                                    |                          |

|             |                 | P1.6         | _                                    |                          |

|             |                 | P1.7         | -                                    |                          |

| P2.0 – P2.7 | 19, 20, 21, 22, |              | -bit bi-directional I/O port         |                          |

|             | 23, 24, 29, 31  |              | Alternative Function                 |                          |

|             |                 | P2.0         | A8                                   |                          |

|             |                 | P2.1         | A9                                   |                          |

|             |                 | P2.2         | A10                                  |                          |

|             |                 | P2.3         | A11                                  |                          |

|             |                 | P2.4         | A12                                  |                          |

|             |                 | P2.5         | A13                                  |                          |

|             |                 | P2.6         | A14                                  |                          |

|             |                 | P2.7         | A15                                  |                          |

| P3.0, P3.1  |                 |              | bit I/O port. 2 bi-directional pins, | 3 outputs, and 2 inputs. |

| P3.3 – P3.7 | 43, 39, 67      | Output pir   | ns always read as 0.                 |                          |

|             |                 | Port Pin     | Alternative Function                 | Direction                |

|             |                 | P3.0         | RxD                                  | Bi-directional           |

|             |                 | P3.1         | TxD                                  | Bi-directional           |

|             |                 | P3.2         | INT0: Not available externally,      | N/A                      |

|             |                 |              | used for PLSES Interrupt.            |                          |

|             |                 | P3.3         | INT1                                 | Input                    |

|             |                 | P3.4         | T0                                   | Output                   |

|             |                 | P3.5         | T1                                   | Input                    |

|             |                 | P3.6         | WR*                                  | Output                   |

| VTALO       | 00              | P3.7         | RD*                                  | Output                   |

| XTAL2       | 32              |              | Output to the inverting oscillator   | amplifier that forms the |

|             |                 | oscillator.  |                                      |                          |

D-CW-0100-04 Page 3 of 56

| Symbol | PIN                                                             | Description                                                                                                                                                                                                                               |

|--------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL1  | 33                                                              | Crystal 1: Input to the inverting oscillator amplifier that forms the oscillator.                                                                                                                                                         |

| CEBAM  | 45                                                              | Output: Digital output used to enable and disable the transmit amplifier.                                                                                                                                                                 |

| CEBOUT | 59                                                              | CEBus power line signal output                                                                                                                                                                                                            |

| CEBIN  | 62                                                              | CEBus power line signal input                                                                                                                                                                                                             |

| SELCLK | 52                                                              | SELCLK: Must be connected to VDD if 14.31818 MHz is used. Connected to VSS if 21.4772 MHz is used.                                                                                                                                        |

| PSEN*  | 56                                                              | PSEN*: Reads strobe to the external program memory via Port 0 and Port2.                                                                                                                                                                  |

| ALE    | 55                                                              | ALE: Latches the low byte of the address during access of external memory in normal operation.                                                                                                                                            |

| VREF   | 64                                                              | Input for analog reference. A 1 μF capacitance must be put between this pin and AGND.                                                                                                                                                     |

| RESET* | 68                                                              | Reset: A LOW on this pin for 24 machine cycles and while the oscillator is running resets the device. This pin has an internal pull-up resistor. Note that, unlike most 8051 devices, no internal Schmitt Trigger is present on this pin. |

| AGND   | 66                                                              | Ground: 0 volt Analog Reference                                                                                                                                                                                                           |

| VDD    | 3, 11, 28, 30,<br>53                                            | Power Supply: Digital 5 volts                                                                                                                                                                                                             |

| VSS    | 1, 25, 35,<br>51,60                                             | Ground: 0 volt Digital Reference                                                                                                                                                                                                          |

| AVCC   | 61                                                              | Power Supply: Analog 5 volts                                                                                                                                                                                                              |

| RSVD   | 18, 34, 37, 41,<br>46, 47, 48, 49,<br>50, 54, 57, 58,<br>63, 65 | Reserved - Must be connected to VSS.                                                                                                                                                                                                      |

| TEST   | 44                                                              | TEST: Must be connected to VSS.                                                                                                                                                                                                           |

D-CW-0100-04 Page 4 of 56

## **Electrical Specifications**

## Absolute Maximum Rating<sup>1</sup>

| Parameter           | Sym                 | Min  | Max      | Units | Test Conditions |

|---------------------|---------------------|------|----------|-------|-----------------|

| Supply Voltage      | $V_{DD}$ - $V_{ss}$ | -0.3 | 7        | V     |                 |

| DC Input Voltage    | $V_{IN}$            | -0.3 | VDD +0.3 | V     |                 |

| DC Input Current    | I <sub>IN</sub>     | -10  | +10      | mΑ    |                 |

| Storage Temperature | $T_{STG}$           | -40  | +125     | οС    |                 |

| ESD Tolerance       |                     |      | 2        | kV    |                 |

<sup>&</sup>lt;sup>1</sup> Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

## DC Electrical Characteristics - Voltages are with respect to VSS unless otherwise stated

| Parameter                 | Sym               | Min     | Typ <sup>2-3</sup> | Max     | Units       | Test Conditions                |

|---------------------------|-------------------|---------|--------------------|---------|-------------|--------------------------------|

| Supply Voltage - Digital  | VDD               | 4.75    | 5                  | 5.25    | V           |                                |

| Supply Voltage - Analog   | AVCC              | 4.75    | 5                  | 5.25    | <b>&gt;</b> |                                |

| Input Voltage (high)      | $V_{IH}$          | 0.7VDD  |                    | VDD+0.3 | <b>&gt;</b> |                                |

| Input Voltage (low)       | $V_{IL}$          | VSS-0.3 |                    | 0.3VDD  | <b>&gt;</b> |                                |

| Output Voltage (high)     | V <sub>OH</sub>   | 2.4     |                    |         | V           | $I_{OH} = 50  \mu A$           |

| Output Voltage (low)      | $V_{OL}$          |         |                    | 0.4     | V           | $I_{OL} = 4 \text{ mA}$        |

| Operating Current Digital | $I_{VDD}$         |         | 25                 | 35      | mΑ          | $f_{CLK} = 14.318 \text{ MHz}$ |

| Operating Current Analog  | I <sub>AVCC</sub> |         | 9.5                | 15.5    | mΑ          | $f_{CLK} = 14.318 \text{ MHz}$ |

| Operating Temperature     | To                | -40     |                    | +85     | °C          |                                |

<sup>&</sup>lt;sup>2</sup> Typical figures are at 25 OC and are for design aid only: not guaranteed and not subject to production testing.

## **AC Electrical Characteristics**

| Parameter                    | Sym                  | Min      | Typ⁴ | Max     | Units | Test Conditions                |

|------------------------------|----------------------|----------|------|---------|-------|--------------------------------|

| CEBout Output Voltage        | $V_{CEBout}$         |          | 3.5  |         | V p-p |                                |

| CEBout Load Impedance        | ZL <sub>CEBout</sub> | 5        |      |         | kΩ    |                                |

| CEBin Input Impedance        | Zin <sub>CEBin</sub> | 40       | 68   | 140     | kΩ    |                                |

| Clock Frequency <sup>5</sup> | f <sub>CLK</sub>     | 14.31818 |      | 21.4772 | MHz   |                                |

| Pin Capacitance XTAL1,XTAL2  | $C_{XTAL}$           |          | 0.8  |         | рF    |                                |

| Input Pin Capacitance        | C                    |          | 8    |         | рF    | $f_{CLK} = 14.318 \text{ MHz}$ |

| Output Pin Capacitance       | Co                   |          | 8    |         | рF    | $f_{CLK} = 14.318 \text{ MHz}$ |

Typical figures are at 25 OC and are for design aid only: not guaranteed and not subject to production testing.

Clock frequency can only be either 14.31818 or 21.4772 MHz for proper chirp timing.

Page 5 of 56 D-CW-0100-04

<sup>&</sup>lt;sup>3</sup> DC Electrical Characteristics are over recommended temperature range & recommended power supply voltages.

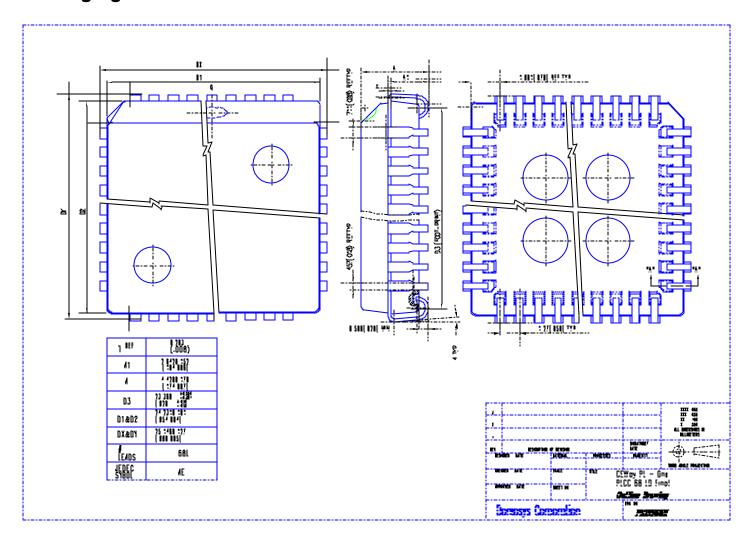

## **Packaging**

## **Ordering Information**

| Part Number | Description                     |

|-------------|---------------------------------|

| PONE-000-01 | CEWay PL-One Integrated Circuit |

D-CW-0100-04 Page 6 of 56

## **CEBus Standard Implementation**

The CEWay PL-One fully implements the CEBus Standard power line Physical Layer (PhyL) using dedicated circuitry. The Physical Layer is composed of a Medium Dependant Physical Sublayer (MDPS) and of a Power Line Symbol Encoding Sublayer (PLSES). It also provides an M8052 core microcontroller on-chip with which the upper layers (DLL, NL, and AL) of the CEBus standard or Home Plug & Play specification can be run. Libraries that implement these upper layers are available in CEBox<sup>™</sup>, the DOMOSYS' software system.

## Medium Dependent Physical Sublayer & Power Line Symbol Encoding Sublayer

The transceiver (MDPS and PLSES) is composed of a transmit chain and a receive chain. The transmitter provides an analog representation of a stored ROM code to an off-chip amplifier for transmission. Upon reception, the device samples the incoming filtered waveform through an ADC and provides a bit-by-bit comparison with an internally stored set of waveform probabilities. When a digital threshold is exceeded, the bit is stored with the rest of the message.

The symbol decoder performs leading zero suppression and recognizes the Preamble EOF (PEOF) string in order to force the device into the receive state. The symbol decoder recognizes the incoming signals from the transversal filter and prepares them for storage in RAM.

The MDPS and PLSES embed a part of the Layer System Management (LSM).

Detailed information on the CEBus Power Line Physical Layer can be found in the following documents:

- EIA 600.31

- IS 60.03 parts 7 & 8

D-CW-0100-04 Page 7 of 56

## M8052 to Physical Layer Interface

Even though the Physical Layer is also composed of the MDPS, the PL-One firmware only communicates with the PLSES through 4 Special Function Registers (SFRs). The PLSES then communicates with the MDPS if need be.

## Power Line Symbol Encoding Sublayer (PLSES)

The main task of the PLSES is to encode/decode a sequence of symbols into/from a stream of states. In addition, it has the task of recognizing the beginning of an incoming frame, and preventing a frame collision when the PL-One firmware requests the channel for a transmission. Sometimes it must suppress leading zeros in a given field before transmitting it, or restore them when receiving it. It also computes the CRC checksum appended to the end of a frame while transmitting or receiving it to ensure communication integrity. The PLSES will also detect Jabber conditions, defined as the transmission or reception of 1,000 consecutive SUPERIOR states on the medium, and indicates this via a PLSES Handshake Interrupt. A timestamp can also be provided following any reception or transmission.

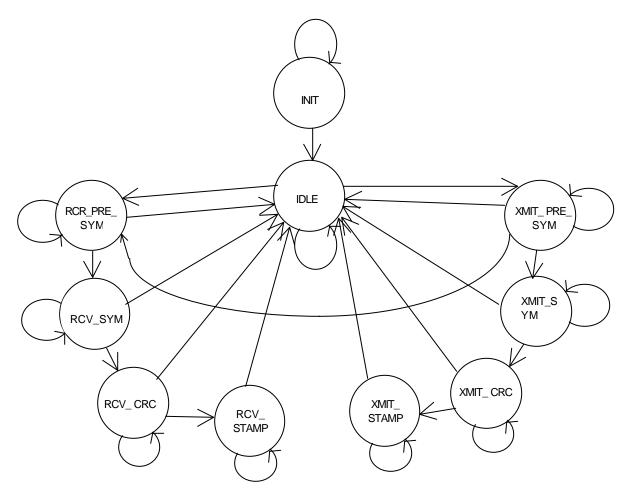

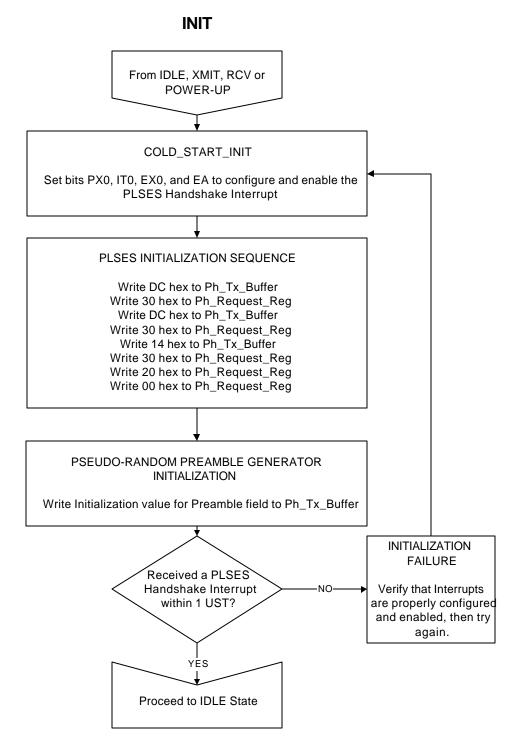

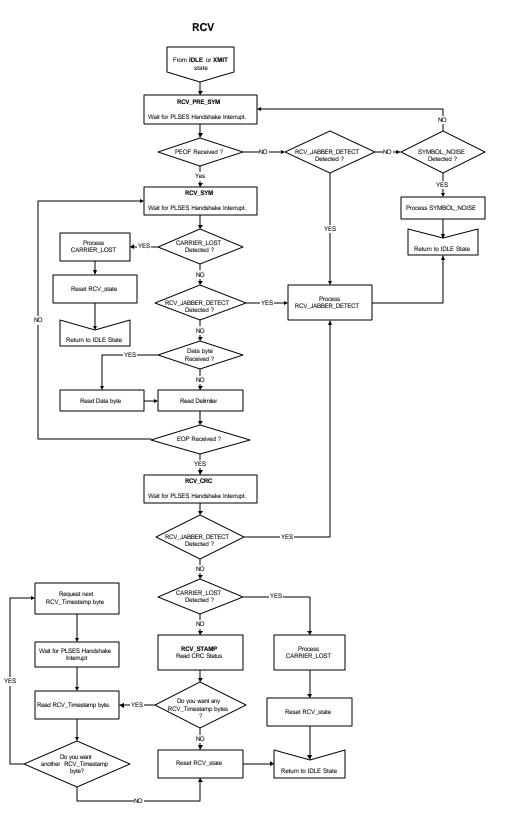

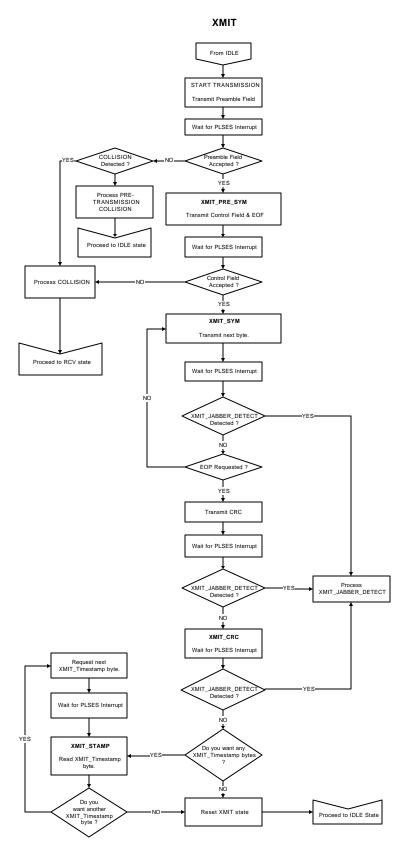

The PLSES operates in four main states: Initialization (INIT), Reception (RCV), Transmission (XMIT) and Idle (IDLE). The RCV and XMIT states can be divided into sub-states as shown in Figure 3 State Transition Diagram for PLSES.

The data travel between the PLSES and the M8052 through four Special Function Registers (SFRs). Each one is 8-bit wide. They are denoted: Ph\_Confirm\_Reg, Ph\_Request\_Reg, Ph\_Rx\_Buffer and Ph\_Tx\_Buffer. When a communication is requested by the PLSES to the PL-One firmware, an interrupt (INT0) is sent to the M8052. The latter then reads the flags in the Ph\_Confirm\_Reg SFR to determine the type of interrupt service routine to execute. The description of all flags is shown in Table 3. On the other hand, when the PL-One firmware requests an action by the PLSES, the former writes a control value to the Ph\_Request\_Reg. The description and the configuration of each of the control bits is shown in Table 6.

Data travels from the M8052 to the PLSES through the Ph\_Tx\_Buffer SFR one byte at a time. Similarly, the data is read by the PL-One firmware through the Ph\_Rx\_Buffer SFR one byte at a time.

## Ph Rx Buffer

It is used to pass on the packet Data symbols. It should be pointed out that when the Leading Zero Suppression function has been carried out, the empty positions are padded with zeros. It is also used to pass up both the reception and transmission timestamp bytes.

## Ph\_Confirm\_Reg

The values of the 6 LSBits of this port are valid for exactly one read cycle after receiving a PLSES Handshake Interrupt. When this port has been read once, the LSBits' values will not necessarily be valid until the next time a PLSES Handshake Interrupt is received. The 2 MSBits (*ch\_active* and *ch\_noisy*) of this port are always valid.

D-CW-0100-04 Page 8 of 56

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Ph_Confirm_Reg      |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

|       |       |       |       |       |       |       | 0     | jabber              |

|       |       |       |       |       |       | 0     |       | rx_del <sub>0</sub> |

|       |       |       |       |       | 0     |       |       | rx_del <sub>1</sub> |

|       |       |       |       | 0     |       |       |       | gd/packet           |

|       |       |       | 0     |       |       |       |       | be/bf               |

|       |       | 0     |       |       |       |       |       | col/rx              |

|       | 0     |       |       |       |       |       |       | ch_noisy            |

| 0     |       |       |       |       |       |       |       | ch_active           |

Table 2 Ph\_Confirm\_Reg in Idle State

|                    | Bits in Ph_Confirm_Reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ch_active<br>(MSB) | <u>Description</u> : Channel active indicates the presence of a CEBuslike signal on the channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    | Hardware (HW)Reset state: 0 Enable trigger: Set to 1 whenever a chirp is detected on the medium. It is maintained as long as chirps continue to be detected. This includes the special behavior described for the Ph_Confirm_Reg col/rx flag. It is also maintained while PLSES receives one symbol and is trying to identify a symbol noise condition as described for the Ph_Confirm_Reg ch_noisy flag. Reset trigger: It is reset as soon as the reception of a packet ends (after the reception of the CRC or after a Carrier Lost), when already within the RCV state. If in the IDLE state, it means it was activated from a Symbol Noise. It should then be reset as soon as ch_noisy is enabled.                                                                                                                         |

| ch_noisy           | <u>Description</u> : Channel noisy. In IDLE state, it indicates the presence of an isolated strong peak on the channel (Symbol Noise). At the transition from IDLE to the RCV state, it indicates a frame buried in noise (Medium Noisy). During the rest of the RCV state, it indicates the loss of the carrier (Carrier Lost). <u>HW Reset state</u> : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | Enable trigger: Symbol Noise: Set to 1 when one SUPERIOR Preamble symbol, or 1 PEOF delimiter symbol, followed by 5 consecutive INFERIOR Preamble symbols (1.14 USTs) have been detected. As soon as the 5 <sup>th</sup> consecutive symbol is identified as an INFERIOR, <i>ch_noisy</i> is set to 1. Medium Noisy: It is also set to 1 when only 3 to 6 (inclusive) PEOF symbols were detected. Carrier Lost: It is set to 1 when, after having received at least a PEOF and any other symbols after that PEOF, and before a complete CRC has been received, an INFERIOR state is detected on the medium. Reset trigger: In a Symbol Noise condition, it is reset as soon as a new chirp is detected. If no new chirps are detected, or for the two other conditions, it is reset when the PLSES Handshake Interrupt is reset. |

D-CW-0100-04 Page 9 of 56

|           | Bits in Ph_Confirm_Reg                                                                                                                                                                                                                                                                                                                                                             |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit       | Description                                                                                                                                                                                                                                                                                                                                                                        |

| col/rx    | <u>Description</u> : Collision/Reception. In the XMIT state, it indicates the detection of a collision with another frame during the transmission of the Preamble field. In the RCV state, it indicates that you are past the Preamble and PEOF and into the body of a packet. HW Reset state: 0                                                                                   |

|           | Enable trigger: Set to 1 when a collision is detected during transmission of the Preamble (when the PLSES transmits an INFERIOR but detects a SUPERIOR state on the medium). Also set to 1 as soon as the PLSES has detected a PEOF in reception, and remains at 1 throughout the reception. It remains enabled for a Carrier Lost indication.                                     |

|           | Reset trigger: It is reset when the PLSES Handshake Interrupt is reset.  Special constraints: Following a collision the PLSES will automatically transition from its XMIT state to its RCV state. At the same time, <i>ch_active</i> is enabled since a SUPERIOR Preamble symbol has been detected over our INFERIOR Preamble symbol.                                              |

| be/bf     | <u>Description</u> : Buffer Empty/Buffer Full. In XMIT state, it indicates that the Ph_Tx_Buffer has been transmitted successfully and is empty. This flag is also set to 1 when the CRC checksum has been appended to the end of the frame and transmitted. In RCV state, it indicates that the data within the Ph_Rx_Buffer is valid. HW Reset state: 0                          |

|           | Enable trigger: Set to 1 after the PLSES has transmitted on the medium a previous packet field part, via a request with the Ph_Request_Reg. Set to 1 when the PLSES has stored packet Preamble symbols or Data symbols in the Ph_Rx_Buffer.  Reset trigger: It is reset when the PLSES Handshake Interrupt is reset.                                                               |

| gd_packet | Description: Good Packet. In RCV state, it indicates that no error has been detected in the CRC checksum. If it is not set after having received the CRC, it means that the incoming packet was corrupted during the communication.  HW Reset state: 0  Enable trigger: Set to 1 after the last CRC symbol has been received and the CRC checksum has been verified as successful. |

|           | Reset trigger: It is reset when the PLSES Handshake Interrupt is reset.                                                                                                                                                                                                                                                                                                            |

D-CW-0100-04 Page 10 of 56

|                                            | Bits in Ph_Confirm_Reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| rx_del <sub>1</sub><br>rx_del <sub>0</sub> | <ul> <li><u>Description</u>: Reception delimiters. In RCV state, this pair of bits indicates the type of delimiter which terminates the current byte. Their configuration is shown below in Table 4.     <u>HW Reset state</u>: 00     <u>Enable trigger</u>:     <ul> <li>Set to 11 when a PEOF symbol has been detected and received.</li> <li>Set to 10 when an EOP symbol has been detected and received. Also set</li> </ul> </li></ul>                                                                                                                                                                                                                                                                                                                                                           |

|                                            | <ul> <li>to 10 after the CRC has been received and the checksum result is available, or set to 10 when the reception timestamp bytes are being passed to the PL-One firmware.</li> <li>Set to 01 when an EOF symbol has been detected and received.</li> <li>Set to 00 when 8 consecutive packet Data symbols have been saved in Ph_Rx_Buffer before receiving an EOF or EOP delimiter symbol. This case can happen for any packet field part, including those transmitted with Leading Zero Suppression (LZS). Also set to 00 when a PEOF symbol has been received but fewer than 8 Preamble symbols were detected. This situation is likely to happen with a Medium Noisy indication (see ch_noisy bit).</li> <li>Reset trigger: It is reset when the PLSES Handshake Interrupt is reset.</li> </ul> |

| jabber (LSB)                               | Description: Jabber Detect. In XMIT state, it indicates that the PL-One has transmitted at least 1,000 consecutive SUPERIOR symbols. In RCV state, it indicates that the PL-One has received at least 1,000 consecutive SUPERIOR symbols.  HW Reset state: 0  Enable trigger: Set to 1 after the PL-One has transmitted at least 1,000 consecutive SUPERIOR symbols. Also set to 1 after the PL-One has received at least 1,000 consecutive SUPERIOR symbols.  Reset trigger: It is reset when 1024 consecutive SUPERIOR states have been detected on the channel in either transmission or reception.                                                                                                                                                                                                 |

Table 3 Explanation of Bits in Ph\_Confirm\_Reg SFR

| Symbol       | del <sub>1</sub> | del <sub>0</sub> | # USTs |

|--------------|------------------|------------------|--------|

| EOF          | 0                | 1                | 3      |

| EOP          | 1                | 0                | 4      |

| PEOF         | 1                | 1                | 8      |

| No delimiter | 0                | 0                | 0      |

Table 4 Bit Representation of Four Possible Delimiters (EOF, EOP, PEOF, and none)

D-CW-0100-04 Page 11 of 56

## **PLSES Handshake Interrupt Generation**

The PL-One firmware is supplied with an interrupt from the PLSES which is called the "PLSES Handshake Interrupt". This uses the standard 8052 INTO\* interrupt. This means that the port bit P3.2 is no longer available for the user application. P3.2 will normally read as 1, but will fall to 0 as soon as an interrupt is generated from the PLSES. It will remain at 0 until the Ph\_Confirm\_Reg is read.

Note that this interrupt (INT0) MUST be set to the high priority level to ensure that no packets are lost. For this interrupt to be properly configured, the following four bits need to be set:

- PX0: Sets INT0 to high priority

- IT0: INT0 triggers on a falling edge

- EX0: INT0 is enabled

- EA: Enable interrupts

The PLSES Handshake Interrupt is used by the PL-One firmware to perform its communication handshake with the PLSES, and may indicate that valid data is present in the Ph\_Rx\_Buffer. It is provided by PLSES based on some specific PLSES states and events. These are defined in Table 7. The Ph\_Confirm\_Reg needs to always be read to determine the cause of the interrupt, and to process it accordingly.

The PLSES Handshake Interrupt is reset only after a PLSES Handshake Interrupt has been generated, followed by the reading of the Ph\_Confirm\_Reg. Note that the PLSES Handshake Interrupt needs to have been generated first, in order to distinguish between the Ph\_Confirm\_Reg being read by the user application while in its main processing. This can be shown as follows:

- 1. PLSES Handshake Interrupt is generated

- 2. Ph\_Confirm\_Reg is read

- 3. The PLSES Handshake Interrupt is reset

## Ph\_Tx\_Buffer

The Ph\_Tx\_Buffer is used to pass initialization parameters and data to be transmitted down to the PLSES. Setting the *Izs* bit in Ph\_Request\_Reg will result in all leading zeros in this byte not being transmitted. To simply transmit a field delimiter without any data symbols, this byte should be loaded with 00 hex, and transmitted with leading zero suppression. The only exception to this is when transmitting the Preamble field, in which case the contents of the Ph\_Tx\_Buffer have no effect on the Preamble which is transmitted.

## Ph Request Reg

The Ph\_Request\_Reg is initialized with 00 hex following a hardware reset. The Ph\_Request\_Reg is read and interpreted by the PLSES each time it is written to. This value is maintained until it is next written to by the PL-One firmware. The various state transitions that can be brought about by writing to Ph\_Request\_Reg are listed in Table 8.

D-CW-0100-04 Page 12 of 56

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Ph_Request_Reg      |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

|       |       |       |       |       |       |       | 0     | stamp               |

|       |       |       |       |       |       | 0     |       | tx_del <sub>0</sub> |

|       |       |       |       |       | 0     |       |       | tx_del <sub>1</sub> |

|       |       |       |       | 0     |       |       |       | reserved            |

|       |       |       | 0     |       |       |       |       | Izs                 |

|       |       | 0     |       |       |       |       |       | stop_rx             |

|       | 0     |       |       |       |       |       |       | hw_reset            |

| 0     |       |       |       |       |       |       |       | tx                  |

Table 5 Value to write to Ph\_Request\_Reg SFR to stop transmission and return to Idle state

| Bits in Ph_Request_Reg |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit                    | Description                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| tx (MSB)               | Transmission. In IDLE state, it forces the PLSES to enter the XMIT state. In XMIT state, it should always be high. In RCV state, it should always be low.                                                                                                                                                                                                                                                            |  |  |

| hw_reset               | Hardware Reset. In all states, this bit forces the whole Physical Layer (PhyL) to perform a hardware reset and return to the INIT state.                                                                                                                                                                                                                                                                             |  |  |

| stop_rx                | Stop reception. In the INIT state, it is set when passing initialization parameters to the PLSE. In the RCV state, it forces the PLSES to stop reception and enter the IDLE state.                                                                                                                                                                                                                                   |  |  |

| Izs                    | Leading Zero Suppression. In the INIT state, it is set when passing initialization parameters to the PLSE. In the XMIT state, it forces the PLSES to suppress the leading zeros in the Ph_Tx_Buffer. When transitioning from the IDLE to the XMIT_PRE_SYM state, it forces the PLSES to suppress the Preamble symbols; in this case, only the PEOF is transmitted (e.g. for transmitting an IACK or IRetry packets). |  |  |

| reserved               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| tx_del <sub>1</sub>    | Transmission delimiters. This pair of bits is used to select the type of                                                                                                                                                                                                                                                                                                                                             |  |  |

| tx_del <sub>0</sub>    | delimiter to transmit after the byte contained in Ph_Tx_Buffer. The mapping between these bits and the possible delimiters is shown in Table 4.                                                                                                                                                                                                                                                                      |  |  |

| stamp (LSB)            | Stamp. At the end of the RCV or XMIT states, this flag indicates to the PLSES that the PL-One firmware needs one more significant timestamp byte (to a maximum of four total) recorded when the last CRC symbol was received or transmitted.                                                                                                                                                                         |  |  |

Table 6 Explanation of Bits in the Ph\_Request\_Reg SFR

## State Transition Tables for Ph\_Confirm\_Reg and Ph\_Request\_Reg

The following two tables (Table 7 and Table 8) show the state transitions associated with the PLSES Handshake Interrupts (reads of Ph\_Confirm\_Reg), and writes to Ph\_Request\_Reg.

| Current State | Next State   | Ph_Confirm | Transition                                                     |  |

|---------------|--------------|------------|----------------------------------------------------------------|--|

|               |              | _Reg       |                                                                |  |

| IDLE          | RCV_PRE_SYM  | 1000 0000  | Detection of first SUPERIOR and <i>stop_rx</i> bit not active. |  |

| XMIT_PRE_SYM  | XMIT_PRE_SYM | 0001 0000  | After command to start transmission.                           |  |

| IDLE          | IDLE         | 0000 0000  | Ch_Quiet indication every UST.                                 |  |

D-CW-0100-04 Page 13 of 56

| Current State | Next State           | Ph_Confirm                | Transition                                                                      |  |

|---------------|----------------------|---------------------------|---------------------------------------------------------------------------------|--|

| RCV PRE SYM   | RCV PRE SYM          | _ <b>Reg</b><br>1000 0000 | Detection of INFERIOR or SUPERIOR state                                         |  |

| 1.01_1.1.2_01 | 1.0 v_1 1.12_0 1.111 | 1000 0000                 | and                                                                             |  |

|               |                      |                           | 1) if current state is INFERIOR, the number                                     |  |

|               |                      |                           | of consecutive INFERIORs is < 5, or                                             |  |

|               |                      |                           | 2) if current state is SUPERIOR, it is of the                                   |  |

|               |                      |                           | same phase as the first SUPERIOR.                                               |  |

| RCV_PRE_SYM   | IDLE                 | 0100 0000                 | Detection of 5 consecutive INFERIORs.                                           |  |

| RCV_PRE_SYM   | RCV_SYM              | 1011 0110                 | Detection of opposite phase SUPERIOR after                                      |  |

|               |                      |                           | previously detecting 7 or 8 consecutive                                         |  |

| DOV DDE OVIM  | DOV OVA              | 4444 0440                 | SUPERIORs.                                                                      |  |

| RCV_PRE_SYM   | RCV_SYM              | 1111 0110                 | Detection of opposite phase SUPERIOR after previously detecting between 3 and 6 |  |

|               |                      |                           | (inclusive) consecutive SUPERIORs.                                              |  |

| RCV PRE SYM   | RCV PRE SYM          | XXXX XXX1                 | Jabber error.                                                                   |  |

| RCV_SYM       | RCV CRC              | 1011 0100                 | Detection of EOP and valid data in                                              |  |

| 1.00_01101    | 1101_0110            | 1011 0100                 | Ph_Rx_Buffer.                                                                   |  |

| RCV_SYM       | RCV_CRC              | 1010 0100                 | Detection of EOP and no data in                                                 |  |

| _             | _                    |                           | Ph_Rx_Buffer.                                                                   |  |

| RCV_SYM       | RCV_SYM              | 1011 0000                 | Detection of data and 8 valid data bits in                                      |  |

|               |                      |                           | Ph_Rx_Buffer.                                                                   |  |

| RCV_SYM       | RCV_SYM              | 1011 0010                 | Detection of EOF and valid data in                                              |  |

|               |                      |                           | Ph_Rx_Buffer.                                                                   |  |

| RCV_SYM       | RCV_SYM              | 1010 0010                 | Detection of EOF and no data in                                                 |  |

| DOV / OV / A  | DOV 0 (M             | 0440 0000                 | Ph_Rx_Buffer.                                                                   |  |

| RCV_SYM       | RCV_SYM              | 0110 0000                 | Detection of INFERIOR, as a result of carrier                                   |  |

| RCV SYM       | RCV SYM              | XXXX XXX1                 | loss. Jabber error.                                                             |  |

| RCV_CRC       | RCV_STAMP            | 1011 X100                 | Received 16 CRC bits to report CRC status.                                      |  |

| RCV_CRC       | RCV CRC              | 0110 0000                 | Detection of INFERIOR prior to all 16 CRC                                       |  |

| 1.01_01.0     | 1101_0110            | 0110 0000                 | bits, as a result of carrier loss.                                              |  |

| RCV CRC       | RCV_CRC              | XXXX XXX1                 | Jabber error.                                                                   |  |

| RCV_STAMP     | RCV_STAMP            | 1011 0100                 | After each timestamp byte is uploaded.                                          |  |

| XMIT_PRE_SYM  | RCV_PRE_SYM          | 1010 0000                 | Collision detected.                                                             |  |

| XMIT_PRE_SYM  | XMIT_SYM             | 0001 0000                 | Transmission of Preamble completed.                                             |  |

| XMIT_PRE_SYM  | XMIT_PRE_SYM         | XXXX XXX1                 | Jabber error.                                                                   |  |

| XMIT_SYM      | XMIT_SYM             | 0001 0000                 | Buffer empty.                                                                   |  |

| XMIT_SYM      | XMIT_CRC             |                           | Start transmission of CRC. No interrupt is                                      |  |

|               |                      |                           | generated.                                                                      |  |

| XMIT_SYM      | XMIT_SYM             | XXXX XXX1                 | Jabber error.                                                                   |  |

| XMIT_CRC      | XMIT_STAMP           | 0001 0000                 | Transmission of CRC completed.                                                  |  |

| XMIT_CRC      | XMIT_CRC             | XXXX XXX1                 | Jabber error.                                                                   |  |

| XMIT_STAMP    | XMIT_STAMP           | 0001 0000                 | After each timestamp byte is uploaded.                                          |  |

Table 7 State Transitions Associated with PLSES Handshake Interrupts

D-CW-0100-04 Page 14 of 56

| Current State | Ph_Request                      | Next State | Transition                              |  |

|---------------|---------------------------------|------------|-----------------------------------------|--|

|               | _Reg                            |            |                                         |  |

| IDLE          | 101x 0110 XMIT_PRE_SYM Command  |            | Command to start transmission.          |  |

| RCV_PRE_SYM   | X01X XXXX IDLE Abort reception. |            | Abort reception.                        |  |

| RCV_SYM       | X01X XXXX                       | IDLE       | Abort reception.                        |  |

| RCV_CRC       | X01X XXXX                       | IDLE       | Abort reception.                        |  |

| RCV_STAMP     | X01X XXXX                       | IDLE       | Abort reception.                        |  |

| RCV_STAMP     | 0000 0001                       | RCV_STAMP  | This indicates that the MACS needs one  |  |

|               |                                 |            | more timestamp byte.                    |  |

| XMIT_PRE_SYM  | 101X 0XX0                       | XMIT_SYM   | Bits 4, 2, and 1 indicate leading zero  |  |

|               |                                 |            | suppression and field delimiter.        |  |

| XMIT_PRE_SYM  | 00XX XXXX                       | IDLE       | Abort transmission,                     |  |

| XMIT_SYM      | 101X 0XX0                       | XMIT_SYM   | Bits 4, 2, and 1 indicate leading zero  |  |

|               |                                 |            | suppression and field delimiter.        |  |

| XMIT_SYM      | 00XX XXXX                       | IDLE       | Abort transmission.                     |  |

| XMIT_CRC      | 00XX XXXX                       | IDLE       | Abort transmission.                     |  |

| XMIT_STAMP    | 0000 0000                       | IDLE       | Complete transmission, does not require |  |

|               |                                 |            | any more timestamp bytes.               |  |

| XMIT_STAMP    | 1010 0001                       | XMIT_STAMP | This indicates that the MACS needs one  |  |

|               |                                 |            | more timestamp byte.                    |  |

Table 8 State Transitions Associated with Writes to Ph\_Request\_Reg

## **Time stamp Timer**

The PLSES supports a free-running 32-bit timer that is used to associate a timestamp to any received or transmitted packets. The resolution of this timestamp timer is 279 nsec (four oscillator cycles at 14.32 MHz, six cycles at 21.48 MHz.) For a received packet, the timestamp is acquired when the last CRC symbol has been completely received. For a transmitted packet, the timestamp is acquired when the CRC symbol has been completely transmitted. The least significant timestamp byte is transferred first, via Ph\_Rx\_Buffer, at the same time as the end of transmission or reception is indicated. Up to three additional timestamp bytes can be requested from the PLSES by writing 01 hex to the Ph\_Request\_Reg. These bytes are transferred with the least significant byte first.

D-CW-0100-04 Page 15 of 56

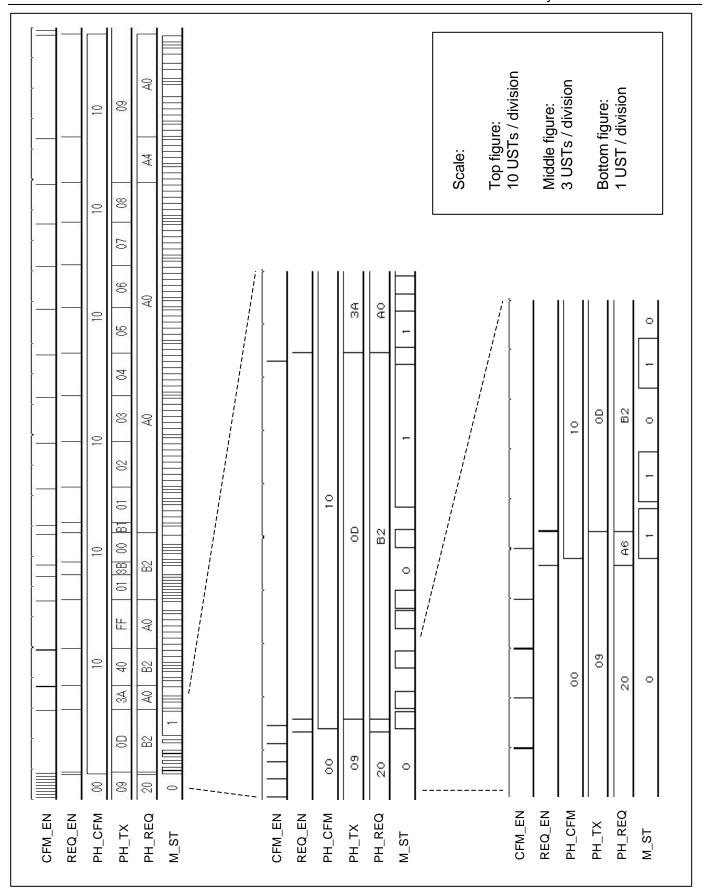

## PLSES - PL-One firmware Interface State Diagram

Figure 3 State Transition Diagram for PLSES

Note: Setting the Ph\_Request\_Reg *hw\_reset* bit will result in a transition to the INIT state from any other state or sub-state. This is not indicated on this diagram in order to simplify it.

D-CW-0100-04 Page 16 of 56

## **PLSES State Transition Table**

| State      | Description                                                                                                                                                                                                                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT State | The SES block goes into INIT state only after a hardware reset, or after the PL-One firmware sets the Ph_Request_Reg <i>hw_reset</i> bit. Two steps are required for the PL-One firmware to fully initialize the PLSES and get it to the IDLE state.                                                                                    |

|            | 1. The PLSE registers must be initialized by writing the following sequence of bytes: Write DC hex to Ph_Tx_Buffer Write 30 hex to Ph_Request_Reg Write DC hex to Ph_Tx_Buffer Write 30 hex to Ph_Request_Reg Write 14 hex to Ph_Tx_Buffer Write 30 hex to Ph_Request_Reg Write 20 hex to Ph_Request_Reg Write 00 hex to Ph_Request_Reg |

|            | <ol> <li>Second, an initial Preamble value must be written to Ph_Tx_Buffer,<br/>which is used as-is for the first transmitted packet. It is also used<br/>as a seed for the generation of pseudo-random Preamble values<br/>for subsequent transmitted frames.</li> </ol>                                                               |

|            | After these two steps, the SES finishes its initialization routine and goes into the IDLE state.                                                                                                                                                                                                                                        |

| IDLE State | In this state the SES has been initialized, is not transmitting a frame, and the channel is quiet. For each unit symbol time (UST) that passes, the SES block will send a PLSES Handshake Interrupt to the PL-One firmware, indicating that there is no activity on the channel.                                                        |

| Transition | The SES block will go from IDLE to XMIT_PRE_SYM when the command to transmit a PEOF is written to Ph_Request_Reg (101X 0110 bin).                                                                                                                                                                                                       |

| Transition | The SES block will go from IDLE to RCV_PRE_SYM when a SUPERIOR state has been detected on the channel.                                                                                                                                                                                                                                  |

D-CW-0100-04 Page 17 of 56

| State                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RCV_PRE_SYM<br>State | The PLSE Sublayer is in the process of receiving Preamble symbols, which are encoded using Preamble USTs that are 114 microseconds in length. This state counts the number of USTs in consecutive INFERIOR or SUPERIOR states to decode each symbol. At each received medium state transition (a SUPERIOR when LAST_RCV is INFERIOR or an INFERIOR when LAST_RCV is SUPERIOR), the symbol is decoded as "1" or "0" according to how many USTs elapsed between state transitions. The state also waits for the Preamble EOF (PEOF), which is 8 normal USTs in length (100 µs each.) In the case where there are no Preamble symbols, e.g. an IACK frame, the RCV_PRE_SYM state will only process and report the PEOF, and the Ph_Confirm_Reg <i>bf/be</i> bit will not be set. |  |  |  |

| Transition           | The SES block will go from RCV_PRE_SYM to RCV_SYM after it receives 3 or more SUPERIOR 1s with 100-microsecond (1 UST) spacing, and the medium state changes from SUPERIOR 1 to SUPERIOR 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Transition           | The SES block will go back to IDLE if it detects that the received SUPERIOR state was noise (a SUPERIOR state followed by five INFERIOR states), or if the Ph_Request_Reg stop_rx bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RCV_SYM State        | The PLSE Sublayer is in the process of receiving symbols within the body of the frame. At each received medium state transition (SUPERIOR 1 to SUPERIOR 2, or vice versa), the symbol is decoded according to the elapsed time since the previous transition. The symbol is stored in an 8-bit shift register in the SES block. When the shift register is full, or an EOF (End of Field) or EOP (End of Packet) symbol is received, the SES block will copy the data in the shift register to Ph_Rx_Buffer, and send a PLSES Handshake Interrupt to the PL-One firmware.                                                                                                                                                                                                     |  |  |  |

| Transition           | The SES will go to RCV_CRC after it receives an EOP symbol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Transition           | The SES will go to IDLE when the carrier is lost or when the Ph_Request_Reg stop_rx bit is set. The carrier lost condition is explained in a later section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| RCV_CRC State        | The PLSE Sublayer is in the process of receiving CRC symbols. A bit is shifted into the 16-bit CRC register for CRC computation every UST. A received SUPERIOR 1 shifts in a 1, and a received SUPERIOR 2 shifts in a 0. After 16 USTs, the Ph_Confirm_Reg gd_packet bit is set according to whether or not the frame has kept its integrity during reception, and the SES will send a PLSES Handshake Interrupt to the PL-One firmware.                                                                                                                                                                                                                                                                                                                                      |  |  |  |

D-CW-0100-04 Page 18 of 56

| State                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Transition            | The SES will also start providing the timestamp to PL-One firmware after the CRC computation, and go to RCV_STAMP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Transition            | The SES will go back to IDLE when the carrier is lost or when the Ph_Request_Reg stop_rx bit is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| RCV_STAMP<br>State    | The PLSE Sublayer is in the process of providing the timestamp to the PL-One firmware. The timestamp is the time associated with the end of the packet CRC reception. The timestamp will be provided on four bytes (LSB first followed by more significant bytes) via the Ph_Rx_Buffer, where each byte will be sent to the PL-One firmware via a PLSES Handshake Interrupt in Ph_Rx_Buffer, and the Ph_Confirm_Reg be/bf bit will be set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Transition            | The SES will go back to IDLE when the Ph_Request_Reg <i>stamp</i> bit (bit 0) is cleared, and the <i>stop_rx</i> bit is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| XMIT_PRE_SYM<br>State | The PLSE Sublayer is in the process of transmitting Preamble symbols.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Decision              | If it is transmitting a long Preamble field (the Ph_Request_Reg Izs bit is 0), the SES will first transmit an 8-bit Preamble value. The PL-One firmware loads the initial Preamble value when the SES is in the INIT state. Later it is computed inside the SES through a pseudo-random process. The first symbol transmitted following a quiet channel is always encoded in SUPERIOR state, the next symbol will be encoded in INFERIOR state, the third symbol will be encoded as the same SUPERIOR state as the first symbol, etc. At the completion of transmitting 8-bit Preamble value, the SES will also transmit the PEOF (the same SUPERIOR state for 8 USTs) before going to the XMIT_SYM state. If it is transmitting a short Preamble field (the Ph_Request_Reg Izs bit is 1), the SES will not transmit an 8-bit Preamble value, instead it will transmit the 8 UST PEOF directly. But the SES still continues the process for computing the pseudo-random Preamble byte for later use. The SUPERIOR state used by XMIT_PRE_SYM state alternates between SUPERIOR 1 and SUPERIOR 2 for consecutive packets. The first packet transmitted will start with a SUPERIOR 1 state, the second packet transmitted will start with a SUPERIOR 2 state, the third one will be a SUPERIOR 1 and so on. |  |  |