## STS4NM20N

### N-CHANNEL 200V - 0.11Ω - 4A SO-8 ULTRA LOW GATE CHARGE MDmesh™ II MOSFET

TARGET DATA

| TYPE      | V <sub>DSS</sub> | R <sub>DS(on)</sub> | ID |

|-----------|------------------|---------------------|----|

| STS4NM20N | 200 V            | < 0.13 Ω            | 4A |

- WORLDWIDE LOWEST GATE CHARGE

- TYPICAL  $R_{DS}(on) = 0.11\Omega$

- HIGH dv/dt and AVALANCHE CAPABILITIES

- LOW INPUT CAPACITANCE

- LOW GATE RESISTANCE

- TIGHT PROCESS CONTROL AND HIGH MANUFACTURING YIELDS

### DESCRIPTION

This 200V MOSFET with a new advanced layout brings all unique advantages of MDmesh technology to lower voltages. The device exhibits worldwide lowest gate charge for any given on-resistance.Its use is therefore ideal as primary switch in isolated DC-DC converters for Telecom and Computer applications.Used in combination with secondary-side low-voltage STripFET<sup>™</sup> products, it contributes to reducing losses and boosting efficiency

### APPLICATIONS

The MDmesh<sup>™</sup> family is very suitable for increasing power density allowing system miniaturization and higher efficiencies

### **ORDERING INFORMATION**

| SALES TYPE | MARKING | PACKAGE | PACKAGING   |

|------------|---------|---------|-------------|

| STS4NM20N  | S4NM20N | SO-8    | TAPE & REEL |

### STS4NM20N

### ABSOLUTE MAXIMUM RATINGS

| Symbol                             | Parameter                                                                                               | Value     | Unit   |

|------------------------------------|---------------------------------------------------------------------------------------------------------|-----------|--------|

| V <sub>DS</sub>                    | Drain-source Voltage (V <sub>GS</sub> = 0)                                                              | 200       | V      |

| V <sub>DGR</sub>                   | Drain-gate Voltage ( $R_{GS}$ = 20 k $\Omega$ )                                                         | 200       | V      |

| V <sub>GS</sub>                    | Gate- source Voltage                                                                                    | ± 30      | V      |

| ۱ <sub>D</sub>                     | Drain Current (continuous) at $T_C = 25^{\circ}C$<br>Drain Current (continuous) at $T_C = 100^{\circ}C$ | 4<br>2.83 | A<br>A |

| I <sub>DM</sub> (2)                | Drain Current (pulsed)                                                                                  | 16        | A      |

| PTOT                               | Total Dissipation at T <sub>C</sub> = 25°C                                                              | 2.5       | W      |

|                                    | Derating Factor (1)                                                                                     | 0.02      | W/°C   |

| d <sub>v</sub> /d <sub>t</sub> (3) | Peak Diode Recovery voltage slope                                                                       | 10        | V/ns   |

### THERMAL DATA

| Rthj-pcb         | Thermal Resistance Junction-pcb Max (1) | 50         | °C/W |

|------------------|-----------------------------------------|------------|------|

| Tj               | Max. Operating Junction Temperature     | 150        | °C   |

| T <sub>stg</sub> | Storage Temperature                     | -55 to 150 | °C   |

### **AVALANCHE CHARACTERISTICS**

| Symbol          | Parameter                                                                                                                     | Max Value | Unit |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|-----------|------|

| I <sub>AR</sub> | Avalanche Current, Repetitive or Not-Repetitive (pulse width limited by T <sub>j</sub> max)                                   | TBD       | A    |

| E <sub>AS</sub> | Single Pulse Avalanche Energy<br>(starting T <sub>j</sub> = 25 °C, I <sub>D</sub> = I <sub>AR</sub> , V <sub>DD</sub> = 35 V) | TBD       | mJ   |

# **ELECTRICAL CHARACTERISTICS** (T<sub>CASE</sub> = 25 °C UNLESS OTHERWISE SPECIFIED) ON/OFF

| Symbol               | Parameter                                                | Test Conditions                                                         | Min. | Тур. | Max.    | Unit     |

|----------------------|----------------------------------------------------------|-------------------------------------------------------------------------|------|------|---------|----------|

| V <sub>(BR)DSS</sub> | Drain-source<br>Breakdown Voltage                        | $I_D = 1 \text{ mA}, V_{GS} = 0$                                        | 200  |      |         | V        |

| IDSS                 | Zero Gate Voltage<br>Drain Current (V <sub>GS</sub> = 0) | $V_{DS}$ = Max Rating<br>$V_{DS}$ = Max Rating, T <sub>C</sub> = 125 °C |      |      | 1<br>10 | μΑ<br>μΑ |

| I <sub>GSS</sub>     | Gate-body Leakage<br>Current (V <sub>DS</sub> = 0)       | V <sub>GS</sub> = ± 30 V                                                |      |      | 100     | μA       |

| V <sub>GS(th)</sub>  | Gate Threshold Voltage                                   | $V_{DS} = V_{GS}, I_D = 250 \ \mu A$                                    | 3.5  | 4.2  | 5       | V        |

| R <sub>DS(on)</sub>  | Static Drain-source On Resistance                        | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 2 A                            |      | 0.11 | 0.13    | Ω        |

### ELECTRICAL CHARACTERISTICS (CONTINUED)

### DYNAMIC

| Symbol                                                   | Parameter                                                                  | Test Conditions                                                       | Min. | Тур.             | Max. | Unit           |

|----------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------|------|------------------|------|----------------|

| g <sub>fs</sub> (4)                                      | Forward Transconductance                                                   | $V_{DS} = 15 \text{ V}$ , $I_D = 2 \text{ A}$                         |      | 1.4              |      | S              |

| C <sub>iss</sub><br>C <sub>oss</sub><br>C <sub>rss</sub> | Input Capacitance<br>Output Capacitance<br>Reverse Transfer<br>Capacitance | V <sub>DS</sub> = 25 V, f = 1 MHz, V <sub>GS</sub> = 0                |      | 670<br>180<br>12 |      | pF<br>pF<br>pF |

| C <sub>oss eq.</sub> (*)                                 | Equivalent Output<br>Capacitance                                           | $V_{GS} = 0V$ , $V_{DS} = 0V$ to 400V                                 |      | TBD              |      | pF             |

| R <sub>G</sub>                                           | Gate Input Resistance                                                      | f = 1 MHz Gate DC Bias = 0<br>Test Signal Level = 20 mV<br>Open Drain |      | TBD              |      | Ω              |

(\*)  $C_{oss eq.}$  is defined as a constant equivalent capacitance giving the same charging time as  $C_{oss}$  when  $V_{DS}$  increases from 0 to 80%  $V_{DSS}$

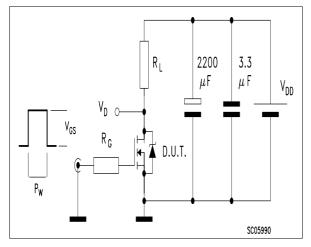

### SWITCHING ON

| Symbol                                               | Parameter                                                    | Test Conditions                                                          | Min. | Тур.            | Max. | Unit           |

|------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|------|-----------------|------|----------------|

| t <sub>d(on)</sub><br>t <sub>r</sub>                 | Turn-on Delay Time<br>Rise Time                              |                                                                          |      | TBD<br>TBD      |      | ns<br>ns       |

| Q <sub>g</sub><br>Q <sub>gs</sub><br>Q <sub>gd</sub> | Total Gate Charge<br>Gate-Source Charge<br>Gate-Drain Charge | V <sub>DD</sub> = 160 V, I <sub>D</sub> = 4 A,<br>V <sub>GS</sub> = 10 V |      | 19<br>3.5<br>11 |      | nC<br>nC<br>nC |

### SWITCHING OFF

| Symbol                                                    | Parameter                                             | Test Conditions | Min. | Тур.              | Max. | Unit           |

|-----------------------------------------------------------|-------------------------------------------------------|-----------------|------|-------------------|------|----------------|

| t <sub>r (Voff)</sub><br>t <sub>f</sub><br>t <sub>c</sub> | Off-Voltage Rise Time<br>Fall Time<br>Cross-Over Time |                 |      | TBD<br>TBD<br>TBD |      | ns<br>ns<br>ns |

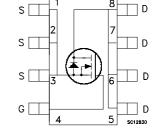

### SOURCE DRAIN DIODE

| Symbol                                                 | Parameter                                                                    | Test Conditions                                                                                                                                                                      | Min. | Тур.              | Max. | Unit          |

|--------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|------|---------------|

| I <sub>SD</sub>                                        | Source-drain Current                                                         |                                                                                                                                                                                      |      |                   | 4    | А             |

| I <sub>SDM</sub> (2)                                   | Source-drain Current (pulsed)                                                |                                                                                                                                                                                      |      |                   | 16   | А             |

| V <sub>SD</sub> (4)                                    | Forward On Voltage                                                           | $I_{SD} = 2 \text{ A}, V_{GS} = 0$                                                                                                                                                   |      |                   | 1.3  | V             |

| t <sub>rr</sub><br>Q <sub>rr</sub><br>I <sub>RRM</sub> | Reverse Recovery Time<br>Reverse Recovery Charge<br>Reverse Recovery Current | $I_{SD} = 2 \text{ A}$ , di/dt = 100 A/µs,<br>V <sub>DD</sub> = 100 V, T <sub>j</sub> = 25°C<br>(see test circuit, Figure 5)                                                         |      | 89<br>300<br>6.5  |      | ns<br>nC<br>A |

| t <sub>rr</sub><br>Q <sub>rr</sub><br>I <sub>RRM</sub> | Reverse Recovery Time<br>Reverse Recovery Charge<br>Reverse Recovery Current | $\begin{split} I_{SD} &= 2 \text{ A, di/dt} = 100 \text{ A/}\mu\text{s,} \\ V_{DD} &= 100 \text{ V, T}_{j} = 150^{\circ}\text{C} \\ (\text{see test circuit, Figure 5}) \end{split}$ |      | TBD<br>TBD<br>TBD |      | ns<br>nC<br>A |

Note: 1. When mounted on 1 inch<sup>2</sup> FR4 Board, 2oz of Cu, t≤ 10 sec. 2. Pulse width limited by safe operating area. 3.  $I_{SD} \le 4 \text{ A}$ , di/dt  $\le 400 \text{ A/}\mu\text{s}$ ,  $V_{DD} \le V_{(BR)DSS}$ ,  $T_j \le T_{jMAX}$ . 4. Pulsed: Pulse duration = 400 µs, duty cycle 1.5 %.

### STS4NM20N

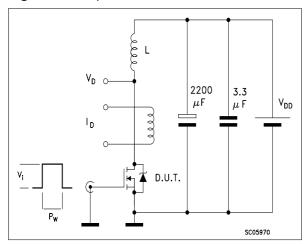

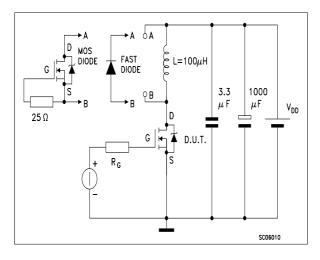

Fig. 1: Unclamped Inductive Load Test Circuit

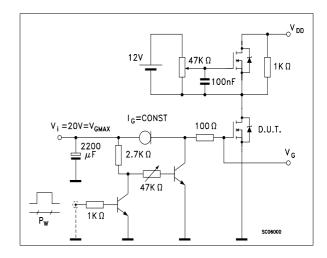

**Fig. 3:** Switching Times Test Circuit For Resistive Load

**Fig. 5:** Test Circuit For Inductive Load Switching And Diode Recovery Times

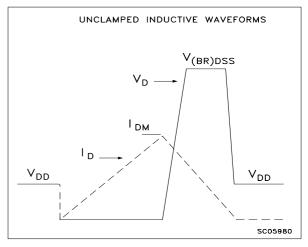

### Fig. 2: Unclamped Inductive Waveform

Fig. 4: Gate Charge test Circuit

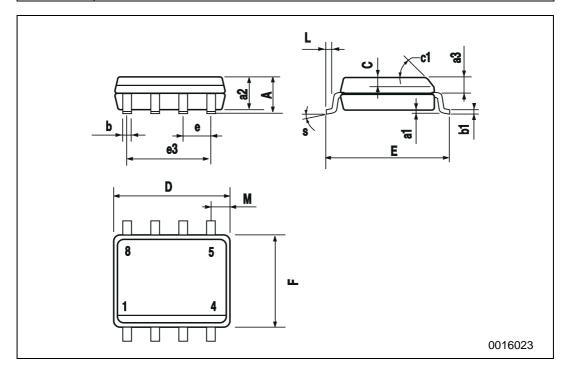

| DIM. |      | mm   |      | inch   |       |       |

|------|------|------|------|--------|-------|-------|

| DIM. | MIN. | TYP. | MAX. | MIN.   | TYP.  | MAX.  |

| А    |      |      | 1.75 |        |       | 0.068 |

| a1   | 0.1  |      | 0.25 | 0.003  |       | 0.009 |

| a2   |      |      | 1.65 |        |       | 0.064 |

| a3   | 0.65 |      | 0.85 | 0.025  |       | 0.033 |

| b    | 0.35 |      | 0.48 | 0.013  |       | 0.018 |

| b1   | 0.19 |      | 0.25 | 0.007  |       | 0.010 |

| С    | 0.25 |      | 0.5  | 0.010  |       | 0.019 |

| c1   |      |      | 45 ( | (typ.) |       |       |

| D    | 4.8  |      | 5.0  | 0.188  |       | 0.196 |

| Е    | 5.8  |      | 6.2  | 0.228  |       | 0.244 |

| е    |      | 1.27 |      |        | 0.050 |       |

| e3   |      | 3.81 |      |        | 0.150 |       |

| F    | 3.8  |      | 4.0  | 0.14   |       | 0.157 |

| L    | 0.4  |      | 1.27 | 0.015  |       | 0.050 |

| М    |      |      | 0.6  |        |       | 0.023 |

### SO-8 MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. © The ST logo is a registered trademark of STMicroelectronics

© 2003 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

© http://www.st.com