ISSUE 7

S/UNI-622-POS DATASHEET ERRATA

# PM5357

# **S/UNI-622-POS**

# SATURN USER NETWORK INTERFACE (622-POS)

# **ERRATA**

**ISSUE 7: APRIL 2000**

ISSUE 7

ERRATA PMC-1990256

S/UNI-622-POS DATASHEET ERRATA

## **REVISION HISTORY**

| Issue<br>No. | Issue Date        | Details of Change                                                                                       |

|--------------|-------------------|---------------------------------------------------------------------------------------------------------|

| 7            | April, 2000       | This document contains errata information corresponding to the issue 4 datasheet and device revision E. |

| 6            | February,<br>2000 | This document contains errata information corresponding to the issue 4 datasheet and device revision D. |

| 5            | December<br>1999  | This document contains errata information corresponding to the issue 3 datasheet and device revision D. |

| 4            | September<br>1999 | This document contains errata information corresponding to the issue 3 datasheet and device revision B. |

| 3            | June 1999         | This document contains errata information corresponding to the issue 3 datasheet and device revision B. |

| 2            | Mar 1999          | This document contains errata information corresponding to the issue 3 datasheet and device revision A. |

| 1            | Feb 1999          | This document contains errata information corresponding to the issue 3 datasheet and device revision A. |

ERRATA PMC-1990256

ISSUE 7 S/UNI-622-POS DATASHEET ERRATA

## **CONTENTS**

| 1 | ISSUE 7 ERRATA                         |                                                                              |     |  |

|---|----------------------------------------|------------------------------------------------------------------------------|-----|--|

|   | 1.1                                    | DEVICE IDENTIFICATION                                                        | 1   |  |

| 2 | DATASHEET DOCUMETNATION DISCREPANCIES: |                                                                              |     |  |

|   | 2.1                                    | POWER SUPPLY FILTERING MECHANICAL DRAWING INCORRECT (PG. 339, SECTION 13.14) | 2   |  |

|   | 2.2                                    | DATASHEET REVISION HISTORY MISSING                                           | . 3 |  |

|   | 2.3                                    | PECL INTERFACE RESISTOR VALUE INCORRECT (SECTION 13.14):                     | 4   |  |

ISSUE 7 S/UNI-622-POS DATASHEET ERRATA

#### 1 ISSUE 7 ERRATA

This issue 7 contains errata applied to the PMC-980911 S/UNI-622-POS Issue 4 datasheet and to Revision E of the device. The issue 4 datasheet and issue 7 errata supersede all prior editions and versions.

#### 1.1 Device Identification

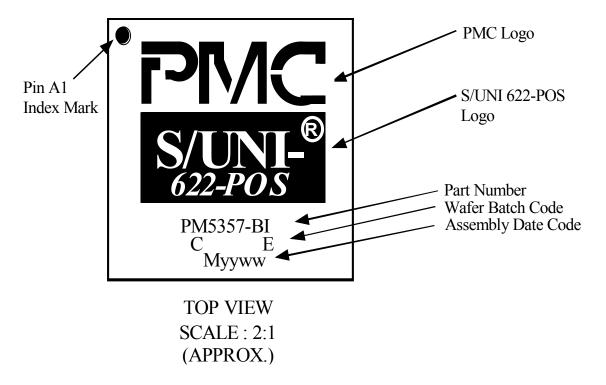

The information contains in this document applies to the PM5357 S/UNI-622-POS revision E device only. The device revision code is marked at the end of the Wafer Batch Code on the face of the device (as shown in Figure 1). PM5357 S/UNI-622-POS revision E is packaged in a 304 pin Super BGA package.

Figure 1: PM5357 S/UNI-622-POS Branding Format

S/UNI-622-POS DATASHEET ERRATA

#### 2 DATASHEET DOCUMETNATION DISCREPANCIES:

ISSUE 7

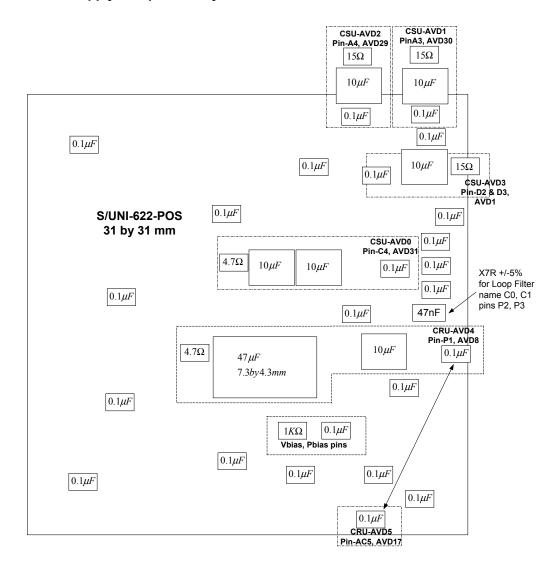

#### 2.1 Power Supply Filtering Mechanical Drawing Incorrect (Pg. 339, Section 13.14)

The loop filter capacitor recommendation specifies a 47nF capacitor not a X7R 47uF capacitor as shown in the datasheet. The correct figure is shown below:

#### **Power Supply Component Layout**

S/UNI-622-POS DATASHEET ERRATA

## **Datasheet Revision History Missing**

The datasheet is missing a revision history.

ISSUE 7

| ISSUE | DATE      | DETAIL                                                                                                                                                                                                       |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4     | Dec, 1999 | #1. Modified section 9.5 (UTOPIA and POS-PHY pin description) and section 14.4 (Functional timing) to reflect operation of the RPA signal (Receive POS-PHY L2 operation requires data be qualified by RVAL). |

|       |           | #2 DC characteristics update (Section 16)                                                                                                                                                                    |

|       |           | #3 Registers updated with correct defaults and descriptions:                                                                                                                                                 |

|       |           | Register 0X01, Bit 4 (TFPEN), Defaults To 1, Not 0                                                                                                                                                           |

|       |           | Register 0X08, Description Incorrect                                                                                                                                                                         |

|       |           | Register 0X09 Description Incorrect                                                                                                                                                                          |

|       |           | Register 0XC1, Bit 1 (DSCR), Defaults To 1, Not 0                                                                                                                                                            |

|       |           | Register 0XC4, Bit 3 (TPAHWM), Defaults To 0, Not 1                                                                                                                                                          |

|       |           | New Register 0XFC: Concatenation Status And Enable                                                                                                                                                           |

|       |           | New Register 0XFD: Concatenation Interrupt Status                                                                                                                                                            |

|       |           | New Register Bit Required For OC-3 Operation (Register 0X07)                                                                                                                                                 |

|       |           | Register 0X5E Bit 5 (RTYPE) To Enable LAN Or WAN Performance                                                                                                                                                 |

|       |           | Register 0X00 Type Bits Incorrect                                                                                                                                                                            |

|       |           | Loss Of Multi-frame Tributary AIS (LOMTUAIS) Bit 2 Incorrectly Stated In Register 0X0D                                                                                                                       |

|       |           | #4 APS pin description modified                                                                                                                                                                              |

|       |           | #5 Documented overflowing Transmit FIFO                                                                                                                                                                      |

|       |           | #6 Updated TFCLK timing specifications, RFCLK timing specifications                                                                                                                                          |

|       |           |                                                                                                                                                                                                              |

**ERRATA** PMC-1990256

ISSUE 7

S/UNI-622-POS DATASHEET ERRATA

| ISSUE | DATE         | DETAIL                                                                                                         |

|-------|--------------|----------------------------------------------------------------------------------------------------------------|

|       |              | #7 Diagnostic Loop-back Clarification                                                                          |

|       |              | #8 Bit Error Rate Monitor Table Update                                                                         |

|       |              | #9 Receive Data Requires 3 RFCLK Cycles Before Becoming Valid (Utopia Level 3 Only)                            |

|       |              | #10 TPAHWM Upper Limit                                                                                         |

|       |              | #11 Receive Line AIS Insertion Is Not Gated By ALLONES                                                         |

|       |              | #12 Large Power Supply Glitch (Beyond Specification) Can Cause Clock Synthesis Unit To Lose Lock To Reference. |

| 3     | Jan 13, 1999 | Corrected wrong pin number assignments in pin description.                                                     |

| 2     | Dec 12, 1998 | General update in preparation for Issue 2 S/UNI-622-POS                                                        |

| 1     | Mar 30, 1998 | Updated datasheet                                                                                              |

## 2.3 PECL Interface Resistor Value Incorrect (Section 13.14):

The pull down for 3.3V PECL interface is shown as 330 ohm instead of the recommended 150 ohm.

ERRATA PMC-1990256

ISSUE 7

S/UNI-622-POS DATASHEET ERRATA

#### **CONTACTING PMC-SIERRA, INC.**

Please report any functional discrepancies or datasheet errors to:

PMC-Sierra, Inc. 105-8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000

Fax: (604) 415-6200

Document Information: document@pmc-sierra.com info@pmc-sierra.com

Application Information: apps@pmc-sierra.com

(604) 415-4533

Web Site: <a href="http://www.pmc-sierra.com">http://www.pmc-sierra.com</a>

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

© 1999,2000 PMC-Sierra, Inc.

PMC-1990256 (R7) ref PMC-1980911 (R4) Issue date: April, 2000