REFERENCE DESIGN REV. 2.0 PMC - 981210 PMC-Sierra, Inc.

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

PM4351 COMET

# PM4351

# COMET

# **COMET REFERENCE DESIGN REV. 2.0**

ADVANCED ISSUE 1: NOVEMBER 1998

i

REFERENCE DESIGN REV. 2.0 PMC - 981210

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

# CONTENTS

| 1 | FEATURES1   |                                                |  |  |

|---|-------------|------------------------------------------------|--|--|

| 2 | OVERVIEW2   |                                                |  |  |

|   | 2.1         | APPLICATIONS                                   |  |  |

| 3 | FUN         | CTIONAL DESCRIPTION6                           |  |  |

|   | 3.1         | COMET                                          |  |  |

|   | 3.2         | MT90810 FLEXIBLE MVIP INTERFACE CIRCUIT (FMIC) |  |  |

|   | 3.3         | BUS TRANSCEIVER9                               |  |  |

|   | 3.4         | OSCILLATORS9                                   |  |  |

|   | 3.5         | TRANSMIT AND RECEIVE LINE INTERFACE            |  |  |

|   | 3.6         | POWER SUPPLY9                                  |  |  |

|   | 3.7         | MVIP BUS CONNECTOR10                           |  |  |

|   | 3.8         | MICROPROCESSOR INTERFACE CONNECTOR11           |  |  |

| 4 | IMPL        | EMENTATION DESCRIPTION13                       |  |  |

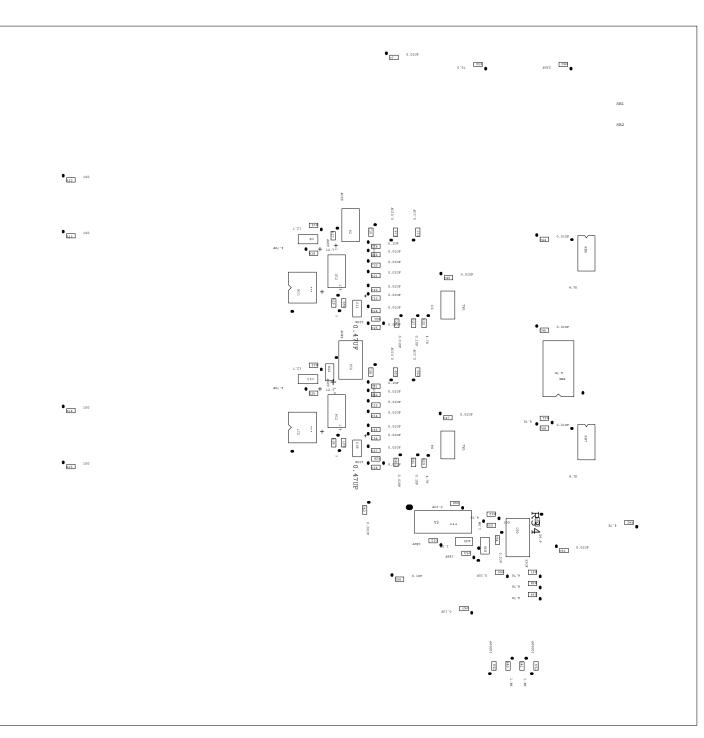

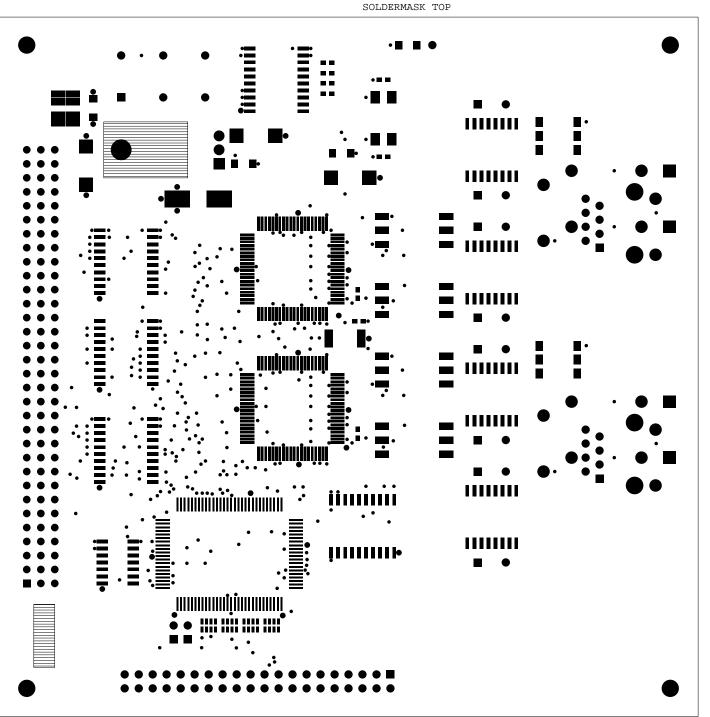

|   | 4.1         | ROOT DRAWING, SHEET 113                        |  |  |

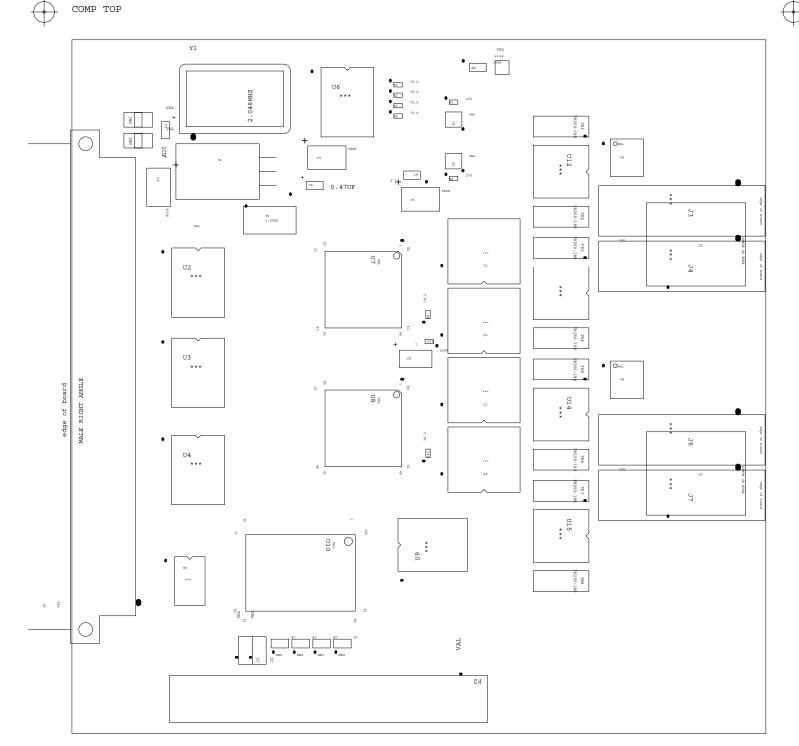

|   | 4.2         | COMET BLOCK, SHEET 2 & 3 13                    |  |  |

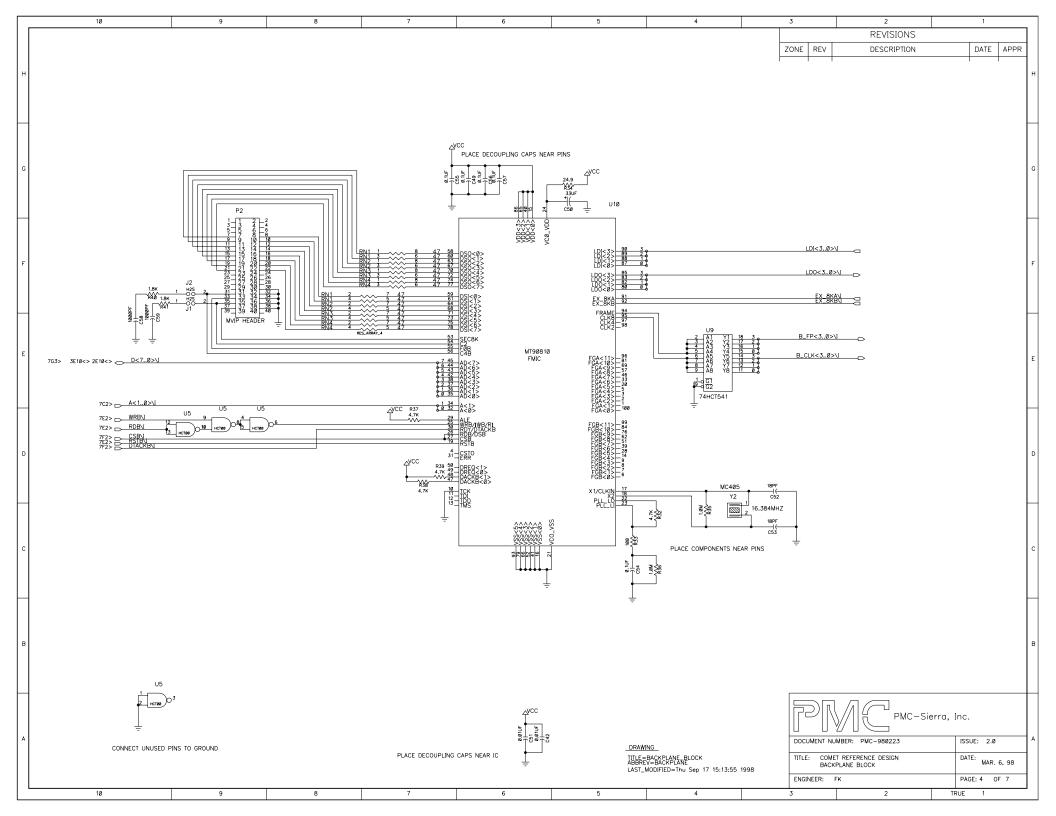

|   | 4.3         | BACKPLANE BLOCK, SHEET 4                       |  |  |

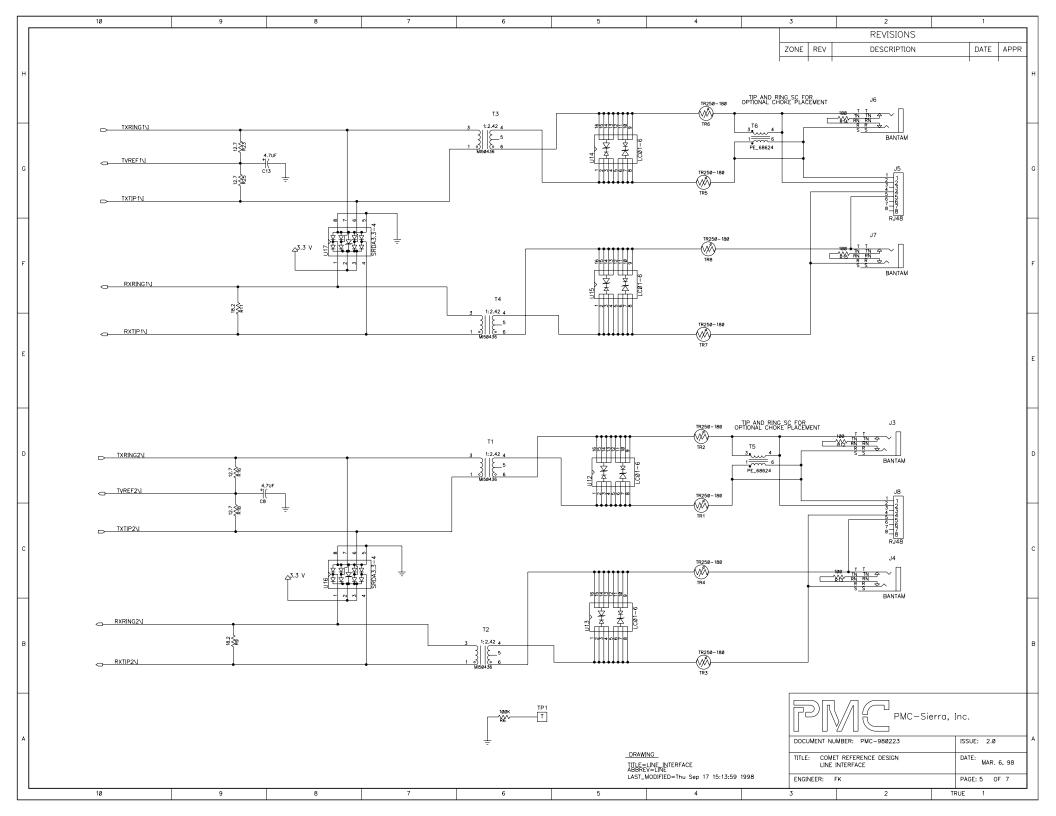

|   | 4.4         | LINE INTERFACE, SHEET 5 13                     |  |  |

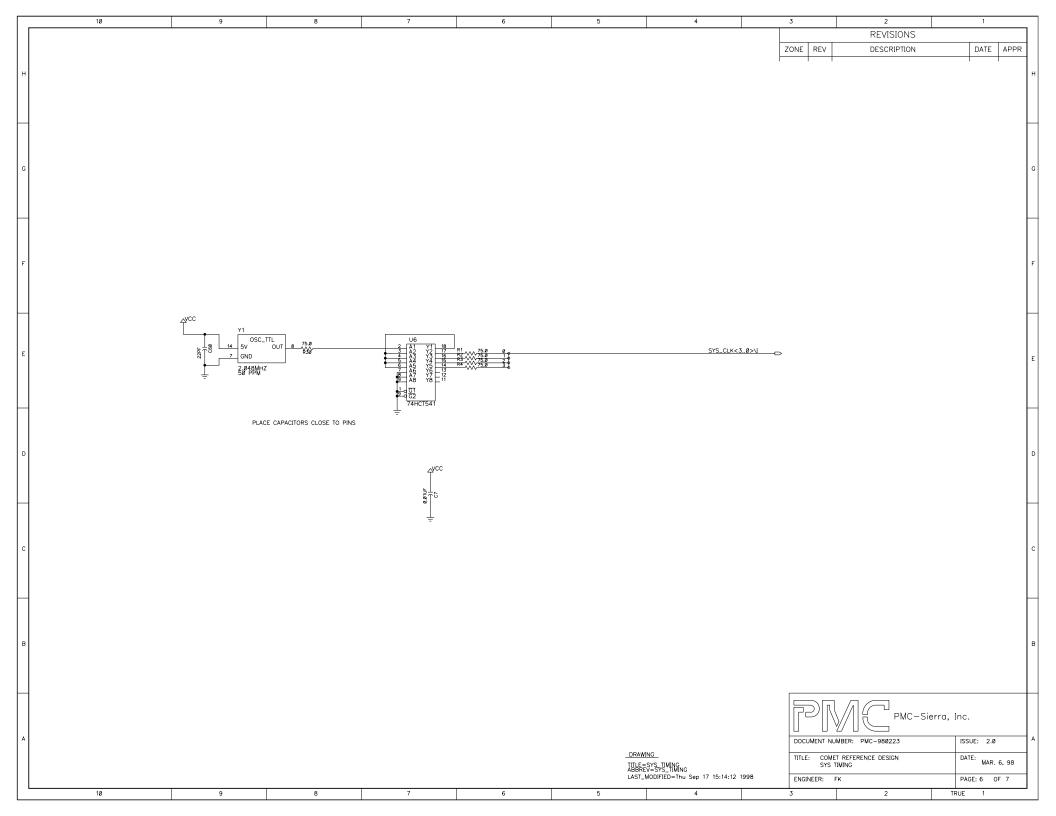

|   | 4.5         | SYS TIMING, SHEET 614                          |  |  |

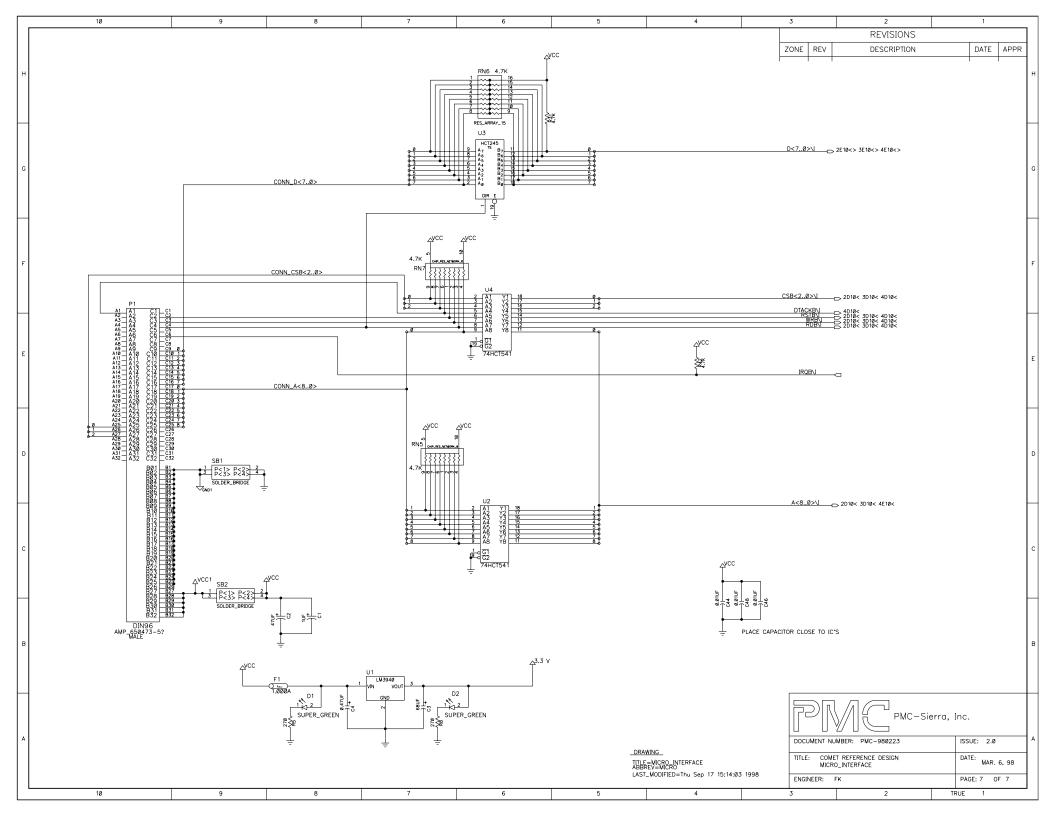

|   | 4.6         | MICRO INTERFACE, SHEET 714                     |  |  |

| 5 | SCHEMATICS1 |                                                |  |  |

| 6 | BILL        | OF MATERIAL16                                  |  |  |

PM4351 COMET

REFERENCE DESIGN REV. 2.0 PMC - 981210

COMET REFERENCE DESIGN REV. 2.0

| 7 | REFERENCES | .20 |

|---|------------|-----|

| 7 | REFERENCES | .2  |

REFERENCE DESIGN REV. 2.0 PMC - 981210

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

# **LIST OF FIGURES**

| FIGURE 1: COMET REFERENCE SYSTEM | 2 |

|----------------------------------|---|

| FIGURE 2: WIRELESS APPLICATION   | 4 |

| FIGURE 3: MVIP BUS ARCHITECURE   | 5 |

| FIGURE 4: BLOCK DIAGRAM          | 6 |

REFERENCE DESIGN REV. 2.0 PMC - 981210

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

# LIST OF TABLES

| TABLE 1 : MVIP BUS CONNECTOR PIN ASSIGNMENTS | 10 |

|----------------------------------------------|----|

| TABLE 2 : MICROPROCESSOR INTERFACE CONNECTOR | 11 |

| TABLE 3 : MAJOR COMPONENTS LIST              | 16 |

REFERENCE DESIGN REV. 2.0 PMC - 981210 PMC PMC-Sierra, Inc.

PM4351 COMET

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

#### 1 FEATURES

- A complete reference design of a dual channel, T1/E1/J1 switch card with an MVIP (Multi-Vendor Integration Protocol) interface.

- Two ports, each using a COMET device, provide framing and, line interface circuitry for short haul and long haul T1, E1, and J1 transmission rates.

- Provides a platform for the demonstration of the COMET's functions and performance.

- Provides a microprocessor Interface to Applied Telecom Evaluation motherboard (EP-CTL). The software drivers include the basic drivers available from PMC-Sierra and the Telecom Application Package (TAP) available from Applied Telecom. A GUI interface is provided for ease of operation.

- Provides a platform for V5.1/5.2 applications with third party application software.

- Provides a platform for ETS 300-011 E1 homologation and T1 testing to ANSI T1.403.

- Provides fractional N\*DS0 backplane rates.

- Provides software-selectable E1, T1, J1 rate selection.

- Provides software-selectable backplane timing selection.

- Provides a programmable PRBS test patter generator, receiver and analyzer.

- Demonstrates protection circuitry that meets both ETS 300 046 and FCC part 68.

REFERENCE DESIGN REV. 2.0 PMC - 981210

COMET REFERENCE DESIGN REV. 2.0

# 2 OVERVIEW

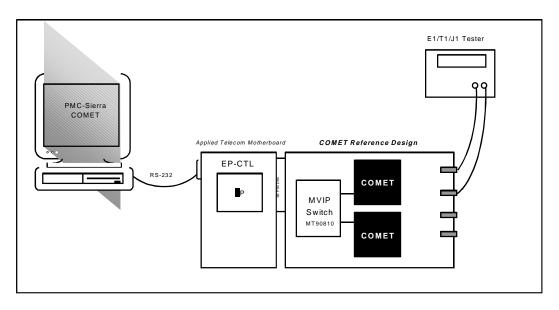

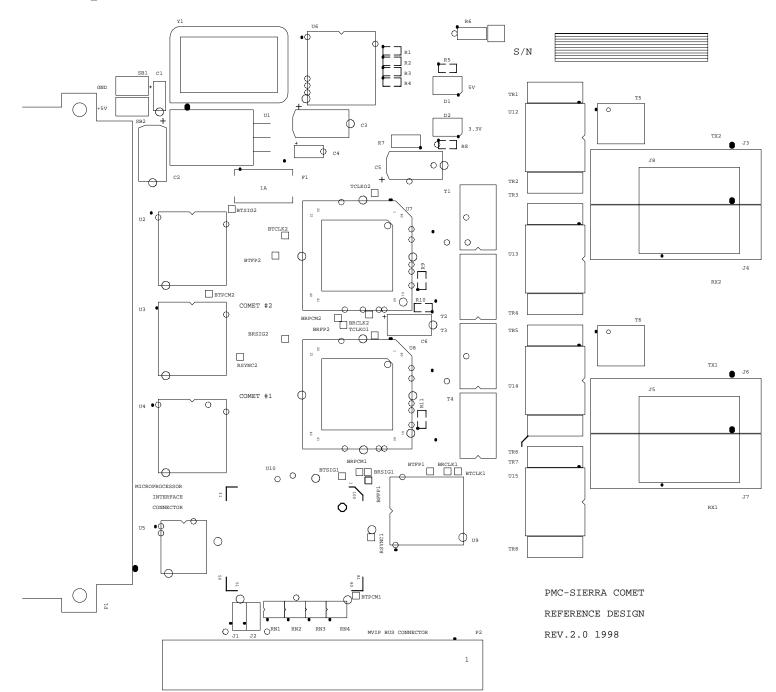

The COMET reference design allows for the evaluation and demonstration of the PMC-Sierra PM4351 COMET device. This reference design illustrates how to implement a dual channel, T1/E1/J1 switch card, with an MVIP interface, using two COMET devices. This board is designed to interface with an Applied Telecom evaluator module (EP-CTL) to form a complete reference design. A graphical user interface, along with the COMET software drivers, are provided for operation of the reference design. Software is also provided for operation of the Mitel 8986 digital switch. All required decoding logic is provided on the COMET reference board to give the Applied Telecom's evaluator module direct access to all registers of both COMET devices. The Applied Telecom evaluator interfaces to a PC directly through an RS-232 connector.

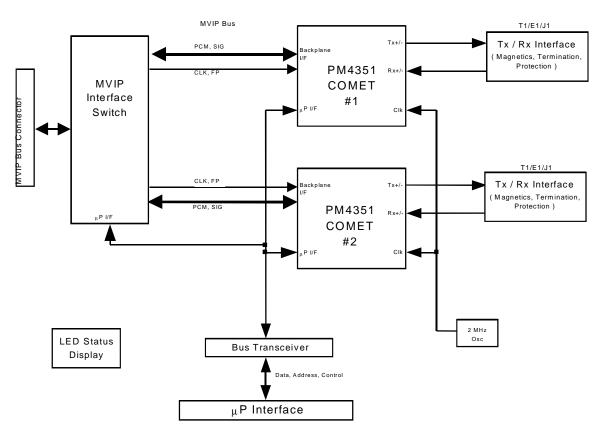

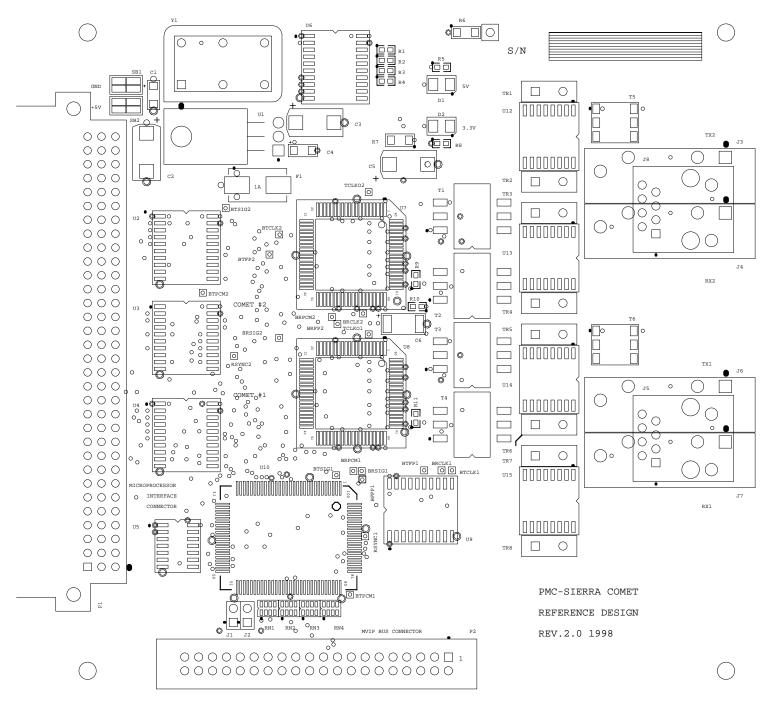

#### Figure 1: COMET Reference System

**ISSUE 1**

The COMET reference design includes two COMET devices, an MVIP bus switch, analog line circuitry and a microprocessor interface to the Applied Telecom Evaluator. The MVIP standard specifies a common bus interface for network, telephony, voice, and fax device interconnection. The backplane signals from the two COMET devices are connected to a Mitel 8986 Digital Switch for support of distributed switching as defined in MVIP-90 standard. The COMET reference design illustrates the COMET's MVIP compatibility. MVIP-90 specifies that for a MVIP switching compatible board, the switch must be capable of making full-duplex connections and of connecting any incoming network channel

PM4351 COMET

COMET REFERENCE DESIGN REV. 2.0

to some sub-set of the MVIP bus time-slots, together with the ability to drive any outgoing network channel from some set of MVIP time-slots.

The COMET reference design, together with the ATI Evaluation Motherboard, can be used to demonstrate V5.1/V5.2 applications. The ATI Evaluation Motherboard and Application Program Interface (API) provide access to COMET's three HDLC controllers for data processing. Investigations on software tools for V5.1/V5.2 applications for the demonstration of protocol handling and system management are now underway.

The COMET reference design board is configured, monitored, and powered through an edge connector that is designed to mate with an Applied Telecom evaluator module. Software drivers and API are available from Applied Telecom to fully control and utilize the COMET reference design.

# 2.1 Applications

The COMET reference design is suitable in the following applications

- T1/E1 Wireless Cellular Base Transceiver Stations (BTS)

- T1/E1 Internet Access Equipment

- T1/E1 Channel Service Units (CSU)

- V5.1/V5.2 Interface Applications

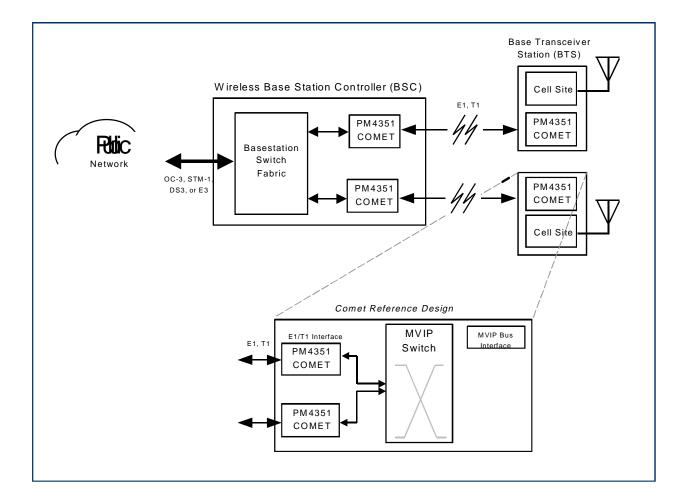

Figure 2 illustrates the COMET reference design in a wireless base transceiver station (BTS) application. The COMET reference design represents a line card which processes the incoming and outgoing E1 or T1 data signal in a MVIP system. The backplane data signal are input into the MVIP switch and can be switched on a DS0 time slot basis. Since the MVIP switch does not provide a multiplexer/demultiplexer function, an external multiplexer/demultiplexer is needed to transfer 64Kbps data from and to the cell site. The MVIP bus data rates can be set to 2.048, 4.096 or 8.192 Mbps depending on the application.

REFERENCE DESIGN REV. 2.0 PMC - 981210

ISSUE 1

# Figure 2: Wireless Application

PMC-Sierra, Inc.

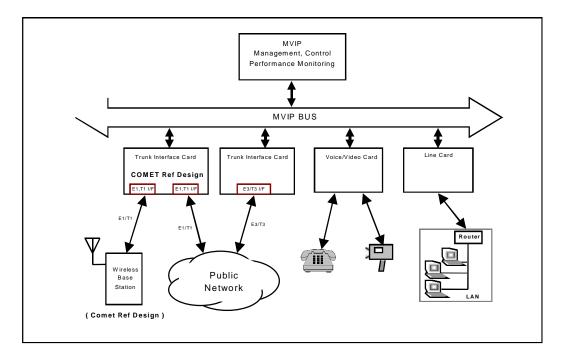

Figure 3 shows a MVIP bus switching system architecture. The COMET reference board can be used to interface to a BTS or to the public network at T1, E1, or J1 data rates.

COMET REFERENCE DESIGN REV. 2.0

PMC - 981210

**REFERENCE DESIGN REV. 2.0**

PMC PMC-Sierra, Inc.

PM4351 COMET

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

# Figure 3: MVIP Bus Architecure

REFERENCE DESIGN REV. 2.0 PMC - 981210

PM4351 COMET

COMET REFERENCE DESIGN REV. 2.0

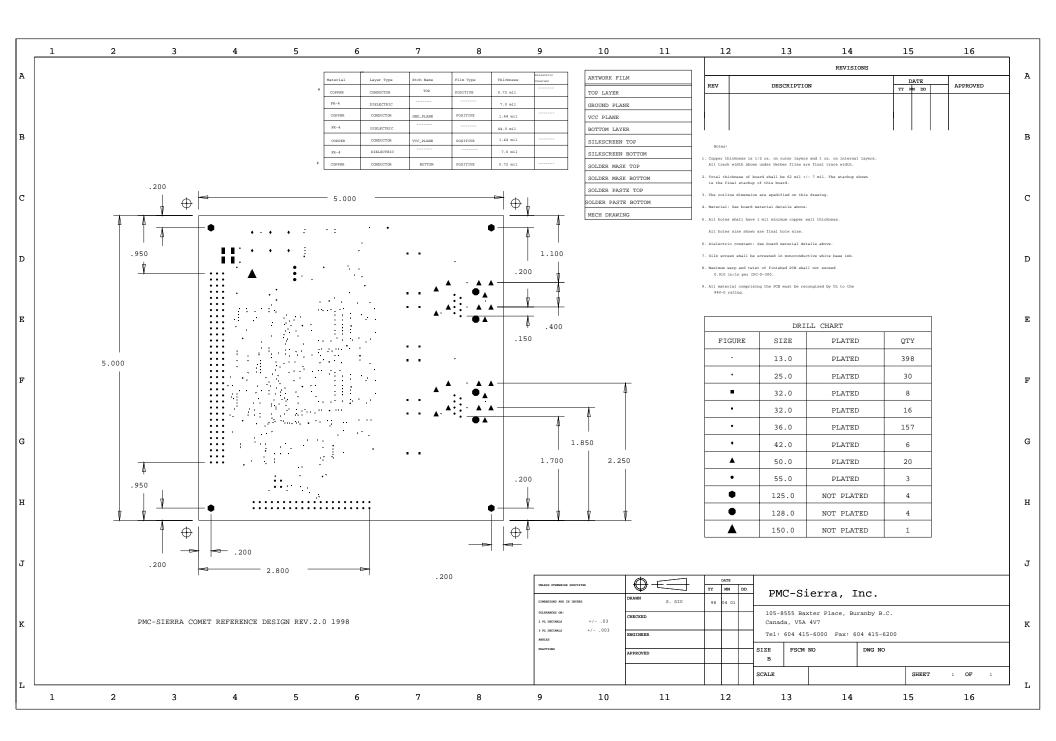

# 3 FUNCTIONAL DESCRIPTION

**ISSUE 1**

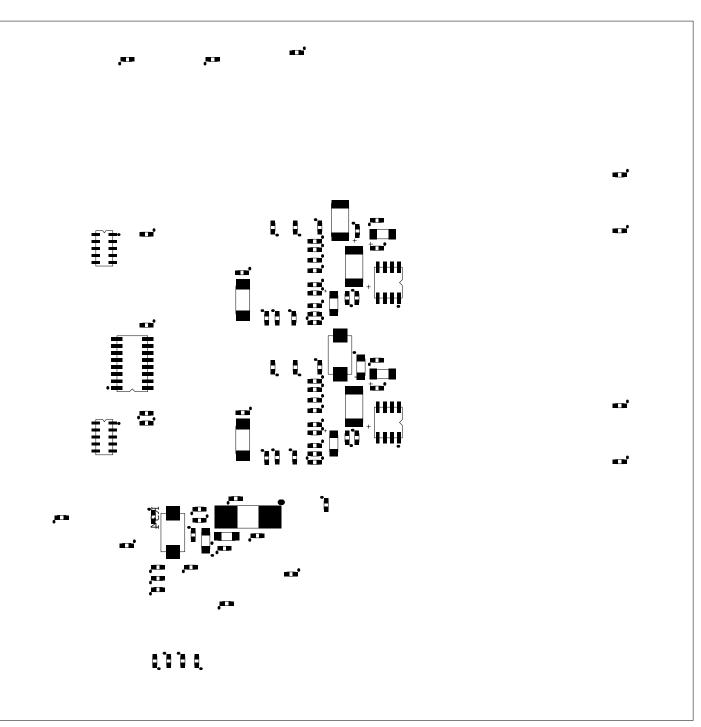

#### Figure 4: Block Diagram

#### 3.1 COMET

The PM4351 Combined E1/T1/J1 Transceiver (COMET) is a feature-rich monolithic integrated circuit suitable for use in long haul and short haul T1, E1, and J1 systems with a minimum of external circuitry. The COMET is software configurable, allowing feature selection without changes to external wiring.

Analog circuitry is provided to allow direct reception of long haul E1 and T1 compatible signals with up to 43 dB cable loss (at 1.024 MHz in E1 mode) or up to 36 dB cable loss (at 772 kHz in T1 mode) using a minimum of external components. Typically, only line protection, a transformer and a line termination resistor are required. Digital line inputs are provided for applications not requiring a physical T1 or E1 interface.

REFERENCE DESIGN REV. 2.0 PMC - 981210

PM4351 COMET

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

The COMET recovers clock and data from the line and frames to incoming data. In T1 mode, it can frame to several DS-1 signal formats: SF, ESF, T1DM (DDS) and SLC®96. In E1 mode, the COMET frames to basic G.704 E1 signals and CRC-4 multiframe alignment signals, and automatically performs the G.706 interworking procedure. AMI, HDB3 and B8ZS line codes are supported.

The COMET supports detection of various alarm conditions such as loss of signal, pulse density violation, Red alarm, Yellow alarm, and AIS alarm in T1 mode and loss of signal, loss of frame, loss of signaling multiframe and loss of CRC multiframe in E1 mode. The COMET also supports reception of remote alarm signal, remote multiframe alarm signal, alarm indication signal, and time slot 16 alarm indication signal in E1 mode. The presence of Yellow and AIS patterns in T1 mode and remote alarm and AIS patterns in E1 mode is detected and indicated. In T1 mode, the COMET integrates Yellow, Red, and AIS alarms as per industry specifications. In E1 mode, the COMET integrates Red and AIS alarms.

Performance monitoring with accumulation of CRC-6 errors, framing bit errors, line code violations, and loss of frame events is provided in T1 mode. In E1 mode, CRC-4 errors, far end block errors, framing bit errors, and line code violation are monitored and accumulated.

Dual (transmit and receive) elastic stores for slip buffering and rate adaptation to backplane timing are provided, as is a signaling extractor that supports signaling debounce, signaling freezing, idle code substitution, digital milliwatt tone substitution, data inversion, and signaling bit fixing on a per-channel basis. Receive side data and signaling trunk conditioning is also provided.

In T1 mode, the COMET generates framing for SF, ESF and T1DM (DDS) formats. In E1 mode, the COMET generates framing for a basic G.704 E1 signal. The signaling multiframe alignment structure and the CRC multiframe structure may be optionally inserted. Framing can be optionally disabled.

Internal analog circuitry allows direct transmission of long haul and short haul T1 and E1 compatible signals using a minimum of external components. Typically, only line protection, a transformer and an optional line termination resistor are required. Digitally programmable pulse shaping allows transmission of DSX-1 compatible signals up to 655 feet from the cross-connect, E1 short haul pulses into 120 ohm twisted pair or 75 ohm coaxial cable, E1 long haul pulses into 120 ohm twisted pair as well as long haul DS-1 pulses into 100 ohm twisted pair with integrated support for Line Build Out (LBO) filtering as required by the FCC rules. In addition, the programmable pulse shape extending over 5-bit periods allows customization of short haul and long haul line interface circuits to

PM4351 COMET

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

application requirements. Digital line inputs and outputs are provided for applications not requiring a physical T1 or E1 interface.

In the transmit path, the COMET supports signaling insertion, idle code substitution, digital milliwatt tone substitution, data inversion, and zero code suppression on a per-channel basis. Zero code suppression may be configured to Bell (bit 7), GTE, or DDS standards, and can also be disabled. Transmit side data and signaling trunk conditioning is also provided. Signaling bit transparency from the backplane may be enabled.

The COMET provides three transmit HDLC controllers. These controllers may be used for the transmission of messages on the ESF data link (T1) or national use bits (E1) and in any time slot. In T1 mode, the COMET can be configured to generate in-band loop back codes and ESF bit oriented codes. In E1 mode, transmission of the 4-bit Sa codewords defined in ETSI 300-233 is supported.

The COMET provides optional jitter attenuation in both the transmit and receive directions.

The COMET provides both a parallel microprocessor interface for controlling the operation of the device and serial PCM interfaces that allow backplane rates from 1.544 Mbit/s to 8.192 Mbit/s to be directly supported. Up to four COMET devices can be multiplexed on a byte-interleaved basis on a common bus with no additional arbitration logic. The COMET supports the Mitel ST<sup>®</sup> bus, AT&T CHI<sup>®</sup> and MVIP standards.

For a complete description of the COMET, please refer to PMC-Sierra's COMET databook, PMC-970624.

# 3.2 MT90810 Flexible MVIP Interface Circuit (FMIC)

The Mitel MT90810 FMIC provides a MVIP interface between the MVIP system bus and different variety of processors, telephony and communication interfaces. The MT90810's built-in digital time-slot switch provides MVIP Enhanced Switching between the MVIP system bus and any combination of up to 128 full duplex local channels of 64kb/s each. The MT90810's local serial interface supports PMC rates of 2.048, 4.096, and 8.192 Mb/s.

The MT90810 takes in two 8KHz recovered clocks from the two COMET devices and selects one of the two to generate a 8.192 MHz clock. This 8.192 MHz is synchronized to the selected COMET's receive line. The MT90810 then supplies PMC - 981210

PM4351 COMET

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

the 8 MHz clock to the receive and transmit backplane clocks (BTCLK, BRCLK) of both COMET devices. This ensures the three devices are all synchronized to one clock. The MT90810 also generates a 8KHz frame pulse signal for the two COMET devices.

The MT90810 provides an interface to 4 pairs of input and output local streams. For this reference design, the four local streams include BTPCM, BTSIG, BRPCM, and BRSIG as two stream pairs for each COMET device. The MT90810 is configured and setup through a 8-bit microprocessor interface from the ATI controller motherboard.

#### 3.3 Bus Transceiver

Bus Transceivers are provided at the ATI connector interface to prevent excessive loading of the ATI's Evaluation Motherboard.

#### 3.4 Oscillators

The COMET can run in both T1 or E1 modes. To run in T1 mode, oscillator Y1 should be populated with a 1.544 Mhz oscillator. To run in E1 mode, oscillator Y1 should be populated with a 2.048 Mhz oscillator.

#### 3.5 Transmit and Receive Line Interface

The transmit and receive line interface consists of line connectors, line protection circuitry and magnetics. The reference board provides two types of interface connectors, a mini-bantam and RJ-48C. The RJ48C has been provided according to the ANSI T1.403 standard for a Universal Service Ordering Code (USOC) connector. The line interface provides one termination scheme for both T1 and E1 rates. A termination of  $110\Omega$  is used to allow the interface to be compatible with both T1 and E1. This provides a software switchable reference board for both T1 and E1 by simply configuring the COMET device.

The protection circuitry prevents overvoltage and overcurrent power surge due to lighting strikes or other power impairments, and meets both ETS 300 046 and FCC Part 68 requirements.

#### 3.6 Power Supply

The COMET reference design contains components that operate at either 3.3V or 5V, referenced to the ground. The Applied Telecom's Evaluator provides

PM4351 COMET

COMET REFERENCE DESIGN REV. 2.0

power to the COMET reference board through the edge DIN connector. The 5V power is converted into 3.3V using a DC-DC voltage regulator.

It is recommended that 5.0V power is provided before 3.3V power to avoid latchup in 5.0V tolerant systems. Please refer to the COMET datasheet for further details steps of powering up the COMET device.

# 3.7 MVIP Bus Connector

The MVIP bus connector provides an interface to the MVIP system bus. The MVIP bus consists of sixteen 2.048 Mbit/s serial data streams (DSi0-7 and DSo0-7), clocking, and framing signals. Clocks /C4 and C2 are 4.096 and 2.048 MHz clocks respectively. Frame pulse /F0 is the MVIP 8KHz framing signal. SEC8K is a secondary 8 kHz signal line used to carry 8 kHz timing information derived from trunks on a secondary or subsequent digital trunk interface. The connector is a 20x2 40 pin shroud header.

| Pin<br>Number | Pin Name | Pin<br>Number | Pin Name |

|---------------|----------|---------------|----------|

| 1             | Reserved | 2             | Reserved |

| 3             | Reserved | 4             | Reserved |

| 5             | Reserved | 6             | Reserved |

| 7             | DSo0     | 8             | DSi0     |

| 9             | DSo1     | 10            | DSi1     |

| 11            | DSo2     | 12            | DSi2     |

| 13            | DSo3     | 14            | DSi3     |

| 15            | DSo4     | 16            | DSi4     |

| 17            | DSo5     | 18            | DSi5     |

| 19            | DSo6     | 20            | DSi6     |

| 21            | DSo7     | 22            | DSi7     |

| 23            | Reserved | 24            | Reserved |

| 25            | Reserved | 26            | Reserved |

| 27            | Reserved | 28            | Reserved |

#### Table 1 : MVIP Bus Connector Pin Assignments

ISSUE 1

REFERENCE DESIGN REV. 2.0 PMC - 981210

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

| Pin<br>Number | Pin Name | Pin<br>Number | Pin Name |

|---------------|----------|---------------|----------|

| 29            | Reserved | 30            | Ground   |

| 31            | /C4      | 32            | Ground   |

| 33            | /F0      | 34            | Ground   |

| 35            | C2       | 36            | Ground   |

| 37            | SEC8K    | 38            | Ground   |

| 39            | Reserved | 40            | Reserved |

#### 3.8 Microprocessor Interface Connector

The microprocessor interface to Applied Telecom's evaluator is a 96 pin DIN edge connector. Table 1 describes the signals and pin designations of the microprocessor connector.

| Pin<br>Name | Туре  | Pin<br>No. | Function                                                                                                                   |  |

|-------------|-------|------------|----------------------------------------------------------------------------------------------------------------------------|--|

| CS0         | Input | A25        | Chip Select for COMET #1                                                                                                   |  |

| CS1         | Input | A26        | Chip Select for COMET # 2                                                                                                  |  |

| CS2         | Input | A27        | Chip Select for the MVIP Switch                                                                                            |  |

| RSTB        | Input | C2         | Reset Pin for COMET and MVIP Switch<br>RSTB is an active low asynchronous<br>hardware reset                                |  |

| WRB         | Input | C3         | 3 Write Strobe. WRB is an active low signal<br>that asserts during a register write to any of<br>the COMET or MVIP devices |  |

| RDB         | Input | C4         | Read Strobe. RDB is an active low signal<br>that asserts during a register read from any<br>of the COMET or MVIP devices   |  |

#### Table 2 : Microprocessor Interface Connector

PMC - 981210

**REFERENCE DESIGN REV. 2.0**

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

| Pin<br>Name                                                          | Туре              | Pin<br>No.                                                  | Function                                                                                                                                            |

|----------------------------------------------------------------------|-------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE                                                                  | Input             | C5                                                          | Address Latch Enable. ALE is an active high address latch enable and latches the address bus when low.                                              |

| IRQ1B                                                                | Input             | C6                                                          | Interrupt Signal. IRQ1B is active low<br>maskable hardware interrupt. IRQ1B goes<br>low when any of the three devices interrupt<br>source is active |

| D[0]<br>D[1]<br>D[2]<br>D[3]<br>D[4]<br>D[5]<br>D[6]<br>D[7]         | Input /<br>Output | C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16         | Data Bus. D[7:0] is an eight-bit bi-directional data bus used for microprocessor read and write access                                              |

| A[0]<br>A[1]<br>A[2]<br>A[3]<br>A[4]<br>A[5]<br>A[6]<br>A[7]<br>A[8] | Input             | C17<br>C18<br>C19<br>C20<br>C21<br>C22<br>C23<br>C24<br>C25 | Address Bus. A[8:0] is a nine bit address<br>bus that selects specific registers during<br>microprocessor access                                    |

| VCC                                                                  | Power             | B27<br>B28<br>B29<br>B30<br>B31<br>B32                      | +5V Power Supply from the Evaluation<br>Motherboard                                                                                                 |

| Ground                                                               | Power             | B1<br>to<br>B26                                             | Ground                                                                                                                                              |

REFERENCE DESIGN REV. 2.0 PMC - 981210

со

COMET REFERENCE DESIGN REV. 2.0

#### 4 IMPLEMENTATION DESCRIPTION

**ISSUE 1**

The COMET reference design schematics were captured using Cadence software Concept Schematics Capture tool.

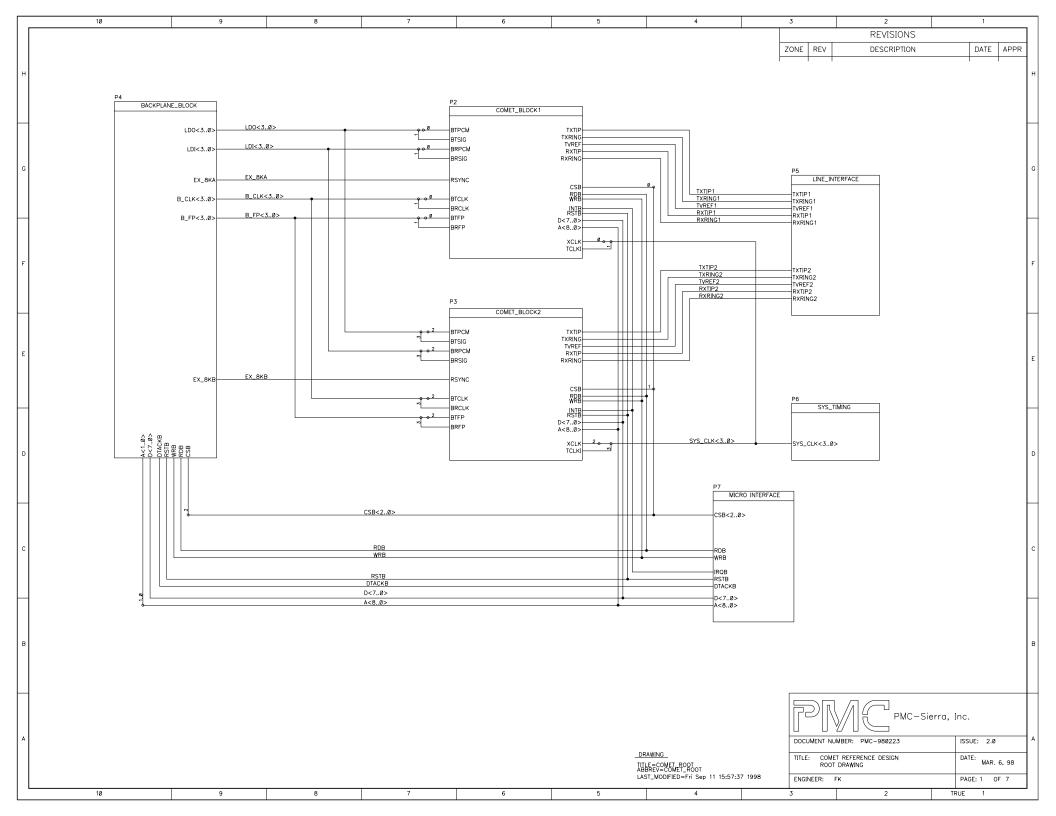

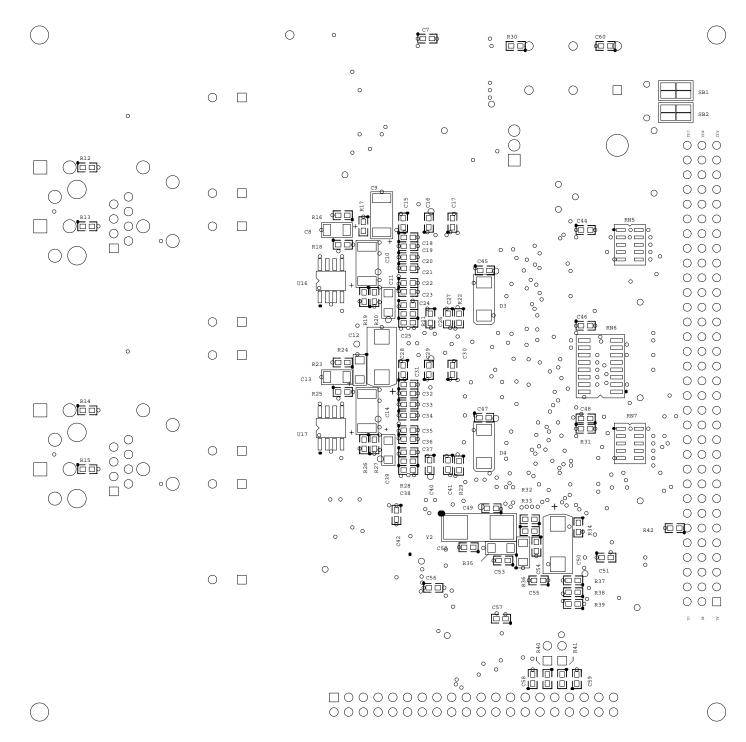

# 4.1 ROOT DRAWING, Sheet 1

This sheet provides an overview of the major functional blocks of the COMET reference design. It shows interconnections between the COMET\_BLOCK1, COMET\_BLOCK2, BACKPLANE\_BLOCK, LINE\_INTERFACE, SYS\_TIMING, and MICRO\_INTERFACE blocks. Groups of signals have been combined into a bus type name format even though these signals are not typically made into buses. This is done to make the schematic less cluttered and more readable and to utilize the capabilities of the schematic capture tool. An example of such signals are the B\_CLK<3..0>, B\_FP<3..0> and SYS\_CLK<3..0>.

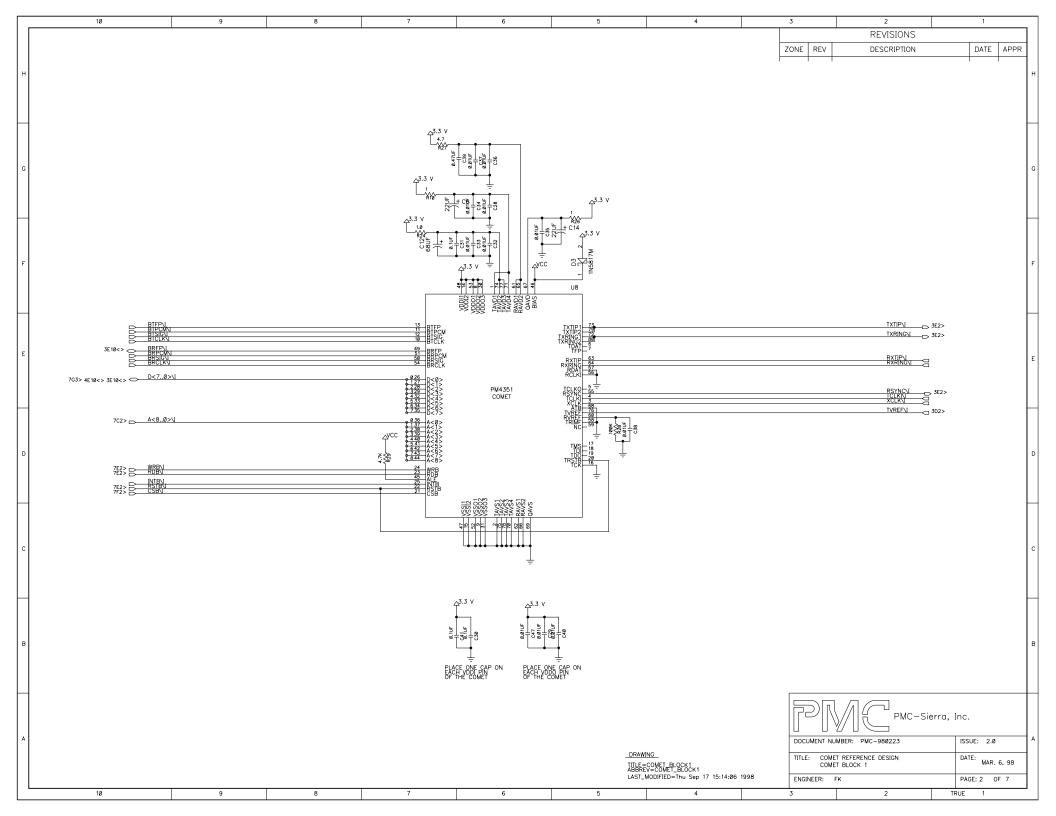

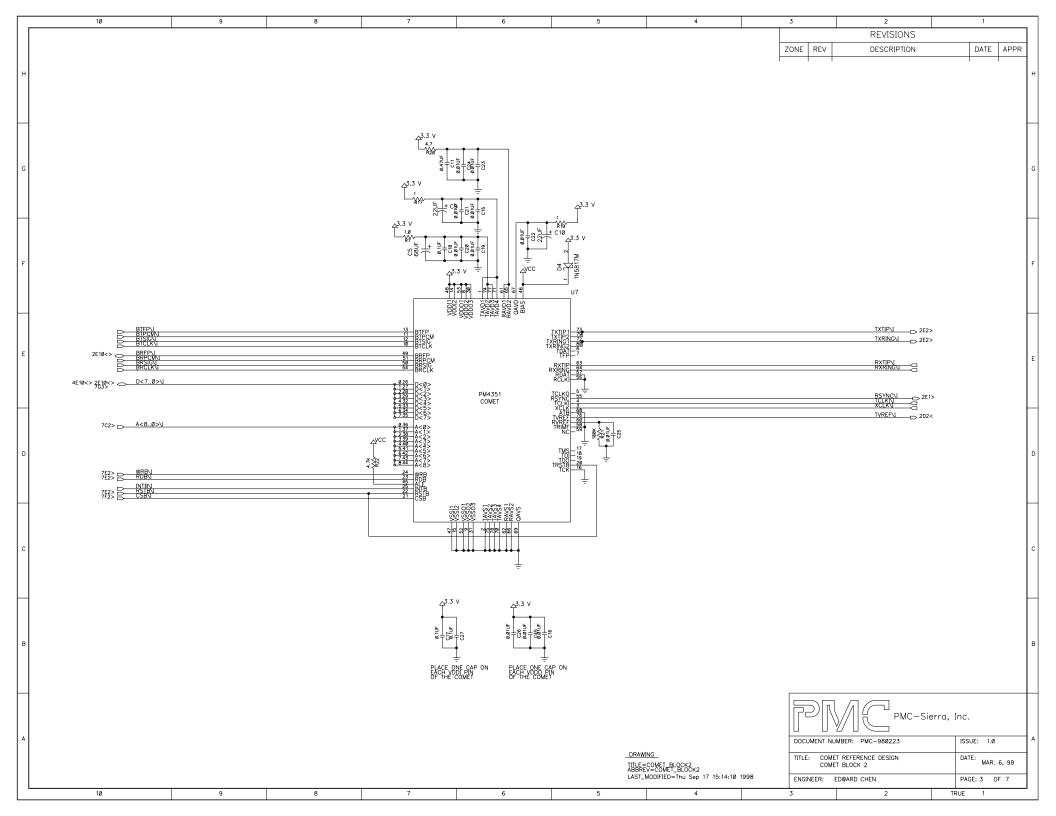

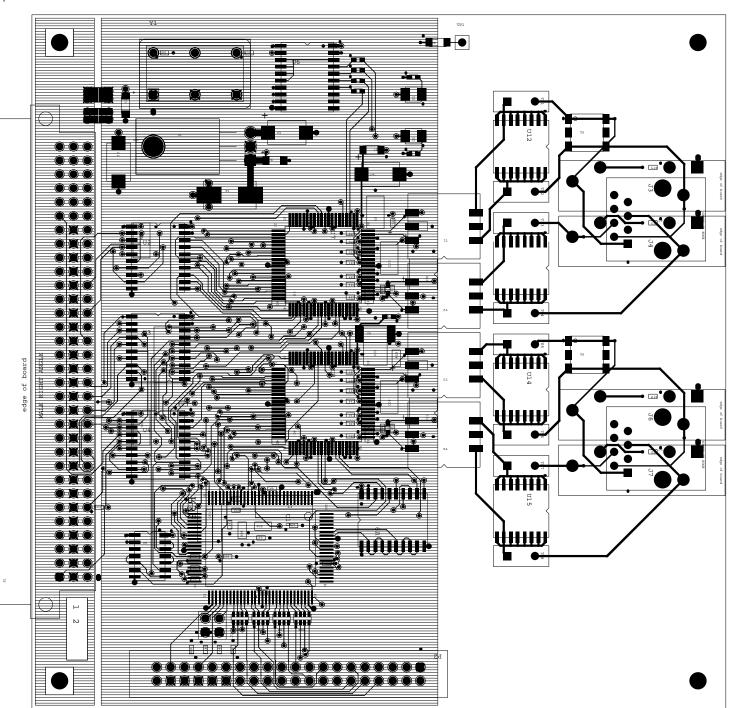

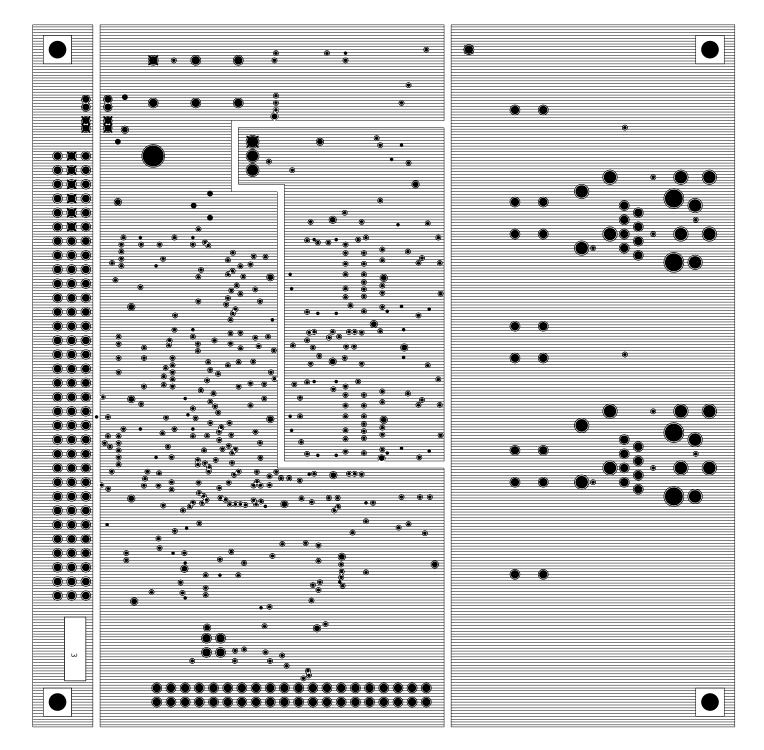

# 4.2 COMET BLOCK, Sheet 2 & 3

This sheet shows the COMET device and its power circuitry. The power circuitry includes a schottky diode for protection while powering up the COMET device and separate filtering circuitry for the analog and digital power pins. The analog power circuitry consists of decoupling capacitors and ferrite beads. For digital power circuitry, ferrite beads are not recommended because of fast CMOS switching of digital I/O's.

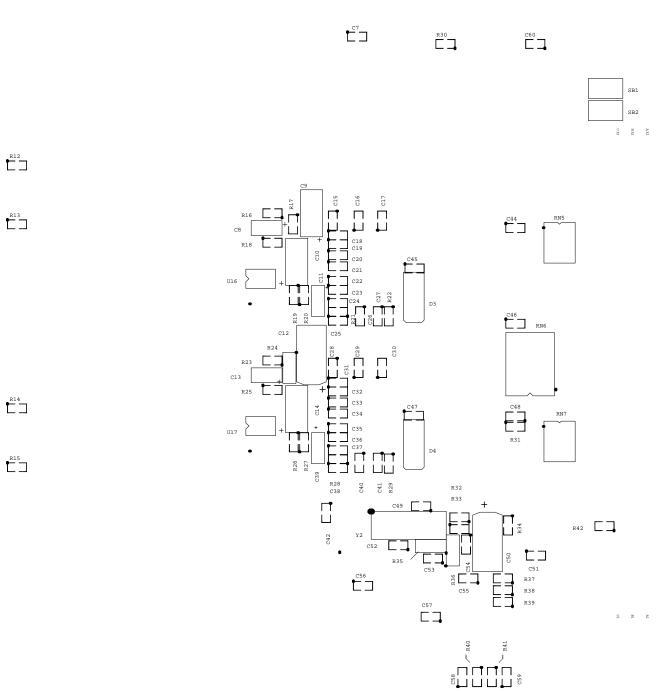

#### 4.3 BACKPLANE BLOCK, Sheet 4

The backplane block schematics shows the MVIP Interface Switch (MT90810) with an external header. A buffer is provided to buffer the clock and frame pulse to the backplane of the two COMET devices. The clock filtering circuitry ensures the correct operation of the PLL inside the MVIP Interface Switch. Jumpers are provided to optional select termination for the C2 and /C4 clock lines. When connecting two COMET reference boards together, the slave COMET board needs to terminate the clock lines. A 20x2 header allows two COMET reference boards to be connected via a ribbon cable.

# 4.4 LINE INTERFACE, Sheet 5

This schematics shows the termination, magnetic and protection circuitry for the line interface. A 1:2.42 transformer is used to couple the COMET transmit and receive line to the connectors. The LC01-6 transient voltage suppressor (TVS)

ADVANCE REFERENCE DESIGN REV. 2.0 PMC - 981210

PM4351 COMET

COMET REFERENCE DESIGN REV. 2.0

and the Raychem PTC provides over voltage protection. A common-mode choke is used on the transmit side for reducing electromagnetic noise. A single footprint is provided for both the bantam and RJ48C connectors.

### 4.5 SYS TIMING, Sheet 6

The 2.048 MHz or 1.544 MHz clock for the two COMET devices is buffered through a 8-bit buffer. The clock lines are series terminated to reduce reflection and bouncing.

# 4.6 MICRO INTERFACE, Sheet 7

This schematics shows the connector to the ATI EP-CTL and buffers for the microprocessor signals. The LM3940 drop-out voltage regulator supplies 3.3V to the two COMET devices. Two LED's are provided to display the status of power supply to the COMET board.

REFERENCE DESIGN REV. 2.0 PMC - 981210

PM4351 COMET

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

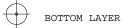

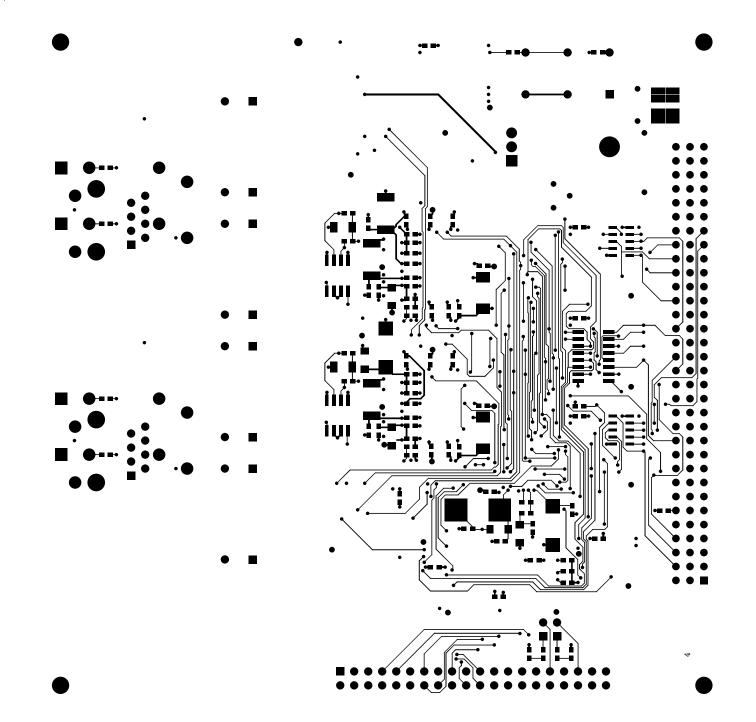

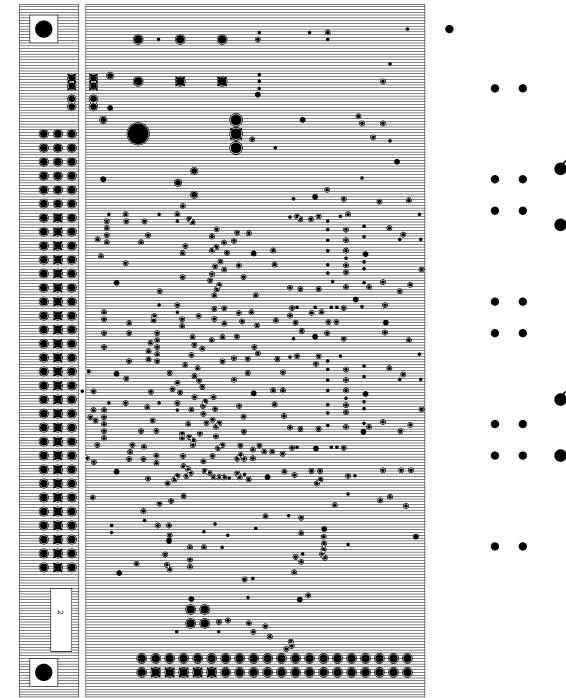

# 5 SCHEMATICS

$\left( + \right)$

$\bigcirc$

$\left( \bullet \right)$

$(\mathbf{+})$

)-

$\bigcirc$

$\left\{ +\right\}$

$\left( + \right)$

$\oplus$

REFERENCE DESIGN REV. 2.0 PMC - 981210

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

## 6 BILL OF MATERIAL

## Table 3 : Major Components List

| Ref. No  | Component                | Manufacturer           | Package Type  | Quantity |

|----------|--------------------------|------------------------|---------------|----------|

| U12-U15  | LC01-6                   | Semtech                | SOIC16        | 4        |

|          |                          | 805-498-2111           |               |          |

| U16, U17 | SRDA3.3-4                | Semtech                | SOIC8         | 2        |

| TR1-TR8  | Thermistor-<br>TR250-180 | Raychem                | RES200        | 8        |

|          |                          | 800-227-7040           |               |          |

| U10      | MT90810                  | Mitel                  | PQFP100       | 1        |

|          |                          | 800-648-3579           |               |          |

| U1       | LM3940                   | National Semiconductor | TO220         | 1        |

|          |                          | 408-721-5000           |               |          |

| P2       | 20x2<br>Connector        | 3M                     | Headers       | 1        |

|          |                          | 800-364-3577           |               |          |

| T1-T4    | MI-50436                 | Midcom                 | RF-trans6_mir | 4        |

|          |                          | 605-886-4385           |               |          |

|          | TG23-<br>1505NS          | Halo Electronics       | SMD 6 pin     |          |

|          |                          | 650-568-6161           |               |          |

|   | Part Name - Value | Part Number  | Jedec Type | Ref Des     | Qty |

|---|-------------------|--------------|------------|-------------|-----|

| 1 | 1N58171N5817M     | 1N5817M      | MLL41      | D3, D4      | 2   |

| 2 | 74HCT00_SOIC-     |              | SOIC14     | U5          | 1   |

|   | 123_XXX XXX       |              |            |             |     |

| 3 | 74HCT245_SOIC-    |              | SOIC20W    | U3          | 1   |

|   | 123_XX XXXX       |              |            |             |     |

| 4 | 74XXX541_SOIC-    | MM74HCT541WM | SOIC20W    | U2, U4, U6, | 4   |

|   | HCT, 74HCT541     |              |            | U9          |     |

PM4351 COMET

REFERENCE DESIGN REV. 2.0 PMC - 981210

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

|    |                                        |                                   | I                       |                                        |    |

|----|----------------------------------------|-----------------------------------|-------------------------|----------------------------------------|----|

| 5  | BANTAM-BASE                            | ELECTRO SONIC<br>PC-834-J-(BLACK) | BANTAM                  | J3, J4, J6, J7                         | 4  |

| 6  | CAPACITOR-<br>0.01UF, 50V,<br>X7R_603  | DIGIKEY<br>PCC103BVCT-ND          | 603                     | C7, C15, C16,<br>C19-C26,<br>C28, C29, | 28 |

|    |                                        |                                   |                         | C32-C38,<br>C40, C42,<br>C44-C48, C51  |    |

| 7  | CAPACITOR-0.1UF,<br>16V, Y5V_603       |                                   |                         | C17, C27,<br>C30, C41                  | 4  |

| 8  | CAPACITOR-0.1UF,<br>25V, Y5V_603       | NEWARK 52F017                     | 603                     | C18, C31,<br>C49, C54-C57              | 7  |

| 9  | CAPACITOR-<br>0.47UF, 25V, TANT<br>TEH | DIGI-KEY<br>PCT5474CT-ND          | SMDTANCAP_A             | C4, C11, C39                           | 3  |

| 10 | CAPACITOR-<br>1000PF, 50V,<br>X7R_0603 | DIGI-KEY<br>PCC102BNCT-NE         | 603                     | C58, C59                               | 2  |

| 11 | CAPACITOR-18PF,<br>50V, NPO_603        | DIGI-KEY<br>PCC180ACVCT-ND        | 603                     | C52, C53                               | 2  |

| 12 | CAPACITOR-1UF,<br>16V, TANT TEH        | DIGI-KEY<br>PCT3105CT-ND          | SMDTANCAP_A             | C1                                     | 1  |

| 13 | CAPACITOR-22PF,<br>16V, Y5V_603        |                                   | 603                     | C60                                    | 1  |

| 14 | CAPACITOR-22UF,<br>6.3V, TANT TEH      | DIGI-KEY<br>PCT1226CT-ND          | SMDTANCAP_C             | C6, C9, C10,<br>C14                    | 4  |

| 15 | CAPACITOR-33UF,<br>16V, TANT TEH       | DIGI-KEY<br>PCT3336CT-ND          | NEC_D                   | C50                                    | 1  |

| 16 |                                        | DIGI-KEY<br>PCT2475CT-ND          | SMDTANCAP_B             | C8, C13                                | 2  |

| 17 | CAPACITOR-47UF,<br>10V, TANT TEH       | DIGI-KEY<br>PCT2476CT-ND          | NEC_D                   | C2                                     | 1  |

| 18 | CAPACITOR-68UF,<br>6.3V, TANT TEH      | DIGI-KEY<br>PCT1686CT-ND          | NEC_D                   | C3, C5, C12                            | 3  |

| 19 | CHIP_RES_NETWO                         |                                   | RN-EXBA                 | RN5, RN7                               | 2  |

| 20 | COMET QFP-BASE                         |                                   | QFP80-1                 | U7, U8                                 | 2  |

| 21 | CON_HEADER_20X<br>2_3M_2 540-BASE      | 3M 2540-6002<br>UG                | HEADER_20X2_<br>3M_2540 | P2                                     | 1  |

| 22 | CRYSTAL_MC405-<br>BASE                 | DIGI-KEY<br>SE2405CT-ND           | CRYS_MC-405             | Y2                                     | 1  |

| 23 |                                        | DIGI-KEY A1254-<br>ND             | AMP_650473-5            | P1                                     | 1  |

PM4351 COMET

REFERENCE DESIGN REV. 2.0 PMC - 981210

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

| 24 | FUSESMD_SOCK                              |                                     | NANO_SMF_SO       | F1                    | 1 |

|----|-------------------------------------------|-------------------------------------|-------------------|-----------------------|---|

| 05 | ,                                         | F1222CT-ND                          |                   | 14 10                 | 0 |

|    | HEADER2S_100<br>MIL-BASE                  | DIGI-KEY S1011-<br>36-ND            | JUMPER2           | J1, J2                | 2 |

| 26 | LC01_6_SMD-BASE                           | SEMTECH LC01-<br>6                  | SOIC16WB          | U12-U15               | 4 |

| 27 | LED-<br>SUPER_GREEN,<br>SURFACE MOUNT     | NEWARK<br>95F9373                   | LED_11            | D1, D2                | 2 |

| 28 | LM3940_TO220-<br>BASE                     | LM3940IT-3.3                        | TO220ABH          | U1                    | 1 |

| 29 | MI50436                                   |                                     | RF-TRANS6_MI<br>R | T1-T4                 | 4 |

| 30 | MT90810_PQFP-<br>BASE                     | MT90810AK                           | QFP100-5          | U10                   | 1 |

| 31 | OSC_TTL_DIP-<br>2.048MHZ , 50 PPM,<br>CHA | K1150BA                             | CRYS14            | Y1                    | 1 |

| 32 | PE_68624                                  |                                     | PE_68624          | T5, T6                | 2 |

| 33 | RESISTOR-1, 5%,<br>603                    |                                     | 603               | R10, R17,<br>R19, R26 | 4 |

| 34 | RESISTOR-1.0, 1%, 1206                    | DIGI-KEY<br>P <value>RCT-ND</value> | SMDRES1206        | R7, R24               | 2 |

| 35 | RESISTOR-1.0M,<br>5%, 1206                | DIGI-KEY<br>P <value>ECT-ND</value> | SMDRES1206        | R35, R36              | 2 |

| 36 | RESISTOR-1.8K,<br>5%, 603                 | DIGI-KEY<br>P1.8KGCT-ND             | 603               | R40, R41              | 2 |

| 37 | RESISTOR-100, 5%,<br>603                  |                                     | 603               | R12-R15, R33          | 5 |

| 38 | RESISTOR-100K,<br>1%, 603                 |                                     | 603               | R21, R28              | 2 |

| 39 | RESISTOR-100K,<br>5%, 1206                | DIGI-KEY<br>P <value>ECT-ND</value> | SMDRES1206        | R6                    | 1 |

| 40 | RESISTOR-12.7,<br>1%, 603                 | DIGI-KEY<br>P12.7HCT-ND             | 603               | R16, R18,<br>R23, R25 | 4 |

| 41 | RESISTOR-18.2,<br>1%, 603                 | DIGI-KEY<br>P18.2HCT-ND             | 603               | R9, R11               | 2 |

| 42 | RESISTOR-24.9,<br>1%, 603                 | DIGI-KEY<br>P24.9HCT-ND             | 603               | R34                   | 1 |

| 43 | RESISTOR-270, 5%,<br>603                  | DIGI-KEY<br>P <value>GCT-ND</value> | 603               | R5, R8                | 2 |

| 44 | RESISTOR-4.7, 5%,<br>603                  |                                     | 603               | R20, R27              | 2 |

PMC - 981210

**REFERENCE DESIGN REV. 2.0**

PM4351 COMET

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

| 45 | RESISTOR-4.7K, | DIGI-KEY                    | 603      | R22, R29,    | 8 |

|----|----------------|-----------------------------|----------|--------------|---|

|    | 5%, 603        | P <value>GCT-ND</value>     |          | R31, R32,    |   |

|    |                |                             |          | R37-R39, R42 |   |

| 46 | RESISTOR-75.0, |                             | 603      | R1-R4, R30   | 5 |

|    | 1%, 603        |                             |          |              |   |

| 47 | RES_ARRAY_15_S | DIGI-KEY 766-               | SOIC16   | RN6          | 1 |

|    | MD-4.7 K       | 161-R <value>-ND</value>    |          |              |   |

| 48 | RES_ARRAY_4_SM | DIGI-KEY                    | RN4      | RN1-RN4      | 4 |

|    | D-47           | Y4 <value code="">-</value> |          |              |   |

|    |                | ND                          |          |              |   |

| 49 | RJ48-          | MOLEX 95001-                | RJ48     | J5, J8       | 2 |

|    | MOLEX_95001    | 9841                        |          |              |   |

| 50 | SRDA3_3_4_SMD- | SEMTECH                     | SOIC8    | U16, U17     | 2 |

|    | BASE           | SRDA3_3_4                   |          |              |   |

| 51 | THERMISTOR-    |                             | RES200   | TR1-TR8      | 8 |

|    | TR250-180,     |                             |          |              |   |

|    | RES200         |                             |          |              |   |

| 52 | TST_PT-BASE    | DIGI-KEY S1011-             | TST_PT_1 | TP1          | 1 |

|    |                | 36-ND                       |          |              |   |

REFERENCE DESIGN REV. 2.0 PMC - 981210

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

## 7 REFERENCES

- PMC-Sierra, Inc., PM4351 COMET Data Sheet, Issue 4, April 1998

- GO-MVIP, Inc., MVIP-90 Standard, Release 1.1, October 1994

- Applied Telecom web page: <u>www.apptel.com</u>

- ANSI T1.403-1995 American National Standard for Telecommunications Carrier to Customer Installation DS-1 Metallic Interface Specifications.

- European Telecommunication Standard ETS 300 046 Integrated Services Digital Network (ISDN); Primary rate access – safety and protection

- ETSI Technical Basis for Regulation TBR 13 Business Telecommunications (BTC); 2048 kbit/s digital structured leased lines (D2048S); Attachment requirements for terminal equipment

- ETSI Technical Basis for Regulation TBR 12 Business Telecommunications (BT); Open Network Provision (ONP) technical requirements; 2048 kbit/s digital unstructured leased lines (D2048U); Attachment requirements for terminal equipment interface

- ETSI Technical Basis for Regulation TBR 4 Integrated Services Digital Network (ISDN); Attachment requirements for terminal equipment to connect to an ISDN usin ISDN primary rate access

- Federal Communications Commission code of federal regulations FCC Part 68

REFERENCE DESIGN REV. 2.0 PMC - 981210

PM4351 COMET

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

**NOTES**

REFERENCE DESIGN REV. 2.0 PMC - 981210 PMC PMC-Sierra, Inc.

PM4351 COMET

ISSUE 1

COMET REFERENCE DESIGN REV. 2.0

## **CONTACTING PMC-SIERRA, INC.**

PMC-Sierra, Inc. 105-8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000

Fax: (604) 415-6200

Document Information: Corporate Information: Application Information: Web Site: document@pmc-sierra.com info@pmc-sierra.com apps@pmc-sierra.com http://www.pmc-sierra.com

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

© 1998 PMC-Sierra, Inc.

PM-981210

Issue date: November 1998