### **Preliminary Technical Data**

#### FEATURES

Fixed gain of 29 dB Operation from 2.3 GHz to 2.4 GHz EVM  $\leq$ 3% with 16 QAM OFDMA @ Pout = 25 dBm [3.5V] and @ Pout = 27.5 dBm [5V] Input internally matched to 50  $\Omega$ Power supply: 3.2 V to 5.5 V Quiescent current 130 mA in high power mode 70 mA in low power mode PAE: >20% Multiple operating modes to reduce battery drain Low power mode: 100 mA (Operating) Standby mode: 10 mA Sleep mode: < 1  $\mu$ A

#### **APPLICATIONS**

WiMAX/WiBro Mobile Terminals and CPEs Good performance from 2.5Ghz to 2.7Ghz - See Page 7

#### **GENERAL DESCRIPTION**

The ADL5570 is a high linearity 2.3 GHz to 2.4 GHz power amplifier designed for WiMAX terminals and CPEs using TDD operation at a duty cycle of 50% or lower. With a gain of 29 dB and an output compression point of 31 dBm , it can operate at an output power level up to 26 dBm while maintaining an EVM of  $\leq$ 3% with a supply voltage of 3.5V. PAE is greater than 20% at P<sub>OUT</sub> = 25 dBm with a 3.5V supply voltage.

The ADL5570 RF input is matched on chip and provides an input return loss of less than -10 dB. The open-collector output is externally matched with strip-line and external shunt capacitance.

# 2.3 GHz to 2.4 GHz WiMAX Power Amplifier

# ADL5570

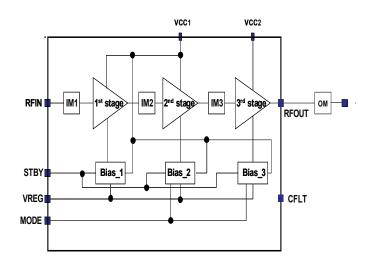

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.AD5570 Block Diagram

The ADL5570 operates over a supply voltage range from 3.2 V to 5.5 V with a supply current of 400mA Burst RMS when delivering 25 dBm (3.5 V supply). A low power mode is also available for operation at power levels  $\leq$ 10 dBm with optimized operating and quiescent currents of 100 and 70 mA, respectively. A Standby mode is available which reduces the quiescent current to 10 mA: useful when a TDD terminal is receiving data.

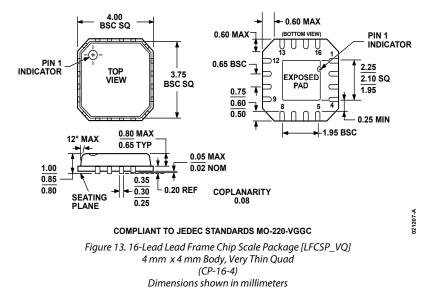

The ADL5570 is fabricated in a GaAs HBT process and is packaged in a 4mm x 4mm 16-Lead Pb-free RoHS compliant LFCSP that uses an exposed paddle for excellent thermal impedance. It operates from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## **Preliminary Technical Data**

### TABLE OF CONTENTS

| Features                            | 1 |

|-------------------------------------|---|

| Applications                        | 1 |

| Functional Block Diagram            | 1 |

| General Description                 | 1 |

| Revision History                    | 2 |

| Target Specifications - VCC = 3.5 V | 3 |

| Target Specifications - Vcc = 5 V   | 4 |

| Pin Configuration and Function Descriptions | 5 |

|---------------------------------------------|---|

| Typical Performance Characteristics         | 6 |

| APPLICATIONS                                | 7 |

| 2.5 GHz to 2.7 Ghz Peformance               | 7 |

| Evaluation Board                            | 8 |

| Outline Dimensions 1                        | 0 |

#### **REVISION HISTORY**

3/07—Rev. PrF: Preliminary Version

### TARGET SPECIFICATIONS - VCC = 3.5 V

T = 25°C, 1024 FFT, 16 QAM OFDMA modulated carrier, 10 MHz Channel BW,  $Z_L = 50 \Omega$ , MODE = 0 V, STBY = 0 V, VREG = 2.85 V, 33% duty cycle, unless otherwise noted.

#### Table 1.

| Parameter              | Conditions                                               | Min Typ Max | Unit  |

|------------------------|----------------------------------------------------------|-------------|-------|

| Frequency Range        | See table 5 for tuning details                           | 2.3 2.4     | GHz   |

| Linear Output Power    | $MODE = 0 V, EVM \le 3\%$                                | 25          | dBm   |

|                        | $MODE = 2.5 \text{ V}, \text{EVM} \le 3\%$               | 10          | dBm   |

| Gain                   |                                                          | 29          | dB    |

| vs. Frequency          | ±5 MHz                                                   | ±0.3        | dB    |

| vs. Temp               | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                | ±0.5        | dB    |

| vs. Supply             | 3.2 V to 4.2 V                                           | ±1          | dB    |

| OP1dB                  | Unmodulated input                                        | 31          | dBm   |

| EVM                    | $P_{OUT} = 25 \text{ dBm}$                               | 3           | % rms |

| Input Return Loss      |                                                          | 10          | dB    |

| Spectral Mask @ 25dBm  |                                                          |             |       |

| Output Power           | ±5 MHz carrier offset                                    | 35          | dBc   |

|                        | ±6 MHz carrier offset                                    | 37          | dBc   |

|                        | ±10.5 MHz carrier offset                                 | 41          | dBc   |

|                        | ±20 MHz carrier offset                                   | 51          | dBc   |

| Harmonic Distortion    |                                                          | 36          | dBc   |

| Power Supply Interface | VCC = 3.5 V                                              |             |       |

| Supply Current         | $P_{OUT} = 25 \text{ dBm}, \text{MODE} = 0 \text{ V}.$   | 250         | mA    |

|                        | $P_{OUT} = 12 \text{ dBm}, \text{MODE} = 2.5 \text{ V}.$ | 100         | mA    |

| PAE                    | $P_{OUT} = 25 \text{ dBm}, \text{MODE} = 0 \text{ V}$    | >20         | %     |

| Standby Mode           | VREG = 2.85 V, STBY = 2.5 V                              | 10          | mA    |

| Sleep Mode             | VREG = 0 V                                               | 10          | μΑ    |

| Turn On/Off Time       |                                                          | 1           | μs    |

| VSWR Survivability     |                                                          | 10:1        |       |

### TARGET SPECIFICATIONS - VCC = 5 V

T = 25°C, 1024 FFT, 16 QAM OFDMA modulated carrier, 10 MHz Channel BW,  $Z_L = 50 \Omega$ , MODE = 0 V, STBY = 0 V, VREG = 2.85 V, 33% duty cycle, unless otherwise noted.

#### Table 2.

| Parameter                             | Conditions                                | Min Typ Max | Unit  |

|---------------------------------------|-------------------------------------------|-------------|-------|

| Frequency Range                       | See table 5 for tuning details            | 2.3 2.4     | GHz   |

| Linear Output Power                   | $MODE = 0 V, EVM \le 3\%$                 | 27.5        | dBm   |

|                                       | MODE = 2.5 V, EVM $\leq$ 3 %              | 10          | dBm   |

| Gain                                  |                                           | 28          | dB    |

| vs. Frequency                         | ±5 MHz                                    | ±0.3        | dB    |

| vs. Temp                              | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$ | ±0.5        | dB    |

| vs. Supply                            | 4.5 V to 5.5 V                            | ±1          | dB    |

| OP1dB                                 | Unmodulated input                         | 32          | dBm   |

| EVM                                   | $P_{OUT} = 27.5 \text{ dBm}$              | 3           | % rms |

| Input Return Loss                     |                                           | 10          | dB    |

| Spectral Mask @ 25dBm<br>Output Power | ±5MHz carrier offset                      | 38          | dBc   |

|                                       | ±6 MHz carrier offset                     | 39          | dBc   |

|                                       | ±10.5 MHz carrier offset                  | 43          | dBc   |

|                                       | ±20 MHz carrier offset                    | 49          | dBc   |

| Harmonic Distortion                   |                                           | 36          | dBc   |

| Power Supply Interface                | VCC = 5 V                                 |             |       |

| Supply Current                        | P <sub>OUT</sub> = 27.5 dBm, MODE = 0 V   | 300         | mA    |

|                                       | P <sub>OUT</sub> = 13 dBm, MODE = 2.5 V   | 115         | mA    |

| PAE                                   | P <sub>OUT</sub> = 27.5 dBm, MODE = 0 V   | 16          | %     |

| Standby Mode                          | VREG = 2.85 V, STBY = 2.5 V               | 10          | mA    |

| Sleep Mode                            | VREG = 0 V                                | 10          | μΑ    |

| Turn On/Off Time                      |                                           | 1           | μs    |

| VSWR Survivability                    |                                           | 10:1        |       |

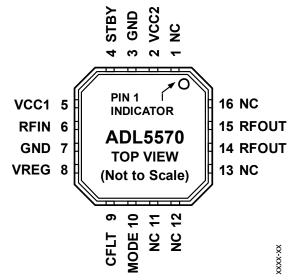

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. ADL5570 Pin Configuration

#### Table 3. Pin Function Descriptions

| Pin No.         | Mnemonic          | Description                                                                                                                                                                                                                   |

|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5               | VCC1              | Connect to Power Supply.                                                                                                                                                                                                      |

| 6               | RFIN              | Matched RF Input.                                                                                                                                                                                                             |

| 8               | VREG              | When VREG is low, the device goes into sleep mode, reducing supply current to 1 uA. When VREG is high (2.85 V), the device operates in its normal transmit mode. When high, VREG draws a bias current of approximately 10 mA. |

| 9               | CFLT              | A Ground Referenced Capacitor. It should be connected to this node to reduce bias line noise (see figure 8).                                                                                                                  |

| 10              | MODE              | Switches Between High Power and Low Power Modes. When MODE is low (0 V), the device operates in high power mode. When MODE is high (2.5 V), the device operates in low power mode.                                            |

| 14, 15          | RFOUT             | Unmatched RF Output. These parallel outputs can be matched to 50 $\Omega$ using strip-line and shunt capacitance. The power supply voltage should be connected to these pins through a choke inductor.                        |

| 2               | VCC2              | This power supply pin should be connected to the supply via a choke circuit (see Figure 8).                                                                                                                                   |

| 4               | STBY              | When STBY is low (0 V), the device operates in transmit mode. When the radio is receiving data, STBY can be taken high (2.5 V), reducing supply current to 10 mA.                                                             |

| 1, 11 to 13, 16 | N/C               | No Connect. Do not connect these pins.                                                                                                                                                                                        |

| 7               | GND               | Connected to Ground.                                                                                                                                                                                                          |

|                 | Exposed<br>Paddle | The exposed paddle should be soldered down to a low impedance ground plane (use multiple vias (at least 9) to stitch together the ground planes) for optimum electrical and thermal performance.                              |

#### Table 4. Operating Modes<sup>1</sup>

| Mnemonic | Normal Operation | Low Power Mode, POUT ≤ 10dBm | Standby Mode | Sleep Mode |

|----------|------------------|------------------------------|--------------|------------|

| VREG     | High             | High                         | High         | Low        |

| MODE     | Low              | High                         | Х            | Х          |

| STBY     | Low              | Low                          | High         | Х          |

$^{1}$  X = don't care.

### ADL5570

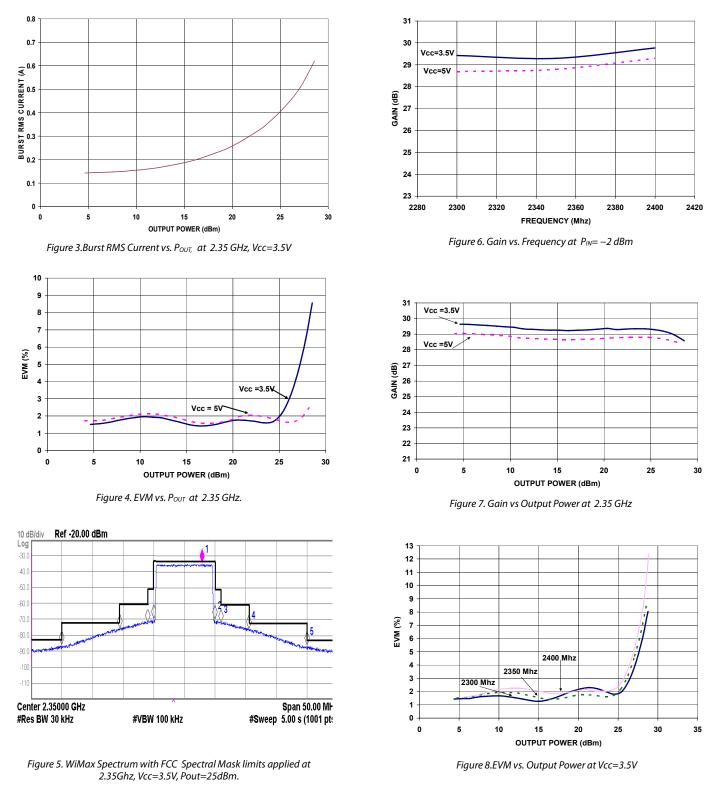

### **TYPICAL PERFORMANCE CHARACTERISTICS**

T = 25°C, 1024 FFT, 16 QAM OFDMA modulated carrier, 10 MHz Channel BW,  $Z_L = 50 \Omega$ , MODE = 0 V, STBY = 0 V, VREG = 2.85 V, 33% duty cycle, unless otherwise noted.

### APPLICATIONS

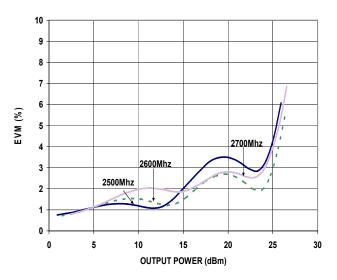

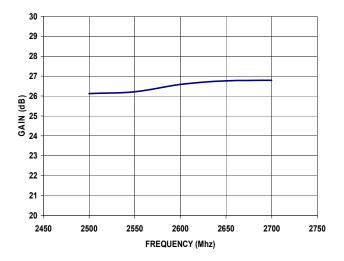

#### 2.5 GHZ TO 2.7 GHZ PEFORMANCE

The ADL5570 is optimized for superior performance within the 2.3 GHz to 2.4 GHz frequency band. With a change in the external matching capacitor, C3, to 2.4 pF, the ADL5570 shows good performance in the 2.5 GHz to 2.7 GHz frequency band. The EVM, Gain and RMS current performance data are shown in Figure 9 and Figure 10.

Figure 9. EVM vs Output power Perfomance at Vcc=3.5V and 16QAM OFDMA Signal

Figure 10. Gain vs Frequency Performance at Vcc=3.5V and 16QAM OFDMA Signal

### ADL5570

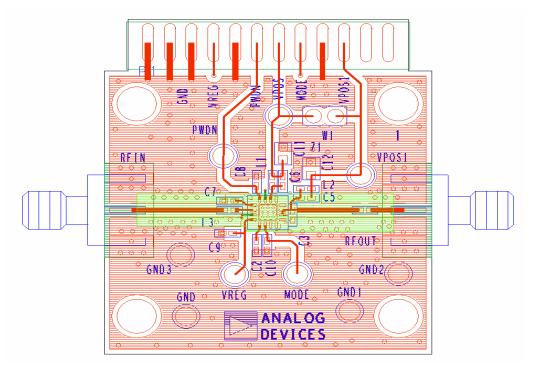

### **EVALUATION BOARD**

Figure 11. Evaluation Board Layout

The ADL5570 perfomance data were taken on a FR4 board layout. Care should be taken to ensure  $50\Omega$  impedance for all RF traces. For optimal performance in linearity, gain and efficiency, the output matching capacitor, C3, should be placed 30 mils from the edge of the package.

Component

TP1(STBY)

TP2 (VREG)

Vpos, Vpos1, GND

| Configuration Options Function                                                                                                                                                                                                                           | Default Value           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Supply and Ground Connections                                                                                                                                                                                                                            | W1 = Installed          |

| <b>Transmit/Standby Mode</b> : When STBY is low (0 V), the device operates in transmit mode. When the radio is receiving data, STBY can be taken high (2.5 V), reducing supply current to 10 mA.                                                         | Not Applicable          |

| <b>Normal/Sleep Mode</b> : When VREG is low, the device goes into sleep mode, reducing supply current to 10 uA. When VREG is high (2.85 V), the device operates in its normal transmit mode. When high, VREG draws a bias current of approximately 10 mA | Not Applicable          |

| <b>High/Low Power Mode</b> : Switches between High Power and Low Power Modes. When Mode is low (0V), the device operates in High Power Mode. When Mode is high (MODE = 2.5 V), the device operates in Low Power Mode.                                    | Not Applicable          |

| Input Interface: (1.3) matches the input to 50 ohms                                                                                                                                                                                                      | 13 - 22  nH (Size 0402) |

#### Table 5. Evaluation Board Configurat

|                           | operates in its normal transmit mode. When high, VREG draws a bias current of approximately 10 mA                                                                                                                     |                                                                                                                                                                                                                                                                                                      |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TP5(MODE)                 | <b>High/Low Power Mode</b> : Switches between High Power and Low Power Modes. When Mode is low (0V), the device operates in High Power Mode. When Mode is high (MODE = 2.5 V), the device operates in Low Power Mode. | Not Applicable                                                                                                                                                                                                                                                                                       |

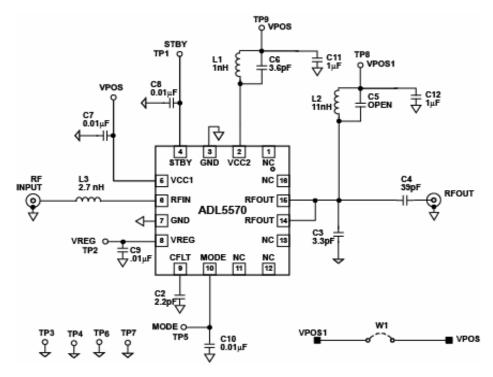

| L3,                       | <b>Input Interface</b> : (L3) matches the input to 50 ohms.                                                                                                                                                           | L3 = 2.2nH (Size 0402)                                                                                                                                                                                                                                                                               |

| C3, C4,                   | <b>Output Interface</b> : C4 provides dc blocking. C3 matches the output to 50 ohms.                                                                                                                                  | C4 = 39pF (Size 0402)<br>C3 = 3.3pF (Size 0402)<br>(C3 value for 2.3 Ghz to 2.4Ghz<br>operation)                                                                                                                                                                                                     |

| C2                        | <b>Filter Interface</b> : A ground referenced capacitor should be connected to this node to reduce bias line noise                                                                                                    | C2 = 2.2pF (Size 0402)                                                                                                                                                                                                                                                                               |

| C7, C8, C9, C10, C11, C12 | <b>Power Supply Decoupling</b> : The capacitors, C7, thru C12, are used for power supply decoupling. They should be placed as close as possible to the DUT.                                                           | $\begin{array}{l} {\sf C7}=0.01\mu{\sf F}~({\sf Size}~0402)\\ {\sf C8}=0.01\mu{\sf F}~({\sf Size}~0402)\\ {\sf C9}=0.01\mu{\sf F}~({\sf Size}~0402)\\ {\sf C10}=0.01\mu{\sf F}~({\sf Size}~0402)\\ {\sf C11}~=1\mu{\sf F}~({\sf Size}~0402)\\ {\sf C12}=1\mu{\sf F}~({\sf Size}~0402)\\ \end{array}$ |

| L1, L2, C6, C5            | <b>RF Trap</b> : L1, C6 and L2, C5 form tank circuits and prevent RF from propagating on the dc supply lines                                                                                                          | L1 = 1nH (Size 0402)<br>C6 = 3.6pF (Size 0402)<br>L1 = 11nH (Size 0402)<br>C5 = OPEN                                                                                                                                                                                                                 |

Figure 12. Application Schematic

### **OUTLINE DIMENSIONS**

©2007 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. PR06729-0-4/07(PrG)

www.analog.com

Rev. PrG | Page 10 of 10