# 2K X 8 CMOS Electrically Erasable PROM

### **FEATURES**

- Fast Read Access Times — 100ns, 150ns, 200ns, 250ns

- Low CMOS Power Consumption

- 30mA active (max.)

- 100µA standby (max.)

- 5 Volt-only Operation - Including Write

- Industrial Temperature Range Available (XLE28C16B)

- Fast Nonvolatile Write Cycle

- Internally Latched Data and Address

- 120ns Byte-load Cycle

- 5ms Nonvolatile Write Cycle

- On-chip Inadvertent Write Protection

- Unlimited Read Cycle Endurance

- 10,000 Rewrites per Byte

- 10 Year Secure Data Retention

- **DATA Polling To Minimize Write Cycle Times**

- Reliable Floating Gate CMOS Technology

- 16 Byte Page Mode

### **OVERVIEW**

The XL28C16B is a full-featured, 2K x 8 bit CMOS E2PROM (Electrically Erasable Programmable Read Only Memory). Operationally, it is compatible with industry standard 16K bit E2PROM devices, and it offers improved speed and power efficiency. Read access times are as low as 100ns; standby current, less than 100µA. The device is fully functional with a single 5V power supply, and the XL28C16B is manufactured with EXEL's 1.5µ CMOS E2PROM process.

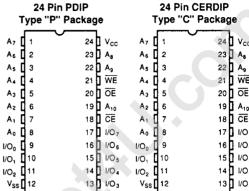

#### PIN CONFIGURATION

# 24 Vcc 21 WE 20 1 0至 19 A10 18 T CE 17 1 1/07 16 1/06 15 1 1/05 14 1 1/04 13 1 1/03

#### П 1/07 16 106 1/00 15 1/05 1/0. 1/02 14 1/04 13 1/03

24 Pin Skinny DIP

Type "P3" Package

1 2 A<sub>5</sub>

Аз

A<sub>2</sub> ۵ 24 1 V<sub>CC</sub>

23 A<sub>8</sub>

22 A<sub>9</sub>

21 WE

20 1 OE

19 🛮 A<sub>10</sub>

D CE

# PIN NAMES

| A <sub>0</sub> -A <sub>10</sub> | Address Inputs          |

|---------------------------------|-------------------------|

| 1/00-1/07                       | Data Inputs/Outputs     |

| CE                              | Chip Enable             |

| DE V                            | Output Enable           |

| WE                              | Write Enable            |

| Vcc                             | Supply Voltage          |

| Vss                             | Power and Signal Ground |

| NC                              | No Connect              |

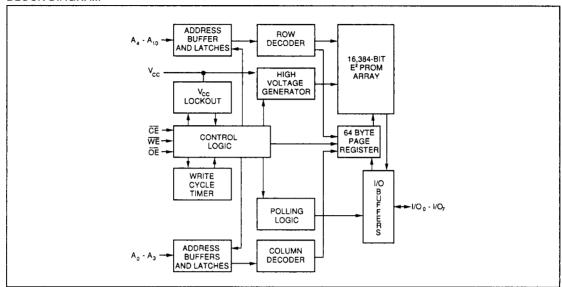

#### **BLOCK DIAGRAM**

The sophisticated architecture of this device provides complete and automatic control of the nonvolatile write cycle eliminating the need for external timers, latches, high voltage generators and inadvertent write protection circuitry. It fits into a standard SRAM socket and responds to typical SRAM write commands.

The XL28C16B features VCC lockout, power-on reset and noise protected  $\overline{WE}$ , to inhibit inadvertent writes.

The XL28C16B is compatible with industrial standard 2K  $\times$  8 E<sup>2</sup>PROMS — its pinouts and operating modes conform to established standards. This compatibility extends to higher and lower density EXEL E<sup>2</sup>PROMS as well.

#### **APPLICATIONS**

The XL28C16B provides secure and reliable data storage thoughout your system's lifetime, both during periods of power on and power off. It may be written to through standard microprocessor protocols as if it were a Static RAM, yet it retains its data in the absence of system power for at least 10 years after the data is written. This flexibility has resulted in a wide variety of digital system applications.

The nonvolatile storage in the XL28C16B replaces dip switches as a means of storing configuration data. It delivers firmware for booting up systems, and for operating industrial and process controllers, traffic controllers, robotics and telemetry, measuring instruments and appliance controls. It retains phone numbers and messages in facsimile machines. The XL28C16B is ideal in applications that are self-adapting such as video games and systems that require automatic re-calibration, as well as those that are subject to power failures.

# **ENDURANCE and DATA RETENTION**

The XL28C16B is designed for applications requiring up to 10,000 data changes per E<sup>2</sup>PROM byte ensuring a guaranteed endurance of 20 million data changes per device. It provides 10 years of secure data retention, with or without power applied after the data is written.

### **DEVICE OPERATION**

Three control pins ( $\overline{CE}$ ,  $\overline{OE}$  and  $\overline{WE}$ ) select all standard user-operating modes for the XL28C16B. Chip erase (typically executed during test procedures) requires a higher supply voltage on one input pin. This conforms with existing E<sup>2</sup>PROM standards.

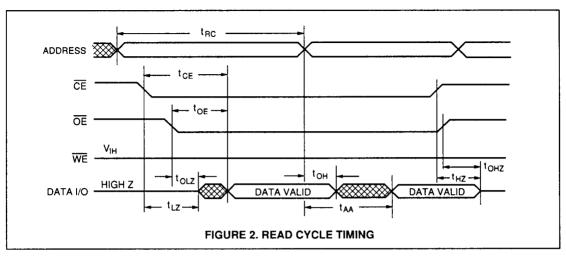

#### **Read Mode**

Data is read from the XL28C16B by bringing both  $\overline{CE}$  and  $\overline{OE}$  LOW while keeping  $\overline{WE}$  HIGH. With the read mode selected, address lines can be changed at any time, in any order to read data at various locations in the E<sup>2</sup>PROM array. Read access time is measured from the time when the final controlling line ( $\overline{CE}$  or  $\overline{OE}$ ) goes LOW, or the time when the address is established.

The device can be read an unlimited number of times, because the stored charge that defines the bit state is not affected by a read cycle. (See Figure 2.)

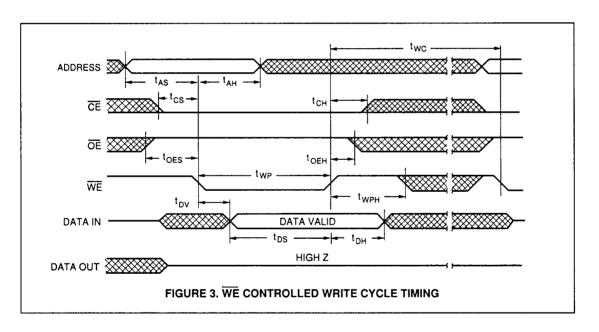

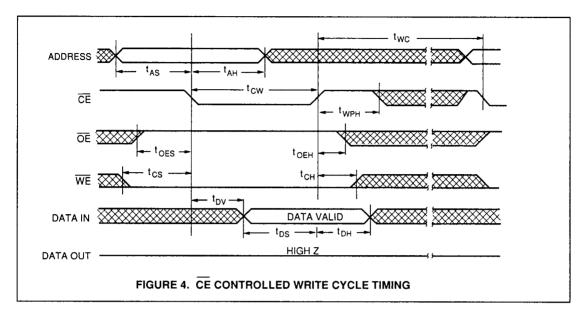

#### Write Mode

The XL28C16B uses a two-step process to store new data. Byte-load cycles fill latches in a volatile page buffer. A subsequent nonvolatile write cycle transfers new entries in the page-buffer to the E<sup>2</sup>PROM array.

The XL28C16B contains 128 16-byte pages. Address lines A4-A10 identify the page: lines A0-A3 identify the byte within the page. All bytes written within one write cycle must be on the same page (A4-A10 must remain unchanged). Any number of the 16 bytes in the page can be written or re-written, in any order; the last data written is retained.

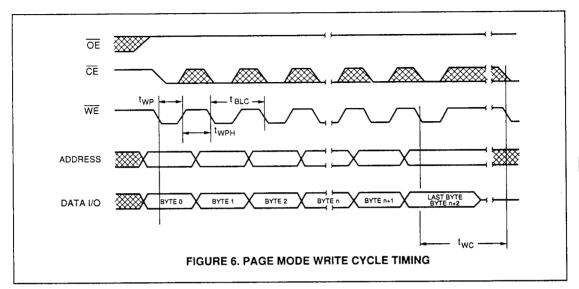

Either  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$  can be used to trigger the byte-load cycle. The address is latched into internal address latches upon the last falling edge of  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$ . A byte-load timer is started on the subsequent rising edge of the controlling line. The timer provides a 75µS window for initiating the next byte-load cycle. Byte-loading can continue indefinitely if each new load cycle is started within the timeout period. Please note that all write cycles require that  $\overline{\text{OE}}$  is held HIGH.

When the timer times out, additional byte-load cycles are inhibited and data is automatically transferred from the page buffer to the E<sup>2</sup>PROM array during the internal nonvolatile write cycle. Byte flags, set during the byte-load cycles, ensure that high voltage is applied only to newly written bytes. By avoiding the unnecessary cycling of bytes, the endurance of the array is extended. The nonvolatile write cycle is immune to any concurrent control pin activity.

A write-latch is set on the first byte-load of each write cycle. Output pins remain in a high impedance state except during a byte-load (when they contain new input data) or during a DATA polling read cycle. When the nonvolatile cycle is completed, the operating mode is again determined by the control pins (CE, OE and WE). (See Figures 3. 4 and 6.)

# **Output Disable Mode**

If, while in the read mode,  $\overline{OE}$  is brought HIGH, the device remains in the read mode, but with the outputs disabled. (I/O pins are in a high impedance state.)

# Standby Mode

Whenever  $\overline{CE}$  is brought HIGH, the device is set into its standby mode, placing the I/O pins in a high impedance state. Standby power dissipation is less than 100µA with CMOS level inputs. While  $\overline{CE}$  remains HIGH, all other input pins are disabled, insulating the device from activity on the system busses.

## **Chip Erase**

The chip erase mode allows the user to erase the entire E²PROM array with a single command. The method requires the application of high voltage ( $V_H$ ) on the  $\overline{OE}$  pin, with  $\overline{CE}$  at a logical "0." Chip erase is initiated by a standard byte write command while holding data on the I/V0 inputs high. A byte containing all "1's" is automatically written to all locations in the E²PROM array. (Refer to the Mode Selection chart.)

### **MONITORING DEVICE STATUS**

Because the internal nonvolatile write cycle is completely managed by the XL28C16B, a status indicator has been incorporated to provide for the system to monitor the READY/BUSY status of the device. This is accomplished through a system software routine which simply re-reads the XL28C16B until it determines a simple logical condition

## **MODE SELECTION**

| CE  | ŌĒ  | WE              | Mode                       | I/O                     | Power   |

|-----|-----|-----------------|----------------------------|-------------------------|---------|

| ViH | X   | Χ               | Standby                    | HIGH Z                  | Standby |

| VIL | VIL | ViH             | Read                       | Dout                    | Active  |

| VIL | ViH | 7               | Byte Write (WE Controlled) | DiN                     | Active  |

|     | ViH | V <sub>IL</sub> | Byte Write (CE Controlled) | DiN                     | Active  |

| VIL | Vн  | VIL             | Chip Erase*                | Data In≖V <sub>IH</sub> | Active  |

| X   | VIL | Х               | Write Inhibit              | -                       | _       |

<sup>\*</sup>Contact EXEL for details

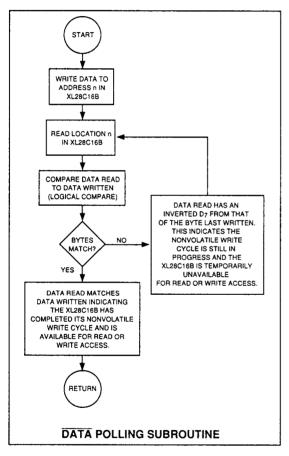

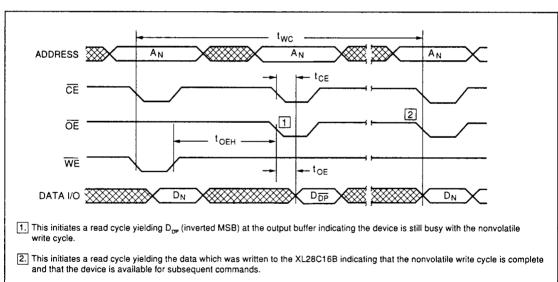

**DATA** Polling

The XL28C16B provides a feature named DATA polling which enables the host system to determine the status of the device through the use of the system busses. No additional hardware is required. Any attempt to read the part while the XL28C16B is busy executing its nonvolatile write cycle will be interpreted as a DATA polling read. This is performed by exercising the control pins in the same sequence as for a normal read. DATA polling cycles have no effect on the byte-load timer, contents of the data buffer or nonvolatile cycle timing.

DATA polling is a simple software technique used to determine the status of the XL28C16B. It is executed as a normal read cycle where the target byte location is the same as that of the byte last written to the XL28C16B. During the 5ms (max.) period that the device requires to complete its nonvolatile write cycle, the I/O buffers are set in a high impedance state with the exception of I/O7. I/O7 is set to output the **complement** of the value of the MSB of the last byte written to the XL28C16B when a read command is asserted.

The procedure is quite simple. The system reads the location last written to in the XL28C16B and executes a compare operation between the data thus retrieved and the original data byte written. If the compare fails, the XL28C16B is still busy with its nonvolatile write cycle. If the compare passes, the nonvolatile write cycle is complete and the device is available for read or write accesses.

This procedure is commonly used to determine the actual nonvolatile write cycle completion timing eliminating the need to await the 5ms (max.) period specified and enabling accelerated device loading operations. (See Figure 5.)

### WRITE PROTECT MECHANISMS

The XL28C16B features several integrated mechanisms to protect it from inadvertent writes that might occur during system power supply transitions or periods of system noise. In addition to the user-controlled protection mechanisms, the following specialized circuits are built in.

#### **OE** Write Inhibit

If  $\overline{OE}$  is brought LOW before the  $\overline{CE}$  and  $\overline{WE}$  write command sequence, the internal nonvolatile write cycle will not occur. See the Mode Selection Table on page 3.

### **Noise Protection**

Write pulses of less than 10ns duration on the  $\overline{WE}$  pin will not initiate nonvolatile write cycles.

# **ABSOLUTE MAXIMUM RATINGS**

| Temperature Under Bias                            | 55°C to +125°C |

|---------------------------------------------------|----------------|

| Storage Temperature                               | 65°C to +150°C |

| Lead Soldering Temperature (less than 10 seconds) | 300°C          |

| Supply Voltage                                    | 0 to 6.5V      |

| Voltage on Any Pin*                               | 0.6V to +7.0V  |

| Voltage on Any Pin*                               | 0.6V to +15V   |

| ESD Rating                                        | 2000V          |

| DC Output Current                                 | 5mA            |

| *With respect to ground                           |                |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions indicated in the operational sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Although this product includes specific circuitry to protect it from electrostatic discharge, conventional precautions should be taken to protect it from any voltages higher than the rated maxima.

# DC CHARACTERISTICS

$T_A = 0$ °C to +70°C for the XLS28C16B or -40°C to +85°C for the XLE28C16B,  $V_{CC} = 5V\pm10\%$

| Symbol           | Parameter                              | Test Conditions                                                                                                     | Min.                                                                         | Max.                  | Units  |  |

|------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------|--------|--|

| Icc              | V <sub>CC</sub> Current-Active (TTL)   | $\overline{CE} = \overline{OE} = V_{IL}$ $WE = V_{IH}$ $I/O's = open$ $A_0 - A_{12} = toggling$ $f = 5 \text{ MHz}$ | WE = V <sub>IH</sub> I/O's = open A <sub>0</sub> -A <sub>12</sub> = toggling |                       |        |  |

| I <sub>SB</sub>  | V <sub>CC</sub> Current-Standby (TTL)  | CE = VIH<br>OE = VIL<br>I/O's = open<br>A <sub>0</sub> -A <sub>12</sub> = Vcc                                       |                                                                              | 2                     | mA     |  |

| I <sub>SBC</sub> | V <sub>CC</sub> Current-Standby (CMOS) | $\overline{CE} >= V_{CC} - 0.2$<br>$\overline{OE} = V_{1L}$<br>I/O's = open<br>$A_0 - A_{12} >= V_{CC} - 0.2$       |                                                                              | 100                   | μА     |  |

| L                | Input Leakage Current                  | V <sub>IN</sub> = GND to V <sub>CC</sub>                                                                            | -10                                                                          | 10                    | μA     |  |

| 1 <sub>LO</sub>  | Output Leakage Current                 | V <sub>OUT</sub> = GND to V <sub>CC</sub><br>CE = V <sub>IH</sub>                                                   | -10                                                                          | 10                    | μА     |  |

| V <sub>IL</sub>  | Input Low Voltage                      |                                                                                                                     |                                                                              | 0.8                   | V      |  |

| V <sub>IH</sub>  | Input High Voltage                     |                                                                                                                     | 2.0                                                                          | V <sub>CC</sub> + 0.5 | ٧      |  |

| V <sub>OL</sub>  | Output Low Voltage                     | 1 <sub>OL</sub> = 2.1mA                                                                                             |                                                                              | 0.4                   | ٧      |  |

| V <sub>OH</sub>  | Output High Voltage                    | I <sub>OH</sub> = -400µ A<br>I <sub>OH</sub> = -10µA                                                                | 2.4<br>V <sub>CC</sub> -0.1                                                  |                       | V<br>V |  |

| V <sub>H</sub>   | High Voltage for Chip Erase            |                                                                                                                     | 11.4                                                                         | 12.6                  | ٧      |  |

# **CAPACITANCE**

$T_{A}= +25^{\circ}C$ , f = 1.0 MHz

| Symbol           | Test                     | Test Conditions       | Max. | Units |

|------------------|--------------------------|-----------------------|------|-------|

| C <sub>1/O</sub> | Input/Output Capacitance | V <sub>I/O</sub> = 0V | 10   | pF    |

| CIN              | Input Capacitance        | V <sub>IN</sub> = 0V  | 6    | pF    |

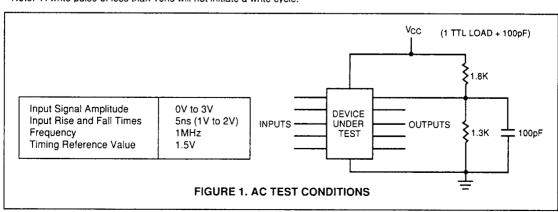

## **AC OPERATING CHARACTERISTICS**

# READ CYCLE (See Figure 2)

$T_A = 0$ °C to +70°C for the XLS28C16B or -40°C to +85°C for the XLE28C16B,  $V_{CC} = 5V \pm 10\%$

|                 |                                    | XL28C16B-100<br>Limits |      | XL28C16B-150<br>Limits |          | XL28C16B-200<br>Limits |      | XL28C16B-250<br>Limits |      |       |

|-----------------|------------------------------------|------------------------|------|------------------------|----------|------------------------|------|------------------------|------|-------|

| Symbol          | Parameter                          | Min.                   | Max. | Min.                   | Max.     | Min.                   | Max. | Min.                   | Max. | Units |

| tro             | Read Cycle Time                    | 100                    |      | 150                    |          | 200                    |      | 250                    |      | ns    |

| 1 <sub>AA</sub> | Address Access Time                |                        | 100  |                        | 150      |                        | 200  |                        | 250  | ns    |

| tce             | Chip Enable Access Time            |                        | 100  |                        | 150      |                        | 200  |                        | 250  | ns    |

| toe             | Output Enable Access Time          |                        | 70   |                        | 80       |                        | 90   |                        | 100  | ns    |

| tLZ             | Chip Enable to Output in Low Z     | 0                      |      | 0                      |          | 0                      |      | 0                      |      | ns    |

| tHZ             | Chip Disable to Output in High Z   | 0                      | 50   | 0                      | 50       | 0                      | 50   | 0                      | 60   | ns    |

| tolz            | Output Enable to Output in Low Z   | 0                      |      | 0                      |          | 0                      |      | 0                      |      | ns    |

| tонz            | Output Disable to Output in High Z | 0                      | 35   | Ö                      | 50       | 0                      | 50   | 0                      | 60   | ns    |

| tон             | Output Hold from Address Change    | 15                     |      | 15                     | <u> </u> | 15                     |      | 15                     |      | ns    |

# WRITE CYCLE (See Figures 3, 4, 5 and 6)

$T_A = 0$ °C to +70°C for the XLS28C16B or -40°C to +85°C for the XLE28C16B,  $V_{CC} = 5V \pm 10\%$

| Symbol | Parameter                      | Min. | Max. | Units |

|--------|--------------------------------|------|------|-------|

| twc    | Write Cycle Time               |      | 5    | ms    |

| tBLC   | Byte Load Cycle                | .120 | 100  | μs    |

| tas    | Address Setup Time             | 0    |      | ns    |

| tah    | Address Hold Time              | 35   |      | ns    |

| tcs    | Write Setup Time               | 0    |      | ns    |

| tсн    | Write Hold Time                | 0    |      | ns    |

| tcw    | Chip Enable Pulse Width        | 50   |      | ns    |

| toes   | Output Enable Setup Time       | 5    |      | ns    |

| toen   | Output Enable Hold Time        | 5    |      | ns    |

| *twp   | Write Enable Pulse Width       | 70   |      | ns    |

| twph   | Write Pulse Width High         | 50   |      | ns    |

| tos    | Data Setup Time                | 30   |      | ns    |

| tph    | Data Hold Time                 | 0    |      | ns    |

| tov    | Data Valid Time                |      | 1    | μs    |

| tinit  | Power-up Initialization Period |      | 20   | ms    |

<sup>\*</sup> Note: A write pulse of less than 10ns will not initiate a write cycle.

FIGURE 5. DATA POLLING TIMING