# SRAM MODULE 4Mbyte(1M x 32-Bit) 3.3V Part No. HMS1M32M8V, HMS1M32Z8V

### **GENERAL DESCRIPTION**

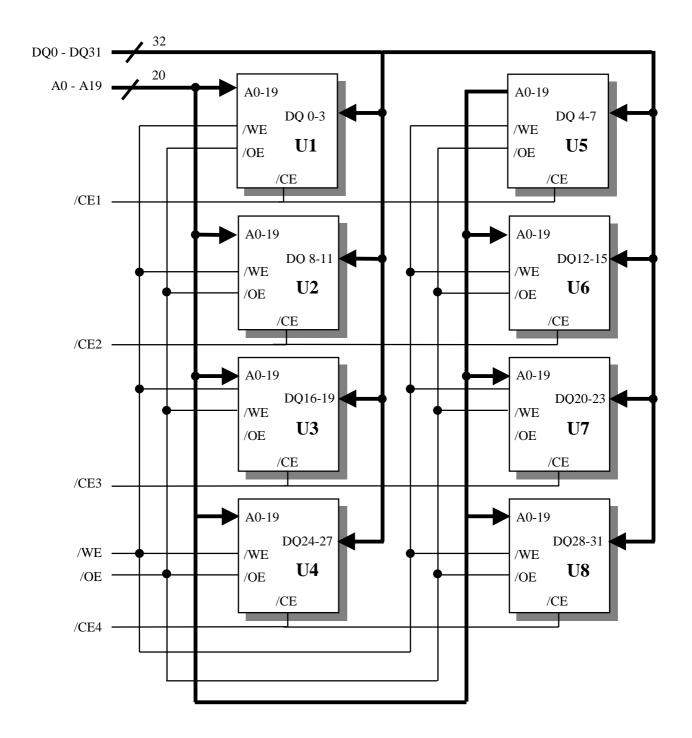

The HMS1M32M8V is a high-speed static random access memory (SRAM) module containing 1,048,576 words organized in a x32-bit configuration. The module consists of eight 1M x 4 SRAMs mounted on a 72-pin, double-sided, FR4-printed circuit board.

PD0 to PD3 identify the module's density allowing interchangeable use of alternate density, industry- standard modules. Eight chip enable inputs, (/CE1, /CE2, /CE3 and /CE4) are used to enable the module's 4 bytes independently. Output enable (/OE) and write enable(/WE) can set the memory input and output.

Data is written into the SRAM memory when write enable (/WE) and chip enable (/CE) inputs are both LOW. Reading is accomplished when /WE remains HIGH and /CE and output enable (/OE) are LOW.

For reliability, this SRAM module is designed as multiple power and ground pin. All module components may be powered from a single +3.3V DC power supply and all inputs and outputs are fully LVTTL-compatible.

#### **FEATURES**

### ◆ Part identification

- HMS1M32M8V: SIMM design

- HMS1M32Z8V: ZIP design

- → Pin-Compatible with the HMS1M32M8V

- Fast access times: 10, 12ns and 15ns

- ◆ High-density 4MByte design

- ◆ High-reliability high-speed design

- Single  $+ 3.3V \pm 0.3V$  power supply

- ◆ Easy memory expansion /CE and /OE functions

- All inputs and outputs are LVTTL-compatible

- ◆ Industry-standard pinout

- FR4-PCB design

- ◆ Low power Dissipation

#### **OPTIONS MARKING**

| • | Timing |

|---|--------|

|   |        |

| 10ns access | -10 |

|-------------|-----|

| 12ns access | -12 |

| 15ns access | -15 |

◆ Packages

72-pin SIMM M

### PIN ASSIGNMENT

|      |    |               |        |    |      | Γ-       |   |

|------|----|---------------|--------|----|------|----------|---|

| NC   | 1  |               | $\cap$ |    | /CE4 | 37       | ] |

| NC   | 2  |               | $\cup$ |    | /CE3 | 38       | ] |

| PD2  | 3  |               |        |    | A17  | 39       | ] |

| PD3  | 4  |               |        |    | A16  | 40       | ] |

| Vss  | 5  | $\overline{}$ |        |    | /OE  | 41       | ] |

| PD0  | 6  | Ħ             |        |    | Vss  | 42       | ] |

| PD1  | 7  | Ħ.            |        |    | DQ24 | 43       | ] |

| DQ0  | 8  | Ħ             |        |    | DQ16 | 44       | ] |

| DQ8  | 9  | Ħ             |        |    | DQ25 | 45       | ] |

|      | 10 | Ħ             |        |    | DQ17 |          | ] |

| DQ9  | 11 | Ħ             |        |    | DQ26 | 47       | ] |

| DQ2  | 12 | Ħ             |        |    | DQ18 |          | ] |

| DQ10 | 13 |               |        |    | DQ27 | 49       | ] |

| DQ3  | 14 |               |        |    | DQ19 | 50       | ] |

| DQ11 | 15 |               |        |    | A3   | 51       | ] |

|      | 16 |               |        |    | A10  | 52       | ] |

| A0   | 17 |               |        |    | A4   | 53       | ] |

| A7   | 18 |               |        |    | A11  | 54       | ] |

| A1   | 19 |               |        |    | A5   | 55       | ] |

| A8   | 20 |               |        |    | A12  | 56       | ] |

| A2   | 21 |               |        |    | Vcc  | 57       | ] |

| A9   | 22 |               |        |    | A13  | 58       | ] |

| DQ12 | 23 |               |        |    | A6   | 59       | ] |

| DQ4  | 24 |               |        |    | DQ20 | 60       | ] |

| DQ13 | 25 |               |        |    | DQ28 | 61       | ] |

| DQ5  | 26 |               |        |    | DQ21 | 62       | ] |

| DQ14 | 27 |               |        |    | DQ29 | 63       | ] |

| DQ6  | 28 |               |        |    | DQ22 | 64       | ] |

| DQ15 | 29 |               |        |    | DQ30 | 65       | ] |

| DQ7  | 30 |               |        |    | DQ23 | 66       | ] |

| Vss  | 31 |               |        |    | DQ31 |          | ] |

| /WE  | 32 |               |        |    | Vss  |          | ] |

| A15  | 33 |               |        |    | A18  |          | ] |

| A14  | 34 |               |        |    | A19  | 70       | ] |

| /CE2 | 35 |               |        |    | NC   | 71       | ] |

| /CE1 | 36 |               |        |    | NC   | 72       | ] |

|      |    | F             |        |    |      | <u> </u> |   |

|      |    |               |        |    |      |          |   |

|      |    |               | SI     | MM | PD0  | = Vss    | S |

|      |    |               | 51     |    | -    |          |   |

**TOP VIEW**

PD1 = Open

PD3 = Open

PD2 = Vss

### FUNCTIONAL BLOCK DIAGRAM

| MODE         | /OE | /CE | /WE | OUTPUT | POWER   |

|--------------|-----|-----|-----|--------|---------|

| STANDBY      | X   | Н   | X   | HIGH-Z | STANDBY |

| NOT SELECTED | Н   | L   | Н   | HIGH-Z | ACTIVE  |

| READ         | L   | L   | Н   | Dout   | ACTIVE  |

| WRITE        | X   | L   | L   | Din    | ACTIVE  |

### ABSOLUTE MAXIMUM RATINGS

| PARAMETER                             | SYMBOL           | RATING          |

|---------------------------------------|------------------|-----------------|

| Voltage on Any Pin Relative to Vss    | $V_{ m IN,OUT}$  | -0.5V to +4.6V  |

| Voltage on Vcc Supply Relative to Vss | $V_{CC}$         | -0.5V to +4.6V  |

| Power Dissipation                     | $P_{\mathrm{D}}$ | 8W              |

| Storage Temperature                   | $T_{ m STG}$     | -65°C to +150°C |

| Operating Temperature                 | $T_{A}$          | 0°C to +70°C    |

<sup>•</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **RECOMMENDED DC OPERATING CONDITIONS** ( $T_A \! = \! 0$ to 70 $^o$ C )

| PARAMETER          | SYMBOL          | MIN   | TYP. | MAX        |

|--------------------|-----------------|-------|------|------------|

| Supply Voltage     | $V_{CC}$        | 3.0V  | 3.3V | 3.6V       |

| Ground             | $V_{SS}$        | 0     | 0    | 0          |

| Input High Voltage | $V_{ m IH}$     | 2.0   | -    | Vcc+0.3V** |

| Input Low Voltage  | V <sub>IL</sub> | -0.3* | -    | 0.8V       |

<sup>\*</sup>  $V_{IL}(Min.) = -2.0V$  (Pulse Width  $\leq 10$ ns) for  $I \leq 20$  mA

### DC AND OPERATING CHARACTERISTICS (1)( $0^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ 70 $^{\circ}$ C ; Vcc = 3.3V $\pm$ 0.3V )

| PARAMETER              | TEST CONDITIONS                                                                            | SYMBO<br>L      | MIN | MAX | UNITS |

|------------------------|--------------------------------------------------------------------------------------------|-----------------|-----|-----|-------|

| Input Leakage Current  | $V_{IN} = Vss \text{ to } Vcc$                                                             | $IL_I$          | -2  | 2   | μΑ    |

| Output Leakage Current | /CE= $V_{IH \text{ or }}$ /OE = $V_{IH}$ or /WE= $V_{IL}$ $V_{OUT}$ = $V_{SS}$ to $V_{CC}$ | $IL_0$          | -2  | 2   | μΑ    |

| Output High Voltage    | $I_{OH} = -4.0$ Ma                                                                         | V <sub>OH</sub> | 2.4 |     | V     |

| Output Low Voltage     | $I_{OL} = 8.0 \text{mA}$                                                                   | V <sub>OL</sub> |     | 0.4 | V     |

<sup>\*</sup> Vcc=3.3V, Temp=25 °C

<sup>\*\*</sup>  $V_{IH}(Min.) = Vcc+2.0V$  (Pulse Width  $\leq 10ns$ ) for  $I \leq 20$  mA

### DC AND OPERATING CHARACTERISTICS (2)

|                                   |                                                                                                                          |           |     | MAX |     |      |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|-----|------|

| DESCRIPTION                       | TEST CONDITIONS                                                                                                          | SYMBOL    | -12 | -15 | -20 | UNIT |

| Power Supply<br>Current:Operating | Min. Cycle, 100% Duty /CE= $V_{IL}$ , $V_{IN}$ = $V_{IH}$ or $V_{IL}$ , $I_{OUT}$ = $0$ mA                               | $l_{CC}$  | 150 | 145 | 140 | mA   |

| Power Supply<br>Current:Standby   | Min. Cycle, /CE=V <sub>IH</sub>                                                                                          | $l_{SB}$  | 70  | 70  | 70  | mA   |

| Current:Standby                   | f=0MHZ, /CE $\geq$ V <sub>CC</sub> -0.2V,<br>V <sub>IN</sub> $\geq$ V <sub>CC</sub> -0.2V or V <sub>IN</sub> $\leq$ 0.2V | $l_{SB1}$ | 20  | 20  | 20  | mA   |

### **CAPACITANCE**

| DESCRIPTION               | TEST CONDITIONS | SYMBOL    | MAX | UNIT |

|---------------------------|-----------------|-----------|-----|------|

| Input /Output Capacitance | $V_{I/O}=0V$    | $C_{I/O}$ | 8   | pF   |

| Input Capacitance         | $V_{IN}=0V$     | $C_{IN}$  | 7   | pF   |

<sup>\*</sup> NOTE: Capacitance is sampled and not 100% tested

# $AC\ CHARACTERISTICS\ (0^{o}C \le T_{A} \le 70\ ^{o}C\ ;\ Vcc = 3.3V \pm 0.3V,\ unless\ otherwise\ specified)$

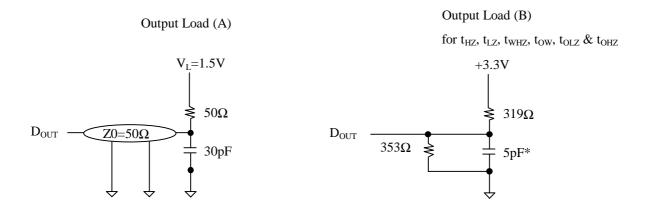

#### **TEST CONDITIONS**

| PARAMETER                                | VALUE     |

|------------------------------------------|-----------|

| Input Pulse Level                        | 0 to 3V   |

| Input Rise and Fall Time                 | 3ns       |

| Input and Output Timing Reference Levels | 1.5V      |

| Output Load                              | See below |

### **READ CYCLE**

|                                 |                   | -12 |     | -15 |     | -20 |     |      |

|---------------------------------|-------------------|-----|-----|-----|-----|-----|-----|------|

| PARAMETER                       | SYMBOL            | MIN | MAX | MIN | MAX | MIN | MAX | UNIT |

| Read Cycle Time                 | $t_{RC}$          | 12  |     | 15  |     | 20  |     | ns   |

| Address Access Time             | $t_{AA}$          |     | 12  |     | 15  |     | 20  | ns   |

| Chip Select to Output           | $t_{CO}$          |     | 12  |     | 15  |     | 20  | ns   |

| Output Enable to Output         | t <sub>OE</sub>   |     | 6   |     | 7   |     | 9   | ns   |

| Output Enable to Low-Z Output   | t <sub>OLZ</sub>  | 0   |     | 0   |     | 0   |     | ns   |

| Chip Enable to Low-Z Output     | $t_{LZ}$          | 3   |     | 3   |     | 3   |     | ns   |

| Output Disable to High-Z Output | t <sub>OHZ</sub>  | 0   | 6   | 0   | 7   | 0   | 9   | ns   |

| Chip Disable to High-Z Output   | $t_{ m HZ}$       | 0   | 6   | 0   | 7   | 0   | 9   | ns   |

| Output Hold from Address Change | $t_{OH}$          | 3   |     | 3   |     | 3   |     | ns   |

| Chip Select to Power Up Time    | $t_{\mathrm{PU}}$ | 0   |     | 0   |     | 0   |     | ns   |

| Chip Select to Power Down Time  | t <sub>PD</sub>   |     | 12  |     | 15  |     | 20  | ns   |

### WRITE CYCLE

|                               |                   | -12 |     | -15 |     | -20 |     |      |

|-------------------------------|-------------------|-----|-----|-----|-----|-----|-----|------|

| PARAMETER                     | SYMBOL            | MIN | MAX | MIN | MAX | MIN | MAX | UNIT |

| Write Cycle Time              | $t_{ m WC}$       | 12  |     | 15  |     | 20  |     | ns   |

| Chip Select to End of Write   | $t_{\mathrm{CW}}$ | 8   |     | 10  |     | 12  |     | ns   |

| Address Set-up Time           | $t_{AS}$          | 0   |     | 0   |     | 0   |     | ns   |

| Address Valid to End of Write | $t_{ m AW}$       | 8   |     | 10  |     | 12  |     | ns   |

| Write Pulse Width             | $t_{ m WP}$       | 8   |     | 10  |     | 12  |     | ns   |

| Write Recovery Time           | $t_{ m WR}$       | 0   |     | 0   |     | 0   |     | ns   |

| Write to Output High-Z        | $t_{ m WHZ}$      | 0   | 6   | 0   | 7   | 0   | 9   | ns   |

| Data to Write Time Overlap    | $t_{ m DW}$       | 6   |     | 7   |     | 9   |     | ns   |

| Data Hold from Write Time     | $t_{ m DH}$       | 0   |     | 0   |     | 0   |     | ns   |

| End of Write to Output Low-Z  | t <sub>OW</sub>   | 3   |     | 3   |     | 3   |     | ns   |

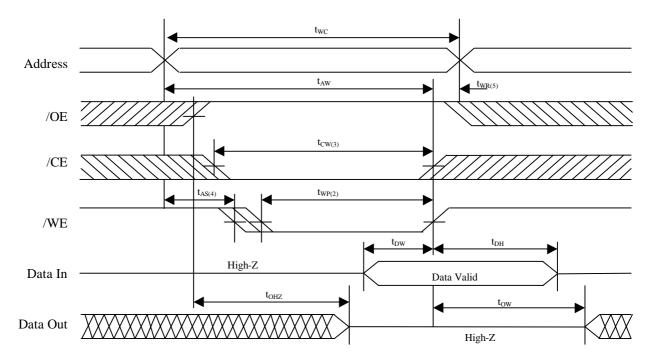

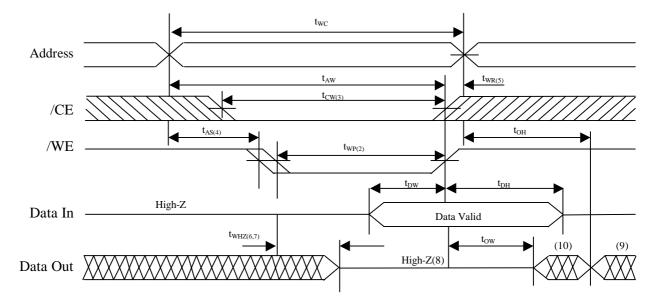

### **TIMING DIAGRAMS**

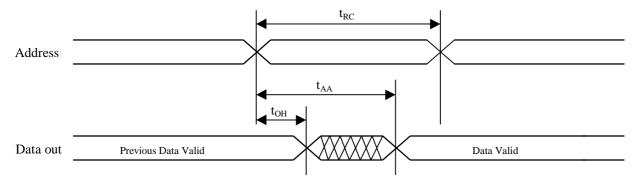

### $\textbf{TIMING WAVEFORM OF READ CYCLE}(\ \text{Address Controlled})(\ /\text{CE =/OE} = V_{IL}\ ,\ /\text{WE} = V_{IH})$

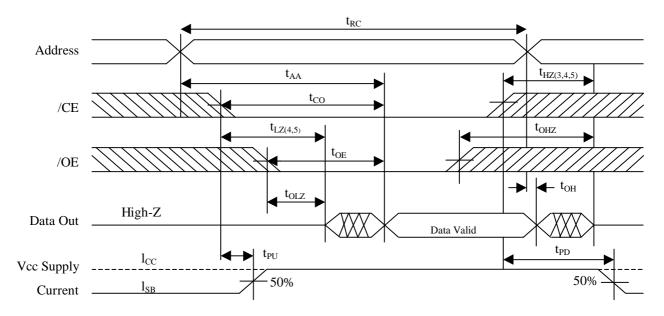

### **TIMING WAVEFORM OF READ CYCLE** ( $/WE = V_{IH}$ )

### Notes (Read Cycle)

- 1. /WE is high for read cycle.

- 2. All read cycle timing is referenced from the last valid address to first transition address.

- 3.  $t_{HZ}$  and  $t_{OHZ}$  are defined as the time at which the outputs achieve the open circuit condition and are not referenced to  $V_{OH}$  or  $V_{OL}$  levels.

- 4. At any given temperature and voltage condition,  $t_{HZ}$  (max.) is less than  $t_{LZ}$  (min.) both for a given device and from device to device.

- 5. Transition is measured  $\pm$  200mV from steady state voltage with Load (B). This parameter is sampled and not 100% tested.

- 6. Device is continuously selected with  $/CE = V_{IL}$ .

- 7. Address valid prior to coincident with /CE transition low.

#### TIMING WAVEFORM OF WRITE CYCLE (/OE = Clock )

#### TIMING WAVEFORM OF WRITE CYCLE (/OE Low Fixed)

#### **Notes**(Write Cycle)

- 1. All write cycle timing is referenced from the last valid address to the first transition address.

- 2. A write occurs during the overlap of a low /CE and a low /WE. A write begins at the latest transition among /CE going low and /WE going low: A write ends at the earliest transition among /CE going high and /WE going high. t<sub>WP</sub> is measured from the beginning of write to the end of write.

- 3. t<sub>CW</sub> is measured from the later of /CE going low to the end of write.

- 4. t<sub>AS</sub> is measured from the address valid to the beginning of wirte.

- 5.  $t_{WR}$  is measured from the end of write to the address change.  $t_{WR}$  applied in case a write ends as /CE, or /WE going high.

- 6. If /OE,/CE and /WE are in the read mode during this period, the I/O pins are in the output low-Z state. Inputs of

opposite phase of the output must not be applied because bus contention can occur.

- 7. For common I/O applications, minimization or elimination of bus contention conditions is necessary during read and write cycle.

- 8. If /CE goes low simultaneously with /WE going low or after /WE going low, the outputs remain high impedance state.

- 9. D<sub>OUT</sub> is the read data of the new address.

- 10. When /CE is low: I/O pins are in the output state. The input signals in the opposite phase leading to the output should not be applied.

### **FUNCTIONAL DESCRIPTION**

| /CE | /WE | /OE | MODE           | I/O PIN                     | SUPPLY CURRENT    |

|-----|-----|-----|----------------|-----------------------------|-------------------|

| Н   | X*  | X   | Not Select     | High-Z                      | $1_{SB}, 1_{SB1}$ |

| L   | Н   | Н   | Output Disable | High-Z                      | $l_{CC}$          |

| L   | Н   | L   | Read           | $\mathrm{D}_{\mathrm{OUT}}$ | $l_{CC}$          |

| L   | L   | X   | Write          | $\mathrm{D_{IN}}$           | $l_{CC}$          |

Note: X means Don't Care

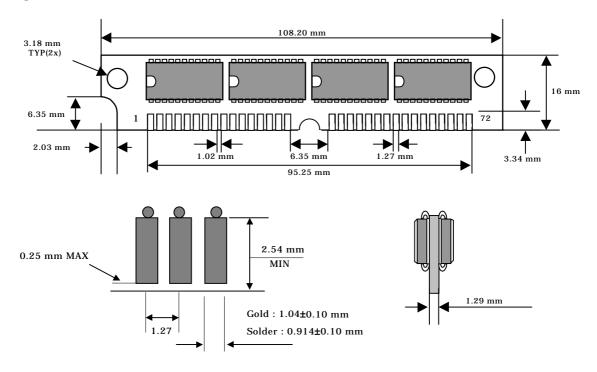

### **PACKAGING DIMMENSIONS**

### **SIMM Design**

(Solder & Gold Plating Lead)

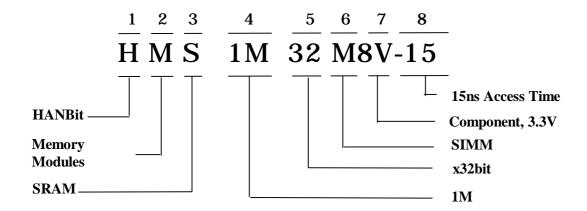

### **ORDERING INFORMATION**

| 1 | <b>Product Line Identifier</b>     |

|---|------------------------------------|

|   | HANBit H                           |

| 2 | Memory Modules                     |

| 3 | SRAM                               |

| 4 | Depth: 1M                          |

| 5 | Width: x 32bit                     |

| 6 | Package Code                       |

|   | SIMM M                             |

|   | ZIP Z                              |

| 7 | Number of Memory Components, 3.3VV |

|   | Access time                        |

|   | 10 10ns                            |

|   | 12 12ns                            |

|   | 15 15ns                            |

|   | 17 17ns                            |

|   | 20 20ns                            |