# **MOTOROLA SEMICONDUCTOR TECHNICAL DATA**

# Advance Information

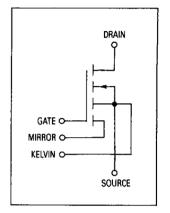

# **Power Field Effect Transistor N-Channel Enhancement-Mode Silicon Gate** with Current Sensing Capability

This TMOS Power FET with current sensing capability is designed for all power control applications where it is desirable to sense current such as in power supplies and motor controls. This device allows current sensing with minimum power loss.

- "Lossless" Current Sensing for Maximum Efficiency - Sense Current is Reduced by a Factor of Over 1000

- Ideal for Short Circuit/Overload Protection

- Simplifies Many Circuits When Used With Current Mode Integrated Circuits Such as the MC34129

- Kelvin Source Contact to Maximize Accuracy

- Rugged SOA is Power Dissipation Limited

- Low RDS(on) -- 0.25 Ohms Maximum

### NOTES

- Handling precautions to protect against electrostatic

- discharge is mandatory

2 Do not use the mirror FET independent of the power FET

3. It is recommended that the mirror terminal (M) be shorted to the source terminal (S) when current sensing is not required.

### MTP10N10M

TMOS SENSEFET DEVICE 10 AMPERES R<sub>DS(on)</sub> = 0.25 OHM 100 VOLTS

### **MAXIMUM RATINGS**

| Rating                                                                           | Symbol                              | Value        | Unit          |

|----------------------------------------------------------------------------------|-------------------------------------|--------------|---------------|

| Drain-to-Source Voltage                                                          | V <sub>DSS</sub>                    | 100          | Vdc           |

| Drain-to-Gate Voltage (RGS = 1 M $\Omega$ )                                      | VDGR                                | 100          | Vdc           |

| Gate-to-Source Voltage — Continuous<br>— Non-repetitive (t <sub>p</sub> ≤ 50 μs) | V <sub>GS</sub><br>V <sub>GSM</sub> | ± 20<br>± 40 | Vdc<br>Vpk    |

| Drain-to-Mirror Voltage                                                          | V <sub>DMS</sub>                    | 100          | Vdc           |

| Gate-to-Mirror Voltage                                                           | VGМ                                 | ± 20         | Vdc           |

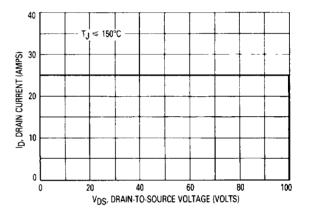

| Drain Current — Continuous<br>— Pulsed                                           | IDM                                 | 10<br>25     | Adc           |

| Sense Current — Continuous<br>— Pulsed                                           | l <sub>W</sub> M                    | 6<br>14      | mA            |

| Total Power Dissipation @ T <sub>C</sub> = 25°C<br>Derate above 25°C             | PD                                  | 75<br>0.6    | Watts<br>W/°C |

| Operating and Storage Temperature Range                                          | T <sub>J</sub> , T <sub>stg</sub>   | -55 to 150   | °C            |

### THERMAL CHARACTERISTICS

| Thermal Resistance, Junction-to-Case Junction-to-Ambient                         | R <sub>Ø</sub> JC<br>R <sub>Ø</sub> JA | 1.67<br>62.5 | °C/W |

|----------------------------------------------------------------------------------|----------------------------------------|--------------|------|

| Maximum Lead Temperature for Soldering Purposes,<br>1/8" from case for 5 seconds | TL                                     | 260          | °C   |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

# **ELECTRICAL CHARACTERISTICS** ( $T_C = 25^{\circ}C$ , $V_{MS} = 0$ unless otherwise noted)

| Char                                                                                                                      | acteristics                                                           | Symbol               | Min      | Тур      | Max        | Unit |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------|----------|----------|------------|------|

| OFF CHARACTERISTICS                                                                                                       |                                                                       |                      |          |          |            |      |

| Drain-to-Source Breakdown<br>(VGS = 0, ID = 0.25 mA                                                                       | •                                                                     | V <sub>(BR)DSS</sub> | 100      | _        | _          | Vdc  |

| Drain-to-Mirror Breakdown Voltage<br>(VGS = 0, I <sub>D</sub> = 0.25 mA)                                                  |                                                                       | V <sub>(BR)DMS</sub> | 100      | _        | _          | Vdc  |

| Zero Gate Voltage Drain Current<br>(VDS = 100 V, VGS = 0)<br>(VDS = 100 V, VGS = 0, TJ = 100°C)                           |                                                                       | DSS                  | _        | _        | 0.2<br>1   | mAdc |

| Gate-Body Leakage Current — Forward (VGSF = 20 Vdc, VDS = 0)                                                              |                                                                       | IGSSF                | _        | _        | 100        | nAdc |

| Gate-Body Leakage Current — Reverse (VGSR = 20 Vdc, VDS = 0)                                                              |                                                                       | GSSR                 | _        | _        | 100        | nAdc |

| N CHARACTERISTICS*                                                                                                        | •                                                                     |                      |          |          |            |      |

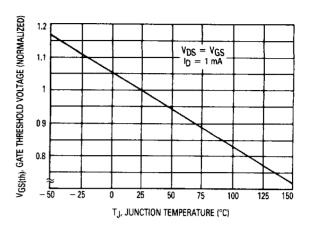

| Gate Threshold Voltage<br>$(V_{DS} = V_{GS}, I_{D} = 1 \text{ mA})$<br>$(T_{J} = 100^{\circ}\text{C})$                    | dc)                                                                   | VGS(th)              | 2<br>1.5 | 3 —      | 4.5<br>4   | Vdc  |

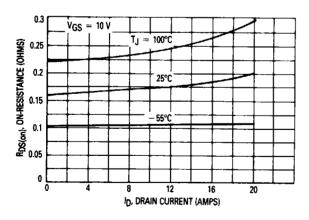

| Static Drain-to-Source On-I<br>(VGS = 10 Vdc, I <sub>D</sub> = 5 A                                                        |                                                                       | R <sub>DS(on)</sub>  | _        | 0.16     | 0.25       | Ohms |

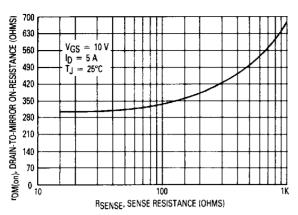

| Static Drain-to-Mirror On-R<br>(VGS = 10 V, I <sub>D</sub> = 10 A                                                         |                                                                       | rDM(on)              | _        | 288      | _          | Ohms |

| Drain-to-Source On-Voltage (V <sub>GS</sub> = 10 Vdc)<br>(I <sub>D</sub> = 10 A)<br>(I <sub>D</sub> = 5 A, $T_J$ = 100°C) |                                                                       | V <sub>DS(on)</sub>  | _        | 1.9<br>— | 2.7<br>2.8 | Vdc  |

| Forward Transconductance<br>(VGS = 10 Vdc, I <sub>D</sub> = 5 A                                                           |                                                                       | 9FS                  | 2.5      |          | -          | mhos |

| Current Mirror Ratio (Cell R<br>(RSENSE = 0, ID = 10 A                                                                    |                                                                       | n                    | 1750     | 1800     | 1850       | _    |

| YNAMIC CHARACTERISTIC                                                                                                     | S                                                                     | ,                    |          |          |            |      |

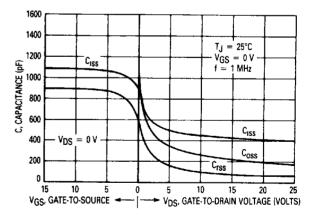

| Input Capacitance                                                                                                         |                                                                       | C <sub>iss</sub>     | _        | -        | 500        | pF   |

| Output Capacitance                                                                                                        | V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0<br>f = 1 MHz              | Coss                 | _        | _        | 300        |      |

| Transfer Capacitance                                                                                                      | See Figure 6                                                          | C <sub>rss</sub>     | _        |          | 100        |      |

| WITCHING CHARACTERIST                                                                                                     | ICS*                                                                  |                      |          |          |            |      |

| Turn-On Delay Time                                                                                                        |                                                                       | td(on)               | _        |          | 50         | ns   |

| Rise Time                                                                                                                 | V <sub>DD</sub> = 25 V, I <sub>D</sub> = 5 A                          | t <sub>r</sub>       |          | _        | 150        |      |

| Turn-Off Delay Time                                                                                                       | R <sub>gen</sub> = 50 Ohms                                            | td(off)              | _        | _        | 100        |      |

| Fall Time                                                                                                                 |                                                                       | tf                   | _        | _        | 50         |      |

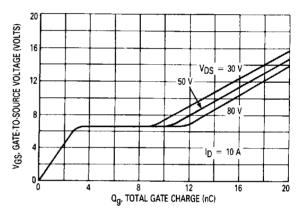

| Total Gate Charge                                                                                                         |                                                                       | $a_{g}$              |          | 16       | 25         | nC   |

| Gate-Source Charge                                                                                                        | $V_{DS} = 80 \text{ V, I}_{D} = 10 \text{ A}$ $V_{GS} = 10 \text{ V}$ | Q <sub>gs</sub>      | _        | 7        | _          |      |

| Gate-Drain Charge                                                                                                         | See Figure 4                                                          | O <sub>gd</sub>      | _        | 9        |            |      |

| OURCE-DRAIN DIODE CHA                                                                                                     | RACTERISTICS*                                                         |                      |          |          | ,          |      |

| Forward On-Voltage                                                                                                        | I <sub>S</sub> = 10 A                                                 | V <sub>SD</sub>      | _        | 2        | _          | Vdc  |

| Forward Turn-On Time                                                                                                      |                                                                       | ton                  | _        | 20       | _          | ns   |

| Reverse Recovery Time                                                                                                     |                                                                       | t <sub>rr</sub>      |          | 700      | _          | 1    |

<sup>\*</sup>Indicates Pulse Test Pulse Width = 300 µs max, Duty Cycle = 2%

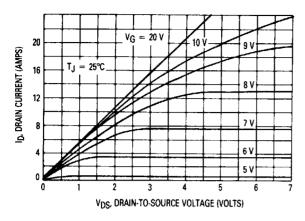

### TYPICAL CHARACTERISTICS

Figure 1. On-Region Characteristics

Figure 2. Gate Threshold Voltage Variation with Temperature

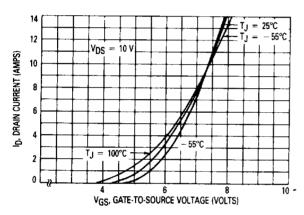

Figure 3. Transfer Characteristics

Figure 4. Stored Charge Variation

Figure 5. On-Resistance versus Drain Current

Figure 6. Capacitance Variation

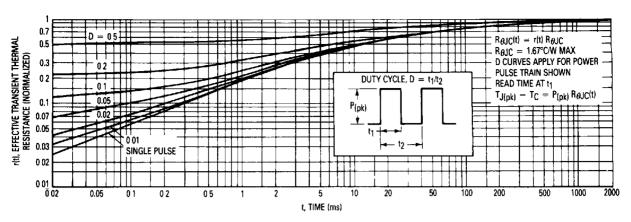

Figure 7. Thermal Response

### SAFE OPERATING AREA INFORMATION

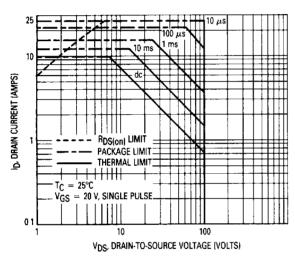

Figure 8. Maximum Rated Forward Biased Safe Operating Area

Figure 9. Maximum Rated Switching Safe Operating Area

### FORWARD BIASED SAFE OPERATING AREA

The FBSOA curves define the maximum drain-to-source voltage and drain current that a device can safely handle when it is forward biased, or when it is on, or being turned on. Because these curves include the limitations of simultaneous high voltage and high current, up to the rating of the device, they are especially useful to designers of linear systems. The curves are based on a case temperature of 25°C and a maximum junction temperature of 150°C. Limitations for repetitive pulses at various case temperatures can be determined by using the thermal response curves. Motorola Application Note, AN569, "Transient Thermal Resistance-General Data and Its Use" provides detailed instructions.

### **SWITCHING SAFE OPERATING AREA**

The switching safe operating area (SOA) of Figure 9 is the boundary that the load line may traverse without incurring damage to the MOSFET. The fundamental limits are the peak current, IDM and the breakdown voltage, V(BR)DSS. The switching SOA shown in Figure 9 is applicable for both turn-on and turn-off of the devices for switching times less than one microsecond.

The power averaged over a complete switching cycle must be less than:

Figure 10. Drain-to-Mirror On-Resistance versus Sense Resistance

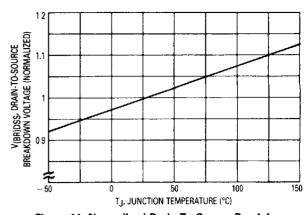

Figure 11. Normalized Drain-To-Source Breakdown Voltage versus Temperature

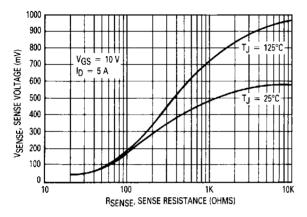

Figure 12. Sense Voltage versus Sense Resistance

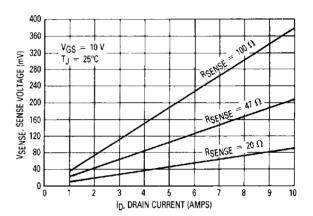

Figure 13. Drain Current versus Sense Voltage

### **USING SENSEFET PRODUCTS**

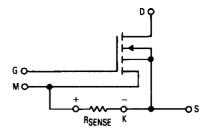

In practical applications, less sense current will flow than that calculated by using the current mirror ratio, n. Shown in Figure 1 is a model of the SENSEFET device. It is seen that RSENSE decreases the voltage across RDM(on) and decreases the sense current. An additional decrease in sense current occurs due to the decreased

> SENSE D R<sub>DM(on)</sub> VSENSE O rDS(on) RSENSE

Figure 14. SENSEFET Model

voltage across the mirror transistors. For this reason, a modified current mirror ratio, n' must be calculated. The equation to calculate n' is derived from the MOSFET square law model in the linear region,

$$n' = \frac{n}{1 - \frac{V_{SE}(V_{GS} - V_{T} - 1/2 \ V_{SE})}{V_{DS(on)}(V_{GS} - V_{T} - 1/2 \ V_{DS(on)})}}$$

$$n' \approx \frac{n}{1 - V_{SE}/V_{DS(on)}}$$

(1)

(for  $V_{SE}$ ,  $V_{DS(on)} << V_{GS} - V_T$ ).

Where, VGS = Gate-to-Source Voltage, VT = Gate-to-Source Threshold Voltage

and

$$V_{SE}$$

= Sense Voltage =  $\frac{RSENSE \ ID}{n'}$ . (2)

Hence, n' can be calculated from equation (1) and the result used in equation (2) to find the value of RSENSE. The value of RSENSE should be kept below 100  $\Omega$  for most accurate results.

### MTP10N10M

These equations were derived using die level source as the ground reference, neglecting contact and wire bond resistance to the source pin. In practice these parasitic resistances can cause significant errors at high currents, therefore it is mandatory to reference the gate drive signal and measure VDS(on) and VSENSE with respect to the Kelvin pin.

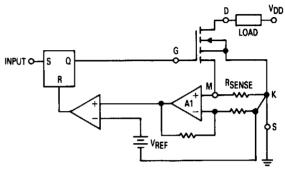

Figure 15 illustrates the correct SENSEFET configuration.

Figure 15. SENSEFET Configuration

### SENSEFET APPLICATIONS CONSIDERATIONS

- Double Pulse Suppression: In PWM circuits it is critically important to include double pulse suppression in the control circuit topology. If the current limit loop is allowed to oscillate at its natural frequency, failure of the SENSEFET device is likely due to over-dissipation. By syncing the current limit loop to the clock with a latch, double pulse suppression architectures solve this problem, and provide effective protection from overload stress.

- Noise Suppression: Noise pickup in the current sensing circuitry of SENSEFET systems can be a first order design issue. Layout, therefore is critical. In addition, some spike limiting capacitance across RSENSE is often desirable, provided that it is placed right at the current sensing circuitry's input terminals. To help with the layout problem, a Kelvin source connection is provided. The Kelvin connection gives SENSEFET devices separate power and signal source pins. This feature can be used advantageously with circuits such as the MC34129 current mode controller and MC33034 brushless dc motor drive, which also have dual grounds.

- Ground Loop Errors: Lossless current sensing is a technique that looks for 100 mV signals in a loop that may carry tens or even hundreds of amps. The potential for ground loop error in this kind of situation is a first order design consideration. In particular, current flowing from the SENSEFET device's source into a non-zero ground impedance can easily create voltage drops which are significant with respect to SENSEFET signal levels. Here again, the Kelvin connection is a useful tool. Tying the current limit circuitry's voltage reference to the Kelvin terminal as shown in Figure 16 eliminates errors that can be developed by high currents flowing in a power ground.

Set A1 gain to match sense voltage to VRFF at max In

Figure 16. Typical Current Sensing with a SENSEFET Device

- Temperature Stability: With very low values of RSENSE, temperature tracking depends primarily upon the matching of monolithic devices and is generally within a few percent for a 100°C change in temperature. As RSENSE is increased, however, temperature coefficient becomes less dependent upon matching and more a function of the power section's on-voltage. In the limit where RSENSE is very large, sense voltage approximates VDS(on) and tracks its temperature coefficient. It is not unusual to see VSENSE change less than 5% for a 100°C change in temperature provided that RSENSE is less than 10% of RDM(on). On the other hand, changes of 50% are not unusual when RSENSE exceeds RDM(on).

- There is a parasitic reverse diode on the current mirror MOSFET as well as the power MOSFET. Diode reverse recovery currents will cause a sense voltage spike that may have to be filtered from the sense circuitry.