# M36L0R8060T1 M36L0R8060B1

256 Mbit (Multiple Bank, Multi-Level, Burst) Flash Memory and 64 Mbit (Burst) PSRAM, 1.8V Supply, Multi-Chip Package

#### **FEATURES SUMMARY**

- MULTI-CHIP PACKAGE

- 1 die of 256 Mbit (16Mb x16, Multiple Bank, Multi-level, Burst) Flash Memory

- 1 die of 64 Mbit (4Mb x16) Pseudo SRAM

- SUPPLY VOLTAGE

- V<sub>DDF</sub> = V<sub>CCP</sub> = V<sub>DDQF</sub> = 1.7 to 1.95V

- V<sub>PPF</sub> = 9V for fast program (12V tolerant)

- ELECTRONIC SIGNATURE

- Manufacturer Code: 20h

- Top Device Code

- M36L0R8060T1: 880Dh

- Bottom Device Code M36L0R8060B1: 880Eh

- PACKAGE

- Compliant with Lead-Free Soldering Processes

- Lead-Free Versions

#### **FLASH MEMORY**

- SYNCHRONOUS / ASYNCHRONOUS READ

- Synchronous Burst Read mode: 54MHz

- Asynchronous Page Read mode

- Random Access: 85ns

- SYNCHRONOUS BURST READ SUSPEND

- PROGRAMMING TIME

- 10µs typical Word program time using Buffer Enhanced Factory Program command

- MEMORY ORGANIZATION

- Multiple Bank Memory Array: 16 Mbit Banks

- Parameter Blocks (Top or Bottom location)

- DUAL OPERATIONS

- program/erase in one Bank while read in others

- No delay between read and write operations

- SECURITY

- 64 bit unique device number

- 2112 bit user programmable OTP Cells

Figure 1. Package

#### BLOCK LOCKING

- All blocks locked at power-up

- Any combination of blocks can be locked with zero latency

- WP<sub>F</sub> for Block Lock-Down

- Absolute Write Protection with V<sub>PPF</sub> = V<sub>SS</sub>

- COMMON FLASH INTERFACE (CFI)

- 100,000 PROGRAM/ERASE CYCLES per BLOCK

#### **PSRAM**

- ACCESS TIME: 70ns

- ASYNCHRONOUS PAGE READ

- Page Size: 16 words

- Subsequent read within page: 20ns

- LOW POWER FEATURES

- Temperature Compensated Refresh (TCR)

- Partial Array Refresh (PAR)

- Deep Power-Down (DPD) Mode

- SYNCHRONOUS BURST READ/WRITE

June 2005 1/18

# **TABLE OF CONTENTS**

| FEATURES SUMMARY                                       | . 1 |

|--------------------------------------------------------|-----|

| FLASH MEMORY                                           | . 1 |

| Figure 1. Package                                      | . 1 |

| PSRAM                                                  | . 1 |

|                                                        |     |

| SUMMARY DESCRIPTION                                    |     |

| Flash Memory Component                                 | . 4 |

| PSRAM Component                                        | . 4 |

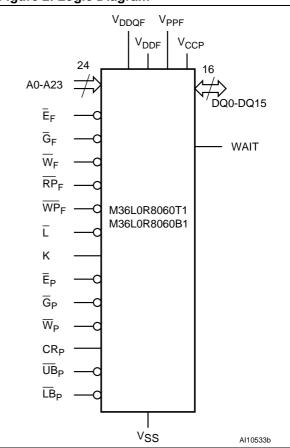

| Figure 2. Logic Diagram                                |     |

| Table 1. Signal Names                                  |     |

| Figure 3. TFBGA Connections (Top view through package) | . 6 |

| SIGNAL DESCRIPTIONS                                    | . 7 |

| Address Inputs (A0-A23).                               |     |

| Data Input/Output (DQ0-DQ15).                          |     |

| Latch Enable (L)                                       |     |

| Clock (K)                                              |     |

| Wait (WAIT).                                           |     |

| Flash Chip Enable ( $\overline{\mathbb{E}}_{F}$ )      |     |

| Flash Output Enable (G <sub>F</sub> )                  |     |

| Flash Write Enable ( $\overline{W}_{F}$ )              |     |

| Flash Write Protect (WP <sub>F</sub> ).                |     |

| Flash Reset (RP <sub>F</sub> ).                        |     |

| PSRAM Chip Enable input ( $\overline{E}_{P}$ )         |     |

| PSRAM Write Enable (WP)                                |     |

| PSRAM Output Enable (GP)                               |     |

| PSRAM Upper Byte Enable (UB <sub>P</sub> )             | . 8 |

| PSRAM Lower Byte Enable (\overline{LB}_P)              | . 8 |

| PSRAM Configuration Register Enable (CR <sub>P</sub> ) |     |

| V <sub>DDF</sub> Supply Voltage                        |     |

| V <sub>CCP</sub> Supply Voltage                        |     |

| V <sub>DDQF</sub> Supply Voltage                       |     |

| V <sub>PPF</sub> Program Supply Voltage                |     |

| V <sub>SS</sub> Ground                                 | . 8 |

| FUNCTIONAL DESCRIPTION                                 | . 9 |

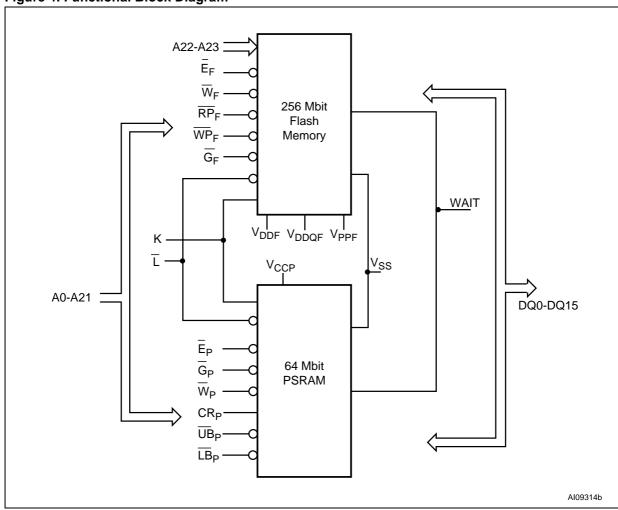

| Figure 4. Functional Block Diagram                     | . 9 |

| Table 2. Main Operating Modes                          |     |

| MAXIMUM RATING                                         | 11  |

| Table 3. Absolute Maximum Ratings                      |     |

|                                                        |     |

| DC AND AC PARAMETERS                                   | 12  |

# M36L0R8060T1, M36L0R8060B1

|    | Table 4.  | Operating and AC Measurement Conditions                                                                                                               | 12 |

|----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | Figure 5. | AC Measurement I/O Waveform                                                                                                                           | 12 |

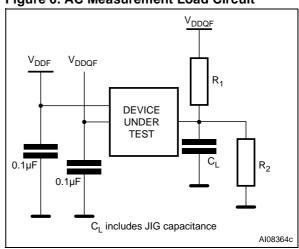

|    | Figure 6. | AC Measurement Load Circuit                                                                                                                           | 12 |

|    | Table 5.  | Device Capacitance                                                                                                                                    | 12 |

|    | Table 6.  | Flash Memory DC Characteristics - Currents                                                                                                            | 13 |

|    | Table 7.  | Flash Memory DC Characteristics - Voltages                                                                                                            | 14 |

|    | Table 8.  | PSRAM DC Characteristics                                                                                                                              | 14 |

| PΑ | CKAGE N   | IECHANICAL                                                                                                                                            | 15 |

|    | •         | TFBGA88 8x10mm, 8x10 ball array - 0.8mm pitch, Bottom View Package Outline Stacked TFBGA88 8x10mm - 8x10 active ball array, 0.8mm pitch, Package Data |    |

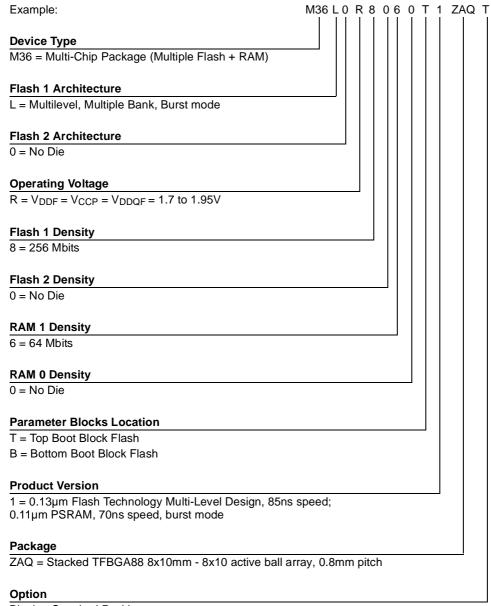

| PΑ | RT NUMB   | ERING                                                                                                                                                 | 16 |

|    | Table 10. | Ordering Information Scheme                                                                                                                           | 16 |

| RE | VISION H  | ISTORY                                                                                                                                                | 17 |

|    | Table 11. | Document Revision History                                                                                                                             | 17 |

#### SUMMARY DESCRIPTION

The M36L0R8060T1 and M36L0R8060B1 combine two memory devices in a Multi-Chip Package:

- a 256-Mbit, Multiple Bank Flash memory, the M30L0R8000T0 or M30L0R8000B0,

- a 64-Mbit PseudoSRAM, the M69KB096AA.

This document should be read in conjunction with the M30L0R8000x0 and M69KB096AA datasheets.

Recommended operating conditions do not allow more than one memory to be active at the same time

The memory is offered in a Stacked TFBGA88 (8x10mm, 8x10 ball array, 0.8mm pitch) package.

In addition to the standard version, the package is also available in Lead-free version, in compliance with JEDEC Std J-STD-020B, the ST ECOPACK 7191395 Specification, and the RoHS (Restriction of Hazardous Substances) directive. All packages are compliant with Lead-free soldering processes.

#### **Flash Memory Component**

For detailed information on how to use the Flash memory component, refer to the M30L0R8000(T/B)0 datasheet which is available from your local STMicroelectronics distributor.

The memory is supplied with all the bits erased (set to '1').

#### **PSRAM Component**

For detailed information on how to use the PSRAM component, see the M69KB096AA datasheet that is available from your local STMicroelectronics distributor.

Figure 2. Logic Diagram

**Table 1. Signal Names**

| able 1. Olynar Names        |                                                        |  |  |  |  |

|-----------------------------|--------------------------------------------------------|--|--|--|--|

| A0-A23                      | Address Inputs                                         |  |  |  |  |

| DQ0-DQ15                    | Common Data Input/Output                               |  |  |  |  |

| Ī                           | Latch Enable input for Flash memory and PSRAM          |  |  |  |  |

| K                           | Burst Clock for Flash memory and PSRAM                 |  |  |  |  |

| WAIT                        | Wait Data in Burst Mode for Flash memory and PSRAM     |  |  |  |  |

| $V_{DDF}$                   | Flash Memory Power Supply                              |  |  |  |  |

| V <sub>DDQF</sub>           | Flash Power Supply for I/O Buffers                     |  |  |  |  |

| V <sub>PPF</sub>            | Flash Optional Supply Voltage for Fast Program & Erase |  |  |  |  |

| V <sub>SS</sub>             | Ground                                                 |  |  |  |  |

| V <sub>CCP</sub>            | PSRAM Power Supply                                     |  |  |  |  |

| NC                          | Not Connected Internally                               |  |  |  |  |

| DU                          | Do Not Use as Internally Connected                     |  |  |  |  |

| Flash Memory Signals        |                                                        |  |  |  |  |

| E <sub>F</sub>              | Chip Enable input                                      |  |  |  |  |

| G <sub>F</sub>              | Output Enable Input                                    |  |  |  |  |

| WF                          | Write Enable input                                     |  |  |  |  |

| RP <sub>F</sub>             | Reset input                                            |  |  |  |  |

| WPF                         | Write Protect input                                    |  |  |  |  |

| PSRAM Signals               |                                                        |  |  |  |  |

| Ē <sub>P</sub>              | Chip Enable Input                                      |  |  |  |  |

| G <sub>P</sub>              | Output Enable Input                                    |  |  |  |  |

| $\overline{\mathbb{W}}_{P}$ | Write Enable Input                                     |  |  |  |  |

| CR <sub>P</sub>             | Configuration Register Enable Input                    |  |  |  |  |

| <del>UB</del> <sub>P</sub>  | Upper Byte Enable Input                                |  |  |  |  |

| LB <sub>P</sub>             | Lower Byte Enable Input                                |  |  |  |  |

|                             |                                                        |  |  |  |  |

Figure 3. TFBGA Connections (Top view through package)

| г | 1                               | 2                  | 3                  | 4                   | 5                             | 6                  | 7                  | 8                  |

|---|---------------------------------|--------------------|--------------------|---------------------|-------------------------------|--------------------|--------------------|--------------------|

| A | DU                              | (DU)               |                    |                     |                               |                    | (DU)               | (DU)               |

| В | ( A4                            | ( A18 )            | ( A19 )            | (Vss.)              | V <sub>DDF</sub>              | (NC)               | ( A21 )            | (A11)              |

| С | ( A5                            | (EB <sub>P</sub> ) | (A23)              | (V <sub>SS</sub> )  | ( NC )                        | (K)                | (A22)              | A12                |

| D | ( A3 )                          | (A17)              | (NC)               | (V <sub>PPF</sub> ) | $(\overline{\mathbb{W}}_{P})$ | $(\bar{E}_P)$      | ( A9 )             | (A13)              |

| E | ( A2 )                          | (A7)               | (NC)               | $(\overline{WP}_F)$ | $(\bar{\tau})$                | (A20)              | (A10)              | (A15)              |

| F | ( A1 )                          | ( A6               | (UB <sub>P</sub> ) | $(\overline{RP}_F)$ | $(\overline{W}_{F})$          | (A8)               | (A14)              | ( A16 )            |

| G | ( A0 )                          | DQ8                | DQ2                | (DQ10)              | DQ5                           | (DQ13)             | (WAIT)             | (NC)               |

| н | $(\overline{G}_P)$              | (DQ0)              | (DQ1)              | (DQ3)               | (DQ12)                        | (DQ14)             | (DQ7)              | (NC)               |

| J | (NC)                            | $(\bar{G}_F)$      | (DQ9)              | (DQ11)              | DQ4                           | (DQ6)              | (DQ15)             | 'VDDQF,            |

| К | $\left(\overline{E}_{F}\right)$ | (DU)               | (DU)               | (NC)                | (VCCP)                        | (NC)               | V <sub>DDQF</sub>  | (CR <sub>P</sub> ) |

| L | (Vss.)                          | (V <sub>SS</sub> ) | V <sub>DDQF</sub>  | (V <sub>DDF</sub> ) | (V <sub>SS</sub> )            | (V <sub>SS</sub> ) | (V <sub>SS</sub> ) | (Vss.)             |

| М | DU                              | (DU)               |                    |                     |                               |                    | (DU)               | (DU)               |

#### SIGNAL DESCRIPTIONS

See Figure 2., Logic Diagram and Table 1., Signal Names, for a brief overview of the signals connected to this device.

Address Inputs (A0-A23). Addresses A0-A21 are common inputs for the Flash memory and PSRAM components. The other lines (A23-A22) are inputs for the Flash memory component only.

The Address Inputs select the cells in the memory array to access during Bus Read operations. During Bus Write operations they control the commands sent to the Command Interface of the internal state machine. The Flash memory is accessed through the Chip Enable  $\underline{\text{signal}}$  ( $\overline{\text{E}_F}$ ) and through the Write Enable signal ( $\overline{\text{W}_F}$ ), while the PSRAM is accessed through the Chip Enable signal ( $\overline{\text{E}_P}$ ) and the Write Enable signal ( $\overline{\text{W}_P}$ ).

**Data Input/Output (DQ0-DQ15).** The Data I/O output the data stored at the selected address during a Bus Read operation or input a command or the data to be programmed during a Bus Write operation.

For the PSRAM component, the upper Byte Data Inputs/Outputs (DQ8-DQ15) carry the data to or from the upper part of the selected address when Upper Byte Enable (UBp) is driven Low. The lower Byte Data Inputs/Outputs (DQ0-DQ7) carry the data to or from the lower part of the selected address when Lower Byte Enable (LBp) is driven Low. When both UBp and LBp are disabled, the Data Inputs/ Outputs are high impedance.

Latch Enable (L). The Latch Enable pin is common to the Flash memory and PSRAM components.

For details of how the Latch Enable signal behaves, please refer to the datasheets of the respective memory components: M69KB096AA for the PSRAM and M30L0R8000T/B0 for the Flash memory.

**Clock (K).** The Clock input pin is common to the Flash memory and PSRAM components.

For details of how the Clock signal behaves, please refer to the datasheets of the respective memory components: M69KB096AA for the PSRAM and M30L0R8000T/B0 for the Flash memory.

**Wait (WAIT).** WAIT is an output pin common to the Flash memory and PSRAM components. However the WAIT signal does not behave in the same way for the PSRAM and the Flash memory.

For details of how it behaves, please refer to the M69KB096AA datasheet for the PSRAM and to the M30L0R8000T/B0 datasheet for the Flash memory.

Flash Chip Enable  $(\overline{E}_F)$ . The Flash Chip Enable input activates the control logic, input buffers, de-

coders and sense amplifiers of the Flash memory component. When Chip Enable is Low,  $V_{IL}$ , and Reset is High,  $V_{IH}$ , the device is in active mode. When Chip Enable is at  $V_{IH}$  the Flash memory is deselected, the outputs are high impedance and the power consumption is reduced to the standby level.

Flash Output Enable ( $\overline{G_F}$ ). The Output Enable pin controls the data outputs during Flash memory Bus Read operations.

Flash Write Enable ( $\overline{W}_F$ ). The Write Enable controls the Bus Write operation of the Flash memory's Command Interface. The data and address inputs are latched on the rising edge of Chip Enable or Write Enable whichever occurs first.

Flash Write Protect (WP<sub>F</sub>). Write Protect is an input that gives an additional hardware protection for each block. When Write Protect is Low,  $V_{IL}$ , Lock-Down is enabled and the protection status of the Locked-Down blocks cannot be changed. When Write Protect is at High,  $V_{IH}$ , Lock-Down is disabled and the Locked-Down blocks can be locked or unlocked. (See the Lock Status Table in the M30L0R8000T0/B0 datasheet).

Flash Reset (RPF). The Reset input provides a hardware reset of the Flash memory. When Reset is at V<sub>IL</sub>, the memory is in Reset mode: the outputs are high impedance and the current consumption is reduced to the Reset Supply Current I<sub>DD2</sub>. Refer to Table 6., Flash Memory DC Characteristics - Currents, for the value of I<sub>DD2</sub>. After Reset all blocks are in the Locked state and the Configuration Register is reset. When Reset is at V<sub>IH</sub>, the device is in normal operation. Exiting Reset mode the device enters Asynchronous Read mode, but a negative transition of Chip Enable or Latch Enable is required to ensure valid data outputs.

The Reset pin can be interfaced with 3V logic without any additional circuitry. It can be tied to  $V_{RPH}$  (refer to Table 7., Flash Memory DC Characteristics - Voltages).

**PSRAM Chip Enable input (Ep).** The Chip Enable input activates the PSRAM when driven Low (asserted). When deasserted (V<sub>IH</sub>), the device is disabled, and goes automatically in low-power Standby mode or Deep Power-down mode.

**PSRAM Write Enable (W<sub>P</sub>).** Write Enable, W<sub>P</sub>, controls the Bus Write operation of the PSRAM. When asserted (V<sub>IL</sub>), the device is in Write mode and Write operations can be performed either to the configuration registers or to the memory array.

**PSRAM Output Enable (GP). O**utput Enable, GP, provides a high speed tri-state control, allowing fast read/write cycles to be achieved with the common I/O data bus.

**PSRAM Upper Byte Enable (UBp).** The Upper Byte En-able, UBp, gates the data on the Upper Byte Data Inputs/Outputs (DQ8-DQ15) to or from the upper part of the selected address during a Write or Read operation.

**PSRAM Lower Byte Enable (LBp).** The Lower Byte Enable, LBp, gates the data on the Lower Byte Data Inputs/Outputs (DQ0-DQ7) to or from the lower part of the selected address during a Write or Read operation.

If both  $\overline{\text{LB}_{P}}$  and  $\overline{\text{UB}_{P}}$  are disabled (High) during an operation, the device will disable the data bus from receiving or transmitting data. Although the device will seem to be deselected, it remains in an active mode as long as  $\overline{\text{E}_{P}}$  remains Low.

#### PSRAM Configuration Register Enable (CR<sub>P</sub>).

When this signal is driven High, V<sub>IH</sub>, Write operations load either the value of the Refresh Configuration Register (RCR) or the Bus configuration register (BCR).

**V<sub>DDF</sub> Supply Voltage.** V<sub>DDF</sub> provides the power supply to the internal core of the Flash memory. It is the main power supply for all Flash memory operations (Read, Program and Erase).

**V<sub>CCP</sub> Supply Voltage.**  $V_{CCP}$  provides the power supply to the internal core of the PSRAM device. It is the main power supply for all PSRAM operations.

$m f V_{DDQF}$  Supply Voltage.  $m f V_{DDQF}$  provides the power supply for the Flash I/O pins. This allows all Outputs to be powered independently of the Flash core power supplies,  $m f V_{DDF}$  and  $m f V_{CCP}$ .

**VPPF Program Supply Voltage.** VPPF is both a Flash control input and a Flash power supply pin. The two functions are selected by the voltage range applied to the pin.

If  $V_{PPF}$  is kept in a low voltage range (0V to  $V_{DDQF}$ )  $V_{PPF}$  is seen as a control input. In this case a voltage lower than  $V_{PPLK}$  gives an absolute protection against Program or Erase, while  $V_{PPF} > V_{PP1}$  enables these functions (see Tables 6 and 7, DC Characteristics for the relevant values).  $V_{PPF}$  is only sampled at the beginning of a Program or Erase; a change in its value after the operation has started does not have any effect and Program or Erase operations continue.

If V<sub>PPF</sub> is in the range of V<sub>PPH</sub> it acts as a power supply pin. In this condition V<sub>PPF</sub> must be stable until the Program/Erase algorithm is completed.

$V_{SS}$  Ground.  $V_{SS}$  is the common ground reference for all voltage measurements in the Flash (core and I/O Buffers) and PSRAM chips. It must be connected to the system ground.

Note: Each Flash memory device in a system should have their supply voltage (V<sub>DDF</sub>) and the program supply voltage V<sub>PPF</sub> decoupled with a 0.1µF ceramic capacitor close to the pin (high frequency, inherently low inductance capacitors should be as close as possible to the package). See Figure 6., AC Measurement Load Circuit. The PCB track widths should be sufficient to carry the required V<sub>PPF</sub> program and erase currents.

# **FUNCTIONAL DESCRIPTION**

The PSRAM and Flash memory components have separate power supplies but share the same grounds. They are distinguished by two Chip Enable inputs:  $\bar{E}_F$  for the Flash memory and  $\bar{E}_P$  for the PSRAM.

Recommended operating conditions do not allow more than one device to be active at a time. The most common example is simultaneous read operations on one of the Flash memory and the PSRAM components which would result in a data bus contention. Therefore it is recommended to put the other devices in the high impedance state when reading the selected device.

Figure 4. Functional Block Diagram

# M36L0R8060T1, M36L0R8060B1

**Table 2. Main Operating Modes**

| Operation                                | Ē <sub>F</sub>  | G <sub>F</sub>                    | W <sub>F</sub>  | L <sub>F</sub>                 | RP <sub>F</sub> | WAIT <sub>F</sub> <sup>(4)</sup> | Ε <sub>P</sub>  | CR <sub>P</sub> | G <sub>P</sub>  | $\overline{W}_{P}$ | LB <sub>P</sub> ,UB <sub>P</sub> | DQ15-DQ0                                 |

|------------------------------------------|-----------------|-----------------------------------|-----------------|--------------------------------|-----------------|----------------------------------|-----------------|-----------------|-----------------|--------------------|----------------------------------|------------------------------------------|

| Flash Read                               | V <sub>IL</sub> | V <sub>IL</sub>                   | V <sub>IH</sub> | V <sub>IL</sub> <sup>(2)</sup> | V <sub>IH</sub> |                                  |                 |                 |                 | Flash Data Out     |                                  |                                          |

| Flash Write                              | V <sub>IL</sub> | V <sub>IH</sub>                   | V <sub>IL</sub> | V <sub>IL</sub> <sup>(2)</sup> | V <sub>IH</sub> |                                  | [               | PSRAM           | I must I        | be disa            | bled.                            | Flash Data In                            |

| Flash Address<br>Latch                   | VIL             | Х                                 | V <sub>IH</sub> | VIL                            | V <sub>IH</sub> |                                  |                 |                 |                 |                    |                                  | Flash Data Out<br>or Hi-Z <sup>(3)</sup> |

| Flash Output<br>Disable                  | V <sub>IL</sub> | V <sub>IH</sub>                   | V <sub>IH</sub> | Х                              | V <sub>IH</sub> |                                  |                 |                 |                 |                    |                                  | Hi-Z                                     |

| Flash Standby                            | V <sub>IH</sub> | Х                                 | Х               | Х                              | V <sub>IH</sub> | Hi-Z                             | Ar              | ny PSR.         | AM mo           | de is al           | lowed.                           | Hi-Z                                     |

| Flash Reset                              | Х               | Χ                                 | Х               | Х                              | VIL             | Hi-Z                             |                 |                 |                 |                    |                                  | Hi-Z                                     |

| PSRAM Read                               |                 |                                   |                 |                                |                 |                                  | V <sub>IL</sub> | VIL             | VIL             | VIH                | V <sub>IL</sub>                  | PSRAM data out                           |

| PSRAM Write                              | Th              | e Flas                            | sh men          | nory mu                        | ust be d        | disabled                         | V <sub>IL</sub> | V <sub>IL</sub> | Х               | V <sub>IL</sub>    | V <sub>IL</sub>                  | PSRAM data in                            |

| PSRAM Write<br>Configuration<br>Register |                 | The Flash memory must be disabled |                 |                                |                 |                                  | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | VIL                | Х                                | PSRAM data in                            |

| PSRAM<br>Standby                         |                 | Any Flash mode is allowed.        |                 |                                |                 |                                  | V <sub>IH</sub> | V <sub>IL</sub> | Х               | Х                  | Х                                | Hi-Z                                     |

| PSRAM Deep<br>Power-Down                 |                 |                                   |                 |                                |                 |                                  | V <sub>IH</sub> | Х               | Х               | Х                  | Х                                | Hi-Z                                     |

47/ 10/18

Note: 1.  $\underline{X} = Don't care$ . 2.  $\underline{L}_F can be tied to V_{IH}$  if the valid address has been previously latched.

Depends on Gr.

WAIT signal polarity is configured using the Set Configuration Register command. See the M30L0R8000T0 datasheet for details.

# **MAXIMUM RATING**

Stressing the device above the rating listed in the Absolute Maximum Ratings table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not im-

plied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

**Table 3. Absolute Maximum Ratings**

| Symbol                                                     | Parameter                                      | V    | /alue                  | Unit   |

|------------------------------------------------------------|------------------------------------------------|------|------------------------|--------|

| Symbol                                                     | Farameter                                      | Min  | Max                    | - Onit |

| T <sub>A</sub>                                             | Ambient Operating Temperature                  | -25  | 85                     | °C     |

| T <sub>BIAS</sub>                                          | Temperature Under Bias                         | -25  | 85                     | °C     |

| T <sub>STG</sub>                                           | Storage Temperature                            | -65  | 125                    | °C     |

| T <sub>LEAD</sub>                                          | Lead Temperature During Soldering              |      | (1)                    | °C     |

| V <sub>IO</sub>                                            | Input or Output Voltage                        | -0.5 | V <sub>DDQ</sub> + 0.3 | V      |

| V <sub>DDF</sub> , V <sub>DDQF</sub> ,<br>V <sub>CCP</sub> | Core and Input/Output Supply Voltages          | -0.2 | 2.45                   | V      |

| V <sub>PPF</sub>                                           | Flash Program Voltage                          | -0.2 | 12.6                   | V      |

| Io                                                         | Output Short Circuit Current                   |      | 100                    | mA     |

| t <sub>VPPFH</sub>                                         | Time for V <sub>PPF</sub> at V <sub>PPFH</sub> |      | 100                    | hours  |

Note: 1. Compliant with the JEDEC Std J-STD-020B (for small body, Sn-Pb or Pb assembly), the ST ECOPACK ® 7191395 specification, and the European directive on Restrictions on Hazardous Substances (RoHS) 2002/95/EU.

**5**

# DC AND AC PARAMETERS

This section summarizes the operating measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC characteristics Tables that follow, are derived from tests performed under the Measurement

Conditions summarized in Table 4., Operating and AC Measurement Conditions. Designers should check that the operating conditions in their circuit match the operating conditions when relying on the quoted parameters.

**Table 4. Operating and AC Measurement Conditions**

| Parameter                                                   | Flash I                | Memory                 | PSF             | RAM  | Unit   |

|-------------------------------------------------------------|------------------------|------------------------|-----------------|------|--------|

| Farameter                                                   | Min                    | Max                    | Min             | Max  | - Onit |

| V <sub>DDF</sub> Supply Voltage                             | 1.7                    | 1.95                   | _               | -    | V      |

| V <sub>CCP</sub> Supply Voltage                             | -                      | _                      | 1.7             | 1.95 | V      |

| V <sub>DDQF</sub> Supply Voltage                            | 1.7                    | 1.95                   | _               | -    | V      |

| V <sub>PPF</sub> Supply Voltage (Factory environment)       | 8.5                    | 9.5                    | _               | _    | V      |

| V <sub>PPF</sub> Supply Voltage (Application environment)   | -0.4                   | V <sub>DDQF</sub> +0.4 | -               | _    | V      |

| Ambient Operating Temperature                               | -25                    | 85                     | -25             | 85   | °C     |

| Load Capacitance (C <sub>L</sub> )                          | 3                      | 30                     | 3               | 0    | pF     |

| Output Circuit Resistors (R <sub>1</sub> , R <sub>2</sub> ) | 16                     | 6.7                    | 16              | 6.7  | kΩ     |

| Input Rise and Fall Times                                   |                        | 5                      |                 |      | ns     |

| Input Pulse Voltages                                        | 0 to V <sub>DDQF</sub> |                        | 0 to V          | DDQF | V      |

| Input and Output Timing Ref. Voltages                       | V <sub>DDQF</sub> /2   |                        | V <sub>DD</sub> | QF/2 | V      |

Figure 5. AC Measurement I/O Waveform

Figure 6. AC Measurement Load Circuit

**Table 5. Device Capacitance**

| Symbol Parameter |                    | Test Condition        | Min | Max | Unit |

|------------------|--------------------|-----------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = 0V$         |     | 14  | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V |     | 18  | pF   |

Note: Sampled only, not 100% tested.

**Table 6. Flash Memory DC Characteristics - Currents**

| Symbol                          | Parameter                                            | Test Condition                                                                         | Тур | Max | Unit |

|---------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------|-----|-----|------|

| ILI                             | Input Leakage Current                                | $0V \leq V_{IN} \leq V_{DDQF}$                                                         |     | ±1  | μA   |

| I <sub>LO</sub>                 | Output Leakage Current                               | $0V \le V_{OUT} \le V_{DDQF}$                                                          |     | ±1  | μA   |

|                                 | Supply Current<br>Asynchronous Read (f=5MHz)         | $\overline{E} = V_IL,  \overline{G} = V_IH$                                            | 13  | 15  | mA   |

|                                 |                                                      | 4 Word                                                                                 | 16  | 18  | mA   |

| I <sub>DD1</sub>                | Supply Current                                       | 8 Word                                                                                 | 18  | 20  | mA   |

|                                 | Synchronous Read (f=54MHz)                           | 16 Word                                                                                | 23  | 25  | mA   |

|                                 |                                                      | Continuous                                                                             | 25  | 27  | mA   |

| I <sub>DD2</sub>                | Supply Current (Reset)                               | $\overline{RP} = V_{SS} \pm 0.2V$                                                      | 50  | 110 | μA   |

| I <sub>DD3</sub>                | Supply Current (Standby)                             | $\overline{E} = V_{DDQF} \pm 0.2V$ $K=V_{SS}$                                          | 50  | 110 | μА   |

| I <sub>DD4</sub>                | Supply Current (Automatic Standby)                   | $\overline{E} = V_{IL}, \overline{G} = V_{IH}$                                         | 50  | 110 | μA   |

|                                 | Cupality Comment (Draguesa)                          | V <sub>PP</sub> = V <sub>PPH</sub>                                                     | 8   | 20  | mA   |

| . (1)                           | Supply Current (Program)                             | $V_{PP} = V_{DD}$                                                                      | 10  | 25  | mA   |

| I <sub>DD5</sub> <sup>(1)</sup> | Supply Current (Erase)                               | V <sub>PP</sub> = V <sub>PPH</sub>                                                     | 8   | 20  | mA   |

|                                 | Supply Current (Erase)                               | V <sub>PP</sub> = V <sub>DD</sub>                                                      | 10  | 25  | mA   |

| (1.2)                           | Supply Current                                       | Program/Erase in one Bank,<br>Asynchronous Read in another<br>Bank                     | 23  | 40  | mA   |

| I <sub>DD6</sub> (1,2)          | (Dual Operations)                                    | Program/Erase in one Bank,<br>Synchronous Read (Continuous<br>f=54MHz) in another Bank | 35  | 52  | mA   |

| I <sub>DD7</sub> <sup>(1)</sup> | Supply Current Program/ Erase<br>Suspended (Standby) | $\overline{E} = V_{DDQF} \pm 0.2V$ $K=V_{SS}$                                          | 50  | 110 | μΑ   |

|                                 | V Supply Current (Program)                           | V <sub>PP</sub> = V <sub>PPH</sub>                                                     | 2   | 5   | mA   |

| , (1)                           | V <sub>PP</sub> Supply Current (Program)             | $V_{PP} = V_{DD}$                                                                      | 0.2 | 5   | μA   |

| I <sub>PP1</sub> <sup>(1)</sup> | V <sub>PP</sub> Supply Current (Erase)               | V <sub>PP</sub> = V <sub>PPH</sub>                                                     | 2   | 5   | mA   |

|                                 | VPP Supply Current (crase)                           | $V_{PP} = V_{DD}$                                                                      | 0.2 | 5   | μA   |

| I <sub>PP2</sub>                | V <sub>PP</sub> Supply Current (Read)                | V <sub>PP</sub> ≤ V <sub>DD</sub>                                                      | 0.2 | 5   | μA   |

| I <sub>PP3</sub> <sup>(1)</sup> | V <sub>PP</sub> Supply Current (Standby)             | $V_{PP} \le V_{DD}$                                                                    | 0.2 | 5   | μA   |

Note: 1. Sampled only, not 100% tested.

2. VDD Dual Operation current is the sum of read and program or erase currents.

**Table 7. Flash Memory DC Characteristics - Voltages**

| Symbol            | Parameter                               | Test Condition           | Min                     | Тур | Max                     | Unit |

|-------------------|-----------------------------------------|--------------------------|-------------------------|-----|-------------------------|------|

| VIL               | Input Low Voltage                       |                          | 0                       |     | 0.4                     | V    |

| V <sub>IH</sub>   | Input High Voltage                      |                          | V <sub>DDQF</sub> – 0.4 |     | V <sub>DDQF</sub> + 0.4 | V    |

| V <sub>OL</sub>   | Output Low Voltage                      | $I_{OL} = 100 \mu A$     |                         |     | 0.1                     | V    |

| Voн               | Output High Voltage                     | I <sub>OH</sub> = -100μA | V <sub>DDQF</sub> – 0.1 |     |                         | V    |

| V <sub>PP1</sub>  | V <sub>PP</sub> Program Voltage-Logic   | Program, Erase           | 1.3                     | 1.8 | 3.3                     | V    |

| V <sub>PPH</sub>  | V <sub>PP</sub> Program Voltage Factory | Program, Erase           | 8.5                     | 9.0 | 9.5                     | V    |

| V <sub>PPLK</sub> | Program or Erase Lockout                |                          |                         |     | 0.4                     | V    |

| V <sub>LKO</sub>  | V <sub>DD</sub> Lock Voltage            |                          |                         |     | 1                       | V    |

| V <sub>RPH</sub>  | RP pin Extended High Voltage            |                          |                         |     | 3.3                     | V    |

**Table 8. PSRAM DC Characteristics**

| Symbol                           | Parameter                                               | Test Condition                                            | Min.  | Тур                 | Max. | Unit                   |    |

|----------------------------------|---------------------------------------------------------|-----------------------------------------------------------|-------|---------------------|------|------------------------|----|

| I <sub>CC1</sub> <sup>(1)</sup>  | Operating Current:<br>Asynchronous Random<br>Read/Write |                                                           | 70ns  |                     |      | 25                     | mA |

| I <sub>CC1P</sub> <sup>(1)</sup> | Operating Current:<br>Asynchronous Page<br>Read         |                                                           | 70ns  |                     |      | 15                     | mA |

| . (1)                            | Operating Current:                                      | $V_{CC} = V_{IH} \text{ or } V_{IL},$<br>$E = V_{IL},$    | 80MHz |                     |      | 35                     | mA |

| I <sub>CC2</sub> <sup>(1)</sup>  | Initial Access,<br>Burst Read/Write                     | I <sub>OUT</sub> = 0mA                                    | 66MHz |                     |      | 30                     | mA |

| . (1)                            | Operating Current:                                      |                                                           | 80MHz |                     |      | 18                     | mA |

| I <sub>CC3R</sub> <sup>(1)</sup> | Continuous Burst Read                                   |                                                           | 66MHz |                     |      | 15                     | mA |

| I <sub>CC3W</sub> <sup>(1)</sup> | Operating Current:                                      |                                                           | 80MHz |                     |      | 35                     | mA |

| ICC3W                            | Continuous Burst Write                                  |                                                           | 66MHz |                     |      | 30                     | mA |

| I <sub>SB</sub> <sup>(2)</sup>   | V <sub>CC</sub> Standby Current                         | $V_{CC} = V_{CCQ}$ or 0V,<br>$\overline{E} = V_{IH}$      |       |                     |      | 120                    | μA |

| ILI                              | Input Leakage Current                                   | $0V \leq V_{IN} \leq V_{CC}$                              |       |                     |      | 1                      | μΑ |

| ILO                              | Output Leakage Current                                  | $\overline{G} = V_{IH} \text{ or } \overline{E} = V_{IH}$ |       |                     |      | 1                      | μA |

| I <sub>ZZ</sub>                  | Deep-Power Down<br>Current                              | $V_{IN} = V_{IH}$ or $V_{IL}$                             |       |                     | 10   |                        | μA |

| V <sub>IH</sub>                  | Input High Voltage                                      |                                                           |       | 1.4                 |      | V <sub>CCQ</sub> + 0.2 | V  |

| V <sub>IL</sub>                  | Input Low Voltage                                       |                                                           |       | -0.2                |      | 0.4                    | V  |

| V <sub>OH</sub>                  | Output High Voltage                                     | I <sub>OH</sub> = −0.2mA                                  |       | 0.8V <sub>CCQ</sub> |      |                        | V  |

| V <sub>OL</sub>                  | Output Low Voltage                                      | $I_{OL} = 0.2 \text{mA}$                                  |       |                     |      | 0.2V <sub>CCQ</sub>    | V  |

Note: 1. This parameter is specified with the outputs disabled to avoid external loading effects. The user must add the current required to drive the output capacitance expected in the actual system.

I<sub>SB</sub>(Max) values are measured with RCR2 to RCR0 bits set to '000' (full array refresh) and RCR6 to RCR5 bits set to '11' (temperature compensated refresh threshold at +85°C). In order to achieve low standby current, all inputs must be driven either to V<sub>CCQ</sub> or V<sub>SS</sub>.

<sup>3.</sup> The Operating Temperature is +25°C.

# **PACKAGE MECHANICAL**

BALL "A1"

A

A1

A1

BGA-Z42

Figure 7. TFBGA88 8x10mm, 8x10 ball array - 0.8mm pitch, Bottom View Package Outline

Note: Drawing is not to scale.

Table 9. Stacked TFBGA88 8x10mm - 8x10 active ball array, 0.8mm pitch, Package Data

| Cumbal |        | millimeters |        |        | inches |        |

|--------|--------|-------------|--------|--------|--------|--------|

| Symbol | Тур    | Min         | Max    | Тур    | Min    | Max    |

| А      |        |             | 1.200  |        |        | 0.0472 |

| A1     |        | 0.200       |        |        | 0.0079 |        |

| A2     | 0.850  |             |        | 0.0335 |        |        |

| b      | 0.350  | 0.300       | 0.400  | 0.0138 | 0.0118 | 0.0157 |

| D      | 8.000  | 7.900       | 8.100  | 0.3150 | 0.3110 | 0.3189 |

| D1     | 5.600  |             |        | 0.2205 |        |        |

| ddd    |        |             | 0.100  |        |        | 0.0039 |

| E      | 10.000 | 9.900       | 10.100 | 0.3937 | 0.3898 | 0.3976 |

| E1     | 7.200  |             |        | 0.2835 |        |        |

| E2     | 8.800  |             |        | 0.3465 |        |        |

| е      | 0.800  | _           | _      | 0.0315 | _      | _      |

| FD     | 1.200  |             |        | 0.0472 |        |        |

| FE     | 1.400  |             |        | 0.0551 |        |        |

| FE1    | 0.600  |             |        | 0.0236 |        |        |

| SD     | 0.400  |             |        | 0.0157 |        |        |

| SE     | 0.400  |             |        | 0.0157 |        |        |

### **PART NUMBERING**

#### **Table 10. Ordering Information Scheme**

Blank = Standard Packing

T = Tape & Reel Packing

E = Lead-free and RoHS Standard packing

F = Lead-free and RoHS Tape & Reel packing

Devices are shipped from the factory with the memory content bits erased to '1'. For a list of available options (Speed, Package, etc.) or for further information on any aspect of this device, please contact the ST-Microelectronics Sales Office nearest to you.

# **REVISION HISTORY**

**Table 11. Document Revision History**

| Date         | Version | Revision Details                                                                                                                                                                |

|--------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-Oct-2004  | 0.1     | First Issue                                                                                                                                                                     |

| 29-Apr-2004  | 0.2     | Part Number M69KB096A changed to M69KB096AA throughout document.                                                                                                                |

| 24-June-2005 | 0.3     | Status changed from Preliminary to Full Datasheet. Table 6., Table 7. and Table 8. modified. Signal changed from V <sub>DDQ</sub> to V <sub>DDQF</sub> throughout the document. |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. ECOPACK is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2005 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America www.st.com