# MSC7110

### Low-Cost 16-Bit DSP with DDR Controller

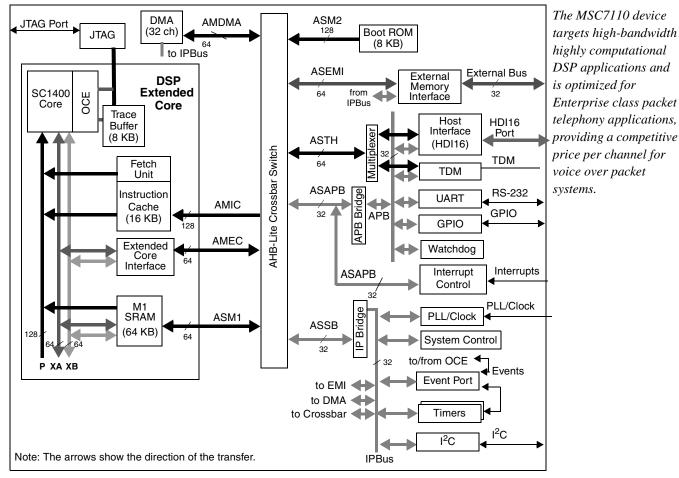

Figure 1. MSC7110 Block Diagram

The MSC7110 device is a highly integrated DSP processor that contains the StarCore<sup>TM</sup> SC1400 core, 64 KB of SRAM memory, a 16 KB ICache, an 8 KB boot ROM, a 128-channel time-division multiplexing (TDM) interface with hardware support for  $\mu$ /A-law decoding/encoding, a UART, a 32-channel DMA controller, a 16-bit host interface (HDI16) to support an external host processor, a programmable interrupt controller (PIC), an I<sup>2</sup>C interface, two 16-bit quad cascadable timers, GPIO signals, and an on-chip emulator (OCE) and event port for enhanced debug capability. The SC1400 core has four ALUs and performs at 1000 DSP million multiply accumulates per second (MMACS) with an internal 266 MHz clock at 1.2 V.

## Features

Table 1 lists the features of the Freescale MSC7110 device.

| Feature                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| StarCore™<br>SC1400 Core     | <ul> <li>Up to 1000 MMACS using an internal 266 MHz clock at 1.2 V. A multiply-accumulate operation includes a multiply-add instruction with the associated data move and pointer update.</li> <li>4 data ALUS.</li> <li>16 data registers, 40 bits each.</li> <li>27 address registers, 32 bits each.</li> <li>Hardware support for fractional and integer data types.</li> <li>Very rich 16-bit wide orthogonal instruction set.</li> <li>Up to six instructions executed in a single clock cycle.</li> <li>Variable-length execution set (VLES) that can be optimized for code density and performance.</li> <li>JTAG port designed to comply with IEEE® Std 1149.1<sup>™</sup>.</li> <li>On-chip emulator (OCE) module with real-time debugging capabilities.</li> </ul> |  |

| Extended Core                | <ul> <li>The high performance extended core delivers up to 1000 MMACS using 4 ALUs running up to 266 MHz, including:</li> <li>SC1400 core processor.</li> <li>64 KB multi-port SRAM (M1) accessed by the SC1400 core with no wait states.</li> <li>16 KB, 16-way instruction cache (ICache).</li> <li>Programmable instruction fetch unit.</li> <li>Write buffer (4-entry).</li> <li>Extended core interface module.</li> </ul>                                                                                                                                                                                                                                                                                                                                              |  |

| Internal Memory              | <ul> <li>The large internal memory space totals 88 KB:</li> <li>64 KB of M1 memory.</li> <li>16 KB ICache.</li> <li>8 KB boot ROM accessible from the SC1400 core.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| External Memory<br>Interface | <ul> <li>DDR memory controller.</li> <li>Glueless interface to 133 MHz DDR-RAM (synchronous and half of internal clock).</li> <li>14-bit external address bus supporting up to 1 GB.</li> <li>16- or 32-bit external data bus.</li> <li>Memory controller supports: <ul> <li>Byte enables for 32-bit external data bus.</li> <li>Data pipeline to reduce data set-up time for synchronous devices.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                    |  |

| Crossbar Switch              | AHB-Lite crossbar switch, allowing up to four parallel data transfers between four master ports and six slave ports, where each port connects to an AHB-Lite bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| DMA Controller               | <ul> <li>Multi-channel DMA controller:</li> <li>Up to 32 time-multiplexed channels.</li> <li>Priority-based time-multiplexing between channels using 32 internal priority levels</li> <li>Priorities can be fixed or round-robin.</li> <li>A flexible channel configuration: <ul> <li>All channels support all features.</li> <li>All channels connect to the slave ports on the crossbar.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                            |  |

| External Interfaces          | <ul> <li>External interfaces and control modules managed on the advanced peripheral bus (APB) including:</li> <li>Time-division multiplexing (TDM) module supporting up to 128 channels.</li> <li>Two 16-bit quad timers.</li> <li>RS-232 interface/universal asynchronous receiver/transmitter (UART).</li> <li>I<sup>2</sup>C interface.</li> <li>Up to 37 general-purpose input/output (GPIO) signals.</li> <li>Interrupt controller to handle external interrupt functions (input and output).</li> </ul>                                                                                                                                                                                                                                                                |  |

Table 1. MSC7110 Features

Table 1. MSC7110 Features (Continued)

| Feature                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Host Interface (HDI16) | Enhanced 16-bit wide interface provides a glueless connection to industry-standard microcontrollers, microprocessors, and DSPs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| TDM Module             | <ul> <li>TDM module with the following features:</li> <li>Totally independent receive and transmit, each having one data line, one clock line, and of frame sync line.</li> <li>Frame sync line and/or clock line can be shared between receive and transmit.</li> <li>Glueless interface to E1/T1 frames and MVIP, SCAS, and H.110 buses.</li> <li>Hardware A-law/µ-law conversion</li> <li>Up to 50 Mbps (50 MHz bit clock).</li> <li>Maximum rate is 1/4 the core frequency.</li> <li>Up to 128 channels.</li> <li>Each channel can be programmed to be active or inactive.</li> <li>8- or 16-bit word widths.</li> <li>The TDM Sync Signal (TDMxTFS/TDMxRFS) can be configured as either input or output</li> <li>The TDM clock signal (TDMxTCK/TDMxRCK) can be configured as either input or output</li> <li>Frame sync and data signals can be programmed to be sampled either on the rising edge on the falling edge of the clock.</li> <li>Frame sync can be programmed as active low or active high.</li> <li>Selectable delay (0–3 bits) between the Frame Sync signal and the beginning of the frame MSB or LSB first support.</li> </ul> |  |

| Timers                 | <ul> <li>Two 16-bit quad timers, each with the following features:</li> <li>Cyclic or one-shot.</li> <li>Input clock polarity control.</li> <li>Interrupt request when counting reaches a programmed threshold.</li> <li>Pulse or level interrupts.</li> <li>Dynamically updated programmed threshold.</li> <li>Read counter any time.</li> <li>Maximum rate is 1/4 the core frequency.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| UART                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Table 1. | MSC7110 Features (Continued) |  |

|----------|------------------------------|--|

|----------|------------------------------|--|

| Feature                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| l <sup>2</sup> C Port                      | <ul> <li>2-wire serial interface through GPIO.</li> <li>Filtered inputs for noise suppression.</li> <li>Compatibility with I<sup>2</sup>C bus standard up to 100 kbps for standard mode and up to 400 kbps for Fast mode.</li> <li>Bidirectional Data Transfer Protocol.</li> <li>Multiple-master operation that also allows any number of devices implementing the I<sup>2</sup>C-master software module to access the memory simultaneously at boot or any time.</li> <li>Compatible with the I<sup>2</sup>C-serial EEPROM access protocol, allowing memory access of up to one MB.</li> </ul>                           |  |

| General-Purpose I/O<br>(GPIO) Port         | Bidirectional signal lines that either serve the peripherals or act as programmable I/O ports.<br>Each port can be programmed separately to serve up to two dedicated peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Programmable Interrupt<br>Controller (PIC) | Consolidates maskable interrupt and non-maskable interrupt sources.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| System Control                             | <ul> <li>Reset controller.</li> <li>Clock controller module.</li> <li>Hardware bus monitors for the MSC7110 buses.</li> <li>Software watchdog timer function.</li> <li>fieldBIST<sup>™</sup> hardware health diagnostics that can be invoked at power-up or off-line via software.</li> <li>Event port.</li> </ul>                                                                                                                                                                                                                                                                                                         |  |

| Internal PLL                               | Generates up to 266 MHz clock for the SC1400 core and up to 133 MHz for the crossbar switch, DMA channels, M2 memory, and other peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Clock Synthesis Module                     | <ul> <li>Programmable low-power Stop and Wait modes.</li> <li>Generation of all device clocks.</li> <li>Halt and restart capability for on-chip peripherals.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Reduced Power<br>Dissipation               | <ul> <li>Separate power supply for internal logic and I/O.</li> <li>Typical case power consumption of 300–400 mW</li> <li>Low-power standby modes.</li> <li>Optimized power management circuitry (instruction-dependent, peripheral-dependent, and mode-dependent).</li> </ul>                                                                                                                                                                                                                                                                                                                                             |  |

| fieldBIST™ Hardware<br>Diagnostics         | <ul> <li>Detects and provides visibility into unlikely field failures for systems with high availability. The unique fieldBIST ensures that the device:</li> <li>Has structural integrity.</li> <li>Operates at the rated speed.</li> <li>Is free from reliability defects.</li> <li>Diagnostics can report partial or complete device inoperability. fieldBIST resolution can pinpoint the following uniquely:</li> <li>6 memory blocks, including ROM</li> <li>3 logic levels (top, extended core, and peripherals)</li> <li>1 PLL</li> <li>Simple JTAG interface allows easy integration to system firmware.</li> </ul> |  |

| Packaging                                  | <ul> <li>400 ball MAP-BGA.</li> <li>17 × 17 mm.</li> <li>0.8 mm pitch.</li> <li>Pb-free or Pb-bearing spheres.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Table 1. N | MSC7110 Features | (Continued) |

|------------|------------------|-------------|

|------------|------------------|-------------|

| Feature                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Software Support                                            | <ul> <li>Real-Time Operating Systems (RTOS) that fully supports MSC7110 device architecture (multicore, memory hierarchy, ICache, timers, DMA, interrupts, peripherals):</li> <li>High-performance and deterministic, delivering predictive response time.</li> <li>Optimized to provide low interrupt latency with high data throughput.</li> <li>Preemptive and priority-based multitasking.</li> <li>Fully interrupt/event driven.</li> <li>Small memory footprint.</li> <li>Comprehensive set of APIs.</li> <li>Fully supports MSC7110 DMA, interrupts, and timer schemes.</li> <li>Distributed system support, enables transparent inter-task communications:</li> <li>Messaging mechanism between tasks using mailboxes and semaphores.</li> <li>Networking support, data transfer between tasks running inside and outside the device using networking protocols.</li> <li>Includes integrated device drivers for such peripherals as TDM, UART, and external buses.</li> <li>Additional features:</li> <li>Incorporates task debugging utilities integrated with compilers and vendors.</li> <li>Board support package (BSP) for MSC7110 ADS.</li> <li>CodeWarrior® Integrated Development Environment (IDE):</li> <li>C/C++ compiler with in-line assembly. Enables the developer to generate highly optimized DSP code. It translates code written in C/C++ into parallel fetch sets and maintains high code density.</li> <li>Librarian. Enables the user to create libraries for modularity.</li> <li>C libraries. A collection of C/C++ functions for the developer's use.</li> <li>Linker. Highly efficient linker to produce executables from object code.</li> <li>Debugger. Seamlessly integrated real-time, non-intrusive multi-mode debugger that enables debugging of highly optimized DSP algorithms. The developer can choose to debug in source code, assembly code, or mixed mode.</li> <li>Profiler. An analysis tool using a patented Binary Code Instrumentation (BCI) technique that enables the developer to identify program design inefficiencies.</li> <li>Boot options:</li> <li>HDI16.</li></ul> |  |

| MetroWerks Application<br>Development System<br>(ADS) Board | <ul> <li>Host debug through single JTAG connector supports both processors.</li> <li>Big Flash memory for stand-alone applications.</li> <li>Support for the following communications ports: <ul> <li>10/100Base-T.</li> <li>T1/E1 TDM interface.</li> <li>H.110.</li> <li>Voice codec.</li> <li>RS-232.</li> <li>High-density (MICTOR) logic analyzer connectors to monitor MSC7110 signals</li> <li>6U cPCI form factor.</li> </ul> </li> <li>Emulates MSC7110 DSP farm by connecting to three other ADS boards.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

## **Product Documentation**

The documents listed in **Table 2** are required for a complete description of the MSC7110 device and are necessary to design properly with the part. Documentation is available from a local Freescale distributor, a Freescale semiconductor sales office, or a Freescale Literature Distribution Center. For documentation updates, visit the Freescale DSP website. See the contact information on the back of this document.

| Name                                                      | Description                                                                                                 | Order Number                                                        |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| MSC7110<br>Technical Data                                 | MSC7110 features list and physical, electrical, timing, and package specifications                          | MSC7110                                                             |

| MSC711x<br>Reference<br>Manual                            | Detailed functional description of memory and peripheral configuration, operation, and register programming | MSC711xRM                                                           |

| SC1000 Family<br>Processor<br>Core<br>Reference<br>Manual | Detailed description of the SC1000 family processor cores, including the SC1400, and instruction set        | 10180-01<br>See the StarCore LLC website at<br>www.starcore-dsp.com |

| Application<br>Notes                                      | Documents describing specific applications or optimized device operation including code examples            | See the MSC7110 product website                                     |

| Table 2 | MSC7110 Documentation |

|---------|-----------------------|

|         | WOOT TO Documentation |

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations not listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GMBH Technical Information Center Schatzbogen 7 81829 München, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T. Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

MSC7110PB Rev. 2 12/2005 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, fieldBIST, and Codewarrior are trademarks of Freescale Semiconductor, Inc. StarCore is a trademark of StarCore LLC. The StarCore SC1400 core is based on StarCore technology under license from StarCore LLC. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2004, 2005.