# **LPC3180**

16/32-bit ARM microcontroller; hardware floating-point coprocessor, USB On-The-Go, and SDRAM memory interface

Rev. 01 — 2 June 2006

**Preliminary data sheet**

## 1. General description

The LPC3180 is an ARM9-based microcontroller for embedded applications requiring high performance combined with low power dissipation. It achieves these objectives through the combination of Philips' state-of-the-art 90 nanometer technology with an ARM926EJ-S CPU core with a Vector Floating Point (VFP) coprocessor and a large array of standard peripherals including USB On-The-Go.

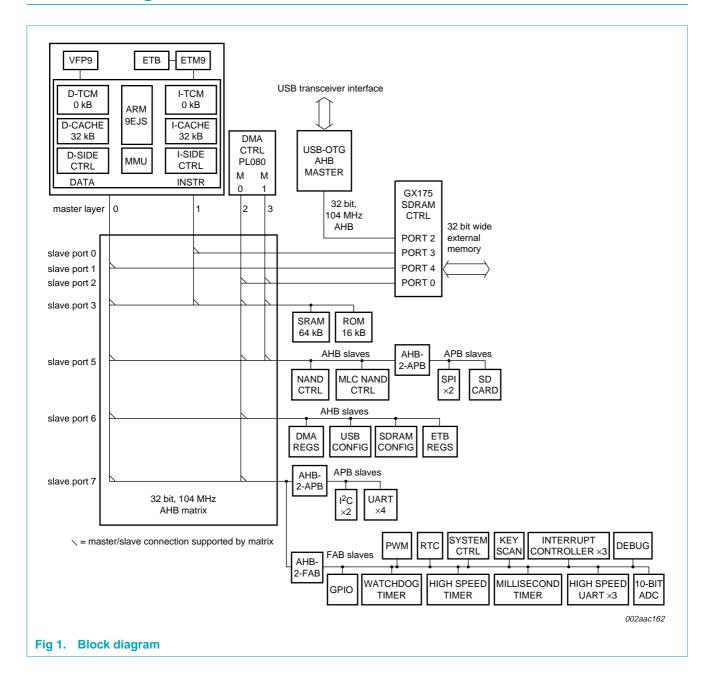

The microcontroller can operate at over 200 MHz CPU frequency (about 220 MIPS per ARM Inc.). The ARM926EJ-S CPU incorporates a 5-stage pipeline and has a Harvard architecture with separate 32 kB instruction and data caches, a demand paged MMU, DSP instruction extensions with a single cycle MAC, and Jazelle Java bytecode execution hardware. A block diagram of the microcontroller is shown in Figure 1.

Power optimization in this microcontroller is done through process and technology development (Intrinsic Power), and architectural means (Managed Power).

The LPC3180 also incorporates an SDRAM interface, NAND flash interfaces, USB 2.0 full-speed interface, seven UARTs, two I<sup>2</sup>C-bus interfaces, two SPI ports, a Secure Digital (SD) interface, and a 10-bit ADC in addition to many other features.

## 2. Features

#### 2.1 Key features

- ARM926EJ-S processor with 32 kB instruction cache and 32 kB data cache, running at up to 208 MHz.

- 64 kB of SRAM.

- High-performance multi-layer AHB bus system provides a separate bus for CPU data and instruction fetch, two data buses for the DMA controller, and another for the USB controller.

- External memory interfaces: one supports DDR and SDR SDRAM, another supports single-level and multi-level NAND flash devices and can serve as an 8-bit parallel interface.

- General purpose DMA controller that can be used with the SD card and SPI interfaces, as well as for memory-to-memory transfers.

- USB 2.0 full-speed device, host (OHCI compliant), and OTG block. A dedicated PLL provides the 48 MHz USB clock.

- Multiple serial interfaces, including seven UARTs, two SPI controllers, and two single master I<sup>2</sup>C-bus interfaces.

- SD memory card interface.

### 16/32-bit ARM microcontroller with external memory interface

- Up to 55 GPI, GPO, and GPIO pins. Includes 12 GPI pins, 24 GPO pins, and six GPIO pins.

- 10-bit ADC with input multiplexing from three pins.

- Real-Time Clock (RTC) with separate power supply and power domain, clocked by a dedicated 32 kHz oscillator. Includes a 128 byte scratch pad memory. The RTC may remain active when the rest of the chip is not powered.

- 32-bit general purpose high-speed timer with 16-bit pre-scaler with capture and compare capability.

- 32-bit millisecond timer driven from the RTC clock. Interrupts may be generated using two match registers.

- Watchdog timer.

- Two PWM blocks with an output rate up to 50 kHz.

- **EXECUTE:** Keyboard scanner function provides automatic scanning of up to an  $8 \times 8$  key matrix.

- Standard ARM test/debug interface for compatibility with existing tools.

- Emulation trace buffer with 2 k × 24-bit RAM allows trace via JTAG.

- On-chip crystal oscillator.

- Stop mode saves power, while allowing many peripheral functions to restart CPU activity.

- On-chip PLL allows CPU operation up to the maximum CPU rate without the need for a high frequency crystal.

- Boundary scan for simplified board testing.

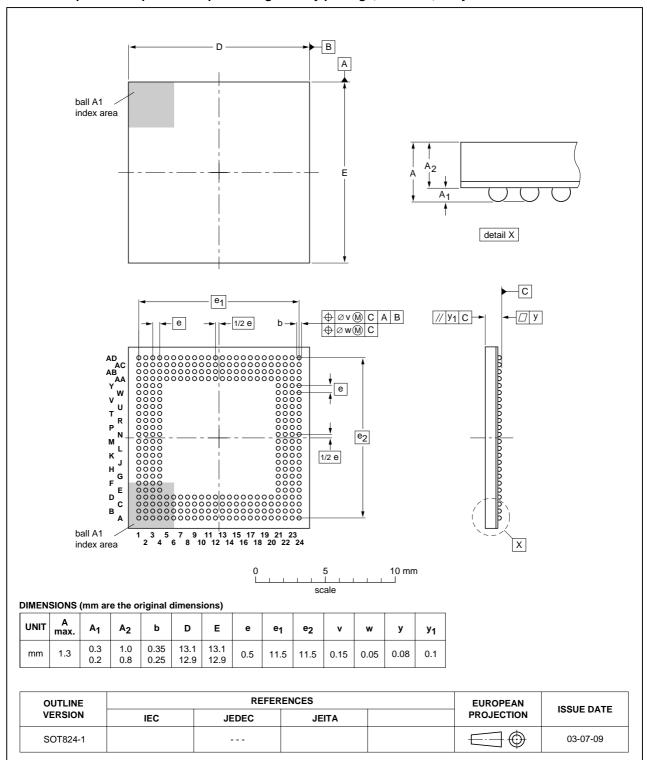

## 3. Ordering information

Table 1. Ordering information

| Type number      | Package  |                                                                                                      |          |  |  |  |  |  |

|------------------|----------|------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

|                  | Name     | Description                                                                                          | Version  |  |  |  |  |  |

| LPC3180FEL320[1] | LFBGA320 | plastic low profile fine-pitch ball grid array package; 320 balls; body $13 \times 13 \times 0.9$ mm | SOT824-1 |  |  |  |  |  |

[1] F = -40 °C to +85 °C temperature range.

## 16/32-bit ARM microcontroller with external memory interface

## 4. Block diagram

## 16/32-bit ARM microcontroller with external memory interface

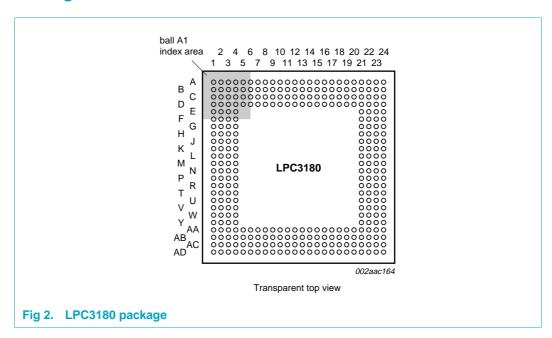

# 5. Pinning information

## 5.1 Pinning

Table 2. Pin allocation table

| Pin | Symbol                  | Pin | Symbol                  | Pin | Symbol            | Pin | Symbol                  |

|-----|-------------------------|-----|-------------------------|-----|-------------------|-----|-------------------------|

| Row | A                       |     |                         |     |                   |     |                         |

| 1   | U6_IRRX/<br>PIO_INP[21] | 2   | U5_RX/PIO_INP[20]       | 3   | HIGHCORE          | 4   | JTAG1_TDO               |

| 5   | JTAG1_TMS               | 6   | JTAG1_RTCK              | 7   | U3_TX             | 8   | VSS                     |

| 9   | VSS                     | 10  | VSS_IO1828_02           | 11  | GPO_23/U2_HRTS    | 12  | GPI_05                  |

| 13  | RTCX_OUT                | 14  | RTCX_IN                 | 15  | VSS               | 16  | VDD28                   |

| 17  | VDD28                   | 18  | i.c.[1]                 | 19  | VDD28             | 20  | VSS                     |

| 21  | VDD12                   | 22  | VDD_PLLHCLK_12          | 23  | SYSX_IN           | 24  | i.c.[1]                 |

| Row | В                       |     |                         |     |                   |     |                         |

| 1   | KEY_COL5                | 2   | U7_HCTS/<br>PIO_INP[22] | 3   | U7_TX             | 4   | VDD_IO1828_02           |

| 5   | JTAG1_TCK               | 6   | JTAG1_TDI               | 7   | VDD_IO1828_01     | 8   | U2_HCTS/<br>PIO_INP[16] |

| 9   | U1_RX/PIO_INP[15]       | 10  | U1_TX                   | 11  | VSS               | 12  | GPO_17                  |

| 13  | VSS_RTCCORE             | 14  | VDD12                   | 15  | VSS               | 16  | VSS                     |

| 17  | i.c.[1]                 | 18  | i.c.[1]                 | 19  | VDD12             | 20  | VSS_PLLUSB              |

| 21  | VSS_OSC                 | 22  | VDD_PLLUSB_12           | 23  | SYSX_OUT          | 24  | i.c.[1]                 |

| Row | С                       |     |                         |     |                   |     |                         |

| 1   | KEY_COL2                | 2   | KEY_COL3                | 3   | U7_RX/PIO_INP[23] | 4   | U5_TX                   |

| 5   | SYSCLKEN                | 6   | U3_RX/PIO_INP[18]       | 7   | U2_RX/PIO_INP[17] | 8   | VSS                     |

## 16/32-bit ARM microcontroller with external memory interface

Table 2.

Pin allocation table ...continued

| Pin   | Symbol                   | Pin | Symbol                        | Pin | Symbol                   | Pin | Symbol                   |  |

|-------|--------------------------|-----|-------------------------------|-----|--------------------------|-----|--------------------------|--|

| 9     | VSS                      | 10  | VDD_COREFXD12_<br>01          | 11  | VDD_RTCCORE12            | 12  | VDD_RTC12                |  |

| 13    | VSS_RTCOSC               | 14  | VDD_RTCOSC12                  | 15  | i.c. <u>[1]</u>          | 16  | VSS                      |  |

| 17    | VDD28                    | 18  | i.c.[1]                       | 19  | VSS                      | 20  | VSS_CORE_01              |  |

| 21    | PLL397_LOOP              | 22  | VDD_PLL397_12                 | 23  | VSS_PLL397               | 24  | ADIN0                    |  |

| Row D |                          |     |                               |     |                          |     |                          |  |

| 1     | KEY_ROW4                 | 2   | KEY_COL0                      | 3   | TEST                     | 4   | VSS_IO1828_01            |  |

| 5     | U6_IRTX                  | 6   | VDD_CORE12_02                 | 7   | JTAG1_NTRST              | 8   | VSS_CORE_02              |  |

| 9     | U2_TX                    | 10  | GPI_11                        | 11  | VSS                      | 12  | ONSW                     |  |

| 13    | RESET_N                  | 14  | VDD28                         | 15  | VSS                      | 16  | VSS_CORE_03              |  |

| 17    | VSS                      | 18  | VDD_COREFXD12_<br>02          | 19  | VSS_PLLHCLK              | 20  | VDD_OSC12                |  |

| 21    | i.c.[1]                  | 22  | VSS_AD                        | 23  | ADIN2                    | 24  | VDD_AD28                 |  |

| Row   | E                        |     |                               |     |                          |     |                          |  |

| 1     | KEY_ROW2                 | 2   | KEY_ROW5                      | 3   | VSS_IO28_01              | 4   | KEY_COL4                 |  |

| 21    | VDD_AD28                 | 22  | ADIN1                         | 23  | RAM_D[30]/<br>PIO_SD[11] | 24  | RAM_D[31]/<br>PIO_SD[12] |  |

| Row   | F                        | 1   |                               |     |                          | '   |                          |  |

| 1     | VSS_IO28_02              | 2   | KEY_ROW1                      | 3   | KEY_ROW3                 | 4   | KEY_COL1                 |  |

| 21    | RAM_D[29]/<br>PIO_SD[10] | 22  | VDD_SDRAM18_02                | 23  | VSS_SDRAM_01             | 24  | RAM_D[28]/<br>PIO_SD[09] |  |

| Row   | G                        |     |                               |     |                          |     |                          |  |

| 1     | i.c. <u>[1]</u>          | 2   | i.c.[1]                       | 3   | KEY_ROW0                 | 4   | VDD_IO28_02              |  |

| 21    | VDD_SDRAM18_01           | 22  | VSS_SDRAM_02                  | 23  | RAM_D[24]/<br>PIO_SD[05] | 24  | RAM_D[27]/<br>PIO_SD[08] |  |

| Row   | Н                        |     |                               |     |                          |     |                          |  |

| 1     | GPI_00                   | 2   | i.c.[1]                       | 3   | PWM_OUT2                 | 4   | i.c.[1]                  |  |

| 21    | RAM_D[19]/<br>PIO_SD[00] | 22  | RAM_D[23]/<br>PIO_SD[04]      | 23  | RAM_D[26]/<br>PIO_SD[07] | 24  | RAM_D[21]/<br>PIO_SD[02] |  |

| Row   | J                        | 1   |                               |     |                          | '   |                          |  |

| 1     | GPI_07                   | 2   | PWM_OUT1                      | 3   | GPI_02                   | 4   | VSS_CORE_04              |  |

| 21    | RAM_D[25]/<br>PIO_SD[06] | 22  | VDD_SDRAM18_03                | 23  | VSS_SDRAM_03             | 24  | RAM_D[20]/<br>PIO_SD[01] |  |

| Row   | K                        |     |                               |     |                          |     |                          |  |

| 1     | GPI_10/U4_RX             | 2   | GPI_08/KEY_COL6/<br>SPI2_BUSY | 3   | GPI_01/SERVICE_N         | 4   | GPI_04/SPI1_BUSY         |  |

| 21    | VDD_CORE12_03            | 22  | VDD_SDRAM18_04                | 23  | RAM_D[22]/<br>PIO_SD[03] | 24  | RAM_D[18]/<br>DDR_NCLK   |  |

| Row   | L                        | 1   |                               | ı   |                          | 1   |                          |  |

| 1     | GPO_03                   | 2   | GPI_09/KEY_COL7               | 3   | VDD_CORE12_05            | 4   | GPO_02                   |  |

| 21    | RAM_D[17]/<br>DDR_DQS1   | 22  | RAM_D[13]                     | 23  | RAM_D[16]/<br>DDR_DQS0   | 24  | RAM_D[15]                |  |

5 of 36

Table 2.

Pin allocation table ...continued

| Pin | Symbol               | Pin | Symbol         | Pin | Symbol               | Pin | Symbol               |

|-----|----------------------|-----|----------------|-----|----------------------|-----|----------------------|

| Row | М                    |     |                | 1   |                      |     |                      |

| 1   | GPO_08               | 2   | GPO_10         | 3   | GPO_07               | 4   | GPO_06               |

| 21  | VSS_SDRAM_04         | 22  | RAM_D[10]      | 23  | RAM_D[14]            | 24  | RAM_D[12]            |

| Row | N                    | '   |                | '   |                      | '   |                      |

| 1   | GPO_13               | 2   | GPO_16         | 3   | VSS_IO28_03          | 4   | GPO_09               |

| 21  | RAM_D[07]            | 22  | VSS_SDRAM_05   | 23  | RAM_D[11]            | 24  | RAM_D[09]            |

| Row | P                    | '   |                | '   |                      | '   |                      |

| 1   | GPO_18               | 2   | GPO_22/U7_HRTS | 3   | GPO_12               | 4   | GPO_21/U4_TX         |

| 21  | RAM_D[04]            | 22  | VDD_SDRAM18_05 | 23  | RAM_D[08]            | 24  | RAM_D[06]            |

| Row | R                    | '   |                |     |                      | •   |                      |

|     | GPIO_01              | 2   | GPIO_05        | 3   | VSS_CORE_05          | 4   | GPO_15               |

| 21  | VSS_CORE_06          | 22  | VSS_SDRAM_06   | 23  | RAM_D[05]            | 24  | RAM_D[03]            |

| Row | Т                    |     |                | '   |                      | '   |                      |

| 1   | GPIO_03/<br>KEY_ROW7 | 2   | GPIO_04        | 3   | GPIO_00              | 4   | SPI2_DATIN           |

| 21  | RAM_CLKIN            | 22  | RAM_D[01]      | 23  | RAM_D[00]            | 24  | RAM_D[02]            |

| Row | U                    |     |                |     |                      |     |                      |

|     | i.c. <u>[1]</u>      | 2   | MS_DIO1        | 3   | GPIO_02/<br>KEY_ROW6 | 4   | VDD_IO28_01          |

| 21  | RAM_RAS_N            | 22  | VDD_SDRAM18_06 | 23  | RAM_CLK              | 24  | RAM_CKE              |

| Row | V                    |     |                |     |                      |     |                      |

|     | SPI1_DATIN           | 2   | SPI2_DATIO     | 3   | SPI2_CLK             | 4   | MS_DIO3              |

| 21  | RAM_DQM[2]           | 22  | RAM_WR_N       | 23  | RAM_CAS_N            | 24  | RAM_CS_N             |

| Row | W                    |     |                | '   |                      | '   |                      |

|     | SPI1_DATIO           | 2   | MS_DIO0        | 3   | SPI1_CLK             | 4   | VSS                  |

| 21  | RAM_A[14]            | 22  | VSS_SDRAM_07   | 23  | RAM_DQM[1]           | 24  | RAM_DQM[3]           |

| Row | Υ                    | '   |                | '   |                      | '   |                      |

|     | MS_BS                | 2   | MS_DIO2        | 3   | GPO_04               | 4   | I2C1_SCL             |

| 21  | VDD_SDRAM18_07       | 22  | RAM_A[10]      | 23  | RAM_A[12]            | 24  | RAM_DQM[0]           |

| Row | AA                   | '   |                | '   |                      | '   |                      |

|     | MS_SCLK              | 2   | VDD_CORE12_01  | 3   | GPI_06/<br>HSTIM_CAP | 4   | VDD1828              |

| 5   | VSS_CORE_07          | 6   | VSS            | 7   | USB_ATX_INT_N        | 8   | USB_DAT_VP/<br>U5_RX |

| )   | I2C2_SDA             | 10  | VSS_CORE_08    | 11  | GPI_03               | 12  | VDD_CORE12_06        |

| 3   | i.c.[1]              | 14  | i.c.[1]        | 15  | VDD_IO18_02          | 16  | FLASH_ALE            |

| 7   | FLASH_RD_N           | 18  | VSS_SDRAM_10   | 19  | VDD_IO18_01          | 20  | VDD_SDRAM18_09       |

| 21  | RAM_A[05]            | 22  | VSS_SDRAM_08   | 23  | RAM_A[09]            | 24  | RAM_A[13]            |

| Row | AB                   | '   |                |     |                      | '   |                      |

| 1   | GPO_11               | 2   | VSS            | 3   | TST_CLK2             | 4   | VSS                  |

| 5   | VSS                  | 6   | VDD_CORE12_07  | 7   | USB_SE0_VM/<br>U5_TX | 8   | VSS_IO18_04          |

Table 2.

Pin allocation table ...continued

| Pin | Symbol          | Pin | Symbol          | Pin | Symbol          | Pin | Symbol          |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| 9   | GPO_00/TST_CLK1 | 10  | GPO_05          | 11  | VDD_IO18_03     | 12  | RESOUT_N        |

| 13  | i.c.[1]         | 14  | i.c.[1]         | 15  | i.c.[ <u>1]</u> | 16  | i.c.[1]         |

| 17  | VSS_CORE_09     | 18  | VDD_CORE12_08   | 19  | FLASH_IO[04]    | 20  | RAM_A[01]       |

| 21  | VSS_SDRAM_09    | 22  | RAM_A[07]       | 23  | RAM_A[08]       | 24  | RAM_A[11]       |

| Row | AC              |     |                 |     |                 |     |                 |

| 1   | I2C1_SDA        | 2   | VSS             | 3   | VSS             | 4   | VSS             |

| 5   | VSS             | 6   | VSS             | 7   | VDD_IO18_04     | 8   | USB_I2C_SCL     |

| 9   | GPO_01          | 10  | GPO_19          | 11  | VSS             | 12  | VSS_IO18_03     |

| 13  | i.c.[ <u>1]</u> | 14  | i.c.[ <u>1]</u> | 15  | FLASH_CLE       | 16  | VSS_IO18_01     |

| 17  | FLASH_IO[06]    | 18  | FLASH_RDY       | 19  | FLASH_IO[02]    | 20  | FLASH_IO[03]    |

| 21  | FLASH_CE_N      | 22  | RAM_A[04]       | 23  | RAM_A[06]       | 24  | VDD_SDRAM18_08  |

| Row | AD              |     |                 |     |                 |     |                 |

| 1   | VSS             | 2   | i.c.[ <u>1]</u> | 3   | VSS             | 4   | VDD1828         |

| 5   | VSS             | 6   | USB_OE_TP_N     | 7   | USB_I2C_SDA     | 8   | I2C2_SCL        |

| 9   | GPO_14          | 10  | GPO_20          | 11  | VSS             | 12  | i.c.[1]         |

| 13  | i.c.[1]         | 14  | i.c.[1]         | 15  | VSS_IO18_02     | 16  | i.c.[ <u>1]</u> |

| 17  | FLASH_WR_N      | 18  | FLASH_IO[07]    | 19  | FLASH_IO[05]    | 20  | FLASH_IO[01]    |

| 21  | FLASH_IO[00]    | 22  | RAM_A[00]       | 23  | RAM_A[02]       | 24  | RAM_A[03]       |

<sup>[1]</sup> These pins are connected internally and must be left unconnected in an application.

## 16/32-bit ARM microcontroller with external memory interface

# 5.2 Pin description

Table 3. Pin description

| - In doorn pro         |                                                      |      |                                                            |

|------------------------|------------------------------------------------------|------|------------------------------------------------------------|

| Symbol                 | Pin                                                  | Type | Description                                                |

| ADIN0                  | C24                                                  | I    | input 0 to the ADC                                         |

| ADIN1                  | E22                                                  | l    | input 1 to the ADC                                         |

| ADIN2                  | D23                                                  | I    | input 2 to the ADC                                         |

| FLASH_ALE              | AA16                                                 | 0    | address latch enable for NAND flash                        |

| FLASH_CE_N             | AC21                                                 | 0    | chip enable for NAND flash                                 |

| FLASH_CLE              | AC15                                                 | 0    | command latch enable for NAND flash                        |

| FLASH_IO[07:00]        | AD18, AC17, AD19,<br>AB19, AC20, AC19,<br>AD20, AD21 | I/O  | NAND flash data bus                                        |

| FLASH_RD_N             | AA17                                                 | 0    | read strobe for NAND flash                                 |

| FLASH_RDY              | AC18                                                 | I    | ready status from NAND flash                               |

| FLASH_WR_N             | AD17                                                 | 0    | write strobe for NAND flash                                |

| GPI_00                 | H1                                                   | I    | general purpose input 00                                   |

| GPI_01/                | K3                                                   | I    | GPI_01 — general purpose input 01                          |

| SERVICE_N              |                                                      | I    | SERVICE_N — boot select input                              |

| GPI_02                 | J3                                                   | ı    | general purpose input 02                                   |

| GPI_03                 | AA11                                                 | ı    | general purpose input 03                                   |

| GPI_04/                | K4                                                   | ı    | GPI_04 — general purpose input 04                          |

| SPI1_BUSY              |                                                      | ı    | SPI1_BUSY — busy input for SPI1                            |

| GPI_05                 | A12                                                  | ı    | general purpose input 05                                   |

| GPI_06/                | AA3                                                  | I    | GPI_06 — general purpose input 06                          |

| HSTIM_CAP              |                                                      | ı    | HSTIM_CAP — capture input trigger for the high-speed timer |

| GPI_07                 | J1                                                   | ı    | general purpose input 07                                   |

| GPI_08/                | K2                                                   | ı    | GPI_08 — general purpose input 08                          |

| KEY_COL6/<br>SPI2_BUSY |                                                      | ı    | KEY_COL6 — keyboard scan column input 6                    |

| 31 12_0031             |                                                      | ı    | SPI2_BUSY — busy input for SPI2                            |

| GPI_09/                | L2                                                   | ı    | GPI_09 — general purpose input 09                          |

| KEY_COL7               |                                                      | I    | KEY_COL7 — keyboard scan column input 7                    |

| GPI_10/                | K1                                                   | I    | GPI_10 — general purpose input 10                          |

| U4_RX                  |                                                      | I    | U4_RX — UART 4 receive data input                          |

| GPI_11                 | D10                                                  | I    | general purpose input 11                                   |

| GPIO_00                | T3                                                   | I/O  | general purpose input/output 00                            |

| GPIO_01                | R1                                                   | I/O  | general purpose input/output 01                            |

| GPIO_02/               | U3                                                   | I/O  | GPIO_02 — general purpose input/output 02                  |

| KEY_ROW6               |                                                      | 0    | KEY_ROW6 — keyboard scan row output 6                      |

| GPIO_03/               | T1                                                   | I/O  | GPIO_03 — general purpose input/output 03                  |

| KEY_ROW7               |                                                      | 0    | KEY_ROW7 — keyboard scan row output 7                      |

| GPIO_04                | T2                                                   | I/O  | general purpose input/output 04                            |

| GPIO_05                | R2                                                   | I/O  | general purpose input/output 05                            |

|                        |                                                      |      |                                                            |

Table 3.

Pin description ...continued

| Symbol    |      | Pin  | Туре | Description                                                                |

|-----------|------|------|------|----------------------------------------------------------------------------|

| GPO_00/   |      | AB9  | 0    | <b>GPO_00</b> — general purpose output 00                                  |

| TST_CLK1  |      |      | 0    | <b>TST_CLK1</b> — Clock test output 1, controlled by the TEST_CLK register |

| GPO_01    |      | AC9  | 0    | general purpose output 01                                                  |

| GPO_02    |      | L4   | 0    | general purpose output 02                                                  |

| GPO_03    |      | L1   | 0    | general purpose output 03                                                  |

| GPO_04    |      | Y3   | 0    | general purpose output 04                                                  |

| GPO_05    |      | AB10 | 0    | general purpose output 05                                                  |

| GPO_06    |      | M4   | 0    | general purpose output 06                                                  |

| GPO_07    |      | M3   | 0    | general purpose output 07                                                  |

| GPO_08    |      | M1   | 0    | general purpose output 08                                                  |

| GPO_09    |      | N4   | 0    | general purpose output 09                                                  |

| GPO_10    |      | M2   | 0    | general purpose output 10                                                  |

| GPO_11    |      | AB1  | 0    | general purpose output 11                                                  |

| GPO_12    |      | P3   | 0    | general purpose output 12                                                  |

| GPO_13    |      | N1   | 0    | general purpose output 13                                                  |

| GPO_14    |      | AD9  | 0    | general purpose output 14                                                  |

| GPO_15    |      | R4   | 0    | general purpose output 15                                                  |

| GPO_16    |      | N2   | 0    | general purpose output 16                                                  |

| GPO_17    |      | B12  | 0    | general purpose output 17                                                  |

| GPO_18    |      | P1   | 0    | general purpose output 18                                                  |

| GPO_19    |      | AC10 | 0    | general purpose output 19                                                  |

| GPO_20    |      | AD10 | 0    | general purpose output 20                                                  |

| GPO_21/   |      | P4   | 0    | GPO_21 — general purpose output 21                                         |

| U4_TX     |      |      | 0    | U4_TX — UART 4 transmit data output                                        |

| GPO_22/   |      | P2   | 0    | GPO_22 — general purpose output 22                                         |

| U7_HRTS   |      |      | 0    | U7_HRTS — UART 7 hardware flow control (RTS) output                        |

| GPO_23/   |      | A11  | 0    | GPO_23 — general purpose output 23                                         |

| U2_HRTS   |      |      | 0    | U2_HRTS — UART 2 hardware flow control (RTS) output                        |

| HIGHCORE  |      | A3   | 0    | core voltage select output                                                 |

| I2C1_SCL  |      | Y4   | I/O  | serial clock for I <sup>2</sup> C1                                         |

| I2C1_SDA  |      | AC1  | I/O  | serial data for I <sup>2</sup> C1                                          |

| I2C2_SCL  |      | AD8  | I/O  | serial clock for I <sup>2</sup> C2                                         |

| I2C2_SDA  |      | AA9  | I/O  | serial data for I <sup>2</sup> C2                                          |

| JTAG1_NTF | RST  | D7   | I    | JTAG reset input                                                           |

| JTAG1_RTC | CK . | A6   | 0    | JTAG return clock output                                                   |

| JTAG1_TCK | (    | B5   | I    | JTAG clock input                                                           |

| JTAG1_TDI |      | B6   | I    | JTAG data input                                                            |

| JTAG1_TDC | )    | A4   | 0    | JTAG data output                                                           |

|           | 6    | A5   |      | JTAG test mode select input                                                |

## 16/32-bit ARM microcontroller with external memory interface

Table 3.

Pin description ...continued

| Table 3. Pin description | oncontinued                                                                                       |      |                                                                                                                                             |

|--------------------------|---------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                   | Pin                                                                                               | Type | Description                                                                                                                                 |

| KEY_COL0 to<br>KEY_COL5  | D2, F4, C1, C2, E4,<br>B1                                                                         | I    | keyboard scan column inputs                                                                                                                 |

| KEY_ROW0 to<br>KEY_ROW5  | G3, F2, E1, F3, D1,<br>E2                                                                         | 0    | keyboard scan row outputs 0 through 5                                                                                                       |

| MS_BS                    | Y1                                                                                                | I/O  | SD card command input/output (SD_CMD)                                                                                                       |

| MS_DIO0 to MS_DIO3       | W2, U2, Y2, V4                                                                                    | I/O  | SD card data bus (SD_D0 to SD_D3)                                                                                                           |

| MS_SCLK                  | AA1                                                                                               | 0    | SD card clock output (SD_CLK)                                                                                                               |

| ONSW                     | D12                                                                                               | 0    | VCCon output signal                                                                                                                         |

| PLL397_LOOP              | C21                                                                                               | I/O  | loop filter pin for PLL397; requires external components if PLL397 is used                                                                  |

| PWM_OUT1                 | J2                                                                                                | 0    | output of Pulse Width Modulator 1                                                                                                           |

| PWM_OUT2                 | H3                                                                                                | 0    | output of Pulse Width Modulator 2                                                                                                           |

| RAM_A[14:00]             | W21, AA24, Y23,<br>AB24, Y22, AA23,<br>AB23, AB22, AC23,<br>AA21, AC22, AD24,<br>AD23, AB20, AD22 | 0    | SDRAM address bus, pins 14 to 00                                                                                                            |

| RAM_CAS_N                | V23                                                                                               | 0    | SDRAM column address strobe output                                                                                                          |

| RAM_CKE                  | U24                                                                                               | 0    | SDRAM clock enable output                                                                                                                   |

| RAM_CLK                  | U23                                                                                               | 0    | SDRAM clock output                                                                                                                          |

| RAM_CLKIN                | T21                                                                                               | I    | SDRAM clock return input                                                                                                                    |

| RAM_CS_N                 | V24                                                                                               | 0    | SDRAM chip select output                                                                                                                    |

| RAM_D[15:00]             | L24, M23, L22,<br>M24, N23, M22,<br>N24, P23, N21,<br>P24, R23, P21,<br>R24, T24, T22, T23        | I/O  | SDRAM data bus, pins 15 to 00                                                                                                               |

| RAM_D[16]/               | L23                                                                                               | I/O  | RAM_D[16] — SDRAM data bus, pin 16                                                                                                          |

| DDR_DQS0                 |                                                                                                   | 0    | DDR_DQS0 — SDRAM data strobe output for lower byte                                                                                          |

| RAM_D[17]/               | L21                                                                                               | I/O  | RAM_D[17] — SDRAM data bus, pin 17                                                                                                          |

| DDR_DQS1                 |                                                                                                   | 0    | DDR_DQS1 — SDRAM data strobe output for upper byte                                                                                          |

| RAM_D[18]/               | K24                                                                                               | I/O  | RAM_D[18] — SDRAM data bus, pin 18                                                                                                          |

| DDR_NCLK                 |                                                                                                   | 0    | DDR_NCLK — inverted SDRAM clock output for DDR                                                                                              |

| RAM_D[31:19]/            | E24, E23, F21, F24,                                                                               | I/O  | RAM_D[31:19] — SDRAM data bus, pins 31 to 19                                                                                                |

| PIO_SD[12:00]            | G24, H23, J21,<br>G23, H22, K23,<br>H24, J24, H21                                                 | I/O  | PIO_SD[12:00] — general purpose input/output, pins 12 to 00; details may be found in Section 6.10 "General purpose parallel I/O" on page 18 |

| RAM_DQM[3:0]             | W24, V21, W23,<br>Y24                                                                             | 0    | SDRAM byte write mask outputs                                                                                                               |

| RAM_RAS_N                | U21                                                                                               | 0    | SDRAM row address strobe output                                                                                                             |

| RAM_WR_N                 | V22                                                                                               | 0    | SDRAM write strobe output                                                                                                                   |

| RESET_N                  | ESET_N D13 I system                                                                               |      | system reset input                                                                                                                          |

| RESOUT_N                 | AB12                                                                                              | 0    | reset output signal                                                                                                                         |

| RTCX_IN                  | A14                                                                                               | I    | RTC oscillator input                                                                                                                        |

| RTCX_OUT                 | A13                                                                                               | 0    | RTC oscillator output                                                                                                                       |

| LPC3180_1                |                                                                                                   |      | © Koninklijke Philins Flectronics N.V. 2006. All rights reserved                                                                            |

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Table 3.

Pin description ...continued

| <u> </u>          | Dincontinued | Time P | Docarintian                                                                  |

|-------------------|--------------|--------|------------------------------------------------------------------------------|

| Symbol            | Pin          |        | Description                                                                  |

| SPI1_CLK          | W3           |        | clock output for SPI1                                                        |

| SPI1_DATIN        | V1           |        | data input for SPI1                                                          |

| SPI1_DATIO        | W1           |        | data input/output for SPI1                                                   |

| SPI2_CLK          | V3           |        | clock output for SPI2                                                        |

| SPI2_DATIN        | T4           |        | data input for SPI2                                                          |

| SPI2_DATIO        | V2           |        | data input/output for SPI2                                                   |

| SYSCLKEN          | C5           |        | system clock request                                                         |

| SYSX_IN           | A23          |        | main oscillator input                                                        |

| SYSX_OUT          | B23          |        | main oscillator output                                                       |

| TEST              | D3           |        | est input; internally pulled down, should be left floating in an application |

| TST_CLK2          | AB3          | O c    | clock test output 2, controlled by the TEST_CLK                              |

| U1_RX/            | B9           |        | U1_RX — UART 1 receive data input                                            |

| PIO_INP[15]       |              |        | PIO_INP[15] — general purpose input to PIO_INP_STATE register                |

| U1_TX             | B10          | 0 L    | JART 1 transmit data output                                                  |

| U2_HCTS/          | B8           | l L    | U2_HCTS — UART 2 hardware flow control (CTS) input                           |

| PIO_INP[16]       |              |        | PIO_INP[16] — general purpose input to PIO_INP_STATE register                |

| U2_RX/            | C7           | ı L    | U2_RX — UART 2 receive data input                                            |

| PIO_INP[17]       |              |        | PIO_INP[17] — general purpose input to PIO_INP_STATE register                |

| U2_TX             | D9           | Ο L    | JART 2 transmit data output                                                  |

| U3_RX/            | C6           | ı L    | U3_RX — UART 3 receive data input                                            |

| PIO_INP[18]       |              |        | PIO_INP[18] — general purpose input to PIO_INP_STATE register                |

| U3_TX             | A7           | Ο L    | JART 3 transmit data output                                                  |

| U5_RX/PIO_INP[20] | A2           | ı L    | U5_RX — UART 5 receive data input                                            |

|                   |              |        | PIO_INP[20] — general purpose input to PIO_INP_STATE register                |

| U5_TX             | C4           | Ο (    | JART 5 transmit data output                                                  |

| U6_IRRX/          | A1           | I/O L  | U6_IRRX — UART 6 receive data input; can be IrDA data                        |

| PIO_INP[21]       |              |        | PIO_INP[21] — general purpose input to PIO_INP_STATE register                |

| U6_IRTX           | D5           |        | JART 6 transmit data output; can be IrDA data                                |

| U7_HCTS/          | B2           | ı L    | U7_HCTS — UART 7 hardware flow control (CTS) input                           |

| PIO_INP[22]       |              |        | PIO_INP[22] — general purpose input to PIO_INP_STATE register                |

| U7_RX/            | C3           |        | U7_RX — UART 7 receive data input                                            |

| PIO_INP[23]       |              | I P    | PIO_INP[23] — general purpose input to PIO_INP_STATE register                |

| U7_TX             | В3           | 0 L    | JART 7 transmit data output                                                  |

| USB_ATX_INT_N     | AA7          | I L    | JSB interrupt from external transceiver                                      |

Table 3.

Pin description ...continued

| Symbol                                                                  | Pin                                                                                                                                                                  | Type | Description                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB_DAT_VP/                                                             | AA8                                                                                                                                                                  | I/O  | USB_DAT_VP — USB transmit data                                                                                                                                                                                                       |

| U5_RX                                                                   |                                                                                                                                                                      | I    | U5_RX — UART 5 receive data input                                                                                                                                                                                                    |

| USB_I2C_SCL                                                             | AC8                                                                                                                                                                  | I/O  | serial clock for USB I <sup>2</sup> C-bus                                                                                                                                                                                            |

| USB_I2C_SDA                                                             | AD7                                                                                                                                                                  | I/O  | serial data for USB I <sup>2</sup> C-bus                                                                                                                                                                                             |

| USB_OE_TP_N                                                             | AD6                                                                                                                                                                  | I/O  | USB transmit enable for DAT/SE0                                                                                                                                                                                                      |

| USB_SE0_VM/                                                             | AB7                                                                                                                                                                  | I/O  | USB_SE0_VM — USB single ended zero transmit                                                                                                                                                                                          |

| U5_TX                                                                   |                                                                                                                                                                      | 0    | U5_TX — UART 5 transmit data output                                                                                                                                                                                                  |

| VDD12                                                                   | B14, A21, B19                                                                                                                                                        | I    | 1.2 V power supply for various internal functional blocks that are not included with VDD_CORE or VDD_COREFXD                                                                                                                         |

| VDD_AD28                                                                | D24, E21                                                                                                                                                             | I    | 3.0 V power supply and positive reference voltage for the ADC                                                                                                                                                                        |

| VDD_CORE12_01 to<br>VDD_CORE12_03,<br>VDD_CORE12_05 to<br>VDD_CORE12_08 | AA2, D6, K21, L3,<br>AA12, AB6, AB18                                                                                                                                 | I    | 1.2 V core main power supply for the CPU and other core logic; this voltage may be reduced to 0.9 V when the core is running at or below 13 MHz; the HIGHCORE pin may be used to signal this condition to an external voltage switch |

| VDD_COREFXD12_01,<br>VDD_COREFXD12_02                                   | C10, D18                                                                                                                                                             | I    | 1.2 V core secondary power supply voltage for the CPU and other core logic; this supply cannot be reduced in the same manner as the VDD_CORE12 supply                                                                                |

| VDD1828,<br>VDD_IO1828_01,<br>VDD_IO1828_02                             | AD4, AA4, B7, B4                                                                                                                                                     | I    | 1.8 V or 3.0 V power supply for I/O pins that may operate from either a 1.8 V range or a 3 V range                                                                                                                                   |

| VDD_IO18_01 to<br>VDD_IO18_04                                           | AA19, AA15, AB11,<br>AC7                                                                                                                                             | I    | 1.8 V power supply for I/O pins that operate only from a 1.8 V range                                                                                                                                                                 |

| VDD28, VDD_IO28_01,<br>VDD_IO28_02                                      | U4, G4, D14, A16,<br>A17, C17, A19                                                                                                                                   | I    | 3.0 V power supply for I/O pins that operate only from a 3 V range                                                                                                                                                                   |

| VDD_OSC12                                                               | D20                                                                                                                                                                  | I    | 1.2 V power supply for the main oscillator                                                                                                                                                                                           |

| VDD_PLL397_12                                                           | C22                                                                                                                                                                  | I    | 1.2 V power supply for the 397x PLL                                                                                                                                                                                                  |

| VDD_PLLHCLK_12                                                          | A22                                                                                                                                                                  | I    | 1.2 V power supply for the HCLK PLL                                                                                                                                                                                                  |

| VDD_PLLUSB_12                                                           | B22                                                                                                                                                                  | I    | 1.2 V power supply for the USB PLL                                                                                                                                                                                                   |

| VDD_RTC12                                                               | C12                                                                                                                                                                  | I    | 1.2 V power supply for the RTC block                                                                                                                                                                                                 |

| VDD_RTCCORE12                                                           | C11                                                                                                                                                                  | I    | 1.2 V power supply for the RTC block                                                                                                                                                                                                 |

| VDD_RTCOSC12                                                            | C14                                                                                                                                                                  | I    | 1.2 V power supply for the 32 kHz RTC oscillator                                                                                                                                                                                     |

| VDD_SDRAM18_01 to<br>VDD_SDRAM18_09                                     | G21, F22, J22, K22,<br>P22, U22, Y21,<br>AC24, AA20                                                                                                                  | I    | 1.8 V power supply for the SDRAM controller block                                                                                                                                                                                    |

| VSS                                                                     | B16, D15, AC11,<br>AB2, AD1, AC2,<br>AD5, AC5, AA6,<br>AC6, AD3, AC4,<br>AC3, AB4, AD11,<br>C9, A9, A8, C8,<br>D11, B11, B15, A15,<br>AB5, W4, C16, D17,<br>A20, C19 | I    | ground for various internal logic blocks that are not included with VDD_CORE or VDD_COREFXD.                                                                                                                                         |

| VSS_AD                                                                  | D22                                                                                                                                                                  | I    | ground for the ADC; this should nominally be the same voltage as VSS, but should be isolated to minimize noise and conversion error                                                                                                  |

Table 3.

Pin description ...continued

| Symbol                            | Pin                                                                                                                                                          | Туре | Description                                                                      |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------|

| VSS_CORE_01 to<br>VSS_CORE_09     | C20, D8, D16, J4,<br>R3, R21, AA5,<br>AA10, AB17                                                                                                             | I    | ground for the core logic functions                                              |

| VSS_IO1828_01 to<br>VSS_IO1828_02 | D4, A10                                                                                                                                                      | I    | ground for I/O pins that may operate from either a 1.8 V range or a 3 V range $$ |

| VSS_IO18_01 to<br>VSS_IO18_04     | AC16, AD15, AC12,<br>AB8                                                                                                                                     | I    | ground for I/O pins that operate only from a 1.8 V range                         |

| VSS_IO28_01 to<br>VSS_IO28_03     | E3, F1, N3                                                                                                                                                   | I    | ground for I/O pins that operate only from a 3 V range                           |

| VSS_OSC                           | B21                                                                                                                                                          | I    | ground for the main oscillator                                                   |

| VSS_PLL397                        | C23                                                                                                                                                          | I    | ground for the 397x PLL                                                          |

| VSS_PLLHCLK                       | D19                                                                                                                                                          | I    | ground for the HCLK PLL                                                          |

| VSS_PLLUSB                        | B20                                                                                                                                                          | I    | ground for the USB PLL                                                           |

| VSS_RTCCORE                       | B13                                                                                                                                                          | I    | ground for the RTC block                                                         |

| VSS_RTCOSC                        | C13                                                                                                                                                          | I    | ground for the 32 kHz RTC oscillator                                             |

| VSS_SDRAM_01 to<br>VSS_SDRAM_10   | F23, G22, J23, M21,<br>N22, R22, W22,<br>AA22, AB21, AA18                                                                                                    | I    | ground for the SDRAM controller block                                            |

| i.C.                              | A18, B17, B18, C18,<br>U1, AD2, AA13,<br>AD16, AB16, AA14,<br>AC14, AB15, AD14,<br>AC13, AB14, AD13,<br>AB13, AD12, H2,<br>G1, G2, H4, D21,<br>B24, A24, C15 |      | internally connected; leave open                                                 |

### 16/32-bit ARM microcontroller with external memory interface

## 6. Functional description

### 6.1 Architectural overview

The microcontroller is a general purpose 32-bit microprocessor, which offers high performance and very low power consumption. The ARM architecture is based on RISC principles, and the instruction set and related decode mechanism are much simpler than those of microprogrammed CISCs. This simplicity results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective processor core.

A 5-stage pipeline is employed so that all parts of the processing and memory systems can operate continuously. At any one point in time, several operations are typically in progress: subsequent instruction fetch, next instruction decode, instruction execution, memory access, and write-back. The combination of architectural enhancements gives the ARM9 about 30 % better performance than an ARM7 running at the same clock rate:

- Approximately 1.3 clocks per instruction (1.9 clocks per instruction for ARM7).

- Approximately 1.1 Dhrystone MIPS/MHz (0.9 Dhrystone MIPS/MHz for ARM7).

The ARM926EJ-S processor also employs a unique architectural strategy known as Thumb, which makes it ideally suited to high-volume applications with memory restrictions, or applications where code density is an issue.

The key idea behind Thumb is that of a super-reduced instruction set. Essentially, the ARM926EJ-S processor has two instruction sets:

- 1. The standard 32-bit ARM set.

- 2. A 16-bit Thumb set.

The Thumb set's 16-bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARM's performance advantage over a traditional 16-bit processor using 16-bit registers. This is possible because Thumb code operates on the same 32-bit register set as ARM code.

Thumb code is able to provide up to 65 % of the code size of ARM, and 160 % of the performance of an equivalent ARM processor connected to a 16-bit memory system.

In addition, the ARM9 includes enhanced DSP instructions and multiplier, as well as an enhanced 32-bit MAC block.

## 6.2 Vector Floating Point (VFP) coprocessor

This CPU coprocessor provides full support for single-precision and double-precision add, subtract, multiply, divide, and multiply-accumulate operations at CPU clock speeds. It is compliant with the IEEE 754 standard, and enables advanced Motor control and DSP applications. The VFP has three separate pipelines for floating-point MAC operations, divide or square root operations, and load/store operations. These pipelines can operate in parallel and can complete execution out of order. All single-precision instructions, except divide and square root, take one cycle and double-precision multiply and multiply-accumulate instructions take two cycles. The VFP also provides format conversions between floating-point and integer word formats.

### 16/32-bit ARM microcontroller with external memory interface

#### 6.3 AHB matrix

The microcontroller has a multi-layer AHB matrix for inter-block communication. AHB is the ARM high-speed bus, which is part of the ARM bus architecture. AHB is a high-bandwidth low-latency bus that supports multi-master arbitration and a bus grant/request mechanism. For systems where there is only one bus master (the CPU), or where there are two masters (CPU and DMA) and the CPU does not generally need to contend with the DMA for program memory access (because the CPU has access to memory on its local bus or has caches or another AHB bus etc.), this arrangement works well. However, if there are multiple bus masters and the CPU needs access to external memory, a single AHB bus can cause a bottleneck. ARM's solution to this was to invent a multi-layer AHB which replaces the request/grant and arbitration mechanism with a multiplexer fabric that pushes arbitration to the level of the devices. Thus, if a CPU and a DMA controller want access to the same memory, the multi-layer fabric will arbitrate between the two on granting access to that memory. This allows simultaneous access by bus masters to different resources at the cost of increased arbitration complexity. As with all trade-offs, the pros and cons must be analyzed, for a microcontroller operating at 200 MHz, removing guaranteed central arbitration in case more than one bus master is active in favor of occasional local arbitration gives better performance.

The blocks outside the CPU can be roughly split into memory controllers, serial communication, I/O, timers/counters and RTC, system control, and debug and trace blocks. These are described as follows.

## 6.4 On-chip SRAM

On-chip SRAM may be used for code and/or data storage. The SRAM may be accessed as 8/16/32 bit. The LPC3180 provides 64 kB of SRAM.

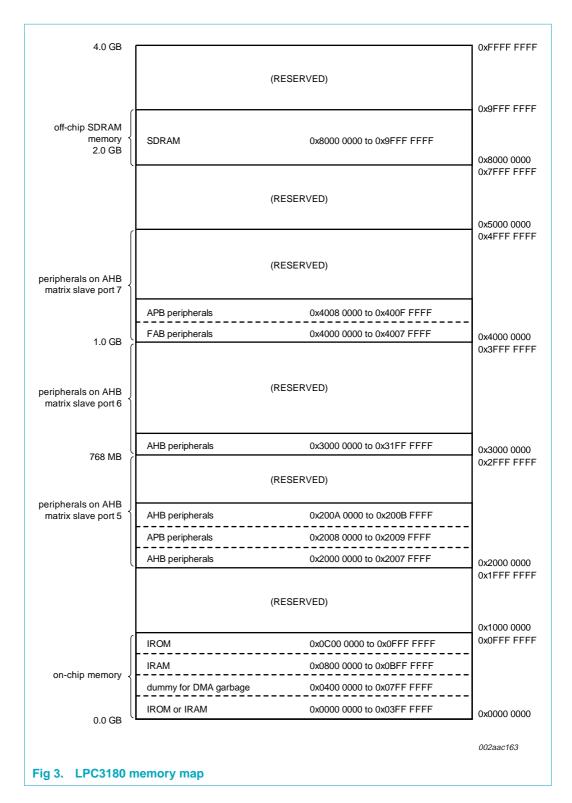

## 6.5 Memory map

The LPC3180 memory map incorporates several distinct regions, as shown in <u>Figure 3</u>. When an application is running, the CPU interrupt vectors are re-mapped to allow them to reside in on-chip SRAM.

## 16/32-bit ARM microcontroller with external memory interface

## 6.6 SDRAM memory controller

The SDRAM memory controller provides an interface between the system bus and external (off-chip) memory devices. A single chip select is supplied, supporting one group of SDRAM in the same address range. The SDRAM controller supports SDR SDRAM

**Preliminary data sheet**

### 16/32-bit ARM microcontroller with external memory interface

devices of 64/128/256/512/1024 Mbit in size, as well as DDR SDRAM devices of 64/128/256/512/1024 Mbit in size. The SDRAM controller uses four data ports to allow simultaneous requests from multiple on-chip AHB bus masters.

#### 6.7 NAND flash controllers

The LPC3180 includes two NAND flash controllers, one for multi-level NAND flash devices and one for single-level NAND flash devices. The two NAND flash controllers use the same pins to interface to external NAND flash devices, so only one interface is active at a time.

### 6.7.1 Multi-Level Cell (MLC) NAND flash controller

The MLC NAND flash controller interfaces to either multi-level or single-level NAND flash devices. An external NAND flash device is used to allow the bootloader to automatically load a portion of the application code into internal SRAM for execution following reset.

The MLC NAND flash controller supports up to 2 Gbit devices with small (528 byte) or large (2114 byte) pages. Programmable NAND timing parameters allow support for a variety of NAND flash devices. A built-in Reed-Solomon encoder/decoder provides error detection and correction capability. A 528 byte data buffer reduces the need for CPU supervision during loading. The MLC NAND flash controller also provides DMA support.

### 6.7.2 Single-Level Cell (SLC) NAND flash controller

The SLC NAND flash controller interfaces to single-level NAND flash devices up to 2 Gbit in size. DMA page transfers are supported, including a 20 byte DMA read and write FIFO. Hardware support for ECC (Error Checking and Correction) is included for the main data area. Software can correct a single bit error.

#### 6.8 DMA controller

The DMA controller allows peripheral-to memory, memory-to-peripheral, peripheral-to-peripheral, and memory-to-memory transactions. Each DMA stream provides unidirectional serial DMA transfers for a single source and destination. For example, a bidirectional port requires one stream for transmit and one for receives. The source and destination areas can each be either a memory region or a peripheral, and can be accessed through the same AHB master or one area by each master.

The DMA controls eight DMA channels with hardware prioritization. The DMA controller interfaces to the system via two AHB bus masters, each with a full 32-bit data bus width. DMA operations may be set up for 8-bit, 16-bit, and 32-bit data widths, and can be either big-endian or little-endian. Incrementing or non-incrementing addressing for source and destination are supported, as well as programmable DMA burst size. Scatter or gather DMA is supported through the use of linked lists. This means that the source and destination areas do not have to occupy contiguous areas of memory.

## 6.9 Interrupt controller

The interrupt controller is comprised of three basic interrupt controller blocks, supporting a total of 60 interrupt sources. Each interrupt source can be individually enabled/disabled and configured for high or low level triggering, or rising or falling edge triggering. Each interrupt may also be steered to either the FIQ or IRQ input of the ARM9. Raw interrupt

### 16/32-bit ARM microcontroller with external memory interface

status and masked interrupt status registers allow versatile condition evaluation. In addition to peripheral functions, each of the six general purpose input/output pins and 12 general purpose input pins are connected directly to the interrupt controller.

## 6.10 General purpose parallel I/O

Some device pins that are not dedicated to a specific peripheral function have been designed to be general purpose inputs, outputs, or I/Os. Also, some pins may be configured either as a specific peripheral function or a general purpose input, output, or I/O. A total of 55 pins can potentially be used as general purpose input/outputs, general purpose outputs, and general purpose inputs.

GPIO pins may be dynamically configured as inputs or outputs. Separate registers allow setting or clearing any number of GPIO and GPO outputs controlled by that register simultaneously. The value of the output register for standard GPIOs and GPO pins may be read back, as well as the current actual state of the port pins.

There are 12 GPI, 24 GPO, and six GPIO pins. When the SDRAM bus is configured for 16 data bits, 13 of the remaining SDRAM data pins may be used as GPIOs.

## 6.10.1 Features

- Bit-level set and clear registers allow a single instruction set or clear of any number of bits in one port.

- A single register selects direction for pins that support both input and output modes.

- · Direction control of individual bits.

- For input/output pins, both the programmed output state and the actual pin state can be read.

- There are a total of 12 general purpose inputs, 24 general purpose outputs, and six general purpose input/outputs.

- Additionally, 13 SDRAM data lines may be used as GPIOs if a 16-bit SDRAM interface is used (rather than a 32-bit interface).

#### 6.11 10-bit ADC

The ADC is a three channel, 10-bit successive approximation ADC. The ADC may be configured to produce results with a resolution anywhere from 10 bits to 3 bits. When high resolution is not needed, lowering the resolution can substantially reduce conversion time.

The analog portion of the ADC has its own power supply to enhance the low noise characteristics of the converter. This voltage is only supplied internally when the core has voltage. However, the ADC block is not affected by any difference in ramp-up time for VDD\_AD and VDD\_CORE voltage supplies.

## 6.11.1 Features

- Measurement range of 0 V to VDD\_AD28 (nominally 3 V).

- · Low noise ADC.

- Maximum 10-bit resolution, resolution can be reduced to any amount down to 3 bits for faster conversion.

- Three input channels.

### 16/32-bit ARM microcontroller with external memory interface

Uses 32 kHz RTC clock

#### 6.12 USB interface

The LPC3180 supports USB in either device, host, or OTG configuration.

#### 6.12.1 USB device controller

The USB device controller enables 12 Mbit/s data exchange with a USB host controller. It consists of register interface, serial interface engine, endpoint buffer memory and DMA controller. The serial interface engine decodes the USB data stream and writes data to the appropriate end point buffer memory. The status of a completed USB transfer or error condition is indicated via status registers. An interrupt is also generated if enabled. The DMA controller when enabled transfers data between the endpoint buffer and the USB RAM.

#### **6.12.1.1** Features

- Fully compliant with USB 2.0 full-speed specification.

- Supports 32 physical (16 logical) endpoints.

- Supports control, bulk, interrupt and isochronous endpoints.

- Scalable realization of endpoints at run time.

- Endpoint maximum packet size selection (up to USB maximum specification) by software at run time.

- RAM message buffer size based on endpoint realization and maximum packet size.

- Supports bus-powered capability with low suspend current.

- Supports DMA transfer on all non-control endpoints.

- One duplex DMA channel serves all endpoints.

- Allows dynamic switching between CPU controlled and DMA modes.

- Double buffer implementation for bulk and isochronous endpoints.

#### 6.12.2 USB host controller

The host controller enables data exchange with various USB devices attached to the bus. It consists of register interface, serial interface engine and DMA controller. The register interface complies to the OHCI specification.

#### **6.12.2.1 Features**

- OHCI compliant.

- OHCI specifies the operation and interface of the USB host controller and SW driver.

- The host controller has four USB states visible to the SW driver:

- USBOperational: Process lists and generate SOF tokens.

- USBReset: Forces reset signaling on the bus, SOF disabled.

- USBSuspend: Monitor USB for wake-up activity.

- USBResume: Forces resume signaling on the bus.

- HCCA register points to interrupt and isochronous descriptors list.

- ControlHeadED and BulkHeadED registers point to control and bulk descriptors list.

### 16/32-bit ARM microcontroller with external memory interface

#### 6.12.3 USB OTG Controller

USB OTG (On-The-Go) is a supplement to the USB 2.0 specification that augments the capability of existing mobile devices and USB peripherals by adding host functionality for connection to USB peripherals.

#### **6.12.3.1** Features

- Fully compliant with On-The-Go supplement to the USB Specification 2.0 Revision 1.0.

- Supports Host Negotiation Protocol (HNP) and Session Request Protocol (SRP) for dual-role devices under software control. HNP is partially implemented in hardware.

- Provides programmable timers required for HNP and SRP.

- Supports slave mode operation through AHB slave interface.

- Supports the OTG ATX from Philips (ISP 1301) or any external CEA-2011OTG specification compliant ATX.

#### **6.13 UARTs**

The LPC3180 contains seven UARTs. Four are standard UARTs, and three are special purpose high-speed UARTs.

#### 6.13.1 Standard UARTs

The four standard UARTs are downwards compatible with the INS16Cx50. These UARTs support rates up to 460800 bit/s from a 13 MHz peripheral clock.

#### **6.13.1.1** Features

- Each standard UART has 64 byte Receive and Transmit FIFOs.

- Receiver FIFO trigger points at 16 B, 32 B, 48 B, and 60 B.

- Transmitter FIFO trigger points at 0 B, 4 B, 8 B, and 16 B.

- Register locations conform to 16C550 industry standard.

- Each standard UART has a fractional rate pre-divider and an internal baud rate generator.

- The standard UARTs support three clocking modes: on, off, and auto-clock. The auto-clock mode shuts off the clock to the UART when it is idle.

- UART 6 includes an IrDA mode to support infrared communication.

- The standard UARTs are designed to support data rates of (2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800) bit/s.

- Each UART includes an internal loopback mode.

### 6.13.2 High-speed UARTs

The three high-speed UARTs are designed to support rates up to 921600 bit/s from a 13 MHz peripheral clock, for on-board communication in low noise conditions. This is accomplished by changing the oversampling from  $16\times$  to  $14\times$ , and altering the rate generation logic.

### 16/32-bit ARM microcontroller with external memory interface

#### **6.13.2.1** Features

- Each high-speed UART has 64 byte Receive and Transmit FIFOs.

- Receiver FIFO trigger points at 1 B, 4 B, 8 B, 16 B, 32 B, and 48 B.

- Transmitter FIFO trigger points at 0 B, 4 B, and 8 B.

- Each high-speed UART has an internal baud rate generator.

- The high-speed UARTs are designed to support data rates of (2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 921600) bit/s.

- · Each UART includes an internal loopback mode.

#### 6.14 I<sup>2</sup>C-bus serial I/O controller

There are two  $I^2C$ -bus interfaces in the LPC3180. The blocks for the  $I^2C$ -bus are a master only implementation supporting the 400 kHz  $I^2C$ -bus mode and lower rates, with 7-bit slave addressing. Each has a four word FIFO for both transmit and receive. An interrupt signal is available from each block.

#### 6.14.1 Features