# Description

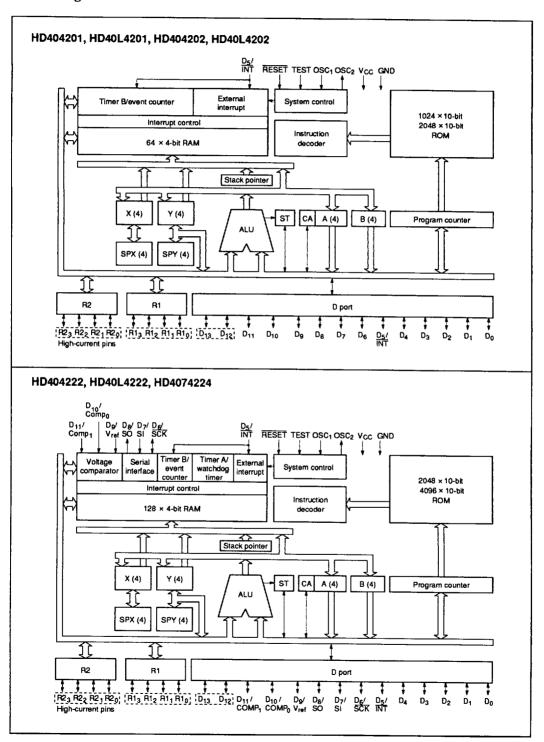

These MCU's are CMOS 4-bit single-chip microcomputers with the same architecture as the HMCS400 Series. Each microcomputers incorporate ROM, RAM, I/O, and peripheral functions such as one or two timer/counters. Also, HD404222 Series has two-channel comparators, and a serial interface.

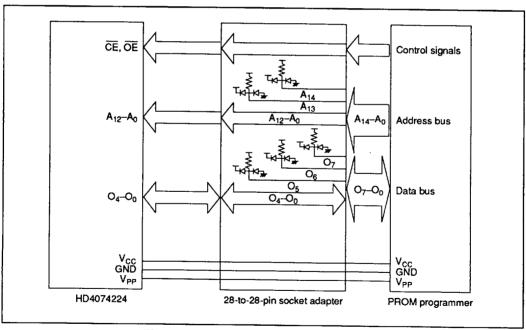

The HD404202 Series includes four chips: the HD404201 with 1-kword ROM and 5-V operation; HD40L4201 with 1-kword ROM and low-voltage operation; HD404202 with 2-kword ROM and 5-V operation; HD40L4202 with 2-kword ROM and low-voltage operation. The HD404222 Series includes three chips: HD404222 with 2-kword ROM and 5-V operation; HD40L4222 with 2-kword and low-voltage operation; HD4074224 with 4-kword PROM.

The HD4074224, incorporating PROM, is a ZTAT<sup>TM</sup> microcomputer which can dramatically shorten system development period and smooth the process from debugging to mass production. (The PROM program specifications are the same as for the 27256.)

### **Features**

The differences between HD404202 Series and HD404222 Series.

|                  | HD404202 Series | HD404222 Series                |

|------------------|-----------------|--------------------------------|

| RAM (digits)     | 64              | 128                            |

| Timers           | 8-bit × 1       | 8-bit × 2                      |

| Serial interface | <u> </u>        | Clock-synchronous<br>8-bit × 1 |

| Comparators      |                 | 2 channels                     |

|                  |                 |                                |

- HMCS400 CPU (software-compatible with the HMCS400 Series)

- 1024-word × 10-bit mask ROM (HD404201, HD40L4201)

- 2048-word × 10-bit mask ROM (HD404202, HD40L4202, HD404222, HD40L4222)

- 4096-word × 10-bit PROM (HD4074224)

- 64-digit × 4-bit RAM (HD404201, HD40L4201, HD404202, and HD40L4202)

- 128-digit × 4-bit RAM (HD404222, HD40L4222, and HD4074224)

- 22 I/O pins including 10 high-current pins

- Two timer/counters

- 8-bit free-running or watchdog timer (watchdog timer is selectable by mask option) (HD404222 Series)

- 8-bit auto-reloading timer/event counter

- Clock-synchronous 8-bit serial interface (HD404222 Series)

- Two-channel comparators (HD404222 Series)

- Two analog input pins

- Reference voltage pin

- · One external interrupt

- · Low-power dissipation modes

- Standby mode

- -- Stop mode

- · Built-in oscillator

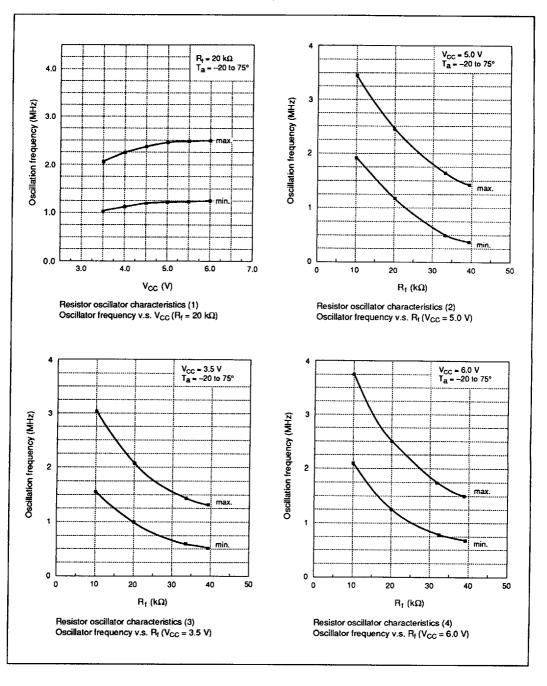

- Resistor or ceramic oscillator (an external clock is also possible)

- · Minimum instruction cycle time

- 0.89 µs (f<sub>OSC</sub> = 4.5 MHz, V<sub>CC</sub> = 3.5 V- 6.0 V)

- $-3.55 \mu s$  (f<sub>OSC</sub> = 1.125 MHz, V<sub>CC</sub> = 2.5 V-6.0 V)

- $-2.0 \mu s$  (f<sub>OSC</sub> = 2.0 MHz, V<sub>CC</sub> = 2.5 V-6.0 V) for HD40L4222

- · Package

- 28 pin shrink-type plastic DIP (DP-28S)

- 28-pin SOP (FP-28DA)

- 30-pin SSOP (FP-30D)

# **Type of Product**

| Device   |                           | ROM<br>Size | Options                                                       | Package     |

|----------|---------------------------|-------------|---------------------------------------------------------------|-------------|

| Mask ROM | HD404201S<br>HD40L4201S   | 1024        | Selected by mask option                                       | DP-28S      |

|          | HD404201FP<br>HD40L4201FP | <del></del> |                                                               | FP-28DA     |

|          | HD404201FT<br>HD40L4201FT | _           |                                                               | FP-30D      |

|          | HD404202S<br>HD40L4202S   | 2048        |                                                               | DP-28S      |

|          | HD404202FP<br>HD40L4202FP |             |                                                               | FP-28DA     |

|          | HD404202FT<br>HD40L4202FT |             |                                                               | FP-30D      |

|          | HD404222S<br>HD40L4222S   | _           |                                                               | DP-28S      |

|          | HD404222FP<br>HD40L4222FP |             |                                                               | FP-28DA     |

|          | HD404222FT<br>HD40L4222FT |             |                                                               | FP-30D      |

| ZTAT™    | HD4074224S01              | 4096        | Timer A: Free-running timer<br>Oscillator: Resistor           | DP-28S      |

|          | HD4074224S02              |             | Timer A: Free-running timer<br>Oscillator: Ceramic oscillator |             |

|          | HD4074224S03              |             | Timer A: Watchdog timer<br>Oscillator: Resistor               | <del></del> |

|          | HD4074224S04              |             | Timer A: Watchdog timer<br>Oscillator: Ceramic oscillator     | <del></del> |

|          | HD4074224FP01             | _           | Timer A: Free-running timer<br>Oscillator: Resistor           | FP-28DA     |

|          | HD4074224FP02             | _           | Timer A: Free-running timer<br>Oscillator: Ceramic oscillator | <del></del> |

|          | HD4074224FP03             | _           | Timer A: Watchdog timer<br>Oscillator: Resistor               | <del></del> |

|          | HD4074224FP04             |             | Timer A: Watchdog timer<br>Oscillator: Ceramic oscillator     | <del></del> |

|          | HD4074224FT01             | _           | Timer A: Free-running timer<br>Oscillator: Resistor           | FP-30D      |

|          | HD4074224FT02             | _           | Timer A: Free-running timer<br>Oscillator: Ceramic oscillator | <del></del> |

|          | HD4074224FT03             |             | Timer A: Watchdog timer<br>Oscillator: Resistor               | _           |

|          | HD4074224FT04             | _           | Timer A: Watchdog timer<br>Oscillator: Ceramic oscillator     | _           |

# Differences between Mask ROM and ZTAT™ Microcomputers

|                                          |                                                                 |                                           |                             | Mask RC                                          | OM .                        |                                                  |                             | ZTAT"                                                                                                  |

|------------------------------------------|-----------------------------------------------------------------|-------------------------------------------|-----------------------------|--------------------------------------------------|-----------------------------|--------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------|

| ltem                                     |                                                                 | HD404201                                  | HD40L4201                   | HD404202                                         | HD40L4202                   | HD404222                                         | HD40L4222                   | HD4074224                                                                                              |

| Power sup<br>(V <sub>CC</sub> )          | ply voltage                                                     | 3.5 to 6.0 V                              | 2.5 to 6.0 V                | 3.5 to 6.0 V                                     | 2.5 to 6.0 V                | 3.5 to 6.0 V                                     | 2.5 to 6.0 V                | 3.5 to 5.5 V,<br>2.7 to 3.5 V                                                                          |

| Instruction<br>time (t <sub>cyc</sub> )  | cycle                                                           | 0.89 to 4.0 μs                            | 3.55 to 10.0 μs             | 0.89 to 4.0 μs                                   | 3.55 to 10.0 μs             | 0.89 to 4.0 μs                                   | 2.0 to 10.0 μs              | 0.89 to 4.0 μs,<br>2.0 to 10.0 μs                                                                      |

| ROM                                      |                                                                 | 1024 × 10-bit                             | 1024 × 10-bit               | 2048 × 10-bit                                    | 2048 × 10-bit               | 2048 × 10-bit                                    | 2048 × 10-bit               | 4096 × 10-bit                                                                                          |

| RAM                                      |                                                                 | 64 × 4-bit                                | 64 × 4-bit                  | 64 × 4-bit                                       | 64 × 4-bit                  | 128 × 4-bit                                      | 128 × 4-bit                 | 128 × 4-bit                                                                                            |

| Watchdog<br>free runnin                  |                                                                 | _                                         | _                           | _                                                | _                           | 1                                                | 1                           | 1                                                                                                      |

| Serial inter                             | face                                                            | _                                         |                             | _                                                | _                           | 1                                                | 1                           | 1                                                                                                      |

| Comparato                                | or                                                              | _                                         | _                           | -                                                | _                           | 2 ch                                             | 2 ch                        | 2 ch                                                                                                   |

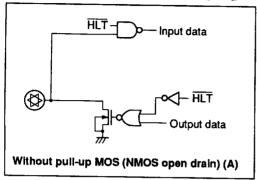

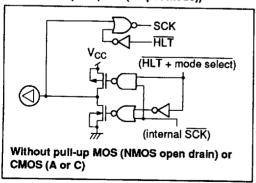

| I/O pin<br>circuit<br>(standard<br>pins) | Without<br>pull-up<br>MOS<br>(NMOS<br>open drain)<br>(option A) | Available                                 | Available                   | Available                                        | Available                   | Available                                        | Available                   | _                                                                                                      |

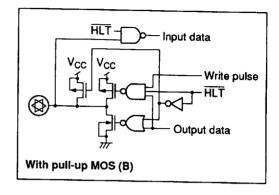

|                                          | With pull-up<br>MOS<br>(option B)                               | Available                                 | Available                   | Available                                        | Available                   | Available                                        | Available                   | Available                                                                                              |

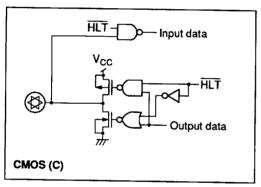

|                                          | CMOS<br>(option C)                                              | Available                                 | Available                   | Available                                        | Available                   | Available                                        | Available                   | <del>_</del>                                                                                           |

| Clock                                    | Ceramic                                                         | Available                                 | Available                   | Available                                        | Available                   | Available                                        | Available                   | Available                                                                                              |

| genera-<br>tion                          | Resistor                                                        | Available with $t_{cyc} = 1.33$ to 4.0 µs | -                           | Available with t <sub>cyc</sub> = 1.33 to 4.0 μs | _                           | Available with t <sub>cyc</sub> = 1.33 to 4.0 μs | _                           | Available only<br>under V <sub>CC</sub> =<br>3.5 to 5.5 V<br>with t <sub>cyc</sub> = 1.33<br>to 4.0 μs |

|                                          | External                                                        | Available                                 | Available                   | Available                                        | Available                   | Available                                        | Available                   | Available                                                                                              |

| Package                                  |                                                                 | DP-28S<br>FP-28DA<br>FP-30D               | DP-28S<br>FP-28DA<br>FP-30D | DP-28S<br>FP-28DA<br>FP-30D                      | DP-28S<br>FP-28DA<br>FP-30D | DP-28S<br>FP-28DA<br>FP-30D                      | DP-28S<br>FP-28DA<br>FP-30D | DP-28S<br>FP-28DA<br>FP-30D                                                                            |

# Pin Arrangement

| HD404201, HD40L          | .4201. HD40 | 94202. HD40L4202                                 |                                      |        |                                          |

|--------------------------|-------------|--------------------------------------------------|--------------------------------------|--------|------------------------------------------|

|                          |             |                                                  | <del></del>                          |        |                                          |

| GND ☐ 1                  |             | 28 🔲 R2 <sub>3</sub>                             | NC 1                                 |        | 30 🗆 NC                                  |

| R1 <sub>0</sub> □ 2      |             | 27 🔲 R2 <sub>2</sub>                             | GND 🗆 2                              |        | 29 🔲 R2 <sub>3</sub>                     |

| R1₁ □3                   |             | 26 🔲 R2 <sub>1</sub>                             | R1 <sub>0</sub> □3                   |        | 28 🗀 R2 <sub>2</sub>                     |

| R1₂ ☐ 4                  |             | 25 🔲 R2 <sub>0</sub>                             | R1₁ ☐ 4                              |        | 27 🗖 R2 <sub>1</sub>                     |

| R1 <sub>3</sub> ☐ 5      |             | 24 🔲 D <sub>13</sub>                             | R1 <sub>2</sub> ☐ 5                  |        | 26 R2 <sub>0</sub>                       |

| D <sub>0</sub> ☐ 6       |             | 23 D <sub>12</sub>                               | R1 <sub>3</sub> ☐ 6                  |        | 25 D <sub>13</sub>                       |

| D₁ □7                    | DP-28S      | 22 TEST                                          | D <sub>0</sub> □ 7                   | FP-30D | 24 D <sub>12</sub>                       |

| D <sub>2</sub>           | FP-28DA     | 21 RESET                                         | D₁ ☐8                                | ,, 005 | 23 TEST                                  |

| D <sub>3</sub> □ 9       |             | 20 🗀 OSC <sub>2</sub>                            | D₂ □ 9                               |        | 22 RESET                                 |

| D₄ ☐ 10                  |             | 19 ☐ OSC₁                                        | D <sub>3</sub> 🔲 10                  |        | 21 ☐ OSC <sub>2</sub>                    |

| D <sub>5</sub> /INT ☐ 11 |             | 18 🗆 V <sub>CC</sub>                             | D₄ ☐ 11                              |        | 20 ☐ osc₁                                |

| D <sub>6</sub>           |             | 17 🗖 D <sub>11</sub>                             | D <sub>5</sub> / <del>INT</del> ☐ 12 |        | 19 🗀 V <sub>CC</sub>                     |

| D <sub>7</sub> 🔲 13      |             | 16 🗀 D <sub>10</sub>                             | D <sub>6</sub> 🔲 13                  |        | 18 🗖 D <sub>11</sub>                     |

| D <sub>8</sub> 🗆 14      |             | 15 D <sub>9</sub>                                | D <sub>7</sub> 🔲 14                  |        | 17 🗖 D <sub>10</sub>                     |

|                          |             |                                                  | D <sub>8</sub>                       |        | 16 🗆 D <sub>9</sub>                      |

| HD404222, HD40L          | 4222, HD40  | 74224                                            |                                      |        |                                          |

| GND □1                   |             | 28 🔲 R2 <sub>3</sub>                             | NC 1                                 |        | 30 NC                                    |

| R1 <sub>0</sub> □ 2      |             | 27 R2 <sub>2</sub>                               | GND 2                                |        | 29 🗆 R2 <sub>3</sub>                     |

| R1 <sub>1</sub> □ 3      |             | 26 R2 <sub>1</sub>                               | R1 <sub>0</sub> 3                    |        | 28 R2 <sub>2</sub>                       |

| R1 <sub>2</sub> 4        |             | 25 R2 <sub>0</sub>                               | R1, 4                                |        | 27   R2 <sub>1</sub>                     |

| R1 <sub>3</sub>          |             | 24 D <sub>13</sub>                               | R1 <sub>2</sub>                      |        | 26 R2 <sub>0</sub>                       |

| $D_0 \square 6$          |             | 23 D <sub>12</sub>                               | $R1_3 \square 6$                     |        |                                          |

| $D_1 \square 7$          | DP-28S      | 20   D <sub>12</sub><br>22   TEST                | $D_0 \square 7$                      |        | 25 D <sub>13</sub><br>24 D <sub>12</sub> |

| D <sub>2</sub>           | FP-28DA     | 21 RESET                                         | D <sub>1</sub>                       | FP-30D | 23 TEST                                  |

| $D_3 \square 9$          |             | 20 OSC <sub>2</sub>                              | D <sub>2</sub>                       |        | 22 RESET                                 |

| D <sub>4</sub>           |             | 19  OSC <sub>1</sub>                             | D <sub>3</sub> 10                    |        | 21 OSC <sub>2</sub>                      |

|                          |             | 18 V <sub>CC</sub>                               | D <sub>4</sub> 11                    |        | 20 OSC <sub>1</sub>                      |

| D <sub>6</sub> /SCK ☐ 12 |             | 17 D <sub>11</sub> /COMP <sub>1</sub>            | D <sub>5</sub> / <del>INT</del> 12   |        | 19 V <sub>CC</sub>                       |

| D <sub>7</sub> /SI       |             | $\begin{array}{c c} & D_{10}/COMP_0 \end{array}$ | $D_6/\overline{SCK}$ 13              |        | 18 D <sub>11</sub> /COMP <sub>1</sub>    |

| D <sub>8</sub> /SO  14   |             | 15 D <sub>9</sub> N <sub>ref</sub>               | D <sub>7</sub> /SI  14               |        | 17 D <sub>10</sub> /COMP <sub>0</sub>    |

| -8/                      | <u>.</u>    |                                                  | D <sub>8</sub> /SO  15               |        | 16 D <sub>9</sub> N <sub>ref</sub>       |

|                          |             |                                                  | -8                                   |        | -   '9' *ref                             |

# **Block Diagram**

# **Pin Description**

| Pin Number |

|------------|

|------------|

|                      |                                          |                                                                                                          |                 | •                                                                                                       |                                                                                                                                    |  |  |

|----------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Item                 | Symbol                                   | DP-28S<br>FP-28DA                                                                                        | FP-30D          | 1/0                                                                                                     | Function                                                                                                                           |  |  |

| Power supply         | V <sub>cc</sub>                          | 18                                                                                                       | 19              |                                                                                                         | Power supply pin                                                                                                                   |  |  |

|                      | GND                                      | 1                                                                                                        | 2               |                                                                                                         | Ground connection pin                                                                                                              |  |  |

| Test                 | TEST                                     | 22                                                                                                       | 23              | ı                                                                                                       | Pin used for test purposes only. Connect it to ground.                                                                             |  |  |

| Reset                | RESET                                    | 21                                                                                                       | 22              | 1                                                                                                       | MCU reset pins                                                                                                                     |  |  |

| to a re-             |                                          | Pins for the internal oscillator circuit. Connect them to a resistor or a ceramic oscillator, or connect |                 |                                                                                                         |                                                                                                                                    |  |  |

|                      | OSC <sub>2</sub>                         | SC <sub>2</sub> 20 21 O OSC <sub>1</sub> to an external oscillator cir                                   |                 | OSC <sub>1</sub> to an external oscillator circuit. The internal oscillator is selected by mask option. |                                                                                                                                    |  |  |

| Port                 | D <sub>0</sub> -D <sub>13</sub>          | 6–17,<br>23, 24                                                                                          | 7–18,<br>24, 25 | 1/0                                                                                                     | Input/output ports addressable by individual bits. Pins D <sub>12</sub> and D <sub>13</sub> can output 15 mA maximum.              |  |  |

|                      | R1 <sub>0</sub> -R2 <sub>3</sub>         | 2–5,<br>25–28                                                                                            | 3–6,<br>26–29   | I/O                                                                                                     | Input/output ports addressable in 4-bit units. These pins can output 15 mA maximum.                                                |  |  |

| Interrupt            | INT                                      | 11                                                                                                       | 12              | ı                                                                                                       | Input pin for external interrupt. It is also used as an external event input for timer B. It is multiplexed with pin ${\rm D_5}$ . |  |  |

| Serial<br>interface* | SCK                                      | 12                                                                                                       | 13              | 1/0                                                                                                     | Serial interface clock input/output pin. It is multiplexed with pinD <sub>6</sub> .                                                |  |  |

|                      | SI                                       | 13                                                                                                       | 14              | 1                                                                                                       | Serial interface receive data input pin. It is multiplexed with pin $D_7$ .                                                        |  |  |

|                      | SO                                       | 14                                                                                                       | 15              | 0                                                                                                       | Serial interface transmit data output pin. It is multiplexed with pin $D_8$ .                                                      |  |  |

| Comparator*          | V <sub>ref</sub>                         | 15                                                                                                       | 16              | ı                                                                                                       | Reference voltage pin to input the threshold voltage of the analog input pins                                                      |  |  |

|                      | COMP <sub>0</sub> ,<br>COMP <sub>1</sub> | 16, 17                                                                                                   | 17, 18          | I                                                                                                       | Analog input pins for the voltage comparator                                                                                       |  |  |

<sup>\*</sup> Only applicable for the HD404222 Series.

# Memory Map

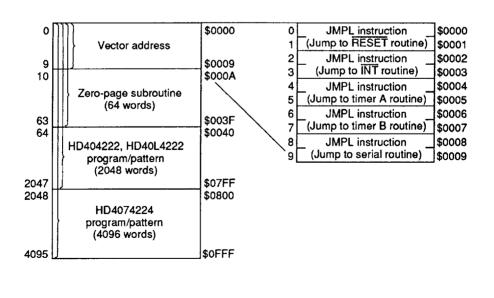

### **ROM Memory Map**

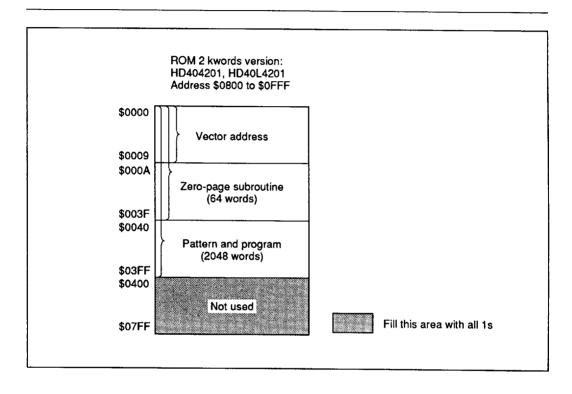

The areas in ROM are described below with its memory map shown in figure 1.

Vector Address Area: Locations \$0000 through \$0009 can be used for JMPL instructions to branch to the starting address of an initialization program for interrupt programs. After MCU reset or an interrupt is performed, the program is executed from a vector address.

Zero-Page Subroutine Area: Locations \$0000 through \$003F can be used for subroutines. The CAL instruction branches to subroutines within this area.

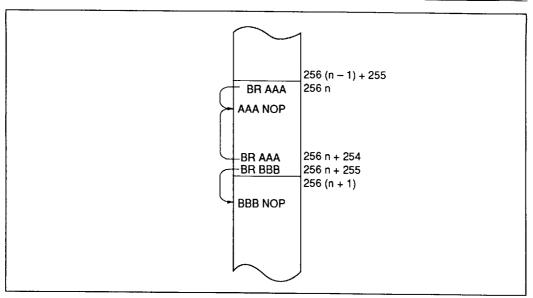

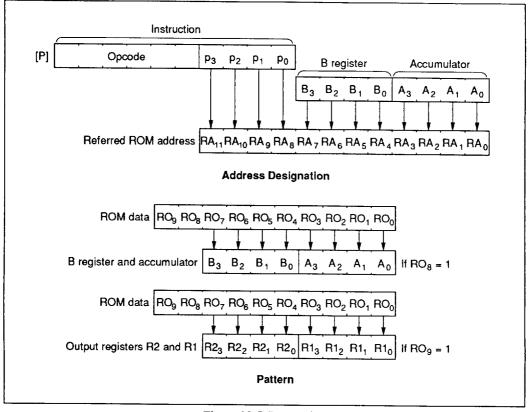

Pattern Area (\$0000 to \$03FF: HD404201, HD40L4201; \$0000 to \$07FF: HD404202, HD40L4202, HD404222, HD40L4222; \$0000 to \$0FFF: HD4074224): The P instruction allows reference to ROM data in this area as a pattern.

Program Area (\$0000 to \$03FF: HD404201, HD40L4201; \$0000 to \$07FF: HD404202, HD40L4202, HD40L4222; \$0000 to \$0FFF: HD4074224)

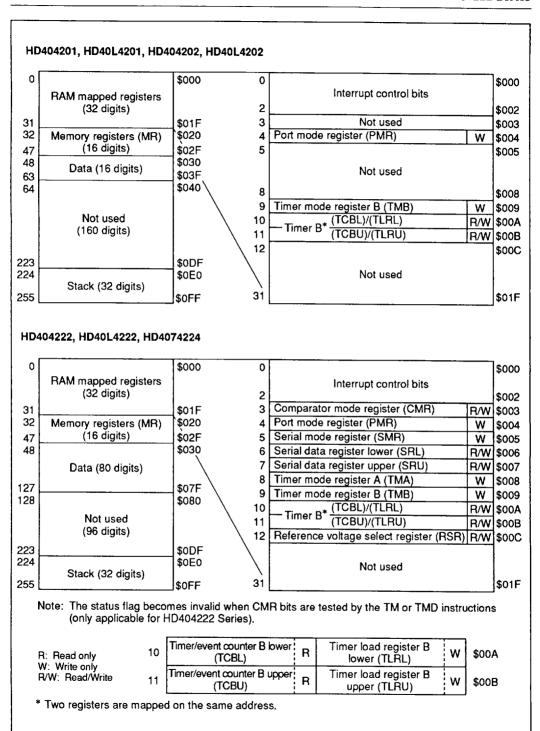

### **RAM Memory Map**

In addition to data and stack areas, interrupt control bits and special function registers are also mapped in RAM memory. The RAM memory map shown in figure 2 is described below.

Interrupt Control Bits Area (\$0000 to \$0002): The interrupt control bits area (figure 3) is used for interrupt control. This area and CMR (location \$03) register is accessible only by RAM bit manipulation instructions. However, the interrupt request

flag cannot be set by software. The RSP bit is used only to reset the stack pointer.

Note that if unusable bits are manipulated, the MCU may malfunction (HD404202 Series: bits 0, 1 of \$001, and \$002; HD404222 Series: bits 2, 3 of \$002).

Special Function Registers Area (\$003 to \$00C): The special function registers are the mode or data registers for external interrupt, the serial interface, the timer/counters, comparator and are also used as data control registers for I/O ports. These registers are classified into three types: write-only, read-only, and read/write, as shown in figure 2. These registers cannot be accessed by RAM bit manipulation instructions (except for CMR register).

Note that if the unusable locations are set, the MCU may mulfunction (only applicable for HD404202 Series \$003, \$005 to \$008 and \$00C).

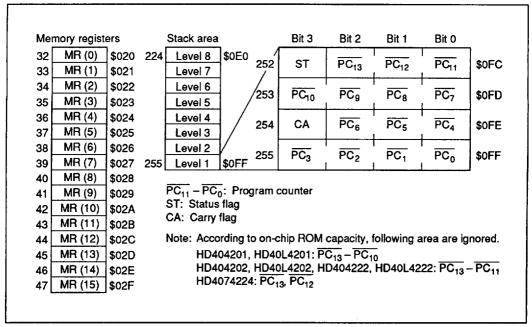

Data Area (\$020 to \$03F: HD404202 Series; \$020 to \$07F: HD404222 Series): The 16 digits of \$020 through \$02F are called memory registers (MR) and are also accessible by the LAMR and XMRA instructions (figure 4).

Stack Area (\$0E0 to \$0FF): Locations \$0E0 through \$0FF are reserved for LIFO stacks to save the contents of the program counter (PC), status flag (ST), and carry flag (CA) when a subroutine call (CAL or CALL instruction) or interrupt is performed. This area can be used as an 8-level nesting stack in which one level requires 4 digits. Figure 4 shows the stack area levels. The program counter is restored by the RTN and RTNI instructions. The status and carry flags are restored only by the RTNI instruction. When this area is not used as a stack, it becomes available as a data area.

#### HD404201, HD40L4201, HD404202, HD40L4202 \$0000 0 JMPL instruction \$0000 (Jump to reset routine) \$0001 1 Vector address 2 JMPL instruction \$0002 9 \$0009 (Jump to INT routine) 3 \$0003 \$000A 10 \$0004 4 Zero-page subroutine Not used 5 \$0005 (64 words) 6 JMPL instruction \$0006 \$003F 63 (Jump to timer B routine) 7 \$0007 64 \$0040 HD404201, HD40L4201 8 \$0008 program/pattern Not used \$0009 9 (1024 words) 1023 \$03FF 1024 \$0400 HD404202, HD40L4202 program/pattern (2048 words)

\$07FF

#### HD404222, HD40L4222, HD4074224

2047

Figure 1 ROM Memory Map

Figure 2 RAM Memory Map

|   | Bit 3                        | Bit 2                     | Bit 1                     | Bit 0                         |       |

|---|------------------------------|---------------------------|---------------------------|-------------------------------|-------|

| 0 | IM of external INT<br>(IMEX) | IF of external INT (IFEX) | Reset SP bit<br>(RSP)     | Interrupt enable flag<br>(IE) | \$000 |

| 1 | IM of timer B<br>(IMTB)      | IF of timer B<br>(IFTB)   | IM of timer A *<br>(IMTA) | IF of timer A *<br>(IFTA)     | \$001 |

| 2 | Not used                     | Not used                  | IM of serial *<br>(IMS)   | IF of serial *<br>(IFS)       | \$002 |

IF: Interrupt request flag IM: Interrupt mask IE: Interrupt enable flag SP: Stack pointer

Note: Each bit in the interrupt control bits area is set by the SEM/SEMD instruction, reset by the REM/REMD instruction, and tested by the TM/TMD instruction. It is not affected by other instructions. Furthermore, the interrupt request flag is not affected by the SEM/SEMD instruction.

The status flag becomes invalid when the unused bits and RSP bit are tested by the TM or TMD instruction.

\* Only applicable for the HD404222 Series.

Figure 3 Configuration of Interrupt Control Bits Area

Figure 4 Configuration of Memory Registers, Stack Area, and Stack Position

# **Functional Description**

### Registers and Flags

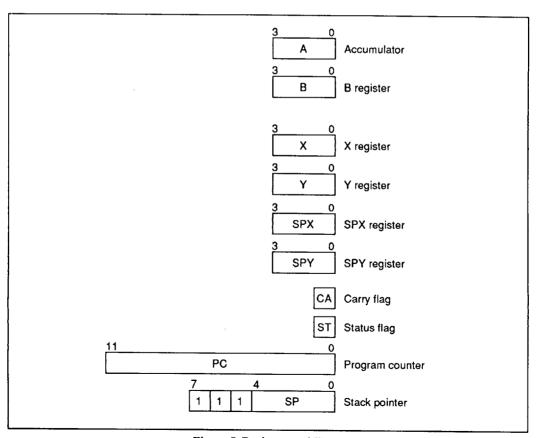

The MCU has eight registers and two flags for CPU operations (figure 5).

Accumulator (A), B Register (B): The 4-bit accumulator and B register hold the results of the arithmetic logic unit (ALU), and transfer data to/from memory, I/O, and other registers.

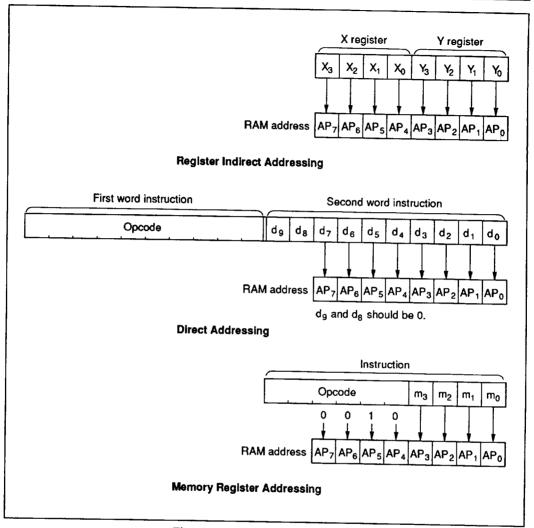

X Register (X), Y Register (Y): The X and Y registers are 4-bit registers used for indirect addressing of RAM. The Y register is also used for D port addressing.

SPX Register (SPX), SPY Register (SPY): The 4-bit registers SPX and SPY are used to assist the

X and Y registers, respectively.

Carry Flag (CA): The carry flag stores the overflow from the ALU generated by an arithmetic operation. It is also affected by the SEC, REC, ROTL, and ROTR instructions.

During an interrupt, the carry flag is pushed onto the stack and is pulled from the stack only by the RTNI instruction.

Status Flag (ST): The status flag holds the ALU overflow, ALU non-zero, and the results of a bit test instruction for arithmetic or compare instructions. The status flag is also used as a branch condition for the BR, BRL, CAL, and CALL instructions. The value of the status flag remains

Figure 5 Registers and Flags

unchanged until the next arithmetic, compare, or bit test instruction is executed. The status flag becomes a 1 after the BR, BRL, CAL, or CALL instruction was either executed or not. During an interrupt, the status flag is pushed onto the stack and can be pulled from the stack only by the RTNI instruction.

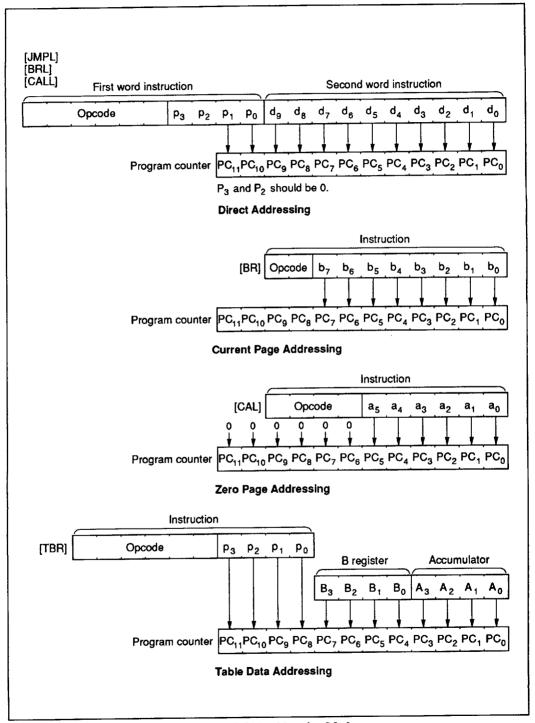

Program Counter (PC): The program counter is a 12-bit binary counter which controls the sequence in which the instructions stored in ROM are executed.

Stack Pointer (SP): The stack pointer (SP) is used to point to the address of the next stack area (up to 8 levels).

The stack pointer is initialized to RAM address \$FF. It is decremented by 4 when data is pushed onto the stack, and incremented by 4 when data is pulled from it. The stack can only be used up to 8 levels deep because the upper 3 bits of the stack pointer are fixed at 111.

Table 1 Initial Values After MCU Reset

|                                  |                                          | initial Value by<br>MCU Reset |                                                       |  |  |

|----------------------------------|------------------------------------------|-------------------------------|-------------------------------------------------------|--|--|

| Item                             |                                          | (RESET = 0)                   | Contents                                              |  |  |

| Program counter (PC)             |                                          | \$0000                        | Execute program from the top of ROM address           |  |  |

| Status flag (ST)                 |                                          | 1                             | Enable branching with conditional branch instructions |  |  |

| Stack pointer (SI                | P)                                       | \$0FF                         | Stack level is 0                                      |  |  |

| I/O pins,                        | Without pull-up MOS                      | 1                             | Enable input                                          |  |  |

| output registers                 | With pull-up MOS                         | 1                             | Enable input                                          |  |  |

|                                  | CMOS                                     | 1                             | _                                                     |  |  |

| Interrupt flags                  | Interrupt enable flag (IE)               | 0                             | Inhibit all interrupts                                |  |  |

| and mask                         | Interrupt request flag (IF)              | 0                             | No interrupt request                                  |  |  |

|                                  | Interrupt mask (IM)                      | 1                             | Mask interrupt request                                |  |  |

| Mode registers                   | Port mode register (PMR)                 | 000                           | See Port Mode Register section                        |  |  |

|                                  | Serial mode register (SMR)*              | 0000                          | See Serial Mode Register section                      |  |  |

|                                  | Timer mode register A (TMA)*             | 0000                          | See Timer Mode Register A section                     |  |  |

|                                  | Timer mode register B (TMB)              | 0000                          | See Timer Mode Register B section                     |  |  |

|                                  | Comparator mode register (CMR)*          | · 00                          | See Comparator Mode Register section                  |  |  |

| Comparator                       | Reference voltage select register (RSR)* | 0000                          | See Reference Voltage Select<br>Register section      |  |  |

| Timer/counters, serial interface | Prescaler                                | \$000                         |                                                       |  |  |

|                                  | Timer counter A (TCA)*                   | \$00                          |                                                       |  |  |

| •                                | Timer counter B (TCB)                    | \$00                          |                                                       |  |  |

|                                  | Timer load register B (TLR)              | \$00                          | _                                                     |  |  |

| •                                | Octal counter*                           | 000                           | _                                                     |  |  |

<sup>\*</sup> Only applicable for the HD404222 Series.

The stack pointer is initialized to \$FF by either MCU reset or RSP bit reset by the REM/REMD instruction.

Table 1 shows the components initialized by the MCU reset, and the status of each component.

#### Reset

Table 2 shows how registers recover from the stop mode.

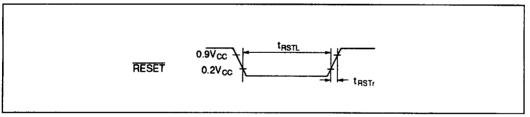

The MCU is reset by pulling the  $\overline{RESET}$  pin low. At power-on or when cancelling the stop mode, the reset period must satisfy  $t_{RC}$  for the oscillator to stabilize. In other cases, at least two instruction cycles are required for the MCU to be reset.

Take note that the reset signal is not acknowledged immediately at power-on by the MCU but at the time the oscillator has stabilized, so during this period the statuses within the MCU and at the I/O pins are not defined.

Table 2 Initial Values After MCU Reset

| Item                 |         | After MCU Reset to<br>Recover from Stop Mode                                          | After MCU Reset to<br>Recover from Other Modes                                             |

|----------------------|---------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Carry flag           | (CA)    | The contents of the items                                                             | The contents of the items                                                                  |

| Accumulator          | (A)     | before MCU reset are not<br>retained and must be initial-                             | before MCU reset are not retained and must be initial-                                     |

| B register           | (B)     | ized by software.                                                                     | ized by software.                                                                          |

| X/SPX registers      | (X/SPX) | <u>-</u>                                                                              | •                                                                                          |

| Y/SPY registers      | (Y/SPY) | -                                                                                     |                                                                                            |

| Serial data register | (SR)*   | _                                                                                     |                                                                                            |

| RAM                  |         | The contents of RAM before MCU reset (just before the STOP instruction) are retained. | The contents of RAM before MCU reset are not retained and must be initialized by software. |

<sup>\*</sup> Only applicable for the HD404222 Series.

#### Interrupts

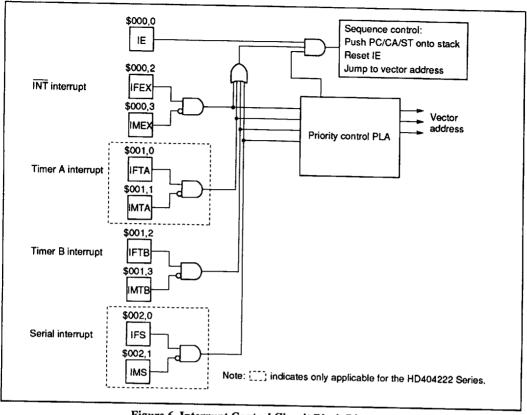

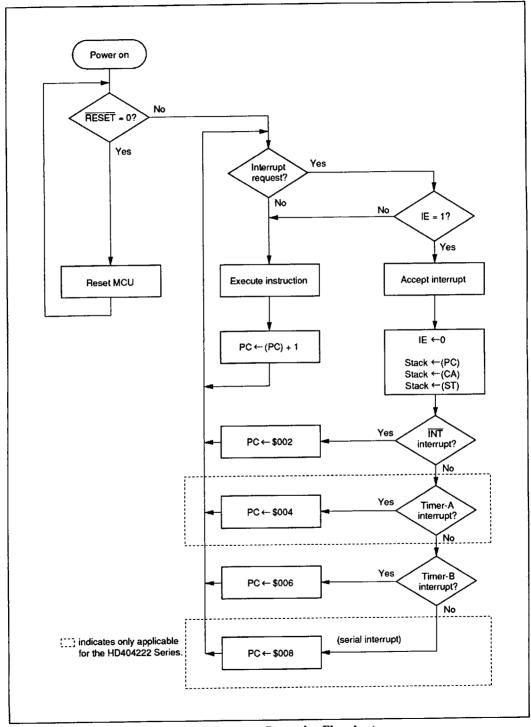

Two interrupt sources are available on the MCU of HD404202 Series. They are an external request (INT) and timer/counter (timer B). HD404222 Series has four interrupt sources: the two sources stated above, timer A and serial interface. For each source, an interrupt request flag (IF), interrupt mask (IM), and interrupt vector addresses are provided to control and maintain the interrupt request. An interrupt enable flag (IE) is also used to control interrupt operations.

Interrupt Control Bits and Interrupt Operation: The interrupt control bits are mapped on \$000 through \$002 of the RAM. These bits are accessible by RAM bit manipulation instructions. The interrupt request flag (IF) cannot be set by software. At MCU reset initialization, the IE and IF are cleared to 0, and IM is set to 1.

Figure 6 is a block diagram of the interrupt control circuit. Table 3 shows the interrupt priority and vector addresses, and table 4 shows the interrupt

conditions corresponding to each interrupt source.

An interrupt request is generated when the IF is set to 1 and IM is 0. If the IE is 1 during this period, the interrupt will be activated and vector addresses will be generated from the priority PLA corresponding to the interrupt sources.

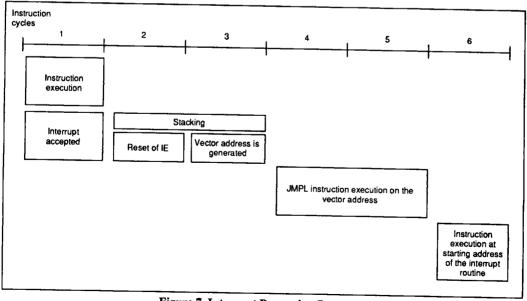

Figure 7 shows the interrupt processing sequence, and figure 8 shows the interrupt processing flowchart. If an interrupt is requested, the instruction being executed finishes in the first cycle. The IE is reset in the second cycle. Also in the second cycle and third cycle, the carry flag, status flag, and program counter are pushed onto the stack. Included in the third cycle is the generation of the vector address.

At each vector address, program the JMPL instruction to branch to the starting address of the interrupt program. The IF which caused the interrupt must be reset by software in the interrupt program.

Table 3 Vector Addresses and Interrupt Priority

#### HD404202 Series

| Reset/Interrupts | Priority | Vector Addresses |

|------------------|----------|------------------|

| RESET            | _        | \$000            |

| INT              | 1        | \$002            |

| Timer B          | 2        | \$006            |

#### HD404222 Series

| Reset/Interrupts | Priority | Vector Addresses |

|------------------|----------|------------------|

| RESET            | _        | \$000            |

| INT              | 1        | \$002            |

| Timer A          | 2        | \$004            |

| Timer B          | 3        | \$006            |

| Serial           | 4        | \$008            |

**Table 4 Interrupt Conditions**

### HD404202 Series

| Interrupt Control Bits | TNT | Timer B |

|------------------------|-----|---------|

| IE                     | 1   | 1       |

| IFEX · IMEX            | 1   | 0       |

| IFTB · IMTB            | *   | 1       |

<sup>\*</sup> indicates don't care

#### HD404222 Series

| Interrupt<br>Control Bits    | ĪNT | Timer A | Timer B | Serial |

|------------------------------|-----|---------|---------|--------|

| IE                           | 1   | 1       | 1       | 1      |

| $IFEX \cdot \overline{IMEX}$ | 1   | 0       | 0       | 0      |

| IFTA · ĪMTA                  | *   | 1       | 0       | 0      |

| IFTB · IMTB                  | *   | *       | 1       | 0      |

| IFS · IMS                    | *   | *       | *       | 1      |

<sup>\*</sup> indicates don't care

Figure 6 Interrupt Control Circuit Block Diagram

Figure 7 Interrupt Processing Sequence

Figure 8 Interrupt Processing Flowchart

Interrupt Enable Flag (IE: \$000, Bit 0): The interrupt enable flag (table 5) enables or disables interrupt requests. It is reset by an interrupt and set by the RTNI instruction.

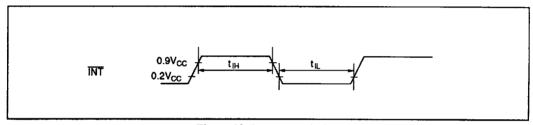

External Interrupt ( $\overline{\text{INT}}$ ): The external interrupt request input ( $\overline{\text{INT}}$ ) can be selected by the port mode register (PMR: \$004). Setting bit 2 of PMR causes the D<sub>5</sub>/ $\overline{\text{INT}}$  pin to be used as  $\overline{\text{INT}}$ .

The external interrupt request flag IFEX (table 6) is set at the falling edge of INT input.

The INT input can be used as a clock signal input to timer B, which counts up at each falling edge of the INT input. When using INT as the timer B external event input, the external interrupt mask IMEX (table 7) has to be set so that the INT interrupt request will not be accepted.

External Interrupt Request Flag (IFEX: \$000, Bit 2): The external interrupt request flag is set the falling edge of the INT input.

External Interrupt Mask (IMEX: \$000, Bit 3): The external interrupt mask (table 7) masks the external interrupt request.

Timer A Interrupt Request Flag (IFTA: \$001, Bit 0): The timer A interrupt request flag (table 8) is set by the timer A overflow output. It can be only used by the HD404222 Series.

Timer A Interrupt Mask (IMTA: \$001, Bit 1): The timer A interrupt mask (table 9) prevents an interrupt request from being generated by the timer A interrupt request flag. It can be only used by the HD404222 Series.

Table 5 Interrupt Enable Flag

| IE | Interrupt Enabled/Disabled |

|----|----------------------------|

| 0  | Disabled                   |

| 1  | Enabled                    |

Table 6 External Interrupt Request Flag

| IFEX | Interrupt Request |

|------|-------------------|

| 0    | No                |

| 1    | Yes               |

Table 7 External Interrupt Mask

| IMEX | Interrupt Request |

|------|-------------------|

| 0    | Enabled           |

| 1    | Disabled (masked) |

|      |                   |

Table 8 Timer A Interrupt Request Flag

| IFTA | Interrupt Request |  |

|------|-------------------|--|

| 0    | No                |  |

| 1    | Yes               |  |

Table 9 Timer A Interrupt Mask

| IMTA | Interrupt Request |

|------|-------------------|

| 0    | Enabled           |

| 1    | Disabled (masked) |

Timer B Interrupt Request Flag (IFTB: \$001, Bit 2): The timer B interrupt request flag (table 10) is set by the overflow output of timer B.

Timer B Interrupt Mask (IMTB: \$001, Bit 3): The timer B interrupt mask (table 11) prevents an interrupt request from being generated by the timer B interrupt request flag.

Serial Interrupt Request Flag (IFS: \$002, Bit 0): The serial interrupt request flag (table 12) will be set when the octal counter counts eight transmit clock signals, or when data transfer is discontinued by resetting the octal counter. It can be only used by the HD404222 Series.

Serial Interrupt Mask (IMS: \$002, Bit 1): The serial interrupt mask (table 13) masks the interrupt request. It can be only used by the HD404222 Series.

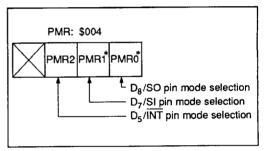

Port Mode Register (PMR: \$004): The 3-bit write-only port mode register controls the  $D_5/\overline{INT}$ ,  $D_7/SI$ , and  $D_8/SO$  pins as shown in table 14. The port mode register is initialized to \$0 by MCU reset. Therefore these pins are initially used as ports. Note that if unusable bit 3 is set, the MCU may malfunction.

Table 10 Timer B Interrupt Request Flag

| IFTB | Interrupt Request |

|------|-------------------|

| 0    | No                |

| 1    | Yes               |

Table 11 Timer B Interrupt Mask

| IMTB | Interrupt Request |  |

|------|-------------------|--|

| 0    | Enabled           |  |

| 1    | Disabled (masked) |  |

Table 12 Serial Interrupt Request Flag

| IFS | Interrupt Request |

|-----|-------------------|

| 0   | No                |

| 1   | Yes               |

Table 13 Serial Interrupt Mask

| IMS | Interrupt Request |  |

|-----|-------------------|--|

| 0   | Enabled           |  |

| 1   | Disabled (masked) |  |

Table 14 Port Mode Register

| PMR2 | D <sub>5</sub> /INT Pin                      |

|------|----------------------------------------------|

| 0    | Used as D <sub>5</sub> port input/output pin |

| 1    | Used as INT input pin                        |

| PMR1* | D <sub>7</sub> /SI Pin                       |

|-------|----------------------------------------------|

| 0     | Used as D <sub>7</sub> port input/output pin |

| 1     | Used as SI input pin                         |

| PMR0* | D <sub>8</sub> /SO Pin                       |

|-------|----------------------------------------------|

| 0     | Used as D <sub>8</sub> port input/output pin |

| 1     | Used as SO output pin                        |

PMR0 and PMR1 can be only used by the HD404222 Series.

# **Operating Modes**

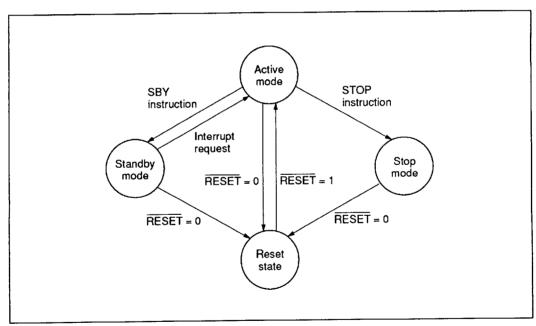

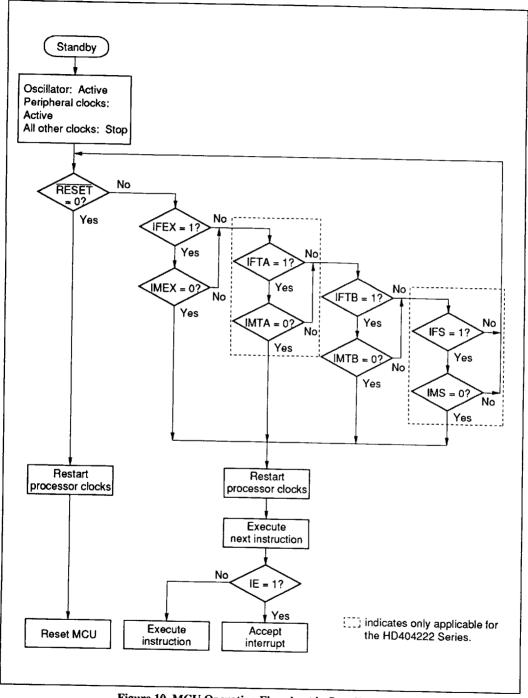

The MCU has two low-power dissipation modes, standby mode and stop mode (table 15). Figure 9 shows a mode transition diagram of these modes.

Standby Mode: Executing the SBY instruction places the MCU into standby mode. In standby

mode, the oscillator circuit, interrupts, timer/counters, and serial interface remain active. On the other hand, the CPU stops since the clock related to the instruction execution stops. Registers, RAM, and I/O pins retain the states they were in just before the MCU went into standby mode.

Table 15 Low-Power Dissipation Mode Function

| Low-Power<br>Dissipation<br>Mode | Instruction         | Oscillator<br>Circuit | instruction<br>Execution | Registers,<br>Flags | Interrupt<br>Function |

|----------------------------------|---------------------|-----------------------|--------------------------|---------------------|-----------------------|

| Standby mode                     | SBY instruction     | Active                | Stop                     | Retained            | Active                |

| Stop mode                        | STOP<br>instruction | Stop                  | Stop                     | Reset*1             | Stop                  |

Table 15 Low-Power Dissipation Mode Function (cont)

| Low-Power<br>Dissipation<br>Mode | RAM      | Input/<br>Output<br>Pins | Timer/<br>Counters,<br>Serial<br>Interface*3 | Comparator*3 | Canceliation<br>Method                  |

|----------------------------------|----------|--------------------------|----------------------------------------------|--------------|-----------------------------------------|

| Standby mode                     | Retained | Retained*2               | Active                                       | Stop         | RESET<br>input,<br>interrupt<br>request |

| Stop mode                        | Retained | High<br>impedance        | Stop                                         | Stop         | RESET<br>input                          |

Notes: \*1. The MCU recovers from stop mode by RESET input. Refer to table 1 for the contents of the flags and registers.

\*3. Serial interface and comparator can be only used by the HD404222 Series.

<sup>\*2.</sup> If an I/O circuit is active, an I/O current may flow, depending on the state of the I/O pin in standby mode. This current is in addition to the current dissipation in standby mode.

The Standby mode may be cancelled by enabling RESET or by asserting an interrupt request. In the former case, the MCU is reset. In the latter case, the MCU becomes active and executes the next instruction following the SBY instruction. After this instruction is completed and if the interrupt enable flag is 1 when an interrupt request asserted, the interrupt is executed, while if it is 0, the interrupt request is put on hold and normal instruction execution continues.

Figure 10 shows the flowchart of the standby mode.

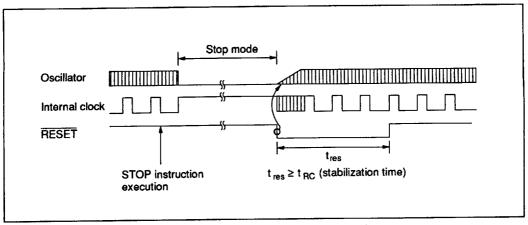

Stop Mode: Executing the STOP instruction brings the MCU into stop mode, in which the

oscillator circuit and all functions of the MCU stop.

The stop mode may be cancelled by resetting the MCU. At this time, as shown in figure 11, the RESET input must be applied for at least t<sub>RC</sub> for the oscillation to stabilize. (Refer to the AC Characteristics table.) After stop mode is cancelled, the RAM retains the state it was in just before the MCU went into stop mode, but the accumulator, B register, X/SPX and Y/SPY registers, carry flag, and serial data register will not retain their contents. (The serial data resister can be only used by the HD404222 Series.)

Figure 9 MCU Operation Mode Transition

Figure 10 MCU Operating Flowchart in Standby Mode

Figure 11 Timing of Stop Mode Cancellation

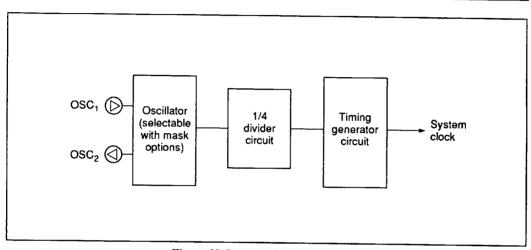

# **Internal Oscillator Circuit**

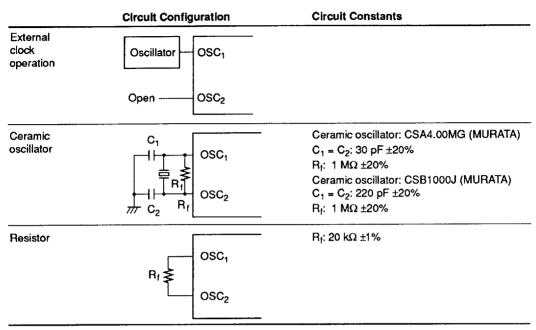

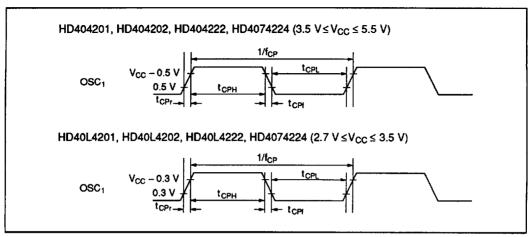

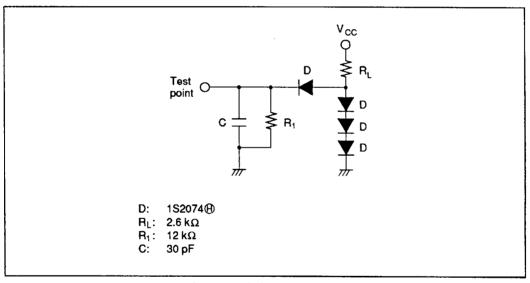

Figure 12 shows a block diagram of the internal oscillator circuit. Through mask options, either a ceramic oscillator or resistor can be selected as the oscillator type and connected to OSC<sub>1</sub> and

OSC<sub>2</sub>. See figure 13 for the layout of the ceramic oscillator. For other cases, an external clock operation is available.

Figure 12 Internal Oscillator Circuit

**Table 16 Examples of Oscillator Circuits**

Notes: The circuit parameters listed above are dependent on the ceramic oscillator and the floating capacitance when designing the board. In employing the resonator, consult with the ceramic oscillator manufacturer to determine the circuit parameters.

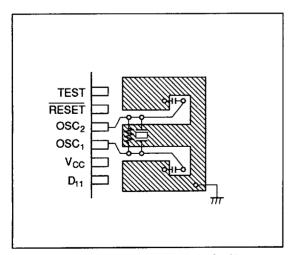

The wiring between OSC<sub>1</sub>, OSC<sub>2</sub>, and the elements should be as short as possible without crossing over other wires. Refer to the layout of the ceramic oscillator in figure 13.

Figure 13 Layout of the Ceramic Oscillator

# Input/Output

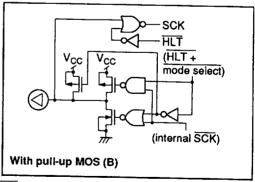

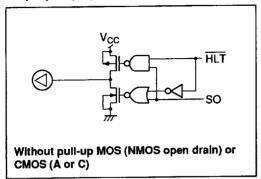

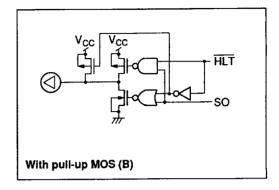

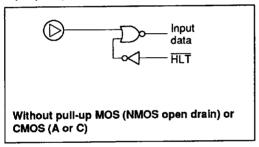

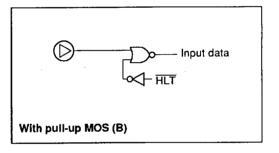

The MCU has 22 standard I/O pins. As for the mask ROM version of HD404201, HD40L4201, HD404202, HD404202, HD404222 and HD40L4222, one of three circuit types can be selected by the mask option for each standard pin: with pull-up MOS or without pull-up MOS (NMOS open drain) or CMOS.

The I/O pins for the HD4074224 are fixed as with pull-up MOS.

When every input/output pin is used as an input pin, the mask option and output data must be selected as specified in table 17.

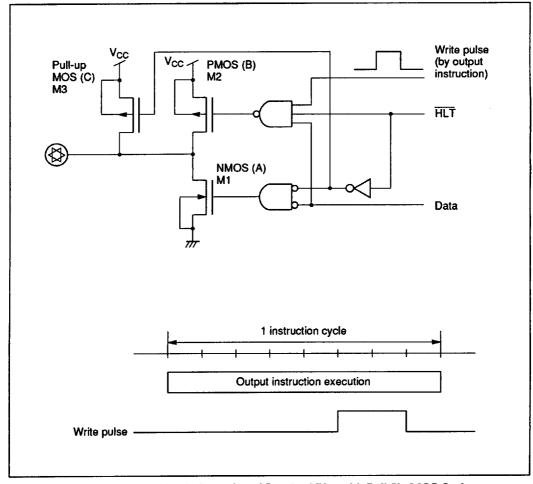

Output Circuit Operation of with Pull-Up MOS Standard Pins: In the standard pin option with pull-up MOS, the circuit shown in figure 14 is used to shorten the rise time of output.

When the MCU executes an output instruction, it generates a write pulse to the R port addressed by this instruction. This pulse will switch the PMOS (B) on (in figure 14) and shorten the rise time. The write pulse keeps PMOS on for two-eighths of the instruction cycle time. While the write pulse is 0, a high output level is maintained by the pull-up MOS (C).

When the HLT signal becomes 0 in stop mode, MOSs (A), (B), and (C) turn off. When the HLT signal is 1, the pins' states are maintained.

D Port: The D port has 14 discrete I/O pins, each of which can be addressed independently. The D port can be set/reset through the SED/RED and SEDD/REDD instructions, and can be tested through the TD and TDD instructions.

For the HD404222 Series pins  $D_5$  to  $D_{11}$  are multiplexed with pins  $\overline{INT}$ ,  $\overline{SCK}$ , SI, SO,  $V_{ref}$ ,  $COMP_0$ , and  $COMP_1$ , respectively. Setting, resetting, or testing non-existing ports results in invalid data. As for the HD404202 Series only pin  $D_5/\overline{INT}$  applies.

R Ports: The R ports are I/O pins that are accessed in 4-bit units. Data is input through the LAR and LBR instructions and output through the LRA and LRB instructions. Writing into non-existing ports will not affect the MCU, however, the values read from the non-existing ports cannot be guaranteed.

Unused I/O Pins: If unused I/O pins are left floating, the LSI may malfunction due to noise. The I/O pins should be fixed as follows to prevent malfunction.

- Select the option of without pull-up MOS for unused I/O pins and connect them to GND of the printed circuit board.

- For the HD404222 Series sets D<sub>5</sub>/INT, D<sub>6</sub>/SCK, D<sub>7</sub>/SI, D<sub>8</sub>/SO, D<sub>9</sub>/V<sub>ref</sub>, D<sub>10</sub>/COMP<sub>0</sub>, and D<sub>11</sub>/COMP<sub>1</sub> as D<sub>5</sub> to D<sub>11</sub>, respectively, by software. As for the HD404202 Series only pin D<sub>5</sub>/INT applies.

Table 17 Data Input from Common Input/Output Pins

| I/O Pin Circuit Typ | e                                     | Input Possible | Input Pin State |

|---------------------|---------------------------------------|----------------|-----------------|

| Standard pins       | CMOS                                  | No             |                 |

|                     | Without pull-up MOS (NMOS open drain) | Yes            | 1               |

|                     | With pull-up MOS                      | Yes            | 1               |

Figure 14 Output Circuit Operation of Standard Pins with Pull-Up MOS Option

## Table 18 I/O Pin Circuit Types

## Standard Pins

# I/O common pins (D<sub>0</sub>-D<sub>13</sub>, R1<sub>0</sub>-R1<sub>3</sub>, R2<sub>0</sub>-R2<sub>3</sub>)

# I/O common pins (SCK (output mode))\*

- Notes: 1. HD404202 Series: when selecting pin D<sub>5</sub> as  $\overline{\text{INT}}$  by software, the pull-up MOS will be disabled even if selecting mask option B (with pull-up MOS).

- 2. HD404222 and HD40L4222: when selecting pins D<sub>5</sub>, D<sub>6</sub>, and D<sub>7</sub> as INT, SCK, and SI input, respectively, by software, the pull-up MOS of each terminal will be disabled even if selecting mask option B (with pull-up MOS). HD4074224: pins D<sub>5</sub>, D<sub>6</sub>, and D<sub>7</sub> are fixed as with pull-up MOS (B). But when selecting these pins as INT, SCK, and SI input, respectively, by software, the pull-up MOS of each terminal will be disabled

- Only applicable for the HD404222 Series.

### Table 18 I/O Pin Circuit Types (cont)

#### Standard Pins

### Output pins (SO)\*

# Input pins (INT, SI\*, SCK\* (input mode))

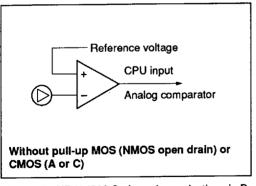

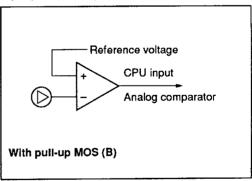

### Input pins (COMP<sub>0</sub>\*, COMP<sub>1</sub>\*)

# Input pins (COMP<sub>0</sub>\*, COMP<sub>1</sub>\*)

- Notes: 1. HD404202 Series: when selecting pin D<sub>5</sub> as INT by software, the pull-up MOS will be disabled even if selecting mask option B (with pull-up MOS).

- HD404222 and HD40L4222: when selecting pins D<sub>5</sub>, D<sub>6</sub>, and D<sub>7</sub> as INT, SCK, and SI input, respectively, by software, the pull-up MOS of each terminal will be disabled even if selecting mask option B (with pull-up MOS).

HD4074224: pins D<sub>5</sub>, D<sub>6</sub>, and D<sub>7</sub> are fixed as with pull-up MOS (B). But when selecting these pins as INT, SCK, and SI input, respectively, by software, the pull-up MOS of each terminal will

- Only applicable for the HD404222 Series.

be disabled

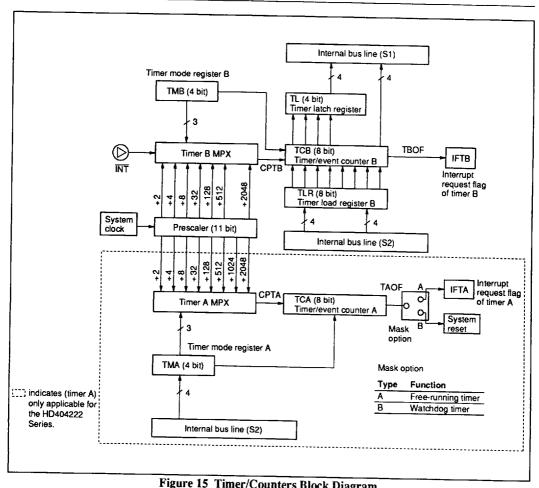

### **Timers**

The MCU of HD404202 Series contains a prescaler and a timer/counter (timer B), where as one prescaler and two timer/counters (timers A and B) are available on the MCU of HD404222 Series. Figure 15 shows the block diagram of timer/counters. The prescaler is an 11-bit counter, timer A is an 8-bit free-running/watchdog timer, and timer B is an 8-bit auto-reload timer/event counter.

Prescaler: The system clock signal is input to the prescaler. At MCU reset, the prescaler is initialized to \$000 and starts dividing the system clock frequency.

The prescaler keeps counting up except at MCU reset and stop mode. The prescaler provides clock signals to timer A, timer B, and the serial interface (Timer A and the serial interface can be only used by the HD404222 Series). The prescaler divide ratio is selected by timer mode register A (TMA), timer mode register B (TMB), and serial mode register (SMR) (TMA and SMR can be only used by the HD404222 Series).

Figure 15 Timer/Counters Block Diagram

Timer A Operation (Only Applicable for the HD404222 Series): Timer A's function is selected via the mask option.

When timer A is used as a free-running timer, it counts up every input clock signal after timer A has been initialized to \$00 by MCU reset. When the next clock signal is input after timer A counts up to \$FF, timer A is set to \$00 again, and generates an overflow output. This sets the timer A interrupt request flag (IFTA: \$001, bit 0) to 1. Therefore, this timer can function as an interval timer periodically generating overflow output at every 256th clock signal. The clock signals input to timer A are selected by timer mode register A (TMA: \$008).

Note that when timer A is used as a free-running timer, if setting bit 3 of timer mode resister A may cause the MCU to malfunction.

When timer A is used as a watchdog timer, the input clock is specified as 1/2048 output divided by the prescaler. The watchdog timer is initialized to \$00 at MCU reset, then counts up every input clock signal. If a clock signal is applied after the timer becomes \$FF, an overflow is generated and the MCU is reset.

After reset, the MCU re-executes the program from

the beginning. The program must set bit 3 of timer mode register A to reset timer counter A.

Timer B Operation: Timer mode register B (TMB: \$009) selects the auto-reload function, input clock source, and the prescaler divide ratio for timer B. When the external event input is used as an input clock signal to timer B, select  $D_5/\overline{\text{INT}}$  as  $\overline{\text{INT}}$  and set the external interrupt mask (IMEX) to prevent an external interrupt request from occurring.

Timer B is initialized by software according to the data written in timer load register B. Timer B counts up at every input clock signal. When the next clock signal is input after timer B is set to \$FF, timer B will generate an overflow output. Then, if the auto-reload function is selected, timer B is initialized to the value of timer load register B. If it is not selected, timer B goes back to \$00. The timer B interrupt request flag (IFTB: \$001, bit 2) will hold the overflow output.

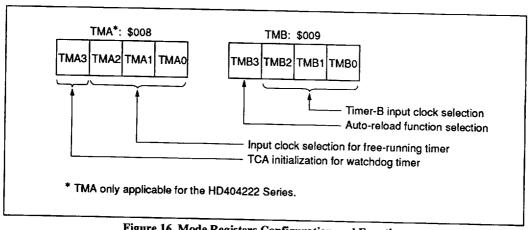

Timer Mode Register A (TMA: \$008): Four-bit write-only timer mode register A selects the timer function for timer A and the prescaler divide ratio of timer A's clock input as shown in table 19. Timer mode register A is initialized to \$0 by MCU reset.

Table 19 Timer Mode Register A

| TMA2 | TMA1 | TMA0 | Prescaler Divide Ratio |

|------|------|------|------------------------|

| 0    | 0    | 0    | ÷ 2048                 |

| 0    | 0    | 1    | + 1024                 |

| 0    | 1    | 0    | + 512                  |

| 0    | 1    | 1    | + 128                  |

| 1    | 0    | 0    | + 32                   |

| 1    | 0    | 1    | + 8                    |

| 1    | 1    | 0    | + 4                    |

| 1    | 1    | 1    | + 2                    |

Table 20 Timer Mode Register B

**Auto-Reload Function**

| 0    | No   |      |                                               |

|------|------|------|-----------------------------------------------|

| 1    | Yes  |      |                                               |

| TMB2 | TMB1 | тмво | Prescaler Divide Ratio,<br>Clock Input Source |

| 0    | 0    | 0    | + 2048                                        |

| 0    | 0    | 1    | + 512                                         |

| 0    | 1    | 0    | + 128                                         |

| 0    | 1    | 1    | + 32                                          |

| 1    | 0    | 0    | +8                                            |

| 1    | 0    | 1    | + 4                                           |

| 1    | 1    | 0    | + 2                                           |

| 1    | 1    | 1    | INT (external event input)                    |

**TMB3**

Timer Mode Register B (TMB: \$009): Four-bit write-only timer mode register B (TMB) selects the auto-reload function, the prescaler divide ratio, and the source of the clock input signal as shown in table 20. Timer mode register B is initialized to \$0 by MCU reset.

The operation mode of timer B changes at the second instruction cycle after timer mode register B is written to. Timer B should be initialized by writing data into timer load register B after the contents of TMB are changed. The configuration and function of timer mode register B is shown in figure 16.

Timer B Load Register (TCBL: \$00A, TCBU: \$00B, TLRL: \$00A, TLRU: \$00B): Timer B consists of an 8-bit write-only timer load register and

an 8-bit read-only timer/event counter. Each has a low-order digit (TCBL: \$00A, TLRL: \$00A) and a high-order digit (TCBU: \$00B, TLRU: \$00B) (figure 2).

The timer/event counter can be initialized by writing data into timer load register B. In this case, write the low-order digit first, and then the high-order digit. The timer/event counter is initialized when the high-order digit is written. The timer load register is initialized to \$00 by MCU reset.

The counter value of timer B can be obtained by reading timer counter. In this case, read the high-order digit first, and then the low-order digit. The count value of the low-order digit is latched at the time when the high-order digit is read.

Figure 16 Mode Registers Configuration and Function

### **Serial Interface**

Only applicable for the HD404222 Series.

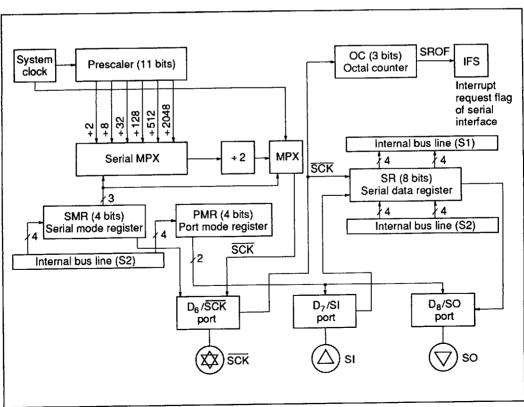

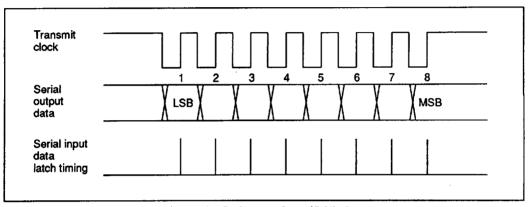

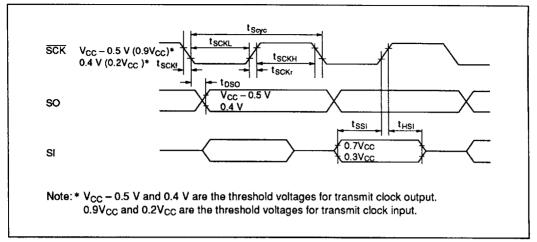

The serial interface is used to transmit/receive 8-bit data serially. It consists of the serial data register, serial mode register, octal counter, and multiplexer, as illustrated in figure 17. Pin D<sub>6</sub>/SCK and the transmit clock signal are controlled by the serial mode register. The contents of the serial data register can be written into or read out by software. The data in the serial data register can be shifted synchronously with the transmit clock signal.

The STS instruction initiates serial interface operations and resets the octal counter to 000. The counter starts to count at the falling edge of the transmit clock ( $\overline{SCK}$ ) signal and increments by one at the rising edge of the  $\overline{SCK}$ . When the octal counter is reset to 000 after eight transmit clock

signals, or when a transmit/receive operation is discontinued by resetting the octal counter, the serial interrupt request flag will be set.

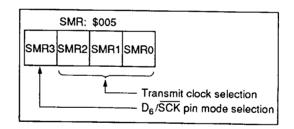

Serial Mode Register (SMR: \$005): The 4-bit write-only serial mode register controls the D<sub>6</sub>/SCK, prescaler divide ratio, and transmit clock source as shown in table 21.

A write signal sent to the serial mode register controls the operating state of the serial interface.

The write signal to the serial mode register stops the serial data register and octal counter from using the transmit clock, and it also resets the octal counter to 000 simultaneously. Therefore, when the serial interface is in the transfer state, the write signal causes the serial mode register to cease the

Figure 17 Serial Interface Block Diagram

data transfer and to set the serial interrupt request flag.

The contents of the serial mode register will be changed on the second instruction cycle after writing into the serial mode register. Therefore, it is necessary to execute the STS instruction after the data in the serial mode register has been changed completely. The serial mode register will be reset to \$0 by MCU reset.

Serial Data Register (SRL: \$006, SRU: \$007): The 8-bit read/write serial data register consists of a low-order digit (SRL: \$006) and a high-order digit (SRU: \$007).

The data in the serial data register is output from the SO pin, from LSB to MSB, synchronously with the falling edge of the transmit clock signal. At the same time, external data will be input from the SI pin to the serial data register, to LSB first, synchronously with the rising edge of the transmit clock. Figure 18 shows the I/O timing chart for the transmit clock signal and the data.

The read/write operations of the serial data register should be performed after the completion of data transmission/reception. Otherwise, the data may not be guaranteed.

Selecting and Changing the Operation Mode: Table 22 shows the serial interface operation modes which are determined by a combination of the values in the port mode register and in the serial mode register. Initialize the serial interface by the write signal to the serial mode register when the operation mode is changed.

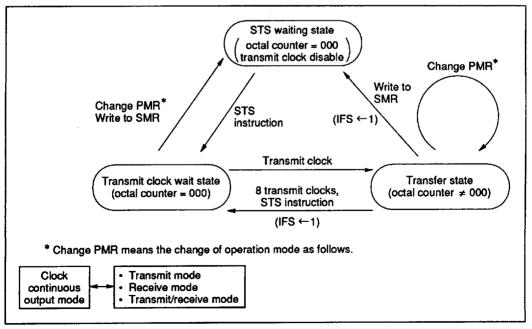

Operating State of the Serial Interface: The serial interface has three operating states: the STS waiting state, transmit clock wait state, and transfer state, as shown in figure 19.

Table 21 Serial Mode Register

| SMR3 | D <sub>6</sub> /SCK                          |

|------|----------------------------------------------|

| 0    | Used as D <sub>6</sub> port input/output pin |

| 1    | Used as SCK input/output pin                 |

#### **Transmit Clock**

| SMR2 | SMR1 | SMR0 | D <sub>6</sub> /SCK Port | Clock Source   | Prescaler<br>Divide Ratio | System Clock<br>Divide Ratio |

|------|------|------|--------------------------|----------------|---------------------------|------------------------------|

| 0    | 0    | 0    | SCK output               | Prescaler      | + 2048                    | + 4096                       |

| 0    | 0    | 1    | SCK output               | Prescaler      | + 512                     | + 1024                       |

| 0    | 1    | 0    | SCK output               | Prescaler      | + 128                     | + 256                        |

| 0    | 1    | 1    | SCK output               | Prescaler      | + 32                      | + 64                         |

| 1    | 0    | 0    | SCK output               | Prescaler      | + 8                       | + 16                         |

| 1    | 0    | 1    | SCK output               | Prescaler      | + 2                       | + 4                          |

| 1    | 1    | 0    | SCK output               | System clock   | _                         | + 1                          |

| 1    | 1    | 1    | SCK input                | External clock |                           |                              |

Table 22 Serial Interface Operation Mode

| SMR3 | PMR1 | PMR0 | Serial Interface<br>Operating Mode |

|------|------|------|------------------------------------|

| 1    | 0    | 0    | Clock continuous output mode       |

| 1    | 0    | 1    | Transmit mode                      |

| 1    | 1    | 0    | Receive mode                       |

| 1    | 1    | 1    | Transmit/receive mode              |

Figure 18 Serial Interface I/O Timing

Figure 19 Serial Interface Operation States

The STS waiting state is the initialization of the serial interface. In this state, the serial interface does not operate even if the transmit clock is applied.

If the STS instruction is executed, the serial interface shifts to the transmit clock wait state. In this state the falling edge of the first transmit clock causes the serial interface to shift to the transfer state, in which the octal counter counts up and the serial data register shifts simultaneously. If clock continuous output mode is selected, however, the serial interface stays in the transmit clock wait state while the transmit clock outputs continuously.

The octal counter becomes 000 again after 8 transmit clocks or after the execution of the STS instruction, so that the serial interface is returned to the transmit clock wait state and the serial interrupt

request flag is set simultaneously.

When the internal transmit clock is selected, the transmit clock output is triggered by the execution of the STS instruction, and stops after 8 clocks.

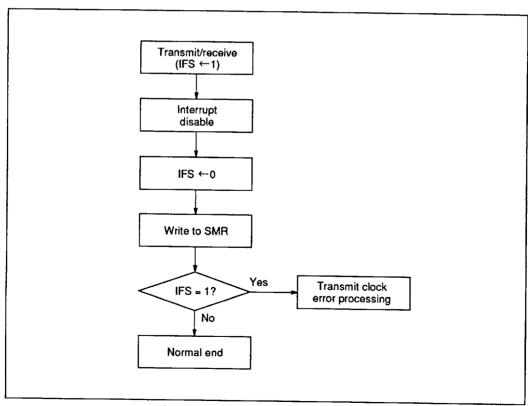

Transmit Clock Error Detection: The serial interface functions abnormally when the transmit clock is disturbed by external noise. In this case, transmit clock errors can be detected by the procedure shown in figure 20.

If more than 8 transmit clocks are applied in the transmit clock wait state, the state of the serial interface shifts in the following sequence: transfer state, transmit clock wait state, and transfer state again. The serial interrupt flag should be reset before entering into the STS state by writing data to SMR. This procedure causes the serial interface request flag to be set again.

Figure 20 Transmit Clock Error Detection

### Comparator

Only applicable for the HD404222 Series.

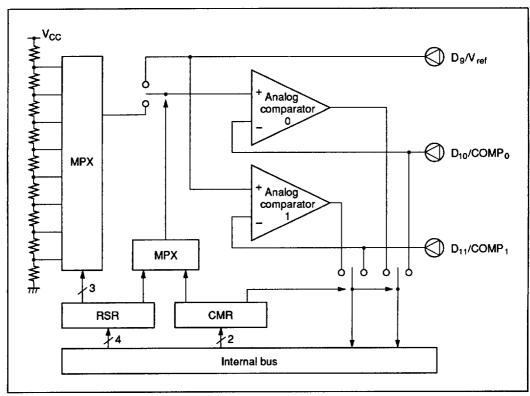

The MCU has two-channel comparators that compare input data with the reference voltage.

Figure 21 shows the comparator block diagram. The comparator block consists of two analog comparators, the comparator mode register (CMR) which selects the comparator operation, the reference voltage select register (RSR) which selects the reference voltage, a ladder resistance which generates the internal reference voltage, and peripheral circuits.

For the  $COMP_0$  input, either the external reference voltage or the internal reference voltage, which is generated by dividing  $V_{CC}$  with the internal ladder resistance, can be selected as the reference voltage.

For the COMP<sub>1</sub> input, only the external reference voltage is used; the internal reference voltage cannot be selected.

The power consumption increases after the comparator operation is selected by CMR, because direct current is constantly supplied to assure the analog comparator characteristics. To reduce the power consumption during comparator use, the comparator operation should not be selected by software except when analog comparison is required. In this case, a maximum of two instruction cycles are required after the comparator operation is selected in order for the analog comparator to stabilize and operate correctly. Therefore, the comparison result should be read at least two instruction cycles after the comparator operation is selected.

Figure 21 Comparator Block Diagram

The comparison result is obtained by executing the TD or TDD instruction. When the analog input voltage is higher than the reference voltage, a 1 is read as input data from the comparator. The comparator automatically stops operating in standby and stop modes.

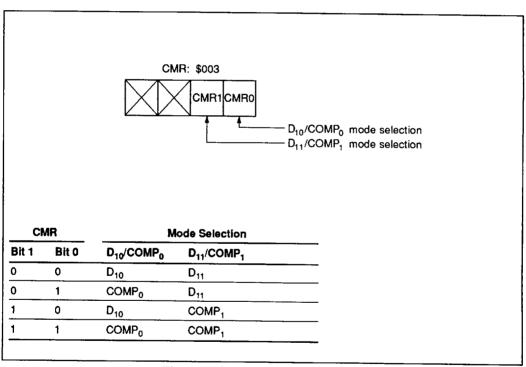

Comparator Mode Register (CMR: \$003): This 2-bit register selects the  $D_{10}/COMP_0$  and  $D_{11}/COMP_1$  functions.

CMR is only affected by the bit manipulation instructions (set by the SEM or SEMD instruction and reset by the REM or REMD instruction). It is

initialized to \$0 by MCU reset. Therefore, it becomes input/output mode after MCU reset.

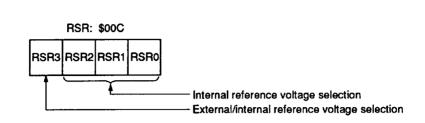

Reference Voltage Select Register (RSR: \$00C): This 4-bit read/write register selects the COMP<sub>0</sub> reference voltage for the analog comparator from the eight-level internal voltage or the external voltage. It is initialized to \$0 by MCU reset.

Notes for Use: When using the analog comparator, carefully program the data output instruction and data input into the port next to  $COMP_0$  and  $COMP_1$  to assure precise and stabilized comparator operation.

Figure 22 Comparator Mode Register

|        | R         | SR    |       |                                                               |

|--------|-----------|-------|-------|---------------------------------------------------------------|

| Bit 3  | Bit 2     | Bit 1 | Bit 0 | Reference Voltage                                             |

| 0      | 0         | 0     | 0     | 1/11 V <sub>CC</sub>                                          |

| 0      | 0         | 0     | 1     | 2/11 V <sub>CC</sub>                                          |

| 0      | 0         | 1     | 0     | 3/11 V <sub>CC</sub>                                          |

| 0      | 0         | 1     | 1     | 4/11 V <sub>CC</sub>                                          |

| 0      | 1         | 0     | 0     | 5/11 V <sub>CC</sub>                                          |

| 0      | 1         | 0     | 1     | 6/11 V <sub>CC</sub>                                          |

| 0      | 1         | 1     | 0     | 7/11 V <sub>CC</sub>                                          |

| 0      | 1         | 1     | 1     | 8/11 V <sub>CC</sub>                                          |

| 1      | _         | _     |       | External V <sub>ref</sub> (D <sub>9</sub> /V <sub>ref</sub> ) |

| — indi | cates 0 o | r 1   |       |                                                               |