# intها.

# 80286 MICROPROCESSOR WITH MEMORY MANAGEMENT AND PROTECTION

(80286-12, 80286-10, 80286-8)

- High Performance HMOS III Technology

- Large Address Space:

- 16 Megabytes Physical

- 1 Gigabyte Virtual per Task

- Integrated Memory Management, Four-Level Memory Protection and Support for Virtual Memory and Operating **Systems**

- High Bandwidth Bus Interface (12.5 Megabyte/Sec)

- **Industry Standard O.S. Support:** – MS-DOS\*, UNIX\*\*, XENIX\*, IRMX®

- **Optional Processor Extension:** 80287 High Performance 80-bit **Numeric Data Processor**

- **Two 8086 Upward Compatible Operating Modes:**

- 8086 Real Address Mode

- Protected Virtual Address Mode

- Complete System Development Support:

- Assembler, PL/M, Pascal and **FORTRAN**

- Available in:

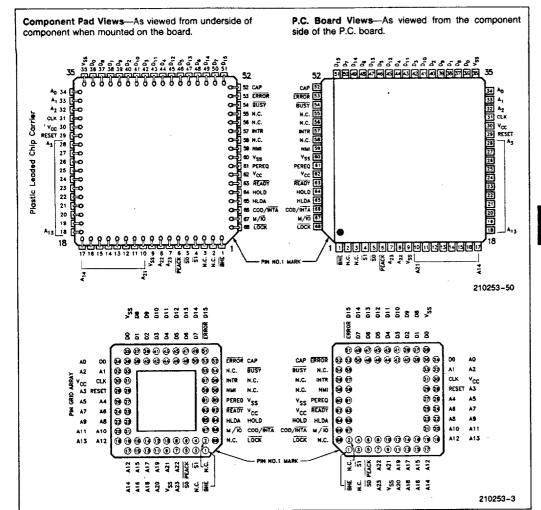

- 68-Pin PLCC (Plastic Leaded Chip Carrier)

- 68-Pin PGA (Pin Grid Arrav)

(See Packaging Spec., Order #231369)

The 80286 is an advanced, high-performance microprocessor with specially optimized capabilities for multiple user and multi-tasking systems. The 80286 has built-in memory protection that supports operating system and task isolation as well as program and data privacy within tasks. A 12.5 MHz 80286 provides six times or more throughput than the standard 5 MHz 8086. The 80286 includes memory management capabilities that map 230 (one gigabyte) of virtual address space per task into 224 bytes (16 megabytes) of physical memory.

The 80286 is upward compatible with 8086 and 88 software. Using 8086 real address mode, the 80286 is object code compatible with existing 8086, 88 software. In protected virtual address mode, the 80286 is source code compatible with 8086, 88 software and may require upgrading to use virtual addresses supported by the 80286's integrated memory management and protection mechanism. Both modes operate at full 80286 performance and execute a superset of the 8086 and 88 instructions.

The 80286 provides special operations to support the efficient implementation and execution of operating systems. For example, one instruction can end execution of one task, save its state, switch to a new task, load its state, and start execution of the new task. The 80286 also supports virtual memory systems by providing a segment-not-present exception and restartable instructions.

- \*XENIX and MS-DOS are trademarks of Microsoft Corp.

- \*\*UNIX is a trademark of UNIX Systems Laboratories.

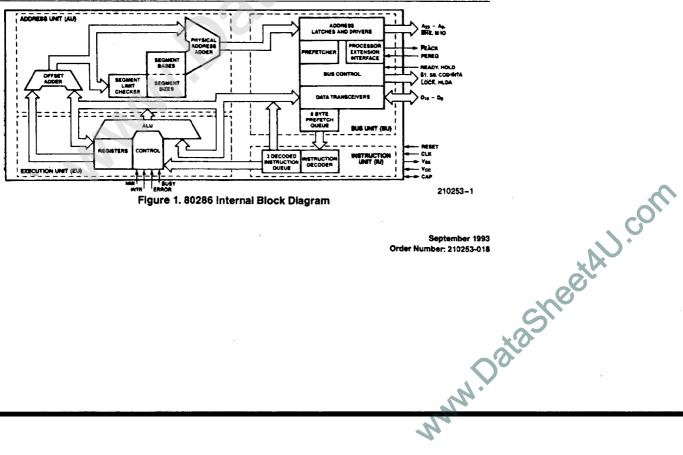

Figure 1. 80286 Internal Block Diagram

Order Number: 210253-018

2-60

intel

80286

**Table 1. Pin Description**

The following pin function descriptions are for the 80286 microprocessor:

| Symbol                          | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                             | Name :     | and Functi                         | on                                                                                           |

|---------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------|----------------------------------------------------------------------------------------------|

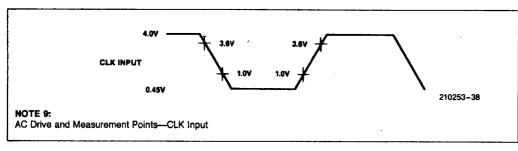

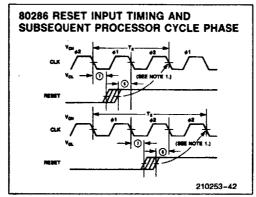

| CLK                             | I    | SYSTEM CLOCK provides the fundamental timing for 80286 systems. It is divided by two inside the 80286 to generate the processor clock. The internal divide-by-two circuitry can be synchronized to an external clock generator by a LOW to HIGH transition on the RESET input.                                                                                                                                        |                                                                                                                                                                                                                                                                                                             |            |                                    |                                                                                              |

| D <sub>15</sub> -D <sub>0</sub> | 1/0  | outputs data duris                                                                                                                                                                                                                                                                                                                                                                                                    | DATA BUS inputs data during memory, I/O, and interrupt acknowledge read cycles; outputs data during memory and I/O write cycles. The data bus is active HIGH and floats to 3-state OFF during bus hold acknowledge.                                                                                         |            |                                    |                                                                                              |

| A <sub>23</sub> -A <sub>0</sub> | 0    | to be transferred active HIGH and                                                                                                                                                                                                                                                                                                                                                                                     | oπ nins D⇒                                                                                                                                                                                                                                                                                                  | A          | rollOW due                         | t addresses. A0 is LOW when data is<br>ing I/O transfers. The address bus is<br>acknowledge. |

| BHE                             | 0    | BUS HIGH ENAE<br>Eight-bit oriented<br>BHE to condition                                                                                                                                                                                                                                                                                                                                                               | BUS HIGH ENABLE indicates transfer or data on the upper byte of the data bus. D <sub>15-8</sub> . Eight-bit oriented devices assigned to the upper byte of the data bus would normally use BHE to condition chip select functions. BHE is active LOW and floats to 3-state OFF during bus hold acknowledge. |            |                                    |                                                                                              |

|                                 |      |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                             | BHE and    | A0 Encod                           | ings                                                                                         |

|                                 |      | BHE Value                                                                                                                                                                                                                                                                                                                                                                                                             | A0 Value                                                                                                                                                                                                                                                                                                    |            |                                    | Function                                                                                     |

|                                 |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                           | Word tran  |                                    |                                                                                              |

| ĺ                               |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 0                                                                                                                                                                                                                                                                                                         | Byte tran  | sfer on upp                        | er half of data bus (D <sub>15</sub> -D <sub>8</sub> )                                       |

|                                 |      |                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                           | Will neve  | FOCCUL                             | er half of data bus (D <sub>7-0</sub> )                                                      |

| \$1, S0                         | 0    | BUS CYCLE STATUS indicates initiation of a bus cycle and, along with M/IO and COD INTA, defines the type of bus cycle. The bus is in a T <sub>S</sub> state whenever one or both are tS1 and S0 are active LOW and float to 3-state OFF during bus hold acknowledge.                                                                                                                                                  |                                                                                                                                                                                                                                                                                                             |            | state whenever one or both are LOW |                                                                                              |

|                                 |      |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                             |            | le Status I                        |                                                                                              |

|                                 |      | COD/INTA                                                                                                                                                                                                                                                                                                                                                                                                              | M/IO                                                                                                                                                                                                                                                                                                        | <u>\$1</u> | <u>50</u>                          | Bus Cycle Initiated                                                                          |

|                                 |      | 0 (LOW)                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                           | 0          | 0                                  | Interrupt acknowledge                                                                        |

|                                 |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                           | 0          | 0                                  | Will not occur Will not occur                                                                |

|                                 |      | ŏ                                                                                                                                                                                                                                                                                                                                                                                                                     | ő                                                                                                                                                                                                                                                                                                           | 1          | 1                                  | None; not a status cycle                                                                     |

|                                 |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                           | 0          | Ó                                  | IF A1 = 1 then halt; else shutdown                                                           |

|                                 |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                           | 0          | 1 1                                | Memory data read                                                                             |

|                                 |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                           | 1          | 0                                  | Memory data write None; not a status cycle                                                   |

|                                 |      | 1 (HIGH)                                                                                                                                                                                                                                                                                                                                                                                                              | ó                                                                                                                                                                                                                                                                                                           | ò          | ò                                  | Will not occur                                                                               |

|                                 |      | 1 '                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                           | 0          | 1                                  | I/O read                                                                                     |

| 1                               |      | 11                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                           | 1          | 0                                  | I/O write                                                                                    |

|                                 |      | 1;                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                           | 1          | 1 0                                | None; not a status cycle<br>Will not occur                                                   |

| 1                               |      | i                                                                                                                                                                                                                                                                                                                                                                                                                     | i                                                                                                                                                                                                                                                                                                           | ŏ          | 1                                  | Memory instruction read                                                                      |

|                                 |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                           | 1          | o                                  | Will not occur                                                                               |

|                                 |      | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                           | 1          | 1                                  | None; not a status cycle                                                                     |

| M/ĪŌ                            | 0    | MEMORY I/O SELECT distinguishes memory access from I/O access. If HIGH during T <sub>s</sub> , a memory cycle or a halt/shutdown cycle is in progress. If LOW, an I/O cycle or an interrupt acknowledge cycle is in progress. M/IO floats to 3-state OFF during bus hold acknowledge.                                                                                                                                 |                                                                                                                                                                                                                                                                                                             |            |                                    |                                                                                              |

| COD/INTA                        | 0    | CODE/INTERRUPT ACKNOWLEDGE distinguishes instruction fetch cycles from memory data read cycles. Also distinguishes interrupt acknowledge cycles from I/O cycles. COD/INTA floats to 3-state OFF during bus hold acknowledge. Its timing is the same as M/IO.                                                                                                                                                          |                                                                                                                                                                                                                                                                                                             |            |                                    |                                                                                              |

| LOCK                            | 0    | BUS LOCK indicates that other system bus masters are not to gain control of the system bus for the current and the following bus cycle. The LOCK signal may be activated explicitly by the "LOCK" instruction prefix or automatically by 80286 hardware during memory XCHG instructions, interrupt acknowledge, or descriptor table access. LOCK is active LOW and floats to 3-state OFF during bus hold acknowledge. |                                                                                                                                                                                                                                                                                                             |            |                                    |                                                                                              |

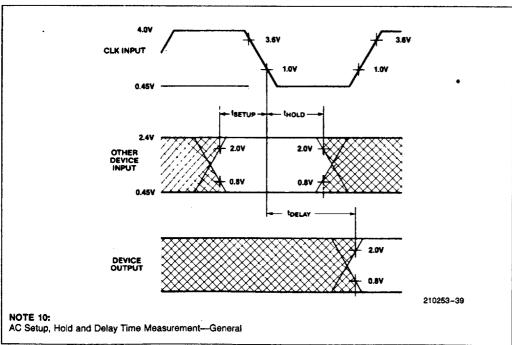

| READY                           | ı    | BUS READY terminates a bus cycle. Bus cycles are extended without limit until terminated by READY LOW. READY is an active LOW synchronous input requiring setup and hold times relative to the system clock be met for correct operation. READY is ignored during bus hold acknowledge.                                                                                                                               |                                                                                                                                                                                                                                                                                                             |            |                                    |                                                                                              |

# Table 1. Pin Description (Continued)

| Symbol         | Type | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

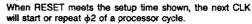

| HOLD<br>HLDA   | 0    | BUS HOLD REQUEST AND HOLD ACKNOWLEDGE control ownership of the 80286 local bus. The HOLD input allows another local bus master to request control of the local bus. When control is granted, the 80286 will float its bus drivers to 3-state OFF and then activate HLDA, thus entering the bus hold acknowledge condition. The local bus will remain granted to the requesting master until HOLD becomes inactive which results in the 80286 deactivating HLDA and regaining control of the local bus. This terminates the bus hold acknowledge condition. HOLD may be asynchronous to the system clock. These signals are active HIGH.                                                                                                                                                                        |

| INTR           |      | INTERRUPT REQUEST requests the 80286 to suspend its current program execution and service a pending external request. Interrupt requests are masked whenever the interrupt enable bit in the flag word is cleared. When the 80286 responds to an interrupt request, it performs two interrupt acknowledge bus cycles to read an 8-bit interrupt vector that identifies the source of the interrupt. To assure program interruption, INTR must remain active until the first interrupt acknowledge cycle is completed. INTR is sampled at the beginning of each processor cycle and must be active HIGH at least two processor cycles before the current instruction ends in order to interrupt before the next instruction. INTR is level sensitive, active HIGH, and may be asynchronous to the system clock. |

| NMI            | 1    | NON-MASKABLE INTERRUPT REQUEST interrupts the 80286 with an internally supplied vector value of 2. No interrupt acknowledge cycles are performed. The interrupt enable bit in the 80286 flag word does not affect this input. The NMI input is active HIGH, may be asynchronous to the system clock, and is edge triggered after internal synchronization. For proper recognition, the input must have been previously LOW for at least four system clock cycles and remain HIGH for at least four system clock cycles.                                                                                                                                                                                                                                                                                        |

| PEREQ<br>PEACK | 0    | PROCESSOR EXTENSION OPERAND REQUEST AND ACKNOWLEDGE extend the memory management and protection capabilities of the 80286 to processor extensions. The PEREQ input requests the 80286 to perform a data operand transfer for a processor extension. The PEACK output signals the processor extension when the requested operand is being transferred. PEREQ is active HIGH and floats to 3-state OFF during bus hold acknowledge. PEACK may be asynchronous to the system clock. PEACK is active LOW.                                                                                                                                                                                                                                                                                                          |

| BUSY<br>ERROR  | 1    | PROCESSOR EXTENSION BUSY AND ERROR indicate the operating condition of a processor extension to the 80286. An active BUSY input stops 80286 program execution on WAIT and some ESC instructions until BUSY becomes inactive (HIGH). The 80286 may be interrupted while waiting for BUSY to become inactive. An active ERROR input causes the 80286 to perform a processor extension interrupt when executing WAIT or some ESC instructions. These inputs are active LOW and may be asynchronous to the system clock. These inputs have internal pull-up resistors.                                                                                                                                                                                                                                             |

Table 1. Pin Description (Continued)

| Symbol          | Type |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

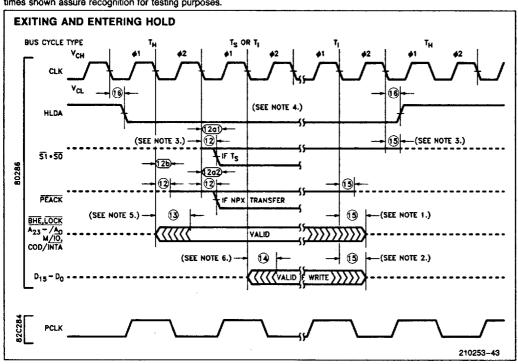

| RESET           | ı    | SYSTEM RESET clears the internal logic of the 80286 and is active HIGH. The 80286 may be reinitialized at any time with a LOW to HIGH transition or RESET which remains active for more than 16 system clock cycles. During RESET active, the output pins of the 80286 enter the state shown below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| i               |      | 8028                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80286 Pin State During Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                 | ,    | Pin Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Names                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                 |      | 1 (HIGH)<br>0 (LOW)<br>3-state OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SÕ, ST, PEACK, A23-A0, BHE, LOCK<br>M/IŌ, COD/INTA, HLDA (Note 1)<br>D <sub>15</sub> -D <sub>0</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                 |      | The HIGH to LOW transition clock. Approximately 38 CLK required by the 80286 for interest code from the power-or A LOW to HIGH transition of end a processor cycle at the clock. The LOW to HIGH transystem clock; however, in this of the processor clock will oc Synchronous LOW to HIGH transystems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ns after a HIGH to LOW transition on RESET.  of RESET must be synchronous to the system it cycles from the trailing edge of RESET are email initialization before the first bus cycle, to in execution address, occurs.  RESET synchronous to the system clock will second HIGH to LOW transition of the system issition of RESET may be asynchronous to the s case it cannot be predetermined which phase cour during the next system clock period.  ransitions of RESET are required only for it clock must be phase synchronous to another |  |

| V <sub>SS</sub> | ı    | SYSTEM GROUND: 0 Volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Vœ              | 1    | SYSTEM POWER: +5 Volt F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| CAP             |      | SUBSTRATE FILTER CAPACITOR: a 0.047 μF ± 20% 12V capacitor must be connected between this pin and ground. This capacitor filters the output of the internal substrate bias generator. A maximum DC leakage current of 1 μA is allowed through the capacitor. A maximum DC leakage current of 1 μA is allowed through the capacitor. For correct operation of the 80286, the substrate bias generator must charge this capacitor to its operating voltage. The capacitor chargeup time is 5 milliseconds (max.) after V <sub>CC</sub> and CLK reach their specified AC and DC parameters. RESET may be applied to prevent spurious activity by the CPU during this time. After this time, the 80286 processor clock can be synchronized to another clock by pulsing RESET LOW synchronous to the system clock. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

NOTE:

1. HLDA is only Low if HOLD is inactive (Low).

intal

# **FUNCTIONAL DESCRIPTION**

#### Introduction

The 80286 is an advanced, high-performance microprocessor with specially optimized capabilities for multiple user and multi-tasking systems. Depending on the application, a 12.5 MHz 80286's performance is up to six times faster than the standard 5 MHz 8086's, while providing complete upward software compatibility with Intel's 8086, 88, and 186 family of CPU's.

The 80286 operates in two modes: 8086 real address mode and protected virtual address mode. Both modes execute a superset of the 8086 and 88 instruction set.

In 8086 real address mode programs use real addresses with up to one megabyte of address space. Programs use virtual addresses in protected virtual address mode, also called protected mode. In protected mode, the 80286 CPU automatically maps 1 gigabyte of virtual addresses per task into a 16 megabyte real address space. This mode also provides memory protection to isolate the operating system and ensure privacy of each tasks' programs and data. Both modes provide the same base instruction set, registers, and addressing modes.

The following Functional Description describes first, the base 80286 architecture common to both modes, second, 8086 real address mode, and third, protected mode.

# **80286 BASE ARCHITECTURE**

The 8086, 88, 186, and 286 CPU family all contain the same basic set of registers, instructions, and addressing modes. The 80286 processor is upward compatible with the 8086, 8088, and 80186 CPU's.

### **Register Set**

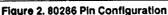

The 80286 base architecture has fifteen registers as shown in Figure 3. These registers are grouped into the following four categories:

General Registers: Eight 16-bit general purpose registers used to contain arithmetic and logical operands. Four of these (AX, BX, CX, and DX) can be used either in their entirety as 16-bit words or split into pairs of separate 8-bit registers.

Segment Registers: Four 16-bit special purpose registers select, at any given time, the segments of memory that are immediately addressable for code, stack, and data. (For usage, refer to Memory Organization.)

Base and Index Registers: Four of the general purpose registers may also be used to determine offset addresses of operands in memory. These registers may contain base addresses or indexes to particular locations within a segment. The addressing mode determines the specific registers used for operand address calculations.

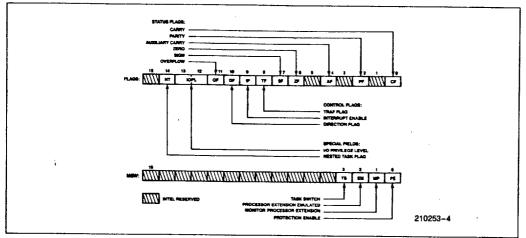

Status and Control Registers: The 3 16-bit special purpose registers in figure 3A record or control certain aspects of the 80286 processor state including the Instruction Pointer, which contains the offset address of the next sequential instruction to be executed.

Figure 3. Register Set

Figure 3a. Status and Control Register Bit Functions

# Flags Word Description

The Flags word (Flags) records specific characteristics of the result of logical and arithmetic instructions (bits 0, 2, 4, 6, 7, and 11) and controls the operation of the 80286 within a given operating mode (bits 8 and 9). Flags is a 16-bit register. The function of the flag bits is given in Table 2.

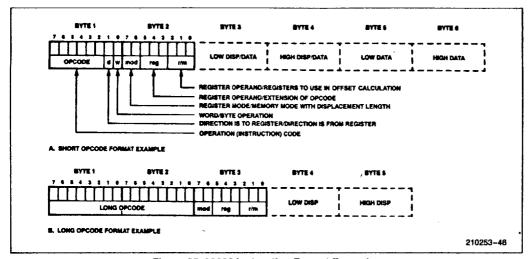

# **Instruction Set**

The instruction set is divided into seven categories: data transfer, arithmetic, shift/rotate/logical, string manipulation, control transfer, high level instructions, and processor control. These categories are summarized in Figure 4.

An 80286 instruction can reference zero, one, or two operands; where an operand resides in a register, in the instruction itself, or in memory. Zero-operand instructions (e.g. NOP and HLT) are usually one byte long. One-operand instructions (e.g. INC and DEC) are usually two bytes long but some are encoded in only one byte. One-operand instructions may reference a register or memory location. Two-operand instructions permit the following six types of instruction operations:

- -Register to Register

- -Memory to Register

- -Immediate to Register

- -Memory to Memory

- -Register to Memory

- -Immediate to Memory

| Table 2. Flags Word Bit Functions |      |                                                                                                                                                                              |  |

|-----------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit<br>Position                   | Name | Function                                                                                                                                                                     |  |

| 0                                 | CF   | Carry Flag—Set on high-order bit carry or borrow; cleared otherwise                                                                                                          |  |

| 2                                 | PF   | Parity Flag—Set if low-order 8 bits of result contain an even number of 1-bits; cleared otherwise                                                                            |  |

| 4                                 | AF . | Set on carry from or borrow to the<br>low order four bits of AL; cleared<br>otherwise                                                                                        |  |

| 6                                 | ZF   | Zero Flag—Set if result is zero;<br>cleared otherwise                                                                                                                        |  |

| 7                                 | SF   | Sign Flag—Set equal to high-order bit of result (0 if positive, 1 if negative)                                                                                               |  |

| 11                                | OF   | Overflow Flag—Set if result is a too-<br>large positive number or a too-small<br>negative number (excluding sign-bit)<br>to fit in destination operand; cleared<br>otherwise |  |

| 8                                 | TF   | Single Step Flag—Once set, a sin-<br>gle step interrupt occurs after the<br>next instruction executes. TF is<br>cleared by the single step interrupt.                        |  |

| 9                                 | IF   | Interrupt-enable Flag—When set,<br>maskable interrupts will cause the<br>CPU to transfer control to an inter-<br>rupt vector specified location.                             |  |

| 10                                | DF   | Direction Flag—Causes string instructions to auto decrement the appropriate index registers when set. Clearing DF causes auto increment.                                     |  |

Two-operand instructions (e.g. MOV and ADD) are usually three to six bytes long. Memory to memory operations are provided by a special class of string instructions requiring one to three bytes. For detailed instruction formats and encodings refer to the instruction set summary at the end of this document.

For detailed operation and usage of each instruction, see Appendix of 80286 Programmer's Reference Manual (Order No. 210498)

| GENERAL PURPOSE |                              |  |  |

|-----------------|------------------------------|--|--|

| MOV             | Move byte or word            |  |  |

| PUSH            | Push word onto stack         |  |  |

| POP             | Pop word off stack           |  |  |

| PUSHA           | Push all registers on stack  |  |  |

| POPA            | Pop all registers from stack |  |  |

| XCHG            | Exchange byte or word        |  |  |

| XLAT            | Translate byte               |  |  |

|                 | INPUT/OUTPUT                 |  |  |

| IN              | Input byte or word           |  |  |

| OUT             | Output byte or word          |  |  |

|                 | ADDRESS OBJECT               |  |  |

| LEA             | Load effective address       |  |  |

| LDS             | Load pointer using DS        |  |  |

| LES             | Load pointer using ES        |  |  |

| FLAG TRANSFER   |                              |  |  |

| LAHF            | Load AH register from flags  |  |  |

| SAHF            | Store AH register in flags   |  |  |

| PUSHF           | Push flags onto stack        |  |  |

| POPF            | Pop flags off stack          |  |  |

Figure 4a. Data Transfer Instructions

| MOVS        | Move byte or word string        |

|-------------|---------------------------------|

| INS         | Input bytes or word string      |

| OUTS        | Output bytes or word string     |

| CMPS        | Compare byte or word string     |

| SCAS        | Scan byte or word string        |

| LODS        | Load byte or word string        |

| STOS        | Store byte or word string       |

| REP         | Repeat                          |

| REPE/REPZ   | Repeat while equal/zero         |

| REPNE/REPNZ | Repeat while not equal/not zero |

Figure 4c. String Instructions

| ADDITION       |                                   |  |  |

|----------------|-----------------------------------|--|--|

| ADD            | Add byte or word                  |  |  |

| ADC            | Add byte or word with carry       |  |  |

| INC            | Increment byte or word by 1       |  |  |

| AAA            | ASCII adjust for addition         |  |  |

| DAA            | Decimal adjust for addition       |  |  |

|                | SUBTRACTION                       |  |  |

| SUB            | Subtract byte or word             |  |  |

| SBB            | Subtract byte or word with borrow |  |  |

| DEC            | Decrement byte or word by 1       |  |  |

| NEG            | Negate byte or word               |  |  |

| CMP            | Compare byte or word              |  |  |

| AAS            | ASCII adjust for subtraction      |  |  |

| DAS            | Decimal adjust for subtraction    |  |  |

| MULTIPLICATION |                                   |  |  |

| MUL            | Multiple byte or word unsigned    |  |  |

| IMUL           | Integer multiply byte or word     |  |  |

| AAM            | ASCII adjust for multiply         |  |  |

|                | DIVISION                          |  |  |

| . DIA          | Divide byte or word unsigned      |  |  |

| IDIV           | Integer divide byte or word       |  |  |

| AAD            | ASCII adjust for division         |  |  |

| CBW            | Convert byte to word              |  |  |

| CWD            | Convert word to doubleword        |  |  |

|                |                                   |  |  |

Figure 4b. Arithmetic Instructions

| LOGICALS |                                            |  |

|----------|--------------------------------------------|--|

| NOT      | "Not" byte or word                         |  |

| AND      | "And" byte or word                         |  |

| OR       | "Inclusive or" byte or word                |  |

| XOR      | "Exclusive or" byte or word                |  |

| TEST     | "Test" byte or word                        |  |

| SHIFTS   |                                            |  |

| SHL/SAL  | Shift logical/arithmetic left byte or word |  |

| SHR      | Shift logical right byte or word           |  |

| SAR      | Shift arithmetic right byte or word        |  |

|          | ROTATES                                    |  |

| ROL      | Rotate left byte or word                   |  |

| ROR      | Rotate right byte or word                  |  |

| RCL      | Rotate through carry left byte or word     |  |

| RCR      | Rotate through carry right byte or word    |  |

Figure 4d. Shift/Rotate Logical Instructions

| C       | ONDITIONAL TRANSFERS               | UNCONDITI     | ONAL TRANSFERS             |

|---------|------------------------------------|---------------|----------------------------|

| JA/JNBE | Jump if above/not below nor equal  | CALL          | Call procedure             |

| JAE/JNB | Jump if above or equal/not below   | RET           | Return from procedure      |

| JB/JNAE | Jump if below/not above nor equal  | JMP           | Jump                       |

| JBE/JNA | Jump if below or equal/not above   |               |                            |

| JC      | Jump if carry                      | ITERATI       | ON CONTROLS                |

| JE/JZ   | Jump if equal/zero                 | ***           |                            |

| JG/JNLE | Jump if greater/not less nor equal | LOOP          | Loop                       |

| JGE/JNL | Jump if greater or equal/not less  | LOOPE/LOOPZ   | Loop if equal/zero         |

| JL/JNGE | Jump if less/not greater nor equal | LOOPNE/LOOPNZ | Loop if not equal/not zero |

| JLE/JNG | Jump if less or equal/not greater  | JCXZ          | Jump if register CX = 0    |

| JNC     | Jump if not carry                  | i             |                            |

| JNE/JNZ | Jump if not equal/not zero         | INT           | ERRUPTS                    |

| JNO     | Jump if not overflow               |               |                            |

| JNP/JPO | Jump if not parity/parity odd      | INT           | Interrupt                  |

| JNS     | Jump if not sign                   | INTO          | Interrupt if overflow      |

| 70      | Jump if overflow                   | IRET          | Interrupt return           |

| JP/JPE  | Jump if parity/parity even         |               | ,                          |

| JS      | Jump if sign                       |               |                            |

Figure 4e. Program Transfer Instructions

| FLAG OPERATIONS                  |  |  |  |  |

|----------------------------------|--|--|--|--|

| Set carry flag                   |  |  |  |  |

| Clear carry flag                 |  |  |  |  |

| Complement carry flag            |  |  |  |  |

| Set direction flag               |  |  |  |  |

| Clear direction flag             |  |  |  |  |

| Set interrupt enable flag        |  |  |  |  |

| Clear interrupt enable flag      |  |  |  |  |

| EXTERNAL SYNCHRONIZATION         |  |  |  |  |

| Halt until interrupt or reset    |  |  |  |  |

| Wait for BUSY not active         |  |  |  |  |

| Escape to extension processor    |  |  |  |  |

| Lock bus during next instruction |  |  |  |  |

| NO OPERATION                     |  |  |  |  |

| No operation                     |  |  |  |  |

| EXECUTION ENVIRONMENT CONTROL    |  |  |  |  |

| Load machine status word         |  |  |  |  |

| Store machine status word        |  |  |  |  |

|                                  |  |  |  |  |

Figure 4f. Processor Control Instructions

| ENTER | Format stack for procedure entry        |

|-------|-----------------------------------------|

| LEAVE | Restore stack for procedure exit        |

| BOUND | Detects values outside prescribed range |

Figure 4g. High Level Instructions

# **Memory Organization**

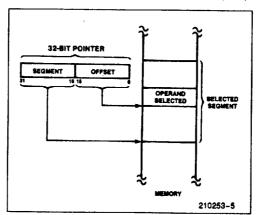

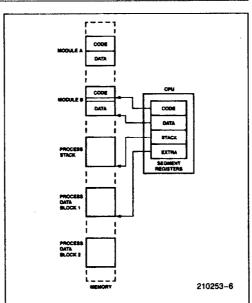

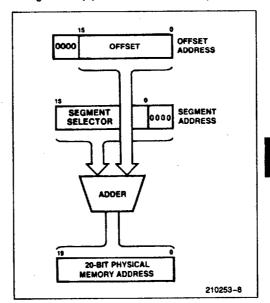

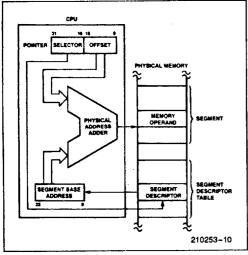

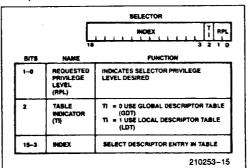

Memory is organized as sets of variable length segments. Each segment is a linear contiguous sequence of up to 64K (2<sup>16</sup>) 8-bit bytes. Memory is addressed using a two component address (a pointer) that consists of a 16-bit segment selector, and a 16-bit offset. The segment selector indicates the desired segment in memory. The offset component indicates the desired byte address within the segment.

Figure 5. Two Component Address

**Table 3. Segment Register Selection Rules**

| Memory<br>Reference Needed | Segment Register<br>Used | Implicit Segment<br>Selection Rule                                                |

|----------------------------|--------------------------|-----------------------------------------------------------------------------------|

| Instructions               | Code (CS)                | Automatic with instruction prefetch                                               |

| Stack                      | Stack (SS)               | All stack pushes and pops. Any memory reference which uses BP as a base register. |

| Local Data                 | Data (DS)                | All data references except when relative to stack or string destination           |

| External (Global) Data     | Extra (ES)               | Alternate data segment and destination of string operation                        |

All instructions that address operands in memory must specify the segment and the offset. For speed and compact instruction encoding, segment selectors are usually stored in the high speed segment registers. An instruction need specify only the desired segment register and an offset in order to address a memory operand.

Most instructions need not explicitly specify which segment register is used. The correct segment register is automatically chosen according to the rules of Table 3. These rules follow the way programs are written (see Figure 6) as independent modules that require areas for code and data, a stack, and access to external data areas.

Special segment override instruction prefixes allow the implicit segment register selection rules to be overridden for special cases. The stack, data, and extra segments may coincide for simple programs. To access operands not residing in one of the four immediately available segments, a full 32-bit pointer or a new segment selector must be loaded.

# **Addressing Modes**

The 80286 provides a total of eight addressing modes for instructions to specify operands. Two addressing modes are provided for instructions that operate on register or immediate operands:

Register Operand Mode: The operand is located in one of the 8 or 16-bit general registers.

Immediate Operand Mode: The operand is included in the instruction.

Six modes are provided to specify the location of an operand in a memory segment. A memory operand address consists of two 16-bit components: segment selector and offset. The segment selector is supplied by a segment register either implicitly chosen by the addressing mode or explicitly chosen by a segment override prefix. The offset is calculated by summing any combination of the following three address elements:

the displacement (an 8 or 16-bit immediate value contained in the instruction)

the base (contents of either the BX or BP base

the index (contents of either the SI or DI index registers)

Any carry out from the 16-bit addition is ignored. Eight-bit displacements are sign extended to 16-bit values.

Combinations of these three address elements define the six memory addressing modes, described below.

**Direct Mode:** The operand's offset is contained in the instruction as an 8 or 16-bit displacement element

Register Indirect Mode: The operand's offset is in one of the registers SI, DI, BX, or BP.

**Based Mode:** The operand's offset is the sum of an 8 or 16-bit displacement and the contents of a base register (BX or BP).

**Indexed Mode:** The operand's offset is the sum of an 8 or 16-bit displacement and the contents of an index register (SI or DI).

Based Indexed Mode: The operand's offset is the sum of the contents of a base register and an index register.

Based Indexed Mode with Displacement: The operand's offset is the sum of a base register's contents, an index register's contents, and an 8 or 16-bit displacement.

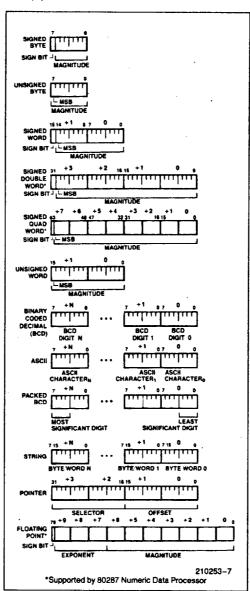

# **Data Types**

The 80286 directly supports the following data types:

Integer:

A signed binary numeric value contained in an 8-bit byte or a 16-bit word. All operations assume a 2's complement representation. Signed 32 and 64-bit integers are supported using the Numeric Data Processor, the 80287.

Ordinal:

An unsigned binary numeric value contained in an 8-bit byte or 16-bit

word.

Pointer:

A 32-bit quantity, composed of a segment selector component and an offset component. Each component is a 16-bit word.

String:

A contiguous sequence of bytes or words. A string may contain from 1

byte to 64K bytes.

ASCII:

A byte representation of alphanumeric and control characters using the ASCII standard of character rep-

resentation.

BCD:

A byte (unpacked) representation of

the decimal digits 0-9.

Packed BCD:

A byte (packed) representation of two decimal digits 0-9 storing one digit in each nibble of the byte.

Floating Point: A signed 32, 64, or 80-bit real num-

ber representation. (Floating point operands are supported using the 80287 Numeric Processor).

Figure 7 graphically represents the data types supported by the 80286.

# I/O Space

The I/O space consists of 64K 8-bit or 32K 16-bit ports. I/O instructions address the I/O space with

# intel.

either an 8-bit port address, specified in the instruction, or a 16-bit port address in the DX register. 8-bit port addresses are zero extended such that A<sub>15</sub>-A<sub>8</sub> are LOW. I/O port addresses 00F8(H) through 00FF(H) are reserved.

Figure 7. 80286 Supported Data Types

# intel.

80286

**Table 4. Interrupt Vector Assignments**

| Function                                    | Interrupt<br>Number | Related<br>Instructions | Does Return Address Point to Instruction Causing Exception? |

|---------------------------------------------|---------------------|-------------------------|-------------------------------------------------------------|

| Divide error exception                      | 0                   | DIV, IDIV               | Yes                                                         |

| Single step interrupt                       | 1                   | All                     |                                                             |

| NMI interrupt                               | 2                   | INT 2 or NMI pin        |                                                             |

| Breakpoint interrupt                        | 3                   | INT 3                   |                                                             |

| INTO detected overflow exception            | 4                   | INTO                    | No                                                          |

| BOUND range exceeded exception              | 5                   | BOUND                   | Yes                                                         |

| Invalid opcode exception                    | 6                   | Any undefined opcode    | Yes                                                         |

| Processor extension not available exception | 7                   | ESC or WAIT             | Yes                                                         |

| intel reserved-do not use                   | 8-15                |                         |                                                             |

| Processor extension error interrupt         | 16                  | ESC or WAIT             |                                                             |

| Intel reserved-do not use                   | 17-31               |                         |                                                             |

| User defined                                | 32-255              |                         |                                                             |

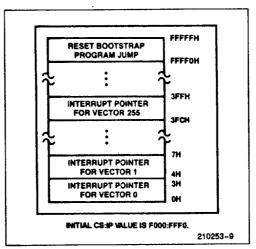

# Interrupts

An interrupt transfers execution to a new program location. The old program address (CS:IP) and machine state (Flags) are saved on the stack to allow resumption of the interrupted program. Interrupts fall into three classes: hardware initiated, INT instructions, and instruction exceptions. Hardware initiated interrupts occur in response to an external input and are classified as non-maskable or maskable. Programs may cause an interrupt with an INT instruction. Instruction exceptions occur when an unusual condition, which prevents further instruction processing, is detected while attempting to execute an instruction. The return address from an exception will always point at the instruction causing the exception and include any leading instruction prefixes.

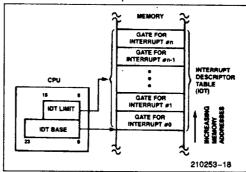

A table containing up to 256 pointers defines the proper interrupt service routine for each interrupt. Interrupts 0–31, some of which are used for instruction exceptions, are reserved. For each interrupt, an 8-bit vector must be supplied to the 80286 which identifies the appropriate table entry. Exceptions supply the interrupt vector internally. INT instructions contain or imply the vector and allow access to all 256 interrupts. Maskable hardware initiated interrupts supply the 8-bit vector to the CPU during an interrupt acknowledge bus sequence. Non-maskable hardware interrupts use a predefined internally supplied vector.

# MASKABLE INTERRUPT (INTR)

The 80286 provides a maskable hardware interrupt request pin, INTR. Software enables this input by

setting the interrupt flag bit (IF) in the flag word. All 224 user-defined interrupt sources can share this input, yet they can retain separate interrupt handlers. An 8-bit vector read by the CPU during the interrupt acknowledge sequence (discussed in System Interface section) identifies the source of the interrupt.

Further maskable interrupts are disabled while servicing an interrupt by resetting the IF bit as part of the response to an interrupt or exception. The saved flag word will reflect the enable status of the processor prior to the interrupt. Until the flag word is restored to the flag register, the interrupt flag will be zero unless specifically set. The interrupt return instruction includes restoring the flag word, thereby restoring the original status of IF.

# NON-MASKABLE INTERRUPT REQUEST (NMI)

A non-maskable interrupt input (NMI) is also provided. NMI has higher priority than INTR. A typical use of NMI would be to activate a power failure routine. The activation of this input causes an interrupt with an internally supplied vector value of 2. No external interrupt acknowledge sequence is performed.

While executing the NMI servicing procedure, the 80286 will service neither further NMI requests, INTR requests, nor the processor extension segment overrun interrupt until an interrupt return (IRET) instruction is executed or the CPU is reset. If NMI occurs while currently servicing an NMI, its presence will be saved for servicing after executing the first IRET instruction. IF is cleared at the beginning of an NMI interrupt to inhibit INTR interrupts.

# int<sub>el</sub>,

#### SINGLE STEP INTERRUPT

The 80286 has an internal interrupt that allows programs to execute one instruction at a time. It is called the single step interrupt and is controlled by the single step flag bit (TF) in the flag word. Once this bit is set, an internal single step interrupt will occur after the next instruction has been executed. The interrupt clears the TF bit and uses an internally supplied vector of 1. The IRET instruction is used to set the TF bit and transfer control to the next instruction to be single stepped.

# **Interrupt Priorities**

When simultaneous interrupt requests occur, they are processed in a fixed order as shown in Table 5. Interrupt processing involves saving the flags, return address, and setting CS:IP to point at the first instruction of the interrupt handler. If other interrupts remain enabled they are processed before the first instruction of the current interrupt handler is executed. The last interrupt processed is therefore the first one serviced.

**Table 5. Interrupt Processing Order**

| Order | Interrupt                           |

|-------|-------------------------------------|

| 1     | Instruction exception               |

| 2     | Single step                         |

| 3     | NMI                                 |

| 4     | Processor extension segment overrun |

| 5     | INTR                                |

| 6     | INT instruction                     |

# **Initialization and Processor Reset**

Processor initialization or start up is accomplished by driving the RESET input pin HIGH. RESET forces the 80286 to terminate all execution and local bus activity. No instruction or bus activity will occur as long as RESET is active. After RESET becomes inactive and an internal processing interval elapses, the 80286 begins execution in real address mode with the instruction at physical location FFFFF0(H). RESET also sets some registers to predefined values as shown in Table 6.

Table 6. 80286 Initial Register State after RESET

| Flag word           | 0002(H) |

|---------------------|---------|

| Machine Status Word | FFF0(H) |

| Instruction pointer | FFFO(H) |

| Code segment        | F000(H) |

| Data segment        | 0000(H) |

| Extra segment       | 0000(H) |

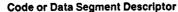

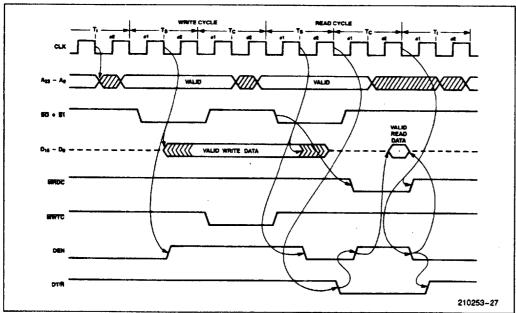

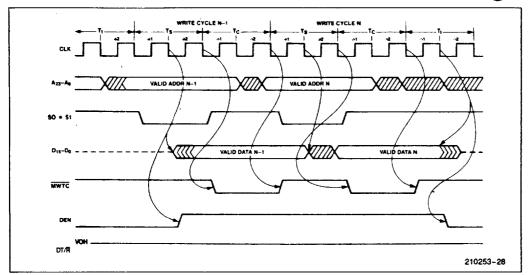

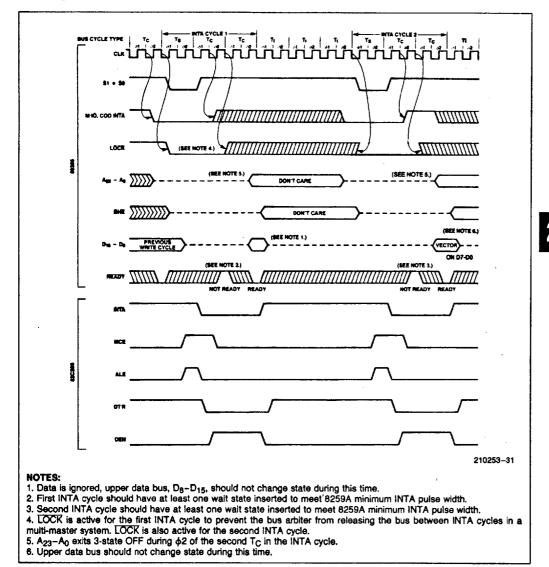

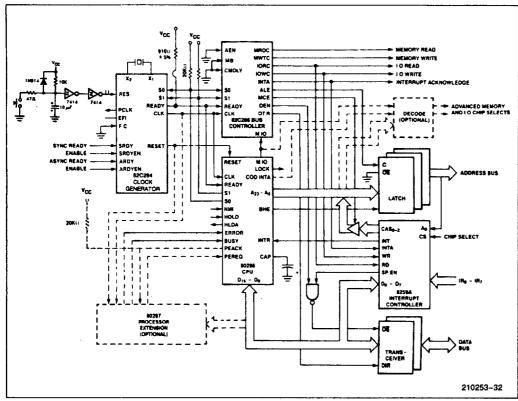

| Stack segment       | 0000(H) |