#### TOSHIBA

# TMP88CS43F data sheet (tentativeness version)

2002-2-25 REV0.2

Note 1) This product is underdevelopment, and there is the case that specification / a function is changed without a notice.

Note 2) This data sheet is tentativeness version, and there is a case changed in future. Toshiba Corporation disclaims all responsibilities for problems that may result from this data sheet. No part of this publication may be reproduced or distributed without the prior written permission of Toshiba Corporation.

# Revisions in Data Books

| S |

|---|

| ≂ |

| ≒ |

| ⊏ |

| ኤ |

| ⋍ |

| Function            | Dane | NON                                                             | Notes                                                                             |

|---------------------|------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------|

|                     | ט ס  | Before revision                                                 | Revised                                                                           |

| Interrupt Control   | 52d  | Before you set EE, be sure to clear IMF (to disable interrupt). | Before you change each enable flag (EF) and/or each interrupt latch (IL), be sure |

| (Interrupt latches, |      |                                                                 | to clear the interrupt master enable flag (IMF) to "0" (to disable interrupts).   |

| interrupt enable    |      |                                                                 | a. After a DI instruction is executed                                             |

|                     |      |                                                                 | b. When an interrupt is accepted, IMF is automatically cleared to "0".            |

|                     |      |                                                                 | However, to enable nested interrupts, change EF and/or IL before setting          |

|                     |      |                                                                 | וואון נס ו (נס פווסמופ ווויפווחלופ).                                              |

| _                   |      |                                                                 | If the individual enable flags (EF) and interrupt latches (IL) are set under      |

|                     |      |                                                                 | conditions other than the above, the proper operation cannot be quaranteed        |

| Watchdog Timer |      |                                                     |                                                                                                                         |

|----------------|------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Finction       | o co | No                                                  | Notes                                                                                                                   |

|                | ביי  | Before revision                                     | Revised                                                                                                                 |

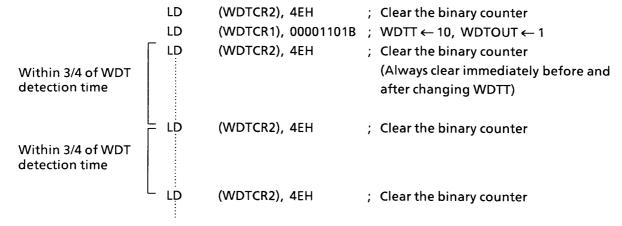

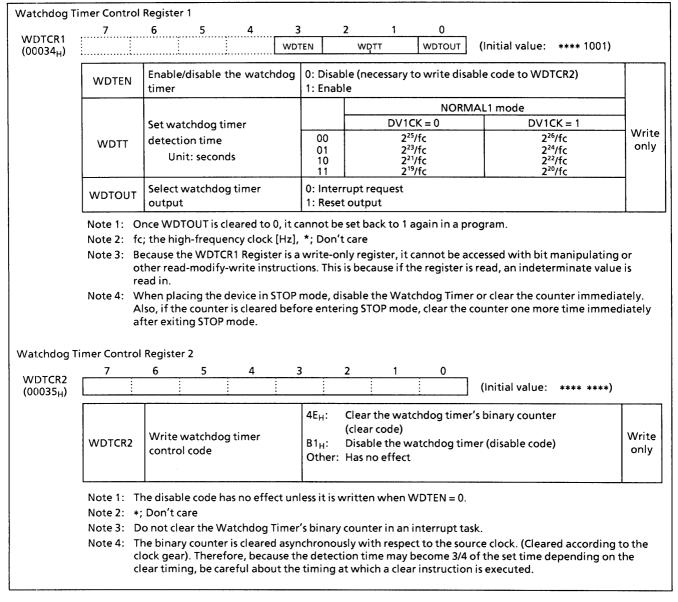

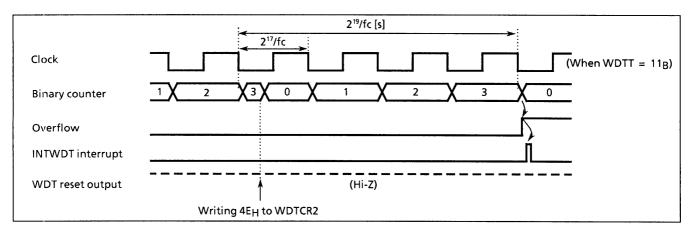

| Watchdog Timer | PS4  | (A note on disabiling the watchdog timer is added.) | Just right before disabling the watchdog timer, disable the acceptance of interrupts (DI) and clear the watchdog timer. |

|                |      |                                                     | If the watchdog timer is disabled under conditions other than the above, the proper operation cannot be guaranteed.     |

|                |      |                                                     | Example : DI Disables interrupt acceptance.                                                                             |

|                |      |                                                     | LD (WDTCR2),4EH Clears the watchdog timer.                                                                              |

|                |      |                                                     | LDW (WDTCR1),B100H Disables the watchdog timer.                                                                         |

|                |      |                                                     | El Enables international                                                                                                |

# I/O Ports

|          | Revised         | When external momory is used, the P10 pin cannot be used as an external | international (INTA) or so 1/O cost se C1 V is outself from this sin |

|----------|-----------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|

| Notes    | Before revision | (A note on the P10 pin is added.)                                       | netui                                                                |

| O O O    | )<br>           | 174                                                                     |                                                                      |

| Function |                 | Port P1                                                                 | _                                                                    |

# AD Converter

| Frinction             | o Ce C    | Notes                                         | les                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|-----------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | 2000<br>- | Before revision                               | Revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AD Converter 758      | 7958      | (A note on the AD control register is added.) | When STOP or SLOW mode is activated the AD control registers 1 (ADCCR1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (AD converter control | )         |                                               | and 2 (ADCCR2) are all initialized. After NORMAL modes is resumed, set both the AD control paristers 1 and 2 (ADCCP1, ADCCP2) and department of the ADCCP2 and the ADCCP2 a |

| ADCCR1                |           |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ADCCR2)               |           |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

2001-08-30

# visions in Data Books

it Timer/Counter (TC1)

| (LOL) COUNCIL N                           | (101)  |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figorion                                  | o c    | Notes                                                                                                                                                                                                                                                                                | SE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                           | υ<br>- | Before revision                                                                                                                                                                                                                                                                      | Revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

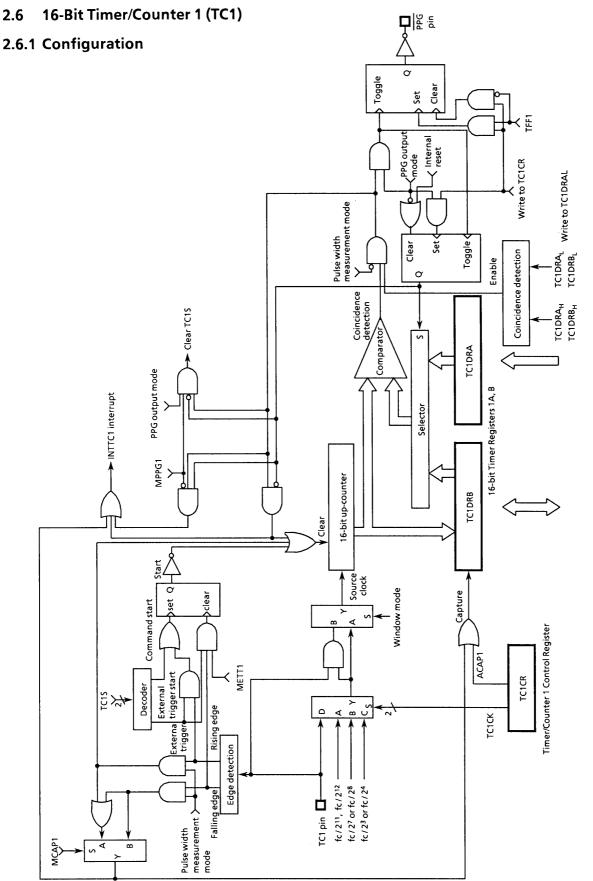

| it Timer/Counter 1 ing to the timer ters) | P58    | Note on writing to the timer registers (TC1DRA,TC1DRB) in the figure "Timer Registers and TC1 Control Register"                                                                                                                                                                      | Because the register configuration has been changed, this note is revised as shown below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                           |        | Note: Writing to the timer registers is not executed until the next falling edge of the source clock.                                                                                                                                                                                | Note: When writing to the timer registers, write first to the lower byte and then to the upper byte continuously. It is recommended that a 16-bit access instruction be used for write.                                                                                                                                                                                                                                                                                                                                                                          |

|                                           |        |                                                                                                                                                                                                                                                                                      | The timer registers are configured as 2-stage shift registers, and the timer register value becomes valid at the next rising edge of the source clock affer data is written to the upper byte (TC1DRA, TC1DRB,). Note that writing only to the lower byte (TC1DRA, TC1DRB,) does not make the register value valid.                                                                                                                                                                                                                                              |

| it Timer/Counter 1<br>3 output mode)      | 765    | "Programmable Pulse Generate (PPG) output mode"                                                                                                                                                                                                                                      | Because INTTC1 is generated by single output as well as by continuous output, this explanation is revised to include operation in the timer stop state.                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                           |        | A match between the counter value and the value set in TC1DRB inverts timer F- F1. Continuous output (MPPG=0) generates INTTC1. The next match between the counter value and the value set in TC1DRB inverts timer F-F1 again and clears TC1. At the same time, INTTC1 is generated. | A match between the counter value and the value set in TC1DRB inverts timer E. Land at the same time generates. INTTC1. The next match between the counter value and the value set in TC1DRA inverts timer F.F.1 again. Clear the counter generates. INTTC1. In the case of single output (MPPG=I). TC1CS is automatically cleared to "O" and the timer stops counting. Writing "O" to TC1CS, while the timer is counting. Southing stops timer operation and clears the counter. In this case PPG output keeps the same level just before the timer is stopped. |

|                                           | 765    | *Programmable Pulse Generate (PPG) output mode": F-F1 timer                                                                                                                                                                                                                          | An additional note on setting timer F-F1 by using TFF1 is included.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                           |        | Since the timer F-F1 value can be set in TFF1 (Bit7 in TC1CR), either positive or negative AND pulses can be output.                                                                                                                                                                 | Timer F-F1 is cleard to "0" during reset. Since the timer F-F1 value can be set in TFF1 (bit? in TC1CR), either positive or negative pulse can be output.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                           |        |                                                                                                                                                                                                                                                                                      | Note: Do not change timer F-F1 by TFF1 white TC1 is operating. The timer F-F1 value can be set or cleared only by initial setting. Setting or clearing the timer F-F1 value, while TC1 is counting or after TC1 stops counting, inverts the output. After TC1 stops, it is necessary to initialize timer F-F1 to change PG output to a desired level. To initialize F-F1, change to the timer mode once (the timer mode need not be started) and then set to the PPG output mode also set TFF1 again.                                                            |

|                                           | P6.5   | (A note on the initialization of timer F-F1 in the PPG output mode is added.)                                                                                                                                                                                                        | Note: To restart the PPG output mode, it is necessary to initialize timer F-F1. To initialize timer F-F1, change to the timer mode once (the timer mode need not be started), then set to the PPG output mode, and also set TFF1 again.                                                                                                                                                                                                                                                                                                                          |

|                                           | 594    | The section on "Programmable Pulse Generate (PPG) output mode" does not include a note on writing to the timer registers.                                                                                                                                                            | The following note on writing to the timer registers in the PPG output mode is added.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                           |        |                                                                                                                                                                                                                                                                                      | Note: The timer register change should be done while TC1 is disabled (TC1S=00). When changing the timer register value while TC1 is counting, set a sufficiently larger value than the count value of the up-counter.                                                                                                                                                                                                                                                                                                                                            |

|                                           |        |                                                                                                                                                                                                                                                                                      | If a smaller value than the count value of the up-counter is set to the timer register, comparison is not performed and it makes the up counter overflow.                                                                                                                                                                                                                                                                                                                                                                                                        |

2001-08-30

# Revisions in Data Books

| : |  |  |  |

|---|--|--|--|

| ) |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

| : |  |  |  |

| ) |  |  |  |

| : |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

| Finction                                                    |             | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                             | p<br>D<br>D | Before revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16-bit Timer/Counter 1<br>(Pulse width<br>measurement mode) | P63         | The section on "Pulse width measurement mode" does not contain a note on reading the capture value from the timer register B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A note on reading the capture value is added.  Note: The capture value of the timer register B has to be read by a 16-bit access instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                             | 783         | Pulse width measurement mode": One-edge capture  TC1 starts counting triggered by the rising (falling) edge of input to TC1 pin (set start by external trigger in TC1CR). The source clock is the internal clock. At the next falling (rising) edge, the counter value is loaded to TC1DRB and an interrupt is generated. If one-edge capture is set, the counter is cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (1) A note on one-edge capture is added.  When start by external trigger is set in TC1CR, the rising (falling) edge of the TC1 pin input triggers TC1 to start counting. (For the source clock, select the internal clock.) At the next falling (rising) edge, the counter value is loaded to TC1DRB and an INTTC1 request is generated.  In the one-edge capture operation, the capture values from the 2nd capture onward Increase by one compared with the capture value immediately after count start (See the finure hollow).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                             | P63         | Explanation of the revised figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | An INTTC1 request is generated at both the rising and falling edges of TC1 input also in the one-edge capture operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                             | P63         | Pulse width measurement mode": Both-edge capture If both-edge capture is set, the counter continues counting; at the next rising (falling) edge, the counter value is loaded to TC1DRB. If a capture value at a falling (fising) edge. is required, data in TC1DRB must be read before a rising (falling), edge is is detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (2) An explanation about both-edge capture is revised, and a note on the pulse width measurement mode is added.  If both-edge capture is set, the counter continues counting and the counter value is loaded to TC1DRB again at the next rising (falling) edge.  Note: Be sure to read the capture value from the timer register B before the next tigger edge is detected. If the capture value cannot be read, it becomes undefined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |