# Programmable Dual Axis Digital Accelerometer and Impact Sensor

**Preliminary Technical Data**

ADIS16204

#### **FEATURES**

**Dual-axis** impact sensing Dual-axis acceleration sensing, +70g, +35g 14-bit resolution 17.1 mg/LSB, 8.55mg/LSB sensitivity Impact peak-level sample and hold **Programmable Event Recorder** 400Hz double-pole Bessel sensor response 12-bit digital temperature sensor output Digitally controlled sensitivity and bias Digitally controlled sample rate, up to 4096 SPS Dual alarm settings with programmable threshold limits Auxiliary digital I/O Digitally activated self test Digitally activated low power mode SPI®-compatible serial interface **Auxiliary 12-bit ADC input and DAC output** Single-supply operation: 3.0 V to +3.6 V 3500 g powered shock survivability

#### **APPLICATIONS**

Impact detection Condition monitoring Safety Systems Shock sensor

#### **GENERAL DESCRIPTION**

The ADIS16204 is a programmable impact sensor in a single compact package enabled by the Analog Devices *i*Sensor™ integration. By enhancing the Analog Devices *i*MEMS\* sensor technology with an embedded signal processing solution, the ADIS16204 provides tunable digital sensor data in a convenient format that can be accessed using a serial peripheral interface (SPI). The SPI interface provides access to measurements for dual-axis linear acceleration, a root-sum-square (RSS) of both axes, temperature, power supply, and one auxiliary analog input. Easy access to digital sensor data provides developers with a system-ready device, reducing development time, cost, and program risk.

Unique characteristics of the end system are accommodated easily through several built-in features, such as a single command in-system offset calibration, along with convenient sample rate control.

Rev. PrA

10/10/2006 4:24 AM

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

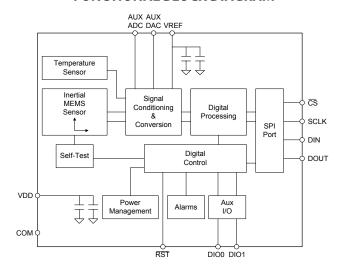

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The ADIS16204 offers the following embedded features, which eliminate the need for external circuitry and provide a simplified system interface:

- Peak sample and hold

- Programmable Event Recording

- Configurable trigger levels

- Auxiliary 12-bit ADC and DAC

- Configurable digital I/O port

- Digital self-test function

The ADIS16204 offers two power management features for managing system-level power dissipation: low power mode and a configurable shutdown feature.

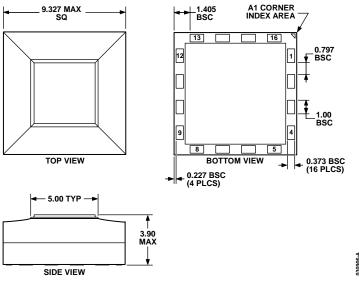

The ADIS16204 is available in a 9.2 mm  $\times$  9.2 mm  $\times$  3.9 mm laminate-based land grid array (LGA) package with a temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

# **Preliminary Technical Data**

# ADIS16204

## **TABLE OF CONTENTS**

| Features 1                | Timing Diagrams                             |

|---------------------------|---------------------------------------------|

|                           |                                             |

| Applications              | Absolute Maximum Ratings                    |

| Functional Block Diagram1 | ESD Caution                                 |

| General Description       | Pin Configuration and Function Descriptions |

| General Description1      | Pin Configuration and Function Descriptions |

| Revision History          | RECOMMENDED PAD GEOMETRY                    |

| Specifications3           | Outline Dimensions                          |

| Timing Specifications     | Ordering Guide                              |

#### **REVISION HISTORY**

8/06—Revision PSD1: PSD1 Kickoff Version

## **SPECIFICATIONS**

$T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ ,  $V_{DD} = 3.3$  V, unless otherwise noted.

Table 1.

| Parameter                                  | Conditions                  | Axis | Min         | Тур      | Max | Unit    |

|--------------------------------------------|-----------------------------|------|-------------|----------|-----|---------|

| ACCELEROMETER                              |                             |      |             |          |     |         |

| Output Full-Scale Range                    |                             | Х    | <u>+</u> 70 |          |     | g       |

|                                            |                             | Υ    | <u>+</u> 35 |          |     | g       |

| Sensitivity                                |                             | Х    |             | 17.1     |     | mg/LSB  |

| •                                          |                             | Υ    |             | 8.55     |     | mg/LSB  |

| Non linearity                              |                             |      |             | 0.2      |     | %       |

| Sensor-to-sensor Alignment Error           |                             |      |             | 0.1      |     | Degrees |

| Cross-axis Sensitivity                     |                             |      | -5          |          | +5  | %       |

| Resonant Frequency                         |                             |      |             | 24       |     | kHz     |

|                                            |                             |      |             |          |     |         |

| OFFSET                                     |                             |      |             |          |     |         |

| Zero-g Output                              |                             | Х    |             | 0.2      |     | g       |

|                                            |                             | Υ    |             | 1.85     |     | g       |

| NOISE                                      |                             |      |             |          |     |         |

| Noise Density                              | 10Hz – 400Hz, no post       |      |             | 1.8      |     | mg/√Hz  |

| •                                          | filtering                   |      |             |          |     |         |

|                                            |                             |      |             |          |     |         |

| FREQUENCY RESPONSE                         |                             |      |             |          |     |         |

| Sensor Bandwidth (-3dB)                    | 2-pole Bessel               |      | 360         | 400      | 440 | Hz      |

| Temperature Drift                          | 25° - Tmin  or  Tmax - 25°C |      |             | 2        |     | Hz      |

| ACCELEROMETER SELF-TEST STATE <sup>1</sup> |                             |      |             |          |     |         |

| Output Change When Active                  | 25°C                        | Χ    |             | 585      |     | LSB     |

| Output Change When Active                  |                             | Υ    |             | 1170     |     | LSB     |

| TEMPERATURE SENSOR                         |                             |      |             |          |     |         |

| Output at 25°C                             |                             |      |             | 1278     |     | LSB     |

| Scale Factor                               |                             |      |             | -2.13    |     | LSB/°C  |

| ADC INPUT                                  |                             |      |             |          |     |         |

| Resolution                                 |                             |      |             | 12       |     | Bits    |

| Integral Nonlinearity                      |                             |      |             | ±2       |     | LSB     |

| Differential Nonlinearity                  |                             |      |             | ±1       |     | LSB     |

| Offset Error                               |                             |      |             | ±4       |     | LSB     |

| Gain Error                                 |                             |      |             | ±2       |     | LSB     |

| Input Range                                |                             |      | 0           |          | 2.5 | V       |

| Input Capacitance                          | During acquisition          |      |             | 20       |     | pF      |

| ON-CHIP VOLTAGE REFERENCE                  |                             |      |             | 2.5      |     | V       |

| Accuracy                                   | At 25°C                     |      | -10         |          | +10 | mV      |

| Reference Temperature Coefficient          |                             |      |             | ±40      |     | ppm/°C  |

| Output Impedance                           |                             |      |             | 70       |     | Ω       |

| DAC OUTPUT                                 | 5 kΩ/100 pF to GND          |      |             |          |     |         |

| Resolution                                 | -                           |      |             | 12       |     | Bits    |

| Relative Accuracy                          | For Code 101 to Code 4095   |      |             | 4        |     | LSB     |

| Differential Nonlinearity                  |                             |      |             | 1        |     | LSB     |

| Offset Error                               |                             |      |             | ±5       |     | mV      |

| Gain Error                                 |                             |      |             | ±0.5     |     | %       |

| Output Range                               |                             |      |             | 0 to 2.5 |     | V       |

| Output Impedance                           |                             |      |             | 2        |     | Ω       |

| Output Settling Time                       |                             |      |             | 10       |     | μs      |

| Parameter                               | Conditions                                                                 | Axis | Min    | Тур   | Max | Unit    |

|-----------------------------------------|----------------------------------------------------------------------------|------|--------|-------|-----|---------|

| LOGIC INPUTS                            |                                                                            |      |        |       |     |         |

| Input High Voltage, V <sub>INH</sub>    |                                                                            |      | 2.0    |       |     | V       |

| Input Low Voltage, V <sub>INL</sub>     |                                                                            |      |        |       | 0.8 | V       |

| Logic 1 Input Current, I <sub>INH</sub> | $V_{IH} = V_{DD}$                                                          |      |        | ±0.2  | ±1  | μΑ      |

| Logic 0 Input Current, I <sub>INL</sub> | $V_{IL} = 0 V$                                                             |      |        | -40   | -60 | μΑ      |

| Input Capacitance, C <sub>IN</sub>      |                                                                            |      |        | 10    |     | pF      |

| DIGITAL OUTPUTS                         |                                                                            |      |        |       |     |         |

| Output High Voltage, V <sub>он</sub>    | I <sub>SOURCE</sub> = 1.6 mA                                               |      | 2.4    |       |     | V       |

| Output Low Voltage, Vol                 | I <sub>SINK</sub> = 1.6 mA                                                 |      |        |       | 0.4 | V       |

| SLEEP TIMER                             |                                                                            |      |        |       |     |         |

| Timeout Period <sup>2</sup>             |                                                                            |      | 0.5    |       | 128 | Seconds |

| FLASH MEMORY                            |                                                                            |      |        |       |     |         |

| Endurance <sup>3</sup>                  |                                                                            |      | 20,000 |       |     | Cycles  |

| Data Retention <sup>4</sup>             | T <sub>J</sub> = 85°C                                                      |      | 20     |       |     | Years   |

| CONVERSION RATE                         |                                                                            |      |        |       |     |         |

| Minimum Conversion Time                 |                                                                            |      |        | 244   |     | μs      |

| Maximum Conversion Time                 |                                                                            |      |        | 484   |     | ms      |

| Maximum Throughput Rate                 |                                                                            |      |        | 4096  |     | SPS     |

| Minimum Throughput Rate                 |                                                                            |      |        | 2.066 |     | SPS     |

| POWER SUPPLY                            |                                                                            |      |        |       |     |         |

| Operating Voltage Range VDD             |                                                                            |      | 3.0    | 3.3   | 3.6 | V       |

| Power Supply Current                    | Normal mode, SMPL_TIME $\geq$ 0x08 (f <sub>s</sub> $\leq$ 910 Hz), at 25°C |      |        | 12    |     | mA      |

|                                         | Fast mode, SMPL_TIME $\leq$ 0x07 ( $f_s \geq$ 1024 Hz), at 25°C            |      |        | 37    |     | mA      |

|                                         | Sleep mode, at 25°C                                                        |      |        | 500   | 750 | μΑ      |

| Turn-On Time                            |                                                                            |      |        | 130   |     | ms      |

$<sup>^{\</sup>text{1}}$  Self-test response changes as the square of  $V_{\text{DD}}.$

<sup>&</sup>lt;sup>2</sup> Guaranteed by design.

<sup>3</sup> Endurance is qualified as per JEDEC Standard 22 Method A117 and measured at –40°C, +25°C, +85°C, and +105°C.

<sup>4</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) 55°C as per JEDEC Standard 22 Method A117. Retention lifetime decreases with junction temperature.

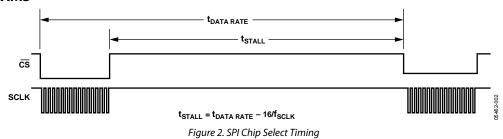

#### **TIMING SPECIFICATIONS**

$T_A = 25$ °C,  $V_{DD} = 3.3$  V, tilt = 0°, unless otherwise noted.

Table 2.

| Parameter             | Description                                                                           | Min <sup>1</sup> | Тур | Max  | Unit   |

|-----------------------|---------------------------------------------------------------------------------------|------------------|-----|------|--------|

| f <sub>SCLK</sub>     | Fast mode, SMPL_TIME $\leq$ 0x07 ( $f_s \geq$ 1024 Hz)                                | 0.01             |     | 2.5  | MHz    |

|                       | Normal mode, SMPL_TIME $\geq$ 0x08 (f <sub>s</sub> $\leq$ 910 Hz)                     | 0.01             |     | 1.0  | MHz    |

| t <sub>DATARATE</sub> | Chip select period, fast mode, SMPL_TIME $\leq$ 0x07 ( $f_s \geq$ 1024 Hz)            | 40               |     |      | μs     |

| <b>t</b> DATARATE     | Chip select period, normal mode, SMPL_TIME $\geq$ 0x08 (f <sub>s</sub> $\leq$ 910 Hz) | 100              |     |      | μs     |

| $t_{cs}$              | Chip select to clock edge                                                             | 48.8             |     |      | ns     |

| t <sub>DAV</sub>      | Data output valid after SCLK edge                                                     |                  |     | 100  | ns     |

| $t_{DSU}$             | Data input setup time before SCLK rising edge                                         | 24.4             |     |      | ns     |

| $t_{DHD}$             | Data input hold time after SCLK rising edge                                           | 48.8             |     |      | ns     |

| $t_{DF}$              | Data output fall time                                                                 |                  | 5   | 12.5 | ns min |

| $t_{\text{DR}}$       | Data output rise time                                                                 |                  | 5   | 12.5 | ns min |

| tsfs                  | CS high after SCLK edge                                                               | 5                |     |      | ns typ |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design, not tested.

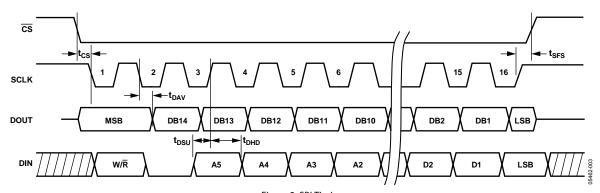

#### **TIMING DIAGRAMS**

Figure 3. SPI Timing (Utilizing SPI Settings Typically Identified as Phase = 1, Polarity = 1)

## ADIS16204

#### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                           | Rating              |

|-------------------------------------|---------------------|

| Acceleration (Any Axis, Unpowered)  | 3500 g              |

| Acceleration (Any Axis, Powered)    | 3500 <i>g</i>       |

| VDD to COM                          | −0.3 V to +7.0 V    |

| Digital Input/Output Voltage to COM | −0.3 V to +5.5 V    |

| Analog Inputs to COM                | -0.3 to VDD + 0.3 V |

| Analog Inputs to COM                | -0.3 to VDD + 0.3 V |

| Operating Temperature Range         | −40°C to +125°C     |

| Storage Temperature Range           | −65°C to +150°C     |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 4. Package Characteristics**

| Package Type    | θ <sub>JA</sub> | θ <sub>JC</sub> | Device Weight |  |

|-----------------|-----------------|-----------------|---------------|--|

| 16-Terminal LGA | 250°C/W         | 25°C/W          | 0.6 grams     |  |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

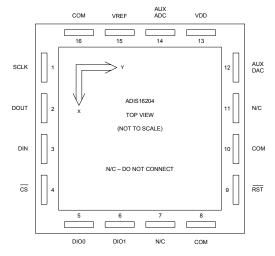

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic   | Type <sup>1</sup> | Description                                                                                                                              |

|---------|------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SCLK       | I                 | Serial Clock. SCLK provides the serial clock for accessing data from the part and writing serial data to the control registers.          |

| 2       | DOUT       | 0                 | Data Out. The data on this pin represents data being read from the control registers and is clocked out on the falling edge of the SCLK. |

| 3       | DIN        | I                 | Data In. Data written to the control registers is provided on this input and is clocked in on the rising edge of the SCLK.               |

| 4       | CS         | 1                 | Chip Select, Active Low. This input frames the serial data transfer.                                                                     |

| 5, 6    | DIO0, DIO1 | I/O               | Multifunction Digital I/O Pins.                                                                                                          |

| 7, 11   | NC         | _                 | No Connect.                                                                                                                              |

| 8, 10   | AUX COM    | S                 | Auxiliary Grounds. Connect to GND for proper operation.                                                                                  |

| 9       | RST        | 1                 | Reset, Active Low. This input resets the embedded microcontroller to a known state.                                                      |

| 12      | AUX DAC    | 0                 | Auxiliary DAC Analog Voltage Output.                                                                                                     |

| 13      | VDD        | S                 | +3.3 V Power Supply.                                                                                                                     |

| 14      | AUX ADC    | 1                 | Auxiliary ADC Analog Input Voltage.                                                                                                      |

| 15      | VREF       | 0                 | Precision Reference Output.                                                                                                              |

| 16      | COM        | S                 | Common. Reference point for all circuitry in the ADIS16204.                                                                              |

$<sup>^{1}</sup>$  S = Supply; O = Output; I = Input.

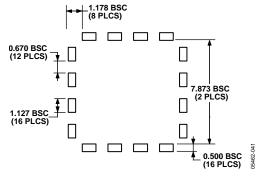

## **RECOMMENDED PAD GEOMETRY**

Figure 5. Example Pad Layout

## **OUTLINE DIMENSIONS**

Figure 6. 16-Terminal Land Grid Array [LGA] (CC-16-2) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                      | Temperature Range | Package Description               | Package Option |

|----------------------------|-------------------|-----------------------------------|----------------|

| ADIS16204BCCZ <sup>1</sup> | -40°C to +105°C   | 16-Terminal Land Grid Array [LGA] | CC-16-2        |

| ADIS16204/PCBZ             |                   | Evaluation Board                  |                |

$<sup>^{1}</sup>$  Z = Pb-free part.

## **NOTES**