# System Reset (with built-in watchdog timer)

## Monolithic IC MM1136

### **Outline**

These ICs were developed to drive low voltage batteries, and have a watchdog timer with built-in microcomputer reset voltage detection circuit and low battery detection circuit.

A single reference voltage is used for low battery voltage detection and microcomputer reset voltage detection, so detection voltage difference is uniform (= 0.2V). Further, there is a built-in watchdog timer for operation diagnosis, which prevents the system from running wild by generating an intermittent reset pulse during system mis-operation.

#### **Features**

1. Accurate voltage drop detection voltage

Low battery detection

Power supply voltage detection

3.4V±3%

2.2V±3%

3. Detection voltage error 0.2V±20mV 1-2

4. Hysteresis Both 50mV typ.

2. Watchdog function stop pin (can be made to function only as reset IC during Vcc rise)

3. Low current consumption 150µA typ.

### **Package**

SOP-8C (MM1136XF)

### **Applications**

- 1. 3V cordless telephones

- 2. Various types of small, handy equipment

#### **Series Table**

| Model  | <b>V</b> SLB | Vslr | T <sub>PR</sub> | Twd   | Twr |

|--------|--------------|------|-----------------|-------|-----|

| MM1136 | 3.4V         | 3.2V | 100ms           | 100ms | 2ms |

\*C⊤=0.02µF

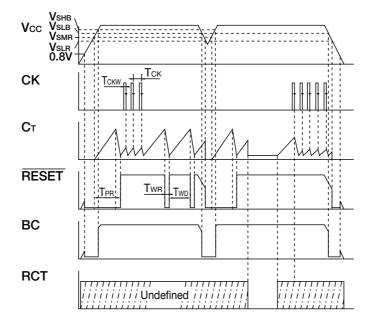

TPR: Reset hold time during Vcc rise

Two: Timer monitoring time

Twn: Reset time

Vslb: Battery check detection voltage

V<sub>SLR</sub>: Reset detection voltage

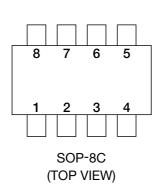

## Pin Assignment

| 1 | TC         |

|---|------------|

| 2 | BC (RESET) |

| 3 | CK         |

| 4 | GND        |

| 5 | Vcc        |

| 6 | RCT        |

| 7 | Vs         |

| 8 | RESET      |

## Pin Description

| Pin No. | Pin name   | Function                                                   |

|---------|------------|------------------------------------------------------------|

| 1       | TC         | Twd, Twr, Tpr time setting pins.                           |

| 2       | BC (RESET) | Battery check output pin (RESET low level output) for 3.4V |

| 3       | CK         | Clock input pin                                            |

| 4       | GND        | GND pin                                                    |

| 5       | Vcc        | Power supply voltage input pin                             |

| 6 RCT   |            | Watchdog timer stop pin                                    |

| 0       | RC1        | Operation → OPEN, Stop → connect to GND                    |

| 7       | Vs         | Detection voltage fine adjustment pin                      |

| 8       | RESET      | Reset output pin (low output)                              |

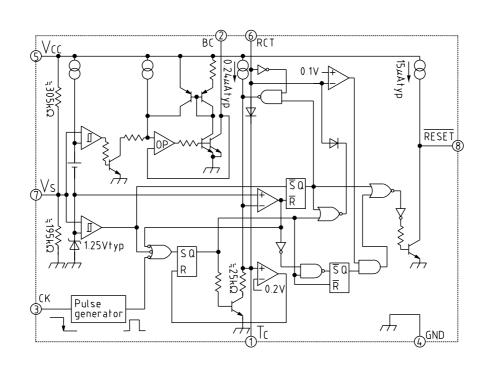

## Block Diagram

## Absolute Maximum Ratings

| Item                          | Symbol   | Rating               | Units                  |

|-------------------------------|----------|----------------------|------------------------|

| Power supply voltage          | Vcc max. | -0.3~+7              | V                      |

| Voltage applied to input pin  | Vin      | -0.3~Vcc+0.3 ( ≤ +7) | V                      |

| Voltage applied to output pin | Vout     | -0.3~Vcc+0.3 ( ≤ +7) | V                      |

| Allowable loss                | Pd       | 450                  | mW                     |

| Storage temperature           | Tstg     | -40~+125             | $^{\circ}\!\mathrm{C}$ |

## **Recommended Operating Conditions**

| Item                            | Symbol     | Rating    | Units |

|---------------------------------|------------|-----------|-------|

| Power supply voltage            | Vcc        | +2.5~+6.5 | V     |

| RESET sync current              | Iolr       | 0~1.5     | mA    |

| BC sync current                 | Iolc       | 0~1.5     | mA    |

| Clock input high level voltage  | Vckh       | 1.4<      | V     |

| Clock input low level voltage   | Vckl       | <0.4      | V     |

| Clock monitoring time setting   | Twd        | 1~1000    | ms    |

| Clock rise and fall times       | trck, tfck | <100      | μs    |

| Power supply voltage rise times | trvcc      | 100<      | μs    |

| Power supply voltage fall times | trvcc      | 50<       | μs    |

| TC pin capacitance              | Ст         | 0.002~2   | μF    |

| Operating temperature           | Тор        | -25~+75   | °C    |

## **Electrical Characteristics**

(Except where noted otherwise, Ta=25°C, V $_{\rm CC}$ =3.8V) (Except where noted otherwise, resistance unit is  $\Omega$ )

| Item                           | Symbol           | Measurement conditions                                | Min.  | Тур.  | Max.  | Units |

|--------------------------------|------------------|-------------------------------------------------------|-------|-------|-------|-------|

| Consumption current            | Icc              | No load                                               |       | 200   | 280   | μA    |

| RESET detection voltage        | Vslr             | Vcc : High→Low<br>RCT : GND, Vτc=OPEN                 | 3.10  | 3.20  | 3.30  | V     |

| Detection voltage              | $\angle V_{SR}$  |                                                       |       | +0.01 | ±0.05 | %/°C  |

| temperature coefficient R      | $\triangle T$    |                                                       |       | ±0.01 | 20.00 | 707 C |

| Hysteresis voltage R           | VHYSR            | Vcc : Low→High<br>RCT : GND, Vτc=OPEN                 |       | 50    | 100   | mV    |

| BC detection voltage           | V <sub>SLB</sub> | Vcc : High→Low, Rlb=10k                               | 3.30  | 3.40  | 3.50  | V     |

| Detection voltage              | ∠VsB             |                                                       |       | .0.01 | ±0.05 | %/°C  |

| temperature coefficient B      | $\Delta T$       |                                                       |       | ±0.01 | ±0.03 | 70/ C |

| Hysteresis voltage B           | VHYSB            | Vcc : Low → High, R <sub>LB</sub> =10k                | 25    | 50    | 100   | mV    |

| Detection voltage difference   | ∠Vsl             | ∠Vsl=Vslb-Vslr                                        | 0.18  | 0.20  | 0.22  | V     |

| CK input threshold             | $V_{TH}$         |                                                       | 0.8   | 1.2   | 2     | V     |

| CK input current               | I <sub>IH</sub>  | Vck=3.8V                                              |       | 0     | 1     | μA    |

|                                | IIL              | Vck=0.0V                                              | -15   | -6    | -2    | μι    |

| Output voltage RH              | Vohr             | Ireset=-5µA                                           | 3.0   | 3.4   |       | V     |

| Output voltage BH              | Vohb             | R <sub>LB</sub> =10k                                  | 3.2   | 3.6   |       | V     |

| Output voltage RL              | Volr             | IRESET=1mA, Vcc=3.0V                                  |       | 0.3   | 0.5   | V     |

| Output voltage BL              | Volb             | IBC=5mA, VCC=3.0V                                     |       | 0.3   | 0.5   | V     |

| Output sync current R          | Iolr             | Vreset=0.5V, Vcc=3.0V                                 | 1     | 2     |       | mA    |

| Output sync current B          | Iolb             | V <sub>BC</sub> =0.5V, V <sub>CC</sub> =3.0V          | 5     | 10    |       | mA    |

| Output source current R        | Iohr             | Vreset=3.4V                                           | 8     | 15    |       | μA    |

| C⊤ charge current              | Іст1             | V <sub>TC</sub> =1.0V during watchdog timer operation | -0.48 | -0.24 | -0.16 | μA    |

|                                | Іст2             | V <sub>TC</sub> =1.0V during power ON reset operation | -0.48 | -0.24 | -0.16 | μA    |

| Minimum operating power supply | Voc              | Vreset=0.4V                                           |       | 0.8   | 1.0   | V     |

| voltage to ensure RESET        | Vcc              | IRESET=0.1mA                                          |       | 0.8   | 1.0   | v     |

| Vcc input pulse width                    | Ты           | Vcc 3.8V                            | 8  |     |     | μs |

|------------------------------------------|--------------|-------------------------------------|----|-----|-----|----|

| CK input pulse width                     | Тскw         | CK TCKW or TCKW                     | 3  |     |     | μs |

| CK input cycle                           | Тск          | СК Тск                              | 20 |     |     | μs |

| Watchdog timer monitoring time *1        | Twd          | C <sub>T</sub> =0.02µF              | 50 | 100 | 150 | ms |

| Watchdog timer reset time *2             | Twr          | Ст=0.02µF                           | 1  | 2   | 3   | ms |

| Reset hold time for power supply rise *3 | TPR          | Ст=0.02µF                           | 50 | 100 | 150 | ms |

| RESET delay time                         | <b>t</b> pdr | Vcc : High → Low, Rlr=10k, Clr=15pF |    | 10  |     | μs |

| BC delay time                            | <b>t</b> PDB | Vcc : High→Low, Rlb=4.7k, Clb=15pF  |    | 10  |     | μs |

| RESET rise time                          | trr          | Rlr=10k, Clr=15pF                   |    | 10  |     | μs |

| RESET fall time                          | tfr          | Rlr=10k, Clr=15pF                   |    | 2   |     | μs |

| BC rise time                             | trв          | Rlb=4.7k, Clb=15pF                  |    | 10  |     | μs |

| BC fall time                             | tғв          | Rlb=4.7k, Clb=15pF                  |    | 2   |     | μs |

#### Notes:

- \*1 Monitoring time is the time from the last pulse (negative edge) of the timer clear clock pulse until reset pulse output.

- In other words, reset output is output if a clock pulse is not input during this time.

- \*2 Reset time means reset pulse width. However, this does not apply to power ON reset.

- \*3 Reset hold time is the time from when Vcc exceeds detection voltage (Vshr) during power ON reset until reset release (RESET output high).

- \*4 Watchdog timer monitoring time (TwD), watchdog timer reset time (TwR) and reset hold time (TPR) during power supply rise can be changed by varying CT capacitance. The times are expressed by the following formulae.

$T_{PR}$  (ms)  $\stackrel{:}{=} 5000 \times C_T$  ( $\mu F$ )  $T_{WD}$  (ms)  $\stackrel{:}{=} 5000 \times C_T$  ( $\mu F$ )  $T_{WR}$  (ms)  $\stackrel{:}{=} 100 \times C_T$  ( $\mu F$ ) Example : When  $C_T = 0.02 \mu F$

$T_{PR} = 100 ms$   $T_{WD} = 100 ms$   $T_{WR} = 2 ms$

- \*5 Two can be varied by placing a resistor (1MEG $\Omega$  or more) between the RCT pin and Vcc.

- $\star 6$  The voltage range when measuring output rise and fall time is  $10\sim 90\%$ .

- $\star 7~\text{Vcc}$  rise time should be 100µs or more, and fall time should be 50µs or more.

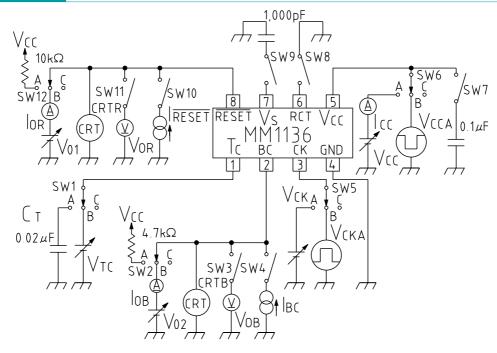

### **Measuring Circuit**

## **Timing Chart**

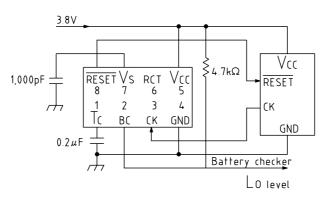

### **Basic Circuit Diagram**