# **Design of Power Factor Correction Circuit Using Greenline™ Compact Power Factor Controller MC33260**

http://onsemi.com

Prepared by Ming Hian Chew

ON Semiconductor Analog Applications Engineering

#### Introduction

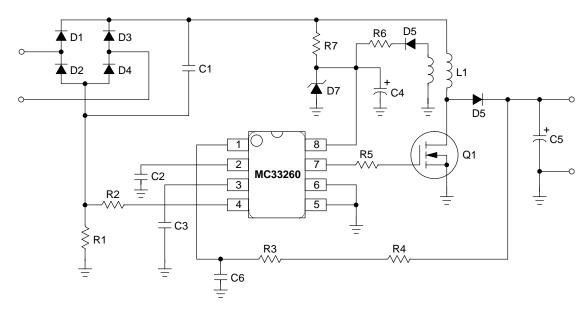

The MC33260 is an active power factor controller that functions as a boost pre–converter which, meeting international standard requirement in electronic ballast and off–line power supply application. MC33260 is designed to drive a free running frequency discontinuous mode, it can also be synchronized and in any case, it features very effective protections that ensure a safe and reliable operation.

This circuit is also optimized to offer extremely compact and cost effective PFC solutions. It does not entail the need of auxiliary winding for zero current detection hence a simple coil can be used instead of a transformer if the MC33260 Vcc is drawn from the load (please refer to page 19 of the data sheet). While it requires a minimum number

#### **APPLICATION NOTE**

of external components, the MC33260 can control the follower boost operation that is an innovative mode allowing a drastic size reduction of both the inductor and the power switch. Ultimately, the solution system cost is significantly lowered.

Also able to function in a traditional way (constant output voltage regulation level), any intermediary solutions can be easily implemented. This flexibility makes it ideal to optimally cope with a wide range of applications.

This application note will discuss on the design of power factor correction circuit with MC33260 with traditional boost constant output voltage regulation level operation and follower boost variable output voltage regulation level operation. For derivation of the design equations related to the IC please refer to MC33260 data sheet.

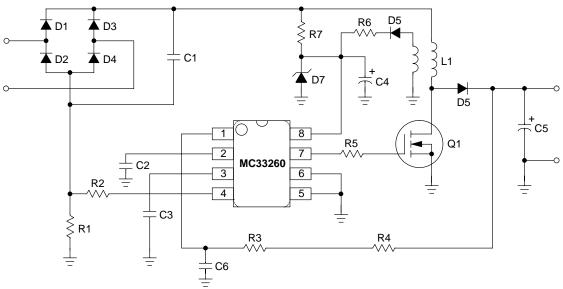

Figure 1. Application Schematic of MC33260

#### **PFC Techniques**

Many PFC techniques have been proposed, boost topology, which can operate in continuous and discontinuous mode, is the most popular. Typically, continuous mode is more favorable for high power application for having lower peak current. On the other hand, for less than 500 W application, discontinuous mode offers smaller inductor size, minimal parts count and lowest

cost. This paper will discuss design of PFC with MC33260, which operates in critical conduction mode.

#### **Discontinuous Conduction Mode Operation**

Critical conduction mode operation presents two major advantages in PFC application. For critical conduction mode, the inductor current must fall to zero before start the next cycle. This operation results in higher efficiency and eliminates boost rectifier reverse recovery loss as MOSFET cannot turn—on until the inductor current reaches zero.

Secondly, since there are no dead–time gaps between cycles, the ac line current is continuous thus limiting the peak switch to twice the average input current. The converter works right on critical conduction mode, which results in variable frequency operation.

#### **Inductor Waveform**

$$\frac{V}{L} = \frac{di}{dt} \tag{1}$$

Equation (1) is the center of the operation of PFC boost converter where  $V=V_{in}(t)$ , the instantaneous voltage across the inductor. Assuming the inductance and the on–time over each line half–cycle are constant, di is actually the peak current,  $I_{Lpk}$ , this is because the inductor always begins charging at zero current.

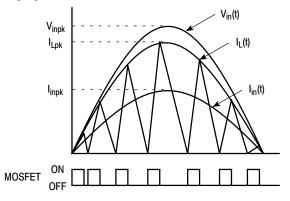

Figure 2. Inductor Waveform

#### **Design Criteria**

The basic design specification concerns the following:

- Mains Voltage Range:  $V_{ac(LL)} V_{ac(HL)}$

- Regulated DC Output Voltage: V<sub>0</sub>

- Rated Output Power: Po

- Expected Efficiency, η

#### **PFC Power Section Design**

Instantaneous Input Voltage, V<sub>in</sub>(t)

Peak Input Voltage, Vinpk

Both  $V_{in}(t)$  and  $V_{inpk}$  are related by below equation

$$V_{in}(t) = V_{inpk} \sin(\omega t)$$

(2)

where

$$V_{inpk} = \sqrt{2} V_{inrms}$$

(3)

Instantaneous Input Current, I<sub>in</sub>(t)

Peak Input Current, Iinpk,

Both I<sub>in</sub>(t) and I<sub>inpk</sub> are related by below equation

$$I_{in}(t) = I_{inpk} \sin(\omega t),$$

(4)

where

$$I_{inpk} = \sqrt{2}I_{inrms}$$

(5)

Input power of the PFC circuit,  $P_{in}$  can be expressed in following equation, by substituting equation (3) and (5).

$$P_{in} = V_{inrms} I_{inrms} = \frac{V_{inpk}}{\sqrt{2}} \cdot \frac{I_{inpk}}{\sqrt{2}} = \frac{V_{inpk} I_{inpk}}{2}$$

(6)

The output power, Po is given by

$$P_{O} = V_{O}I_{O} = \eta P_{in} \tag{7}$$

PFC circuit efficiency is needed in the design equation, for low line operation, it is typically set at 92% while 95% for high line operation. Substituting equation (6) into equation (7),

$$P_{O} = \eta P_{in} = \eta \frac{V_{inpk}I_{inpk}}{2}$$

(8)

Express the above equation in term of I<sub>inpk</sub>,

$$I_{inpk} = \frac{2P_0}{\eta V_{inpk}} = \frac{\sqrt{2}P_0}{\eta V_{inrms}}$$

(9)

The average input current is equal to average inductor current,  $I_{L(avg)}$ ,

$$I_{L(avg)} = I_{in} \tag{10}$$

It has been understood that peak inductor current,  $I_{Lpk}$  is exactly twice the average inductor current,  $I_{L(avg)}$  for critical conduction operation.

$$I_{Lpk} = 2I_{L(avg)} = \frac{2\sqrt{2}P_{O}}{\eta V_{inrms}}$$

(11)

Since  $I_{Lpk}$  is maximum at minimum required ac line voltage,  $V_{ac(LL)}$ ,

$$I_{Lpk} = \frac{2\sqrt{2}P_{O}}{\eta V_{ac(LL)}}$$

(12)

#### **Switching Time**

In theory, the on–time,  $t_{(on)}$  is constant. In practice,  $t_{(on)}$  tends to increase at the ac line zero crossings due to the charge on output capacitor  $C_{out}$ . Let  $V_{ac} = V_{ac(LL)}$  for initial  $t_{(on)}$  and  $t_{(off)}$  calculations.

#### On-time

By solving inductor equation (1), on–time required to charge the inductor to the correct peak current is:

$$t_{(on)} = I_{Lpk} \frac{L_P}{V_{inpk}}$$

(13)

Substituting equation (3) and (12) into equation (13), results in:

$$t_{(on)} = \frac{2\sqrt{2}P_{o}}{\eta V_{ac(LL)}} \cdot \frac{L_{p}}{\sqrt{2}V_{ac(LL)}} = \frac{2P_{o}L_{p}}{\eta V_{ac(LL)}^{2}}$$

(14)

#### Off-time

The instantaneous switch off—time varies with the line and load conditions, as well as with the instantaneous line voltage. Off—time is analyzed by solving equation (1) for the inductor discharging where the voltage across the inductor is  $V_{\rm o}$  minus  $V_{\rm in}$ .

$$t_{(off)} = \frac{I_{Lpk}L_{P}}{V_{O} - V_{inpk}sin(\omega t)}$$

(15)

Multiplying nominator and denominator with  $V_{inpk} sin\omega(t)$  results in:

$$t_{(off)} = \frac{\frac{I_{Lpk}L_{P}}{V_{inpk}sin(\omega t)}}{\frac{V_{O} - V_{inpk}sin(\omega t)}{V_{inpk}sin(\omega t)}} = \frac{t_{(on)}}{\frac{V_{O}}{\sqrt{2}V_{inpk}|sin(\theta)}} = (16)$$

where  $\omega t = \theta$

The off-time,  $t_{(off)}$  is greatest at the peak of the ac line voltage and approaches zero at the ac line zero crossings. Theta  $(\theta)$  represents the angle of the ac line voltage.

The off-time is at a minimum at ac line crossings. This equation is used to calculate  $t_{(off)}$  as Theta approaches zero.

$$t_{(off)min} = \frac{I_{Lpk}^{L}P}{V_{O}}, \theta = 0^{\circ}$$

(17)

#### Switching Frequency

$$f = \frac{1}{t_{(on)} + t_{(off)}}$$

(18)

Switching frequency changes with the steady state line and load operating conditions along with the instantaneous input line voltage. Typically, the PFC converter is designed to operate above the audible range after accommodating all circuit and component tolerances. 25 kHz is a good first approximation. Higher frequency operation that can significantly reduce the inductor size without negatively impacting efficiency or cost should also be evaluated.

The minimum switching frequency occurs at the peak of the ac line voltage. As the ac line voltage traverses from peak to zero,  $t_{(off)}$  approaches zero producing an increase in switching frequency.

#### **Inductor Value**

Maximum on–time needs to be programmed into the PFC controller timing circuit. Both  $t_{(on)max}$  and  $t_{(off)max}$  will be individually calculated and added together to obtain the maximum conversion period,  $t_{total}$ . This is required to obtain the inductor value.

$$t_{(on)max} = \frac{2P_0L_P}{\eta V_{ac(LL)}^2}$$

(19)

$$t_{(off)max} = \frac{I_{Lpk}^{L}P}{V_{0} - V_{inpk}}, (\theta) \approx 90^{\circ}$$

(20)

The exact inductor value can be determined by solving equation (21) by substituting equation (19) and (20) at the selected minimum operating frequency.

$$t_{\text{total}} = t_{\text{(on)max}} + t_{\text{(off)max}}$$

(21)

Equation (21) becomes

$$t_{total} = \frac{\sqrt{2} P_o L_p V_o}{V_{ac(LL)}^2 \eta \left(\frac{V_o}{\sqrt{2}} - V_{ac(LL)}\right)}$$

(22)

By rearranging in term of L<sub>p</sub>,

$$L_{p} = \frac{t_{total} \left( \frac{v_{o}}{\sqrt{2}} - V_{ac(LL)} \right) \eta V_{ac(LL)}^{2}}{\sqrt{2} V_{o} P_{o}}$$

(23)

Equation (23) can be rewritten by substituting rearranged equation (12) in term of  $\sqrt{2P_0}$ .

$$L_{p} = \frac{2 \times t_{total} \left( \frac{V_{o}}{\sqrt{2}} - V_{ac(LL)} \right) V_{ac(LL)}}{V_{o} I_{Lpk}}$$

(24)

Let the switching cycle  $t=40\mu s$  for universal input (85 to 265  $V_{ac}$ ) operation and 20  $\mu s$  for fixed input (92 to 138  $V_{ac}$ , or 184 to 276  $V_{ac}$ ) operation.

#### **Inductor Design Summary**

The required energy storage of the boost inductor is:

$$W_{L} = \frac{1}{2} L_{pl}^{2} I_{pk}^{2} \tag{25}$$

The number of turns required for a selected core size and material is:

$$N_{P} = \frac{L_{P}I_{Lpk}10^{6}}{B_{max}A_{P}} \tag{26}$$

where  $B_{max}$  is in Teslas and  $A_e$  is in square millimeters (mm<sup>2</sup>)

The required air gap to achieve the correct inductance and storage is expressed by:

$$I_{gap} = \frac{4\pi 10^{-7} \,N_{p}^{2} \,A_{e}}{L_{p}} \,mm \tag{27}$$

#### **Design of Auxiliary Winding**

MC33260 does not entail an auxiliary winding for zero current detection. Hence if DC voltage can be tapped from the SMPS or electronic ballast connected to the output of PFC, this step can be skipped. Then an inductor is what it needs.

The auxiliary winding exhibits a low frequency ripple (100–120 Hz). The Vcc capacitor must be large enough (about 47  $\mu$ F) to minimize voltage variations. As a rule of thumb, you can use the below equation to estimate the auxiliary turn number:

$$N_{aux} = \frac{N_p \cdot V_{aux}}{V_L} = \frac{N_p \cdot V_{aux}}{V_0 - V_{ac(HL)}}$$

(28)

The MC33260  $V_{CC}$  maximum voltage being 16 V, one must add a resistor (in the range of 22  $\Omega$ ) and a 15 V zener to protect the circuit against excessive voltages. Vaux should be chosen above the Under-Voltage Lockout threshold (10 V) and below the zener voltage.

#### **Selection of Output Capacitor**

The choice of output capacitance value is dictated by the required hold–up time,  $t_{hold}$  or the acceptable output ripple voltage,  $V_{orip}$  for a given application. As a rule of thumb, can start with 1  $\mu$ F/watt.

#### Selection of Semiconductors

Maximum currents and voltages must first be determined for over all operating conditions to select the MOSFET and boost rectifier. As a rule of thumb, derate all semiconductors to about 75–80% of their maximum ratings. This implying the need of devices with at least 500 V breakdown voltage. Bipolar transistors are an acceptable alternative to MOSFET if the switching frequency is maintained fairly low. High voltage diodes with recovery times of 200 ns, or less should be used for the boost rectifier. One series of the popular devices is the MURXXX Ultrafast Rectifier Series from ON Semiconductor.

Maximum power MOSFET conduction losses.

$$P_{(on)max} \approx \frac{1}{6} \times R_{ds(on)} \times I_{Lpk}^{2} 1 - \frac{1.2 \times V_{ac(LL)}}{V_{o}} (29)$$

#### **Designing the Oscillator Circuit**

For traditional boost operation,  $C_T$  is chosen with below equation:

$$C_{T} \ge \frac{2 \times K_{osc} \times L_{p} \times P_{in} \times V_{o}^{2}}{V_{ac(LL)}^{2} \times R_{o}^{2}} - C_{int}$$

(30)

## Design of Regulation and Overvoltage Protection Circuit

The output voltage regulation level can be adjusted by  $R_0$ ,

$$R_0 \approx \frac{V_0}{200 \, \mu A} \tag{31}$$

#### **Designing the Current Sense Circuit**

The inductor current is converted into a voltage by inserting a ground referenced resistor,  $R_{CS}$  in series with the input diode bridge. Therefore a negative voltage proportional to the inductor current is built.

The current sense resistor losses, P<sub>Rcs</sub>:

$$P_{RCS} = \frac{1}{6} \times R_{CS} \times I_{Lpk}^{2}$$

(32)

Overcurrent protection resistor, R<sub>OCP</sub> can be determined with below equation:

$$R_{OCP} = \frac{R_{CS} \times I_{Lpk}}{I_{OCP}}$$

(33)

## **Current Limiting With Boost Topology Power Factor Correction Circuit**

Unlike buck and flyback circuits, because there is no series switch between input and output in the boost topology, high current occurring with the start—up inrush current surge charging the bulk capacitor and fault load conditions cannot be limited or controlled without additional circuitry.

The MC33260 Zero Current Detection uses the current sensing information to prevent any power switch turn on as long as some current flows through the inductor. Then, during start—up, the power MOSFET is not allowed to turn on while in—rush current flows. Then there is no risk to have the power switch destroyed at start—up because of the in—rush current.

In the same way, in an overload case, the power MOSFET is kept off as long as there is a direct output capacitor charge current, i.e., when the input voltage is higher than the output voltage. Consequently, overload working is fully safe for the power MOSFET. This is one of the major advantages compared to MC33262 and competition.

#### **Current Limiting for Start-up Inrush**

Initially V<sub>0</sub> is zero, when the converter is turned on, the bulk capacitor will charge resonantly to twice Vin. The voltage can be as high as 750 V if V<sub>in</sub> happens to be at the peak high–line 265 V condition (375 V). The peak resonant charging current through the inductor will be many times greater than normal full load current. the inductor must be designed to be much larger and more expensive to avoid saturation. The boost shunt switch cannot do anything to prevent this and could be worse if turned on during start–up.

The inrush current and voltage overshoot during the start-up phase is intolerable. A fuse is not suitable, as it will blow each time the supply is turned on.

There are several methods that may be used to solve the start—up problem:

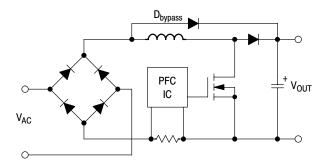

#### 1. Start-up Bypass Rectifier

This is implemented by adding an additional rectifier bypassing the boost inductor. The bypass rectifier will divert the start—up inrush current away from the boost inductor as shown in Figure 3. The bulk capacitor charges through  $D_{bypass}$  to the peak AC line voltage without resonant overshoot and without excessive inductor current.  $D_{bvpass}$  is

reverse—biased under normal operating conditions. If load overcurrent pulls down  $V_o$ ,  $D_{bypass}$  conducts, but this is probably preferable to having the high current flowing through boost inductor.

Figure 3. Rectifier bypass of start-up inrush current

#### 2. External Inrush Current Limiting Circuit

For low power system, a thermistor in series with the pre-converter input will limit the inrush current. Concern is the thermistor may not respond fast enough to provide protection after a line dropout of a few cycles.

A series input resistor shunted by a Triac or SCR is a more efficient approach. A control circuit is necessary. This method can function on a cycle-by-cycle basis for protection after a dropout.

#### **Load Overcurrent Limiting**

If an overcurrent condition occurs and exceeds the boost converter power limit established by the control circuit,  $V_{\rm o}$  will eventually be dragged down below the peak value of the AC line voltage. If this happens, current will rise rapidly and without limit through the series inductor and rectifier. This may result in saturation of the inductor and components will fail. The control circuit holds off the shunt switch, since the current limit function is activated. It cannot help to turn the switch ON – the inductor current will rise even more rapidly and switch failure will occur.

Typically, a power factor correction circuit is connected to another systems like switched mode power supply or electronic ballast. These downstream converters typically will have current limiting capability, eliminating concern about load faults. However, a downstream converter or the bulk capacitor might fail. Hence there is a possibility of a short circuit at the load.

If it is considered necessary to limit the current to a safe value in the event of a downstream fault, some means external to the boost converter must be provided.

#### Design Example I – Traditional Boost Constant Output Voltage Regulation Level Operation Power Factor Correction

The basic design specification concerns the following:

• Mains Voltage Range:  $V_{ac(LL)} - V_{ac(HL)} = 85 - 265 V_{ac}$

- Regulated DC Output Voltage: V<sub>o</sub> = 400 V<sub>dc</sub>

- Rated Output Power: P<sub>0</sub> = 80 W

- Expected Efficiency, η > 90%

#### A. The input power, Pin is given by

$$P_{in} = \frac{P_0}{n} = \frac{80}{0.92} = 86.96 \text{ W}$$

## B. Input diode current is maximum at $V_{inrms} = V_{ac(LL)}$

$$I_{\text{inpk}} = \frac{\sqrt{2} P_0}{\eta V_{\text{ac(LL)}}} = \frac{\sqrt{2} \times 80}{0.92 \times 85} = 1.447 A$$

#### C. Inductor design

1. Inductor peak current:

$$I_{Lpk} = 2I_{inpk} = 2 \times 1.447 = 2.894 A$$

2. Inductor value:

$$\begin{aligned} \mathsf{L}_{p} &= \frac{2 \times \mathsf{t}_{total} \left( \frac{\mathsf{v}_{o}}{\sqrt{2}} - \mathsf{V}_{ac(LL)} \right) \mathsf{V}_{ac(LL)}}{\mathsf{V}_{o} \mathsf{I}_{Lpk}} \\ &= \frac{2 \times 40 \times 10^{-6} \left( \frac{400}{\sqrt{2}} - 85 \right) 85}{400 \times 2.894} = 1.162 \, \text{mH} \end{aligned}$$

Let the switching cycle  $t = 40 \mu s$  for universal input (85 to 265  $V_{ac}$ ) operation.

3. The number of turns required for a selected core size and material is:

$$N_{P} = \frac{L_{P}I_{Lpk}^{10^{6}}}{B_{max}A_{e}} = \frac{1.162 \times 10^{-3} \times 2.894 \times 10^{-6}}{0.3 \times 60}$$

$$= 186.8 \text{ turns} \approx 187 \text{ turns}$$

Using EPCOS E 30/15/7,  $B_{max} = 0.3 \text{ T}$  and  $A_e = 60 \text{ mm}^2$ .

4. The required air gap to achieve the correct inductance and storage is:

$$I_{gap} = \frac{4\pi 10^{-7} N_{p}^{2} A_{e}}{L_{p}}$$

$$= \frac{4\pi \times 10^{-7} \times 187^{2} \times 60 \times 10^{-6}}{1.162 \times 10^{-3}}$$

= 2.269 mm

5. Design of Auxiliary Winding

$$N_{aux} = \frac{V_{aux}N_P}{\left(V_O - V_{ac(HL)}\right)} = \frac{14 \times 187}{(400 - 265)}$$

= 19.4 turns \approx 20 turns

Round up to 20 turns to make sure enough voltage at the auxiliary winding.

#### D. To determine the output capacitor

As rule of thumb, for 80 W output, start with 100  $\mu F\!\!\!\!/ ,$  450 V capacitor.

#### E. Calculation of MOSFET conduction losses

A 8A, 500V MOSFET, MTP8N50E is chosen. The on resistance,  $R_{ds(on)} \approx 1.75~\Omega@100^{\circ}C$ . Therefore, maximum power MOSFET conduction losses is:

$$P_{\text{(on)max}} \approx \frac{1}{6} \times R_{\text{ds(on)}} \times I_{\text{Lpk}}^{2} 1 - \frac{1.2 \times V_{\text{ac(LL)}}}{V_{0}}$$

$$= \frac{1}{6} \times 1.75 \times 2.894^{2} 1 - \frac{1.2 \times 85}{400} = 1.82 \text{ W}$$

## F. Design of regulation and overvoltage protection circuit

The output voltage regulation level can be adjusted by R<sub>0</sub>,

$$R_0 \approx \frac{V_0}{200 \, \mu A} = \frac{400}{200 \, \mu A} = 2 \, M\Omega$$

Use two 1 M $\Omega$  resistors in series.

#### G. Designing the oscillator circuit

For traditional boost operation, C<sub>T</sub> is chosen with below equation:

$$C_{T} \geq \frac{2 \times K_{OSC} \times L_{P} \times P_{in} \times V_{o}^{2}}{V_{ac(LL)}^{2} \times R_{o}^{2}} - C_{int} =$$

$$\frac{2 \times 6400 \times 1.162 \text{mH} \times 86.96 \times 400^2}{85^2 \times 2 \text{M}\Omega^2} - 15 \text{pF} = 7.16 \text{nF}$$

Use 10 nF capacitor.

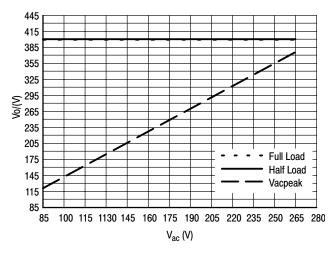

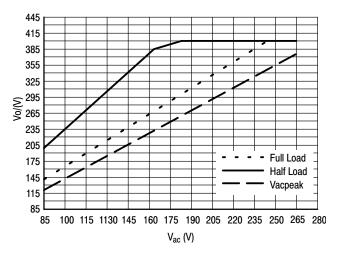

Figure 4. Theoretical  $V_o$  versus  $V_{ac}$  with  $C_T = 10nF$

#### H. Design of the current sense circuit

Choose  $R_{cs} = 0.68 \Omega$

1. So the current sense resistor losses, P<sub>Rcs</sub>:

$$P_{RCS} = \frac{1}{6} \times R_{CS} \times I_{Lpk}^2 = \frac{1}{6} \times 1 \times 2.894^2 = 0.949 \text{ W}$$

Therefore the power rating of R<sub>CS</sub> is chosen to be 2 W.

2. Overcurrent protection resistor,  $R_{OCP}$  can be determined with below equation:

$$R_{OCP} = \frac{R_{CS} \times I_{Lpk}}{I_{OCP}} = \frac{0.68 \times 2.894}{205 \, \mu A} = 9600 \, \Omega$$

Use  $10000~\Omega$  resistor. This provide current limit at 3.01 A versus calculated value of  $I_{Lpk}=2.894~A$ .

## 80 W, Universal Input, Traditional Boost Constant Output Voltage Level Regulation Operation Power Factor Correction Circuit Part List

| Index | Value         | Comment                              | Index | Value       | Comment              |

|-------|---------------|--------------------------------------|-------|-------------|----------------------|

| C1    | 0.63 μF@600 V | Filtering Capacitor                  | R6    | 22 Ω@0.25 W | Aux Winding Resistor |

| C2    | 680 nF        | Pin 2 V <sub>control</sub> Capacitor | R7    | 100 KΩ@2 W  | Start-up Resistor    |

| C3    | 10 nF         | Pin 3 Oscillator Capacitor           | R8    | 1N5406      | Input Diode          |

| C4    | 100 μF@50 V   | Aux Capacitor, E-Cap                 | D1    | 1N5406      | Input Diode          |

| C5    | 100μF@450V    | Output Capacitor, E-Cap              | D2    | 1N5406      | Input Diode          |

| C6    | 1 nF@50 V     | Feedback Filtering Capacitor         | D3    | 1N5406      | Input Diode          |

| R1    | 0.68 Ω@2 W    | Current Sense Resistor               | D4    | 1N4937      | Aux Winding Diode    |

| R2    | 10 KΩ@0.25 W  | OCP Sensing Resistor                 | D5    | MUR460      | Boost Diode          |

| R3    | 1 MΩ@0.25 W   | Feedback Resistor                    | D6    | 1N5245      | Aux 15 V Zener Diode |

| R4    | 1 MΩ@0.25 W   | Feedback Resistor                    | D7    | MTP8N50E    | Power MOSFET         |

| R5    | 10 Ω@0.25 W   | Gate Resistor                        | Q1    | 1.162 mH    | Inductor             |

<sup>\*</sup> E 30/15/7, N67 Material from EPCOS

Primary – 187 turns of # 23 AWG, Secondary – 19 turns of # 23 AWG. Gap length 2.269mm total for a primary inductance L<sub>P</sub> of 1.162mH.

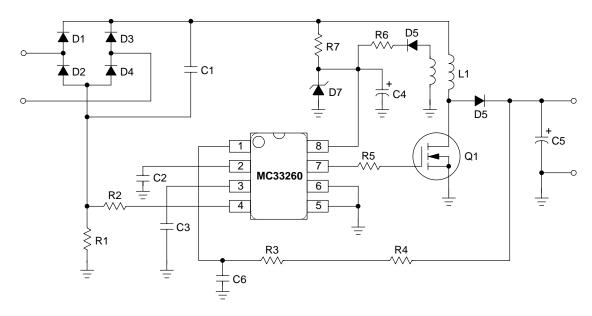

Figure 5. 80 W Universal Input, Traditional Boost Constant Output Voltage Regulation Level Operation Power Factor Correction Circuit

## Design Table for Universal Input, Traditional Boost Constant Output Voltage Regulation Level Operation Power Factor Correction

| Po               | 25            | 50    | 75       | 100   | 125   | 150       | 200   | (Watts)       |

|------------------|---------------|-------|----------|-------|-------|-----------|-------|---------------|

| L <sub>P</sub>   | 3.720         | 1.860 | 1.240    | 0.930 | 0.744 | 0.620     | 0.465 | (mH)          |

| Co               | 33            | 68    | 100      | 100   | 150   | 150       | 220   | (μ <b>F</b> ) |

| R <sub>CS</sub>  | 2             | 1     | 0.68     | 0.5   | 0.39  | 0.33      | 0.25  | Ω             |

| R <sub>OCP</sub> | 10000         | 10000 | 10000    | 9100  | 9100  | 9100      | 9100  | Ω             |

| C <sub>in</sub>  | 0.22          | 0.63  | 0.63     | 1.0   | 1.0   | 1.0       | 1.0   | (μ <b>F</b> ) |

| СТ               | 10            | 10    | 10       | 10    | 10    | 10        | 10    | (nF)          |

| Q                | MTP4N50E      |       | MTP8N50E |       |       | MTW14N50E |       |               |

| Dout             | MUR160 MUR460 |       |          |       |       |           |       |               |

| D <sub>in</sub>  | 1N4           | 007   |          |       |       |           |       |               |

#### Design Example II – Follower Boost Variable Output Voltage Regulation Level Operation Power Factor Correction

The basic design specification concerns the following:

- Mains Voltage Range:  $V_{ac(LL)} V_{ac(HL)} = 85 265 V_{ac}$

- Maximum Regulated DC Output Voltage: V<sub>o</sub> = 400 V<sub>dc</sub>

- Minimum Regulated DC Output Voltage: V<sub>omin</sub> = 140 V<sub>dc</sub>

- Rated Output Power: P<sub>o</sub> = 80 W

- Expected Efficiency, η > 90%

#### A. The input power, $P_{in}$ is given by

$$P_{in} = \frac{P_0}{\eta} = \frac{80}{0.92} = 86.96 \text{ W}$$

# B. Input diode current is maximum at $V_{inrms} = V_{ac(LL)}$

$$I_{inpk} = \frac{\sqrt{2} P_0}{\eta V_{ac(LL)}} = \frac{\sqrt{2} \times 80}{0.92 \times 85} = 1.447 A$$

#### C. Inductor design

1. Inductor peak current:

$$I_{Lpk} = 2I_{inpk} = 2 \times 1.447 = 2.894 A$$

2. Inductor value, for follower boost operation,  $V_o = V_{omin}$ :

$$\begin{split} L_{p} &= \frac{2 \times t_{total} \bigg( \frac{v_{omin}}{\sqrt{2}} - V_{ac(LL)} \bigg)}{V_{omin} I_{Lpk}} \\ &= \frac{2 \times 40 \times 10^{-6} \bigg( \frac{140}{\sqrt{2}} - 85 \bigg) 85}{140 \times 2.894} = 0.235 \, \mu \text{H} \end{split}$$

Let the switching cycle  $t = 40 \mu s$  for universal input (85 to 265  $V_{ac}$ ) operation.

3. The number of turns required for a selected core size and material is:

$$N_P = \frac{L_P I_{Lpk}^{106}}{B_{max} A_e} =$$

$$\frac{0.235 \times 10^{-3} \times 2.894 \times 10^{6}}{0.3 \times 32.1} = 70.6 \text{ turns} \approx 71 \text{ turns}$$

Using EPCOS E 20/10/6, N67 material,  $B_{max}$  =0.3 T and  $A_e$  = 32.1 mm<sup>2</sup>.

4. The required air gap to achieve the correct inductance and storage is:

$$\begin{split} I_{gap} &= \frac{4\pi 10^{-7} N_{\,p}^2 A_e}{L_p} \\ &= \frac{4\pi \times 10^{-7} \times 71^2 \times 32.1 \times 10^{-6}}{0.235 \times 10^{-3}} \\ &= 0.856 \, \text{mm} \end{split}$$

5. Design of Auxiliary Winding

$$N_{aux} = \frac{V_{aux}N_{P}}{\left(V_{O} - V_{ac(HL)}\right)} = \frac{14 \times 71}{(400 - 265)}$$

= 7.4 turns  $\approx$  8 turns

Round up to 8 turns to make sure enough voltage at the auxiliary winding.

#### D. To determine the output capacitor

As rule of thumb, for 80 W output, start with 100  $\mu F\!\!\!\!/ ,$  450 V capacitor.

#### E. Calculation of MOSFET conduction losses

A 4A, 500 V MOSFET, MTP4N50E is chosen. The on resistance,  $R_{ds(on)} \approx 1.75~\Omega@100^{\circ}\text{C}$ . Therefore, maximum power MOSFET conduction losses is:

$$\begin{split} P_{(on)max} &\approx \frac{1}{6} \times R_{ds(on)} \times I_{Lpk}^{2} \ 1 - \frac{1.2 \times V_{ac(LL)}}{V_{omin}} \\ &= \frac{1}{6} \times 1.75 \times 2.894^{2} \ 1 - \frac{1.2 \times 85}{140} = 0.66 \ W \end{split}$$

#### F. Design of regulation and overvoltage protection circuit

The output voltage regulation level can be adjusted by R<sub>0</sub>,

$$R_{O} \approx \frac{V_{O}}{200 \, \mu A} = \frac{400}{200 \, \mu A} = 2 \, M\Omega$$

Use two  $1M\Omega$  resistors in series.

#### G. Designing the Oscillator Circuit

For follower boost operation, C<sub>T</sub> is chosen with below equation:

$$C_T \ge \frac{2 \times K_{OSC} \times L_P \times P_{in} \times V_0^2}{V_{ac(LL)}^2 \times R_0^2} - C_{int} =$$

$$\frac{2 \times 6400 \times 0.234 \text{mH} \times 86.96 \times 140^2}{85^2 \times 2 \ \text{M}\Omega^2} - \ \text{15pF} = \ \text{162 pF}$$

Use 150 pF capacitor.

Figure 6. Theoretical  $V_o$  versus  $V_{ac}$  with  $C_T = 150pF$

#### H. Design of the Current Sense Circuit

Choose  $R_{cs} = 0.68 \Omega$

1. So the current sense resistor losses, P<sub>Rcs</sub>:

$$P_{RCS} = \frac{1}{6} \times R_{CS} \times I_{Lpk}^{2}$$

$$= \frac{1}{6} \times 0.68 \times 2.894^{2} = 0.949 \text{ W}$$

2. Overcurrent protection resistor,  $R_{OCP}$  can be determined with below equation:

$$R_{OCP} = \frac{R_{CS} \times I_{Lpk}}{I_{OCP}} = \frac{0.68 \times 2.894}{205 \,\mu A} = 9600 \,\Omega$$

Use  $10000~\Omega$  resistor. This provide current limit at 3.01 A versus calculated value of  $I_{Lpk}=2.894~A$ .

80 W, Universal Input, Follower Boost Variable Output Voltage Regulation Level Operation Power Factor Correction Circuit Part List

| Index | Value         | Comment                              | Index | Value       | Comment              |

|-------|---------------|--------------------------------------|-------|-------------|----------------------|

| C1    | 0.63 μF@600 V | Filtering Capacitor                  | R6    | 22 Ω@0.25 W | Aux Winding Resistor |

| C2    | 680 nF        | Pin 2 V <sub>control</sub> Capacitor | R7    | 100 KΩ@2 W  | Start-up Resistor    |

| C3    | 150 pF        | Pin 3 Oscillator Capacitor           | D1    | 1N5406      | Input Diode          |

| C4    | 100 μF@50 V   | Aux Capacitor, E-Cap                 | D2    | 1N5406      | Input Diode          |

| C5    | 100 μF@450 V  | Output Capacitor, E-Cap              | D3    | 1N5406      | Input Diode          |

| C6    | 1 nF@50 V     | Feedback Filtering Capacitor         | D4    | 1N5406      | Input Diode          |

| R1    | 0.68 Ω@2 W    | Current Sense Resistor               | D5    | 1N4937      | Aux Winding Diode    |

| R2    | 10 KΩ@0.25 W  | OCP Sensing Resistor                 | D6    | MUR460      | Boost Diode          |

| R3    | 1 MΩ@0.25 W   | Feedback Resistor                    | D7    | 1N5245      | Aux 15 V Zener Diode |

| R4    | 1 MΩ@0.25 W   | Feedback Resistor                    | Q1    | MTP4N50E    | Power MOSFET         |

| R5    | 10 Ω@0.25 W   | Gate Resistor                        | L1*   | 0.235 mH    | Inductor             |

<sup>\*</sup> E 20/10/6, N67 Material from EPCOS

Primary – 71 turns of # 23 AWG, Secondary – 8 turns of # 23 AWG. Gap length 0.865 mm total for a primary inductance  $L_P$  of 0.235 mH.

Figure 7. 80 W Universal Input, Follower Boost Variable Output Voltage Regulation Level Operation Power Factor Correction Circuit

# Design Table for Universal Input, Follower Boost Variable Output Voltage Regulation Level Operation Power Factor Correction

| Po               | 25       | 50    | 75       | 100   | 125    | 150      | 200   | (Watts)       |

|------------------|----------|-------|----------|-------|--------|----------|-------|---------------|

| L <sub>P</sub>   | 0.752    | 376   | 0.251    | 0.188 | 0.150  | 0.102    | 0.094 | (mH)          |

| Co               | 33       | 68    | 100      | 100   | 150    | 150      | 220   | (μ <b>F</b> ) |

| R <sub>CS</sub>  | 2        | 1     | 0.68     | 0.5   | 0.39   | 0.33     | 0.25  | Ω             |

| R <sub>OCP</sub> | 10000    | 10000 | 10000    | 9100  | 9100   | 9100     | 9100  | Ω             |

| C <sub>in</sub>  | 0.22     | 0.63  | 0.63     | 1.0   | 1.0    | 1.0      | 1.0   | (μ <b>F</b> ) |

| СТ               | 0.162    | 0.162 | 0.162    | 0.162 | 0.162  | 0.162    | 0.162 | (nF)          |

| Q                | MTD2N50E |       | MTP4N50E |       |        | MTP8N50E |       |               |

| D <sub>out</sub> | MUF      | R160  | MUR460   |       |        |          |       |               |

| D <sub>in</sub>  | 1N4007   |       | 1N5      | 406   | 1N5406 |          |       | ·             |

### **Notes**

Greenline is a trademark of Semiconductor Components Industries, LLC.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone:** 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax:** 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

**JAPAN**: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.