# ISO-CMOS ST-BUS™ FAMILY MT8979 CEPT PCM 30/CRC-4 Framer & Interface

**Features**

Single chip primary rate 2048 kbit/s CEPT transceiver with CRC-4 option

- Meets CCITT Recommendation G.704

- Selectable HDB3 or AMI line code

- Tx and Rx frame and multiframe synchronization signals

- Two frame elastic buffer with 32 μsec jitter buffer

- · Frame alignment and CRC error counters

- Insertion and detection of A, B, C, D signalling bits with optional debounce

- On-chip attenuation ROM with option for ADI codecs

- · Per channel, overall and remote loop around

- ST-BUS compatible

### **Applications**

- · Primary rate ISDN network nodes

- Multiplexing equipment

- · Private network: PBX to PBX links

- · High speed computer to computer links

ISSUE 8 March 1997

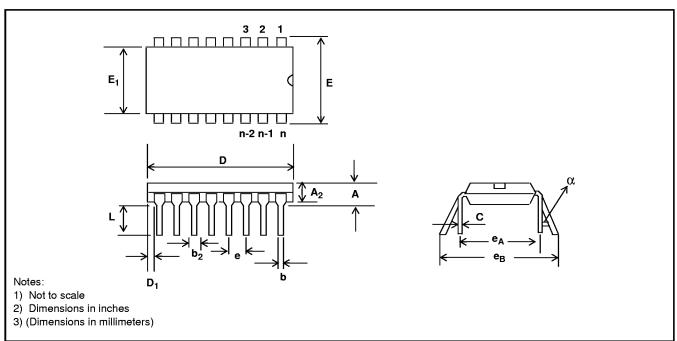

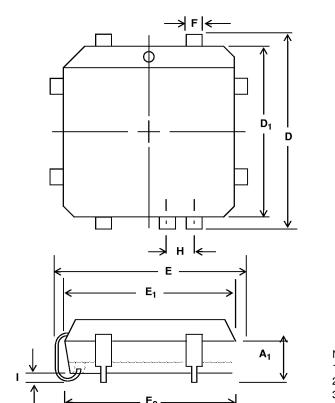

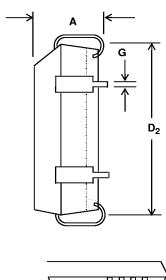

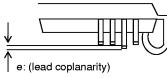

#### **Ordering Information**

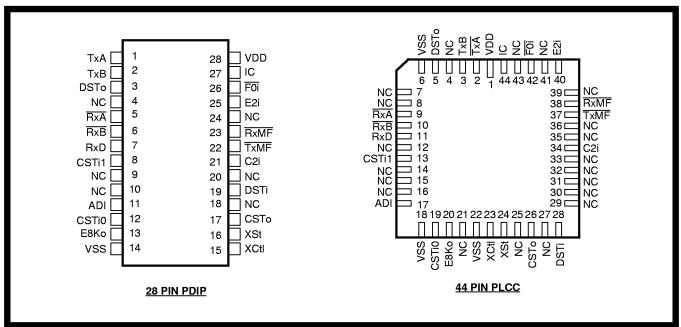

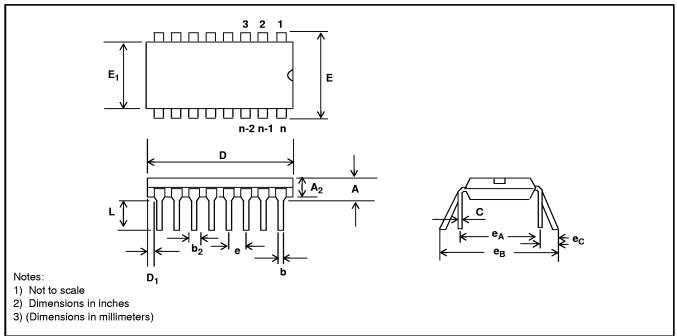

MT8979AE 28 Pin Plastic DIP MT8979AP 44 Pin PLCC -40° to 85°C

### **Description**

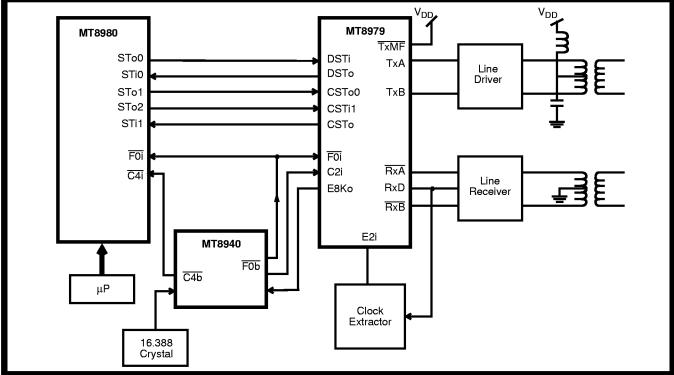

The MT8979 is a single chip CEPT digital trunk transceiver that meets the requirements of CCITT Recommendation G.704 for digital multiplex equipment.

The MT8979 is fabricated in Mitel's low power ISO-CMOS technology.

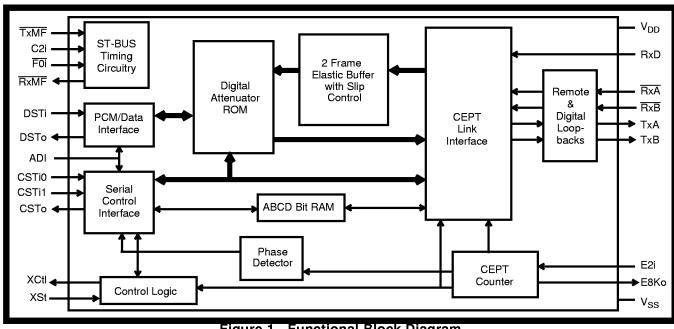

Figure 1 - Functional Block Diagram

Figure 2 - Pin Connections

# **Pin Description**

| Pi  | in#  | Name  | Description                                                                                                                                                                                                                                                                                        |

|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP | PLCC | Name  | Bescription                                                                                                                                                                                                                                                                                        |

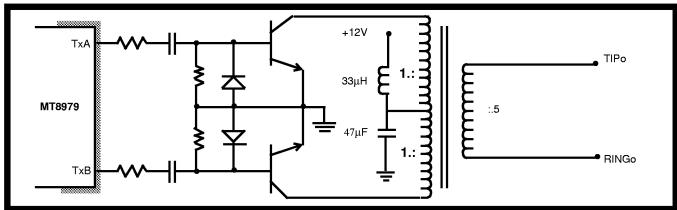

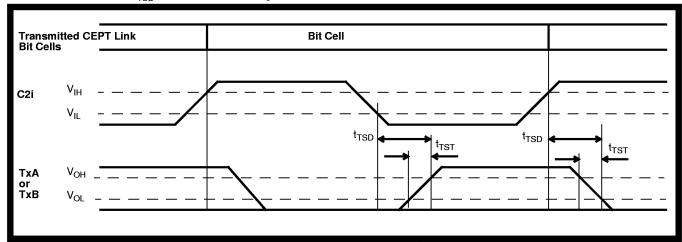

| 1   | 2    | TxA   | <b>Transmit A (Output):</b> A split phase unipolar signal suitable for use with TxB and an external line driver and transformer to construct the bipolar line signal.                                                                                                                              |

| 2   | 3    | ТхВ   | Transmit B (Output:) A split phase unipolar signal suitable for use with TxA and an external line driver and transformer to construct the bipolar line signal.                                                                                                                                     |

| 3   | 5    | DSTo  | Data ST-BUS (Output): A 2048 kbit/s serial output stream which contains the 30 PCM or data channels received from the CEPT line.                                                                                                                                                                   |

| 4   | 4    | NC    | No Connection.                                                                                                                                                                                                                                                                                     |

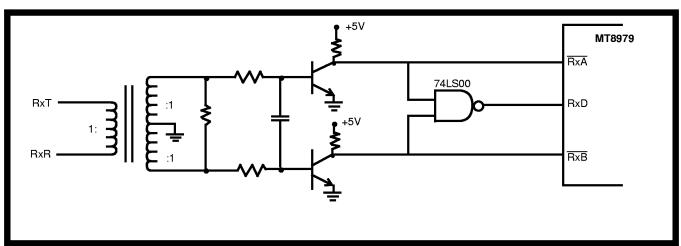

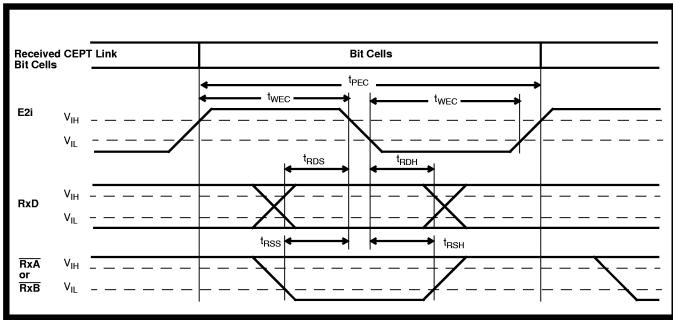

| 5   | 9    | RxA   | Receive A (Input): Received split phase unipolar signal decoded from a bipolar line receiver.                                                                                                                                                                                                      |

| 6   | 10   | RxB   | Receive B (Input): Received split phase unipolar signal decoded from a bipolar line receiver.                                                                                                                                                                                                      |

| 7   | 11   | RxD   | Received Data (Input): Input of the unipolar data generated from the line receiver. This data may be NRZ or RZ.                                                                                                                                                                                    |

| 8   | 13   | CSTi1 | Control ST-BUS Input #1: A 2048 kbit/s stream that contains channel associated signalling, frame alignment and diagnostic functions.                                                                                                                                                               |

| 9   |      | NC    | No Connection.                                                                                                                                                                                                                                                                                     |

| 10  |      | NC    | No Connection.                                                                                                                                                                                                                                                                                     |

| 11  | 17   | ADI   | Alternate Digit Inversion (Input): If this input is high, the CEPT timeslots which are specified on CSTi0 as voice channels are ADI coded and decoded. When this bit is low it disables ADI coding for all channels. This feature allows either ADI or non-ADI codecs to be used on DSTi and DSTo. |

| 12  | 19   | CSTi0 | Control ST-BUS Input #0: A 2048 kbit/s stream that contains 30 per channel control words and two Master Control Words.                                                                                                                                                                             |

# **Pin Description (Continued)**

| Pi  | n #        | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP | PLCC       | Hame            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

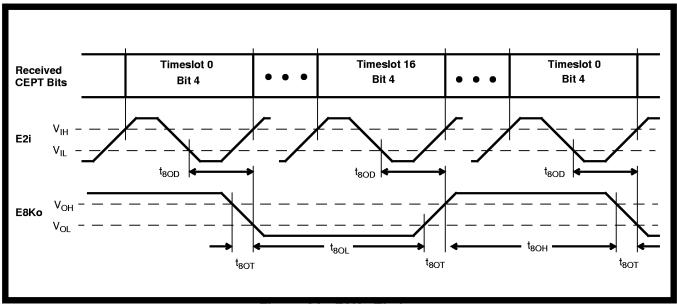

| 13  | 20         | E8Ko            | Extracted 8 kHz Clock (Output): An 8 kHz output generated by dividing the extracted 2048 kHz clock by 256 and aligning it with the received CEPT frame. The 8 kHz signal can be used for synchronizing the system clock to the extracted 2048 kHz clock. Only valid when device achieves synchronization (goes low during a loss of signal or a loss of basic frame synchronization condition).  E8Ko goes high impedance when 8kHzSEL = 0 in MCW2. |

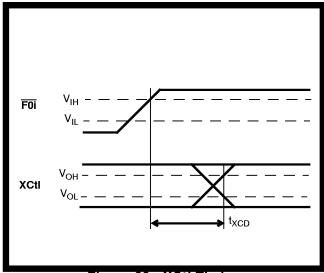

| 15  | 23         | XCtI            | <b>External Control (Output):</b> An uncommitted external output pin which is set or reset via bit 1 in Master Control Word 2 on CSTi0. The state of XCtl is updated once per frame.                                                                                                                                                                                                                                                                |

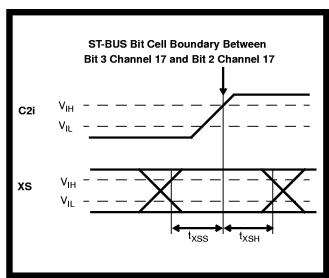

| 16  | 24         | XSt             | <b>External Status</b> : The state of this pin is sampled once per frame and the status is reported in bit 1 of the Master Status Word 1 on CSTo.                                                                                                                                                                                                                                                                                                   |

| 17  | 26         | CSTo            | Control ST-BUS Output: A 2048 kbit/s serial control stream which provides the 16 signalling words, two Master Status Words, Phase Status Word and CRC Error Count.                                                                                                                                                                                                                                                                                  |

| 18  |            | NC              | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 19  | 28         | DSTi            | <b>Data ST-BUS Input</b> : This pin accepts a 2048 kbit/s serial stream which contains the 30 PCM or data channels to be transmitted on the CEPT trunk.                                                                                                                                                                                                                                                                                             |

| 20  |            | NC              | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

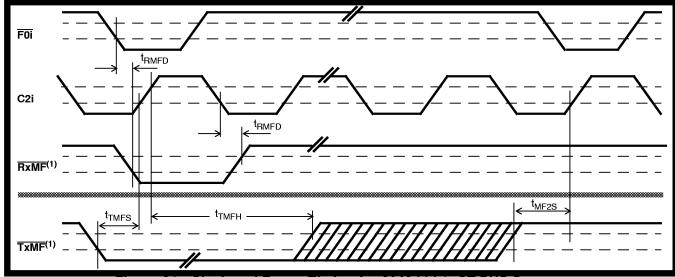

| 21  | 34         | C2i             | <b>2048 kbit/s System Clock (Input)</b> : The master clock for the ST-BUS section of the chip. All data on the ST-BUS is clocked in on the falling edge of the C2i and output on the rising edge. The falling edge of C2i is also used to clock out data on the CEPT transmit link.                                                                                                                                                                 |

| 22  | 37         | TxMF            | <b>Transmit Multiframe Boundary (Input)</b> : This input can be used to set the channel associated and CRC transmitted multiframe boundary (clear the frame counters). The device will generate its own multiframe if this pin is held high.                                                                                                                                                                                                        |

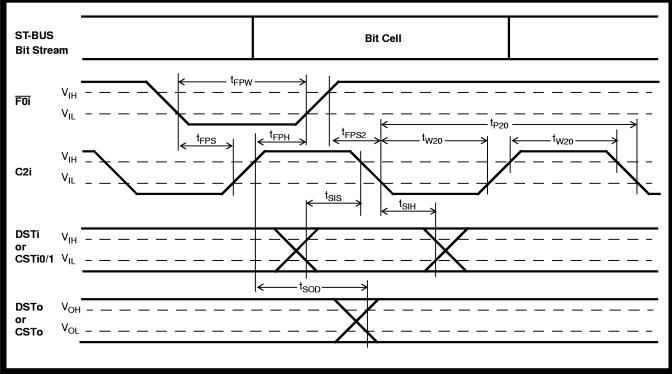

| 23  | 38         | RxMF            | Received Multiframe Boundary (Output): An output pulse delimiting the received Multiframe boundary. (This multiframe is not related to the received CRC multiframe.) The next frame output on the data stream (DSTo) is received as frame 0 on the CEPT link.                                                                                                                                                                                       |

| 24  |            | NC              | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 25  | 40         | E2i             | <b>Extracted 2048 kHz Clock (Input)</b> : The falling edge of this 2048 kHz clock is used to latch the received data (RxD). This clock input must be derived from the CEPT received data and must have its falling edge aligned with the center of the received bit (RxD).                                                                                                                                                                          |

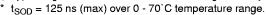

| 26  | 42         | F0i             | Frame Pulse Input: The ST-BUS frame synchronization signal which defines the beginning of the 32 channel frame.                                                                                                                                                                                                                                                                                                                                     |

| 27  | 44         | IC              | Internal Connection: Tie to V <sub>SS</sub> (Ground) for normal operation.                                                                                                                                                                                                                                                                                                                                                                          |

| 28  | 1          | V <sub>DD</sub> | Positive Power Supply Input (+5 Volts).                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14  | 6,8,<br>22 | V <sub>SS</sub> | Negative Power Supply Input (Ground).                                                                                                                                                                                                                                                                                                                                                                                                               |

# **Functional Description**

The MT8979 is a CEPT trunk digital link interface conforming to CCITT Recommendation G.704 for PCM 30 and I.431 for ISDN. It includes features such as: insertion and detection of synchronization patterns, optional cyclical redundancy check and far end error performance reporting, HDB3 decoding and optional coding, channel associated or common channel signalling, programmable digital attenuation and a two frame received elastic buffer. The MT8979 can also monitor several conditions on the CEPT digital trunk, which include, frame and multiframe synchronization, received all 1's alarms, data slips as well as framing and CRC errors, both near and far end.

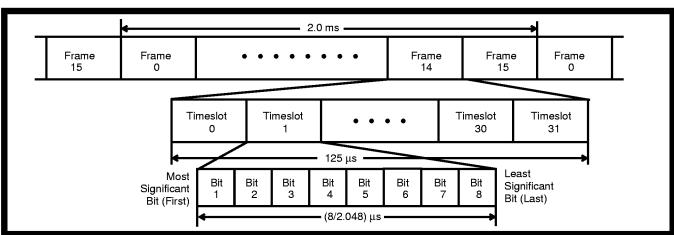

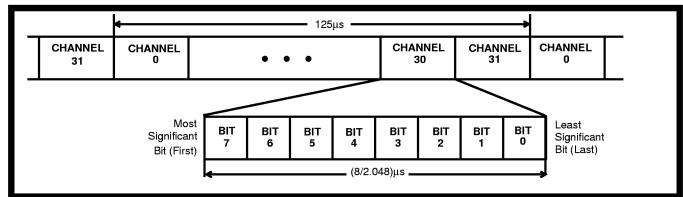

The system interface to the MT8979 is a TDM bus structure that operates at 2048 kbit/s known as the ST-BUS. This serial stream is divided into 125  $\mu$ s frames that are made up of 32 x 8 bit channels.

The line interface to the MT8979 consists of split phase unipolar inputs and outputs which are supplied from/to a bipolar line receiver/driver, respectively.

#### **CEPT Interface**

The CEPT frame format consists of 32, 8 bit timeslots. Of the 32 timeslots in a frame, 30 are defined as information channels, timeslots 1-15 and 17-31 which correspond to telephone channels 1-30. An additional voice/data channel may be obtained by placing the device in common channel signalling mode. This allows use of timeslot 16 for 64 kbit/s common channel signalling.

Synchronization is included within the CEPT bit stream in the form of a bit pattern inserted into timeslot 0. The contents of timeslot 0 alternate

between the frame alignment pattern and the non-frame alignment pattern as described in Figure 4. Bit 1 of the frame alignment and non-frame alignment bytes have provisions for additional protection against false synchronization or enhanced error monitoring. This is described in more detail in the following section.

In order to accomplish multiframe synchronization, a 16 frame multiframe is defined by sending four zeros in the high order quartet of timeslot 16 frame 0, i.e., once every 16 frames (see Figure 5). The CEPT format has four signalling bits, A, B, C and D. Signalling bits for all 30 information channels are transmitted in timeslot 16 of frames 1 to 15. These timeslots are subdivided into two quartets (see Table 6).

#### Cyclic Redundancy Check (CRC)

An optional cyclic redundancy check (CRC) has been incorporated within CEPT bit stream to provide additional protection against simulation of the frame alignment signal, and/or where there is a need for an enhanced error monitoring capability. process treats the binary string of ones and zeros contained in a submultiframe (with CRC bits set to binary zero) as a single long binary number. This string of data is first multiplied by x4 then divided by the generating polynomial  $x^4+x+1$ . This division process takes place at both the transmitter and receiver end of the link. The remainder calculated at the receiver is compared to the one received with the data over the link. If they are the same, it is of high probability that the previous submultiframe was received error free.

The CRC procedure is based on a 16 frame multiframe, which is divided into two 8 frame submultiframes (SMF). The frames which contain the frame alignment pattern contain the CRC bits,  $C_1$  to  $C_4$  respectively, in the bit 1 position. The frames

Figure 3 - CEPT Link Frame & Multiframe Format

which contain the non-frame alignment pattern contain within the bit 1 position, a 6 bit CRC multiframe alignment signal and two spare bits (in frames 13 and 15), which are used for CRC error performance reporting (refer to Figure 6). During the CRC encoding procedure the CRC bit positions are initially set at zero. The remainder of the calculation is stored and inserted into the respective CRC bits of the next SMF. The decoding process repeats the multiplication division process and compares the remainder with the CRC bits received in the next SMF.

The two spare bits (denoted Si1 and Si2 in Figure 6) in the CRC-4 multiframe are used to monitor far-end error performance. The results of the CRC-4 comparisons for the previously received SMFII and SMFI are encoded and transmitted back to the far end in the Si bits (refer to Table 1).

#### **ST-BUS Interface**

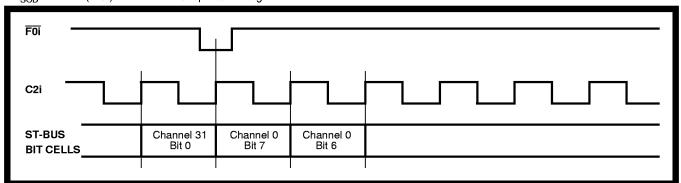

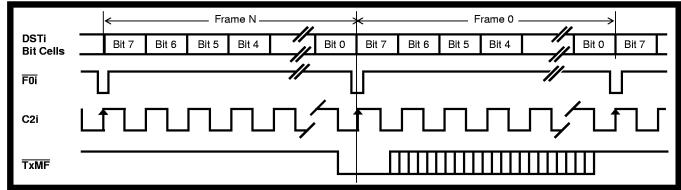

The ST-BUS is a synchronous time division multiplexed serial bus with data streams operating at 2048 kbit/s and configured as 32, 64 kbit/s channels (refer Figure 7). Synchronization of the data transfer is provided from a frame pulse, which identifies the frame boundaries and repeats at an 8 kHz rate. Figure 17 shows how the frame pulse (F0i) defines the ST-BUS frame boundaries. All data is clocked into the device on the falling edge of the 2048 kbit/s clock (C2i), while data is clocked out on the rising edge of the 2048 kbit/s clock at the start of the bit cell.

| Si1 bit<br>(frame<br>13) | Si2 bit<br>(frame<br>15) | Meaning                                                              |

|--------------------------|--------------------------|----------------------------------------------------------------------|

| 1                        | 1                        | CRC results for both SMFI, II are error free.                        |

| 1                        | 0                        | CRC result for SMFII is in error. CRC result for SMFI is error free. |

| 0                        | 1                        | CRC result for SMFII is error free. CRC result for SMFI is in error. |

| 0                        | 0                        | CRC results for both SMFI, II are in error.                          |

Table 1. Coding of Spare Bits Si1 and Si2

#### Data Input (DSTi)

The MT8979 receives information channels on the DSTi pin. Of the 32 available channels on this serial input, 30 are defined as information channels. They are channels 1-15 and 17-31. These 30 timeslots are the 30 telephone channels of the CEPT format numbered 1-15 and 16-30. Timeslot 0 and 16 are unused to allow the synchronization and signalling information to be inserted, from the (CSTi0 Control Streams and CSTi1). relationship between the input and output ST-BUS stream and the CEPT line is illustrated in Figures 8 to 12. In common channel signalling mode timeslot 16 becomes an active channel. In this mode channel 16 on DSTi is transmitted on timeslot 16 of the CEPT link unaltered. This mode is activated by bit 5 of channel 31 of CSTi0.

|                                                      |                                                     |   | Bit Numl                                               | ber               |                   |                   |                   |                   |

|------------------------------------------------------|-----------------------------------------------------|---|--------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

|                                                      | 1                                                   | 2 | 3                                                      | 4                 | 5                 | 6                 | 7                 | 8                 |

| Timeslot 0 containing the frame alignment signal     | Reserved for<br>International<br>use <sup>(1)</sup> | 0 | 0                                                      | 1                 | 1                 | 0                 | 1                 | 1                 |

| Timeslot 0 containing the non-frame alignment signal | Reserved for<br>International<br>use <sup>(2)</sup> | 1 | Alarm indication to the remote PCM multiplex equipment | See<br>Note<br>#3 | See<br>Note<br>#3 | See<br>Note<br>#3 | See<br>Note<br>#3 | See<br>Note<br>#3 |

Figure 4 - Allocation of Bits in Timeslot 0 of the CEPT Link

Note 1: With CRC active, this bit is ignored.

Note 2: With SiMUX active, this bit transmits SMF CRC results in frames 13 and 15

Note 3: Reserved for National use

| Timeslot 16 | of frame 0 | Timeslot 16                                             | of frame 1                                                |       | Timeslot 16                                               | of frame 15                                               |

|-------------|------------|---------------------------------------------------------|-----------------------------------------------------------|-------|-----------------------------------------------------------|-----------------------------------------------------------|

| 0000        | XYXX       | ABCD bits for<br>telephone<br>channel 1<br>(timeslot 1) | ABCD bits for<br>telephone<br>channel 16<br>(timeslot 17) | • • • | ABCD bits for<br>telephone<br>channel 15<br>(timeslot 15) | ABCD bits for<br>telephone<br>channel 30<br>(timeslot 31) |

Figure 5 - Allocation of Bits in Timeslot 16 of the CEPT Link

#### Control Input 0 (CSTi0)

All the necessary control and signalling information is input through the two control streams. Control ST-BUS input number 0 (CSTi0) contains the control information that is associated with each information channel. Each control channel contains the per channel digital attenuation information, the individual loopback control bit, and the voice or data channel identifier, see Table 2. When a channel is in data mode (B7 is high) the digital attenuation and Alternate Digit Inversion are disabled. It should be noted that the control word for a given information channel is input one timeslot early, i.e., channel 0 of CSTi0 controls channel 1 of DSTi. Channels 15 and 31 of CSTi0 contain Master Control Words 1 and 2, which are used to set up the interface feature as seen by the respective bit functions of Tables 3 and

#### Control Input 1 (CSTi1)

Control ST-BUS input stream number 1 (CSTi1) contains the synchronization information and the A, B, C & D signalling bits for insertion into timeslot 16 of the CEPT stream (refer to Tables 5 to 8). Timeslot 0 contains the four zeros of the multiframe alignment signal plus the XYXX bits (see Figure 5). Channels 1 to 15 of CSTi1 contain the A, B, C & D signalling bits as defined by the CEPT format (see Figure 5), i.e., channel 1 of CSTi1 contains the A,B,C & D bits for

DSTi timeslots 1 and 17. Channel 16 contains the frame alignment signal, and channel 17 contains the non-frame alignment signal (see Figure 4). Channel 18 contains the Master Control Word 3 (see Table 9). Figure 11 shows the relationship between the control stream (CSTi1) and the CEPT stream.

#### **Control Output (CSTo)**

Control ST-BUS output (CSTo) contains the multiframe signal from timeslot 16 of frame 0 (see Table 10). Signalling bits A, B, C & D for each CEPT channel are sourced from timeslot 16 of frames 1-15 and are output in channels 1-15 on CSTo, as shown in Table 11. The frame alignment signal and nonframe alignment signal, received from timeslot 0 of alternate frames, are output in timeslots 16 and 17 as shown in Tables 12 and 13.

Channel 18 contains a Master Status Word, which provides to the user information needed to determine the operating condition of the CEPT interface i.e., frame synchronization, multiframe synchronization, frame alignment byte errors, slips, alarms, and the logic of the external status pin (see Table 14). Figure 12, shows the relationship between the control stream channels and the CEPT signalling channels in the multiframe. The ERR bit in the Master Status word is an indicator of the number of errored frame alignment bytes that have been received in alternate timeslot zero. The time interval between toggles of

| Multiple Frame | Frame Type                 | CRC     |                    |   | -                | Timesl            | ot Zer            | 0                 |                   |                   |

|----------------|----------------------------|---------|--------------------|---|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Component      | Traine Type                | Frame # | 1                  | 2 | 3                | 4                 | 5                 | 6                 | 7                 | 8                 |

|                | Frame Alignment Signal     | 0       | C <sub>1</sub>     | 0 | 0                | 1                 | 1                 | 0                 | 1                 | 1                 |

|                | Non-Frame Alignment Signal | 1       | 0                  | 1 | A <sup>(1)</sup> | Sn <sup>(2)</sup> |

| S              | Frame Alignment Signal     | 2       | $C_2$              | 0 | 0                | 1                 | 1                 | 0                 | 1                 | 1                 |

| М              | Non-Frame Alignment Signal | 3       | 0                  | 1 | A <sup>(1)</sup> | Sn <sup>(2)</sup> |

| F              | Frame Alignment Signal     | 4       | $C_3$              | 0 | 0                | 1                 | 1                 | 0                 | 1                 | 1                 |

|                | Non-Frame Alignment Signal | 5       | 1                  | 1 | A <sup>(1)</sup> | Sn <sup>(2)</sup> |

| I              | Frame Alignment Signal     | 6       | C <sub>4</sub>     | 0 | 0                | 1                 | 1                 | 0                 | 1                 | 1                 |

|                | Non-Frame Alignment Signal | 7       | 0                  | 1 | A <sup>(1)</sup> | Sn <sup>(2)</sup> |

|                | Frame Alignment Signal     | 8       | C <sub>1</sub>     | 0 | 0                | 1                 | 1                 | 0                 | 1                 | 1                 |

| S              | Non-Frame Alignment Signal | 9       | 1                  | 1 | A <sup>(1)</sup> | Sn <sup>(2)</sup> |

| М              | Frame Alignment Signal     | 10      | C <sub>2</sub>     | 0 | 0                | 1                 | 1                 | 0                 | 1                 | 1                 |

| F              | Non-Frame Alignment Signal | 11      | 1                  | 1 | A <sup>(1)</sup> | Sn <sup>(2)</sup> |

|                | Frame Alignment Signal     | 12      | C <sub>3</sub>     | 0 | 0                | 1                 | 1                 | 0                 | 1                 | 1                 |

| I              | Non-Frame Alignment Signal | 13      | Si1 <sup>(3)</sup> | 1 | A <sup>(1)</sup> | Sn <sup>(2)</sup> |

| I              | Frame Alignment Signal     | 14      | C <sub>4</sub>     | 0 | 0                | 1                 | 1                 | 0                 | 1                 | 1                 |

|                | Non-Frame Alignment Signal | 15      | Si2 <sup>(3)</sup> | 1 | A <sup>(1)</sup> | Sn <sup>(2)</sup> |

Figure 6 - CRC Bit Allocation and Submultiframing

Note 1: Remote Alarm. Keep at 0 for normal operation.

Note 2: Reserved for National use. Keep at 1 for normal operation.

Note 3: Used to monitor far-end CRC error performance.

Figure 7 - ST-BUS Stream Format

the ERR bit can be used to evaluate the bit error rate of the line according to the CCITT Recommendation G.732 (see section on Frame Alignment Error Counter).

Channel 19 contains the Phase Status Word (see Table 15), which can be used to determine the phase relationship between the ST-BUS frame pulse ( $\overline{\text{F0i}}$ ) and the rising edge of E8Ko. This information could be used to determine the long term trend of the received data rate, or to identify the direction of a slip.

Channel 20 contains the CRC error count (see Table 16). This counter will wrap around once terminal count is achieved (256 errors). If the maintenance option is selected (bit 3 of MCW3) the counter is reset once per second.

Channel 21 contains the Master Status Word 2 (see Table 17). This byte identifies the status of the CRC reframe and CRC sync. It also reports the Si bits received in timeslot 0 of frames 13 and 15 and the ninth and most significant bit  $(b_8)$  of the 9-bit Phase Status Word.

#### **Elastic Buffer**

The MT8979 has a two frame elastic buffer at the receiver, which absorbs the jitter and wander in the received signal. The received data is written into the elastic buffer with the extracted E2i (2048 kHz) clock and read out of the buffer on the ST-BUS side with the system C2i (2048 kHz) clock (e.g., PBX system clock). Under normal operating conditions, in a synchronous network, the system C2i clock is phase-locked to the extracted E2i clock. In this situation every write operation to the elastic buffer is followed by a read operation. Therefore, underflow or overflow of data in the elastic buffer will not occur.

If the system clock is not phase-locked to the extracted clock (e.g., lower quality link which is not

selected as the clock source for the PBX) then the data rate at which the data is being written into the device on the line side may differ from the rate at which it is being read out on the ST-BUS side.

When the clocks are not phase-locked, two situations can occur:

Case #1: If the data on the line side is being written in at a rate SLOWER than it is being read out on the ST-BUS side, the distance between the write pointer and the read pointer will begin to decrease over time. When the distance is less than two channels, the buffer will perform a controlled slip which will move the read pointers to a new location 34 channels away from the write pointer. This will result in the REPETITION of the received frame.

Case #2: If the data on the line side is being written in at a rate FASTER than it is being read out on the ST-BUS side, the distance between the write pointer and the read pointer will begin to increase over time. When the distance exceeds 42 channels, the elastic buffer will perform a controlled slip which will move the read pointer to a new location ten channels away from the write pointer. This will result in the LOSS of the last received frame.

Note that when the device performs a controlled slip, the ST-BUS address pointer is repositioned so that there is either a 10 channel or 34 channel delay between the input CEPT frame and the output ST-BUS frame. Since the buffer performs a controlled slip only if the delay exceeds 42 channels or is less than two channels, there is a minimum eight channel hysteresis built into the slip mechanism. The device can, therefore, absorb eight channels or 32.5µs of jitter in the received signal.

There is no loss of frame synchronization, multiframe synchronization or any errors in the signalling bits when the device performs a slip.

| Ti<br>nel# | 0 | - | 2 | 8 | 4 | 2 | 9 | 3 2 | 6 8 | 10 | 11  | 12 | 13 | 14 | 15 | 16  | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 52   7 | 26 2 | 27   2 | 28 29 | 08 6 | 31 |  |

|------------|---|---|---|---|---|---|---|-----|-----|----|-----|----|----|----|----|-----|----|----|----|----|----|----|----|----|--------|------|--------|-------|------|----|--|

| #          |   | - | 2 | က | 4 | 5 | 9 | 2   | 6   | 10 | = = | 12 | 13 | 14 | 15 | ccs | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 2   | 26 2 | 27 2   | 28 29 | 9 30 | 31 |  |

Figure 8 - Relationship between Input DSTi Channels and Transmitted CEPT Timeslots

| DSTi<br>Channel #  | 0 | - | 2 | 3 6 | 1 5 | 9 9 | 7 | 8  | 6 | 10 | 11 | 12 | 13 | 14 | 15 | 16  | 17 | 18 | 19 | 20 ; | 21   2 | 22 2  | 23 24 | 4 25 | 5 26 | 27 | 28 | 59 | 30 | 31 |

|--------------------|---|---|---|-----|-----|-----|---|----|---|----|----|----|----|----|----|-----|----|----|----|------|--------|-------|-------|------|------|----|----|----|----|----|

| CEPT<br>Timeslot # | 0 | - | 2 | 3   | 5   | 9 9 | 7 | 80 | 6 | 10 | 1  | 12 | 13 | 14 | 15 | SIG | 17 | 18 | 19 | 20 / | 21 2   | 22 23 | 3 24  | 4 25 | 5 26 | 27 | 28 | 53 | 30 | 31 |

Figure 9 - Relationship between Received CEPT Timeslots and Output DSTo Channels

| CSTi0<br>Channel #          | 0 | - | 2 | س | 4  | 5 6 | 6 7 | \ \ \ | 6 8 | 10 | 11 12 | 13 |    | 14 15 | 16 | 17 | 18    | 19 | 20 | 21 | 22 | 23 | 24   | 25 | 56 | 27 | 28 ' | 29 | 30 31 |

|-----------------------------|---|---|---|---|----|-----|-----|-------|-----|----|-------|----|----|-------|----|----|-------|----|----|----|----|----|------|----|----|----|------|----|-------|

| Device Control              |   |   |   |   |    |     |     |       |     |    |       |    |    | ပ     |    |    |       |    |    |    |    |    |      |    |    |    |      |    | C2    |

| CEPT Channel # Control Word | - | 2 | ო | 4 | ני | 9   | 2 8 | 6     | 10  | 11 | 12 13 | 14 | 15 |       | 17 | 18 | 18 19 | 20 | 21 | 22 | 23 | 24 | 25 ; | 26 | 27 | 82 | 53   | 30 | 31    |

Figure 10 - Relationship between Input CSTi0 Channels and Controlled CEPT Timeslots

| <u> -</u>          | *              |                |           |

|--------------------|----------------|----------------|-----------|

| 0 31               | Ė              |                |           |

| 9 30               | *              |                |           |

| 29                 | *              |                |           |

| 28                 | *              |                |           |

| 27                 | *              |                |           |

| 26                 | *              |                |           |

| 25                 | *              |                |           |

| 24                 | *              |                |           |

| 23                 | *              |                |           |

| 22                 | *              |                |           |

| 21                 | *              |                |           |

| 20                 | *              |                |           |

| 19                 | *              |                |           |

| 18                 | ຮ              |                |           |

| 17                 |                | z              | 0         |

| 16                 |                | A              | 0         |

| 15                 |                | 15             | 16        |

| 4                  |                | 41             | 16        |

| 13                 |                | 5              | 16        |

| 12                 |                | 12             | 16        |

| 1                  |                | 11             | 16        |

| 10                 |                | 10             | 16        |

| 6                  |                | 6              | 16        |

| 8                  |                | 8              | 16        |

| 7                  |                | 7              | 16        |

| 9                  |                | 9              | 16        |

| 5                  |                | 5              | 16        |

| 4                  |                | 4              | 16        |

| ဗ                  |                | 3              | 16        |

| 2                  |                | 2              | 16        |

| -                  |                | -              | 16        |

| 0                  |                | 0              | 16        |

| CSTi1<br>Channel # | Device Control | CEPT<br>FRAME# | CHANNEL # |

Figure 11 - Relationship between Input CSTi1 Channels and Transmitted CEPT Frames

| 31                | *             |                               |

|-------------------|---------------|-------------------------------|

| 30                | *             |                               |

| 59                | *             |                               |

| 28 2              | *             |                               |

| 27   2            | *             |                               |

| 26 2              | *             |                               |

| 25   2            |               |                               |

| 24 2              | _             |                               |

| 23 2              | _             |                               |

| 22   2            | *             |                               |

|                   |               |                               |

| 0 21              | 3 S4          |                               |

| 9 20              | 2 83          |                               |

| 3 19              | 1 S2          |                               |

| 7 18              | S1            |                               |

| 17                |               | ZO                            |

| 16                |               | 4 O                           |

| . 15              |               |                               |

| 41                |               | 41 91                         |

| 13                |               | 13                            |

| 12                |               | 12                            |

| 11                |               | 11                            |

| 10                |               | 10                            |

| 6                 |               | 9                             |

| 8                 |               | 8                             |

| 2                 |               | 7                             |

| 9                 |               | 6<br>16                       |

| 5                 |               | 5<br>16                       |

| 4                 |               | 4<br>16                       |

| က                 |               | 3<br>16                       |

| 2                 |               | 2<br>16                       |

| -                 |               | 1                             |

| 0                 |               | 0<br>16                       |

| CSTo<br>Channel # | Device Status | CEPT<br>FRAME #<br>TIMESLOT # |

Figure 12- Relationship between Received CEPT Frames and Output CSTo Channels

| Denotes Unused Channel (CSTo output is not put in high impedance     Denotes Crams Alignment Frame | ince state)  |            |

|----------------------------------------------------------------------------------------------------|--------------|------------|

| - *Denotes Unused Channel (CSTo output is not put in h                                             | igh impeda   |            |

| - *Denotes Unused Channel (CSTo output is r                                                        | not put in h |            |

| - *Denotes Unused Channel (CSTo                                                                    | output is r  |            |

| - *Denotes Unused Cha                                                                              | nnel (CSTo   | 40000      |

| - *Denotes U                                                                                       | nused Cha    | V 0 00 0 1 |

|                                                                                                    | In Setor     | 100+00     |

-CCS Denotes Signalling Channel if Common Channel Signalling Mode Selected

-S1 Denotes Master Status Word 1 (MSW1)

-S2 Denotes Phase Status Word (PSW)

-S3 Denotes CRC Error Count

-S4 Denotes Master Status Word 2 (MSW2)

<sup>A Denotes Frame-Alignment Frame

N Denotes Non Frame-Alignment Frame

C1, C2, C3 Denotes Master Control Words 1,2,3

SIG Denotes Signalling Channel</sup>

# Frame Alignment Error Counter

The MT8979 provides an indication of the bit error rate found on the link as required by CCITT Recommendation G.703. The ERR bit (Bit 5 of MSW1) is used to count the number of errors found in the frame alignment signal and this can be used to estimate the bit error rate. The ERR bit changes state when 16 errors have been detected in the frame alignment signal. This bit can not change state more than once every 128 ms, placing an upper limit on the detectable error rate at approximately 10<sup>-3</sup>. The following formula can be used to calculate the BER:

BER= 16\* number of times ERR bit toggles 7 \* 4000 \* elapsed time in seconds

#### where:

- 7 is the number of bits in the frame alignment signal (0011011).

- 16 is the number of errored frame alignment signals counted between changes of state of the ERR bit.

- 4000 is the number of frame alignment signals in a one second interval.

This formula provides a good approximation of the BER given the following assumptions:

- 1. The bit errors are uniformly distributed on the line. In other words, every bit in every channel is equally likely to get an error.

- 2. The errors that occur in channel 0 are bit errors. If the first assumption holds and the bit error rate is reasonable, (below 10<sup>-3</sup>) then the probability of two or more errors in seven bits is very low.

#### Attenuation ROM

All transmit and receive data in the MT8979 is passed through the digital attenuation ROM according to the values set on bits 5 - 0 of data channels in the control stream (CSTi0). Data can be attenuated on a per-channel basis from 1 to -6 dB for both Tx and Rx data (refer Table 2).

Digital attenuation is applied on a per-channel basis to the data found one channel after the control information stored in the control channel CSTi0, i.e., control stream 0 channel 4 contains the attenuation setting for data stream (DSTo) channel 5.

#### Signalling Bit RAM

The A, B, C, & D Bit RAM is used to retain the status of the per-channel signalling bits so that they may be multiplexed into the Control Output Stream (CSTo). This signalling information is only valid when the module is synchronized to the received data stream. If synchronization is lost, the status of the signalling bits will be retained for 6.0 ms provided the signalling debounce is active.

Integrated into the signalling bit RAM is a debounce circuit which will delay valid signalling bit changes for 6.0 to 8.0 ms. By debouncing the signalling bits, a bit error will not affect the call in progress. (See Table 3, bits 3-0 of channel 15 on the CSTi0 line.)

#### **CEPT PCM 30 Format MUX**

The CEPT Link Multiplexer formats the data stream corresponding to the CEPT PCM 30 format. This implies that the multiplexer will use timeslots 1 to 15 and 17 to 31 for data and uses timeslots 0 & 16 for the synchronization and channel associated signalling.

The frame alignment or non-frame alignment signals for timeslot zero are sourced by the control stream input CSTi1 channel 16 and 17, respectively. The most significant bit of timeslot zero will optionally contain the cyclical redundancy check, CRC multiframe pattern and Si bits used for far-end CRC monitoring.

# Framing Algorithms

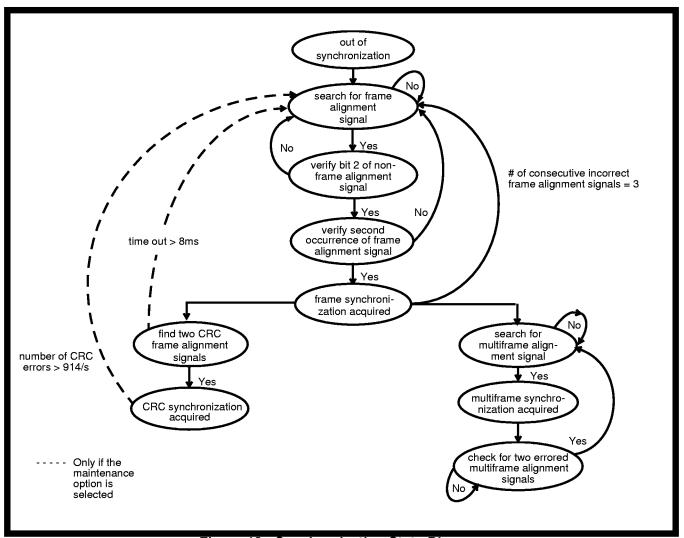

There are three distinct framers within the MT8979. These include a frame alignment signal framer, a multiframe framer and a CRC framer. Figure 13 shows the state diagram of the framing algorithms. The dotted lines shows optional features, which are enabled in the maintenance mode.

The frame synchronization circuit searches for the first frame alignment signal within the bit stream. Once detected, the frame counters are set to find the non-frame alignment signal. If bit 2 of the non-frame alignment signal is not one, a new search is initiated, else the framer will monitor for the frame alignment in the next frame. If the frame alignment signal is found, the device immediately declares frame synchronization.

The multiframe synchronization algorithm is dependent upon the state of frame alignment framer. The multiframe framer will not initiate a search for multiframe synchronization until frame sync is achieved. Multiframe synchronization will be declared on the first occurrence of four consecutive zeros in the higher order quartet of channel 16. Once multiframe synchronization is achieved, the framer will only go out of synchronization after detection of two errors in the multiframe signal or loss of frame alignment synchronization.

The CRC synchronization algorithm is also dependent on the state of the frame alignment framer, but is independent of the multiframe synchronization. The CRC framer will not initate a search for CRC framing signal until frame alignment synchronization is achieved. Once frame alignment

synchronization is acquired, the CRC framer must find two framing signals in bit 1 of the non-frame alignment signal. Upon detection of the second CRC framing signal the MT8979 will immediately go into CRC synchronization. When maintenance feature is enabled (maint bit = 1) the CRC framer will force a complete reframe of the device if CRC frame synchronization is not found within 8 ms or more than 914 CRC errors occur per second.

Figure 13 - Synchronization State Diagram

| ВІТ   | NAME       |                                                                          | DESCRI                                                                                                                                    | PTION                                                         |                                                         |

|-------|------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------|

| 7     | DATA       | treated as a data cha<br>transmission or recep                           | , then the controlled tinnel; i.e., no ADI encontrol, and digital attention, and pin determined.                                          | oding or decoding is uation is disabled.                      | performed on                                            |

| 6     | LOOP       | CEPT 2048 kbit/s linl<br>received timeslot. If<br>This function only ope | ack: If '1', then the co<br>k is looped internally to<br>'0', then this function is<br>erates if frame synchro<br>nnel is looped per fran | o replace the data or<br>s disabled.<br>onization is received | the corresponding from the CEPT link.                   |

| 5,4,3 | RXPAD4,2,1 | Receive Attenuation                                                      | n Pad: Per timeslot re                                                                                                                    | ceive attenuation co                                          | ntrol bits.                                             |

|       |            | RXPAD4<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1                           | RXPAD2<br>0<br>0<br>1<br>1<br>0<br>0<br>1                                                                                                 | RXPAD1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1                | Gain (dB)<br>0<br>-1<br>-2<br>-3<br>-4<br>-5<br>-6<br>1 |

| 2,1,0 | TXPAD4,2,1 | Transmit Attenuatio                                                      | n Pad: Per timeslot to                                                                                                                    | ransmit attenuation o                                         | control bits.                                           |

|       |            | TXPAD4<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1                           | TXPAD2<br>0<br>0<br>1<br>1<br>0<br>0<br>1                                                                                                 | TXPAD1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1                | Gain (dB)<br>0<br>-1<br>-2<br>-3<br>-4<br>-5<br>-6<br>1 |

Table 2. Per Channel Control Word: Data Format for CSTi0 Channels 0-14, and 16-30

| ВІТ              | NAME                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |

|------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                | (N/A)                         | Keep at '1' for normal operation.                                                                                                                                                                                                                                                                                                               |

| 6                | LOOP16                        | Channel 16 Loopback: If '1', then timeslot 16 on the transmitted CEPT 2048 kbit/s link is looped internally to replace the data received on timeslot 16. If '0,' then this function is disabled. This function only operates if frame synchronization is received from the CEPT link and only a single timeslot can be looped within the frame. |

| 5,4              | (N/A)                         | Keep at '1' for normal operation.                                                                                                                                                                                                                                                                                                               |

| 3,2,<br>1<br>& 0 | NDBD, NDBC,<br>NDBB<br>& NDBA | <b>Signalling Bit Debounce:</b> If '1', then no debouncing is applied to the received A, B, C or D signalling bits. If '0', then the received A, B, C or D signalling bits are debounced for between 6 and 8 ms.                                                                                                                                |

Table 3. Master Control 1 (MCW1): Data Format for CSTi0 Channel 15

| BIT | NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | (N/A)     | Keep at '1' for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6   | (N/A)     | Keep at '0' for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5   | ccs       | Common Channel Signalling: If 1, then the MT8979 operates in its common channel signalling mode. Channel 16 on the DSTi pin is transmitted on timeslot 16 of the CEPT link, and timeslot 16 from the received CEPT link is output on channel 16 on the DSTo pin. Channel 15 on the CSTi0 pin contains the information for the control of timeslot 16. Channels 0 to 15 on CSTi1 and CSTo are unused.  If '0', the device is in channel associated signalling mode where channel 16 is used to transmit the ABCD signalling bits. |

| 4   | 8KHzSEL   | <b>8KHz Select:</b> If '1', then an 8 kHz signal synchronized to the received CEPT 2048 kbit/s link is output on the E8Ko pin. This feature is only valid when frame synchronization is received from the CEPT link.  If '0', then the E8Ko pin goes into its high impedance state.                                                                                                                                                                                                                                              |

| 3   | TXAIS     | Transmit Alarm Indication Signal:  If '1', then an all 1' s alarm signal is transmitted on all timeslots.  If '0', then the timeslots functions normally.                                                                                                                                                                                                                                                                                                                                                                        |

| 2   | TXTS16AIS | Transmit Timeslot 16 Alarm Indication Signal:  If '1', then an all 1's alarm signal is transmitted on timeslot 16.  If '0', then timeslot 16 functions normally.                                                                                                                                                                                                                                                                                                                                                                 |

| 1   | XCTL      | External Control:  If '1', then the XCtl pin is driven high.  If '0', then the XCtl pin is driven low.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0   | (N/A)     | (unused)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 4. Master Control 2 (MCW2): Data Format for CSTi0 Channel 31

| ВІТ | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | MA1-4 | <b>Transmit Multiframe Alignment Bits 1 to 4:</b> These bits are transmitted on the CEPT 2048 kbit/s link in bit positions 1 to 4 of timeslot 16 of frame 0 of the multiframe. They should be kept at '0' to allow multiframe alignment to be detected.                                                                                                         |

| 3   | X1    | This bit is transmitted on the CEPT 2048 kbit/s link in bit position 5 of timeslot 16 of frame 0 of the multiframe. It is a spare bit which should be kept at '1' if unused.                                                                                                                                                                                    |

| 2   | Y     | This bit is transmitted on the CEPT 2048 kbit/s link in bit position 6 of timeslot 16 of frame 0 of the multiframe. It is used to indicate the loss of multiframe alignment to the remote end of the link. A '1' on this bit is the signal that multiframe alignment on the received link has been lost. A '0' indicates that multiframe alignment is detected. |

| 1,0 | X2,X3 | These bits are transmitted on the CEPT 2048 kbit/s link in bit positions 7 and 8 respectively, of timeslot 16 of frame 0 of the multiframe. They are spare bits which should be kept at '1' if unused.                                                                                                                                                          |

Table 5. Multiframe Alignment Signal: Data Format for CSTi1 Channel 0 on the Transmitted CEPT Link

| ВІТ                  | NAME                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7,<br>6,<br>5<br>& 4 | A(N),<br>B(N),<br>C(N)<br>& D(N)             | Transmit Signalling Bits for Channel N: These bits are transmitted on the CEPT 2048 kbit/s link in bit positions 1 to 4 of timeslot 16 in frame N, and are the A, B, C and D signalling bits associated with telephone channel N. The value of N lies in the range 1 to 15 and refers to the channel on the CSTi1 channel from which the bits are sourced, the telephone channel with which the bits are associated and the frame on the CEPT link on which the bits are transmitted. For example, the bits input on the CSTi1 pin on channel 3 are associated with telephone channel 3, which is timeslot 3 of the CEPT link, and are transmitted on bits positions 1 to 4 of timeslot 16 in frame 3 of each multiframe on the CEPT link . If bits B, C or D are not used they should be given the values '1, 0' and '1' respectively. The combination '0000' for ABCD bits should not be used for telephone channels 1 to 15 as this would interfere with multiframe alignment. |

| 3,<br>2,<br>1<br>& 0 | A(N+15),<br>B(N+15),<br>C(N+15)<br>& D(N+15) | Transmit Signalling Bits for Channel N+15: These bits are transmitted on the CEPT 2048 kbit/s link in bit positions 5 to 8 of timeslot 16 in frame N, and are the A, B, C and D signalling bits associated with telephone channel N+15. The value of N lies in the range 1 to 15 and refers to both the channel on the CSTi1 stream where the bits are supplied and the frame on the CEPT link on which the bits are transmitted, and indirectly indicates the telephone channel with which the bits are are associated. For example, the bits input on the CSTi1 pin on channel 3 are associated with telephone channel 18, which is timeslot 19 of the CEPT link, and are transmitted in bits positions 5 to 8 of timeslot 16 in frame 3 of each multiframe on the CEPT link.                                                                                                                                                                                                   |

Table 6. Channel Associated Signalling: Data Format for CSTi1 Channels 1 to 15

| BIT | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                       |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IU0    | International Use 0: When CRC is disabled, this bit is transmitted on the CEPT 2048 kbit/s link in bit position 1 of timeslot 0 of frame-alignment frames. It is reserved for international use and should be kept at '1' when not used. If CRC is enabled, this bit is not used. |

| 6-0 | FAF2-8 | <b>Transmit Frame Alignment Frame Bits 2 to 8:</b> These bits are transmitted on the CEPT 2048 kbit/s link in bit positions 2 to 8 of timeslot 0 of frame-alignment frames. These bits form the frame alignment signal and should be set to '0011011'.                            |

Table 7. Frame Alignment Signal: Data Format for CSTi1 Channel 16

| ВІТ | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IU1   | International Use 1: When the CRC is disabled and SiMUX bit in MCW3 is disabled, this bit is transmitted on the CEPT 2048 kbit/s link in bit position 1 of timeslot 0 of non-frame-alignment frames. It is reserved for international use and should be kept at '1' when not used. If CRC is enabled and SiMUX is disabled, this bit is transmitted in bit 1 of timeslot 0 for frame 13 and 15. If both CRC and SiMUX are enabled, then this bit is not used. |

| 6   | NFAF  | <b>Transmit Non-Frame Alignment Bit:</b> This bit is transmitted on the CEPT 2048 kbit/s link in bit position 2 of timeslot 0 of non-frame-alignment frames. In order to differentiate between frame-alignment frames and non-frame-alignment frames, this bit should be kept at '1'.                                                                                                                                                                         |

| 5   | ALM   | Non-Frame Alignment Alarm: This bit is transmitted on the CEPT 2048 kbit/s link in bit position 3 of timeslot 0 of non-frame-alignment frames. It is used to signal an alarm to the remote end of the CEPT link. The bit should be set to '1' to signal an alarm and should be kept at '0' under normal operation.                                                                                                                                            |

| 4-0 | NU1-5 | <b>National Use:</b> These bits are transmitted on the CEPT 2048 kbit/s link in bit positions 4 to 8 of timeslot 0 of non-frame-alignment frames. These bits are reserved for national use, and on crossing international borders they should be set to '1'.                                                                                                                                                                                                  |

Table 8. Non-Frame-Alignment Signal: Data Format for CSTi1 Channel 17

| BIT | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                    |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | N/A    | Keep at zero for normal operation.                                                                                                                                                                                                                                                                                                             |

| 6   | SiMUX  | When set to '1', this bit will cause the SMFI CRC result to be transmitted in the next outgoing Si1 bit in frame 13 and the SMFII CRC result to be transmitted in the next outgoing Si2 bit in frame 15.                                                                                                                                       |

| 5   | RMLOOP | <b>Remote Loopback:</b> If set the $\overline{RxA}$ and $\overline{RxB}$ signals are looped to TxB and TxA respectively.                                                                                                                                                                                                                       |

| 4   | HDB3en | <b>Enable HDB3 Encoding:</b> A '1' will disable the HDB3 line coding and transmit the information transparently.                                                                                                                                                                                                                               |

| 3   | Maint  | <b>Maintenance:</b> A '1' will force a terminal reframe if the CRC multiframe synchronization is not achieved within 8 ms of frame synchronization. Reframe will also be generated if more than 914 CRC errors occur within a one second interval (CRC error counter is reset with every one second interval). A '0' will disable this option. |

| 2   | CRCen  | <b>Enable Cyclical Redundancy Check:</b> A '1' will enable the CRC generation on the transmit data. A '0' will disable the CRC generator. The CRC receiver is always active regardless of the state of CRCen.                                                                                                                                  |

| 1   | DGLOOP | <b>Digital Loopack:</b> When set, the transmitted signal is looped around from DSTi to DSTo. The normal received data is interrupted.                                                                                                                                                                                                          |

| 0   | ReFR   | Force Reframe: If set, for at least 1 frame, and then cleared the chip will begin to search for a new frame position when the chip detects the change in state from high to low. Only the change from high to low will cause a reframe, not a continuous low level.                                                                            |

Table 9. Master Control Word 3 (MCW3): Data Format for CSTi1 Channel 18

| ВІТ | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | MA1-4 | <b>Receive Multiframe Alignment Bits 1 to 4:</b> These are the bits which are received from the CEPT 2048 kbit/s link in bit positions 1 to 4 of timeslot 16 of frame 0 of the multiframe. They should all be '0'.                                                                                                                                                                                      |

| 3   | X1    | This is the bit which is received on the CEPT 2048 kbit/s link in bit position 5 of timeslot 16 of frame 0 of the multiframe. It is a spare bit which should be '1' if unused. It is not debounced.                                                                                                                                                                                                     |

| 2   | Y     | This is the bit which is received on the CEPT 2048 kbit/s link in bit position 6 of timeslot 16 of frame 0 of the multiframe. It is used to indicate the loss of multiframe alignment at the remote end of the link. A '1' on this bit is the signal that multiframe alignment at the remote end of the link has been lost. A '0' indicates that multiframe alignment is detected. It is not debounced. |

| 1,0 | X2,X3 | These are the bits which are received on the CEPT 2048 kbit/s link in bit positions 7 and 8 respectively, of timeslot 16 of frame 0 of the multiframe. They are spare bits which should be '1' if unused. They are not debounced.                                                                                                                                                                       |

Table 10. Received Multiframe Alignment Signal: Data Format for CSTo Channel 0

| віт                  | NAME                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|