## ASSP for Graphics Control

# **Graphics Display Controller**

## **MB86290A**

#### ■ DESCRIPTION

The MB86290A is a graphics display controller for drawing and displaying graphics on a car navigation system or amusement unit.

The MB86290A can process high-quality, true three-dimensional graphics at high speed using advanced features such as distortion control and hidden surface removal during expression of various levels of transparency and drawing in three-dimensional space. It can also process two-dimensional graphics with a smooth touch, for example, by drawing smooth lines and drawing polygons by connecting arbitrarily specified vertices.

#### ■ FEATURES

- Operating frequency: 100 MHz (External clock of 14.32 MHz Max)

- Host interface: Enables direct connection to a CPU (Hitachi SH3/4 or NEC V832).

- Drawing features:

- Drawing at a peak rate of 800 Mpixels per second (at an internal operating frequency of 100 MHz)

- 2D drawing functions: Point, line, triangle, polygon, BLT, and pattern drawing

- 3D drawing functions: Point, line, and triangle drawing, and hidden surface removal by Z-buffering

- Special effects: Anti-aliasing, bold/dashed-line processing, alpha blending, Gouraud shading, texture mapping (bilinear filtering, perspective correct), and tiling

(Continued)

#### ■ PACKAGE

#### (Continued)

- Display features :

- Maximum display resolution supported: 1024 x 768 pixels

- Color display either with a color palette of 8 bits per pixel or directly using 5-bit RGB colors of 16 bits per pixel

- · Overlaying four layers of screen, of which two lower layers can be divided into the left and right parts

- Supporting two 64x64-pixel hardware cursors

- Three-channel D/A converter integrated to output analog RGB signals

- Capable of superimposing using an external synchronization mode

- Memory interface :

- Using SDRAM as graphics memory at an operating clock speed of 100 MHz and data bus width of 64 bits. Capable of connecting up to 32 Mbytes (offering a throughput of 800 Mbps).

- Power-supply voltage: Two power supplies at 2.5 V±0.2 V for internal circuits and 3.3 V±0.3 V for I/O parts

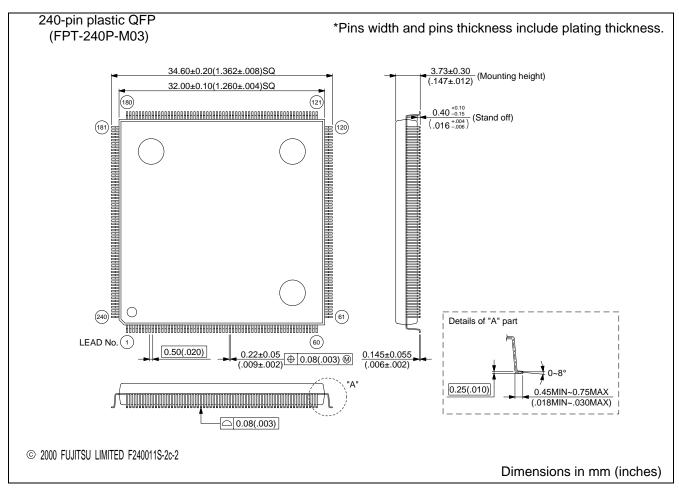

- Package: Plastic QFP with 240 pins (with a lead pitch of 0.5 mm)

- Power consumption: 1 W (at 100 MHz,  $V_{DDL} = 2.5 \text{ V} \pm 0.2 \text{ V}$ )

- Process technology: 0.25 μm CMOS

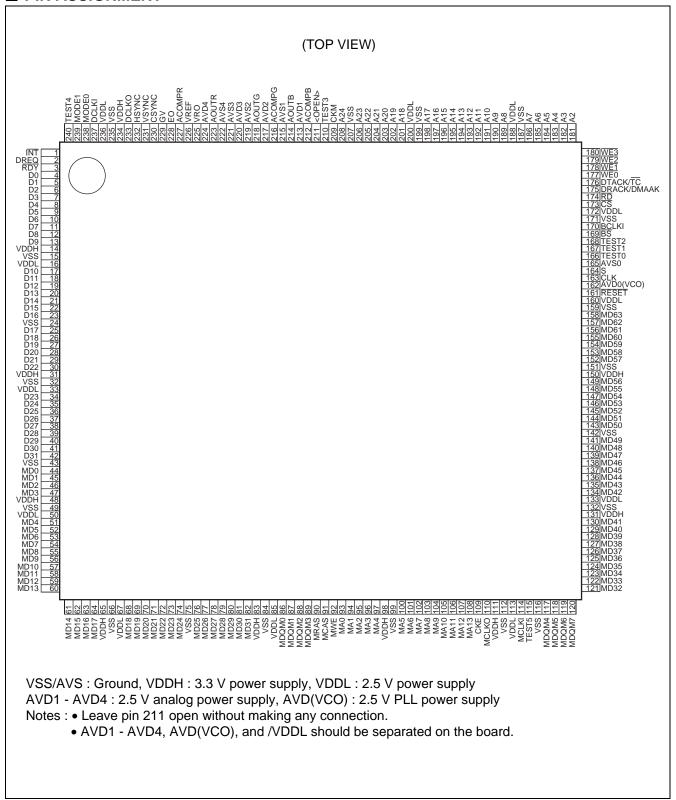

#### **■ PIN ASSIGNMENT**

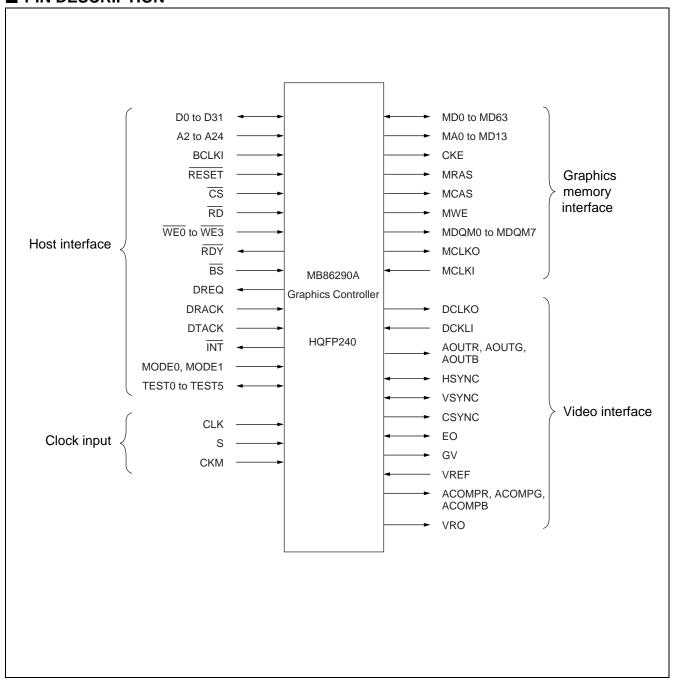

#### **■ PIN DESCRIPTION**

#### • Host Interface Pins

| Pin Name          | Input/output       | Function                                                                                                       |

|-------------------|--------------------|----------------------------------------------------------------------------------------------------------------|

| MODE0,<br>MODE1   | Input              | Host CPU mode select                                                                                           |

| RESET             | Input              | Hardware reset                                                                                                 |

| D0 to D31         | Input/Output       | Host CPU bus data                                                                                              |

| A2 to A24         | Input              | Host CPU bus address (Connect A24 to MWR in V832 mode.)                                                        |

| BCLKI             | Input              | Host CPU bus clock                                                                                             |

| BS                | Input              | Bus cycle start signal                                                                                         |

| <u>CS</u>         | Input              | Chip select signal                                                                                             |

| RD                | Input              | Read strobe signal                                                                                             |

| WE0               | Input              | D0 to D7 write strobe signal                                                                                   |

| WE1               | Input              | D8 to D15 write strobe signal                                                                                  |

| WE2               | Input              | D16 to D23 write strobe signal                                                                                 |

| WE3               | Input              | D24 to D31 write strobe signal                                                                                 |

| RDY               | Output<br>Tristate | Wait request signal ("0" for wait state with SH3; "1" for wait state with SH4 or V832)                         |

| DREQ              | Output             | DMA request signal (active low with both SH and V832)                                                          |

| DRACK/<br>DMAAK   | Input              | InputDMA request acknowledge signal (Connect this to DMAAK in V832 mode. Active high with both SH and V832.)   |

| DTACK/TC          | Input              | DMA transfer strobe signal (Connect this to $\overline{TC}$ in V832 mode. SH = active high, V832 = active low) |

| ĪNT               | Output             | Host CPU interrupt signal (SH = active low, V832 = active high)                                                |

| TEST0 to<br>TEST5 | Input              | Test signal                                                                                                    |

Note: The host interface can connect the MB86290A to the SH4 (SH7750) or SH3 (SH7709) manufactured by Hitachi Ltd. or to the V832 manufactured by NEC without any external circuit in between. (Using the SRAM interface allows the MB86290A to use another CPU.) The host CPU is set by the MODE pins as shown below.

| MODE1 pin | MODE0 pin | CPU Type |

|-----------|-----------|----------|

| L         | L         | SH3      |

| L         | Н         | SH4      |

| Н         | L         | V832     |

| Н         | Н         | Reserved |

- Notes: The host interface transfers data signals at a fixed width of 32 bits.

- There are 23 lines for address signals handled in double words (32 bits) and 32 Mbytes of address

- The external bus can be used at an operating frequency of 100 MHz Max.

- The RDY signal at the low level sets the ready state in the SH4 or V832 mode; the signal at the low level sets the wait state in the SH3 mode. Note that the XRDY signal is a tristate output.

- The host interface supports DMA transfer using an external DMA controller.

- The host interface generates a host processor interrupt signal.

The RESET pin requires low level input of at least 300 μs after setting "S" (PLL reset signal) to high level.

- Fix the TEST signal at high level.

- In the V832 mode, connect the following pins as specified :

| Pin Name | V832 Signal Name |

|----------|------------------|

| A24      | MWR              |

| DTACK    | TC               |

| DRACK    | DMAAK            |

#### Video Interface Pins

| Pin Name | Input/output  | Function                                                                                                                |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------|

| DCLKO    | Output        | Display dot clock signal output                                                                                         |

| DCLKI    | Input         | External synchronous dot clock signal input                                                                             |

| AOUTR    | Analog output | Analog video (R) signal output                                                                                          |

| AOUTG    | Analog output | Analog video (G) signal output                                                                                          |

| AOUTB    | Analog output | Analog video (B) signal output                                                                                          |

| HSYNC    | Input/output* | Horizontal sync signal output<br>Horizontal sync signal input in external synchronization mode                          |

| VSYNC    | Input/output* | Vertical sync signal output Vertical sync signal input in external synchronization mode                                 |

| CSYNC    | Output        | Composite sync signal output                                                                                            |

| EO       | Input/output* | Even/odd-number field identification output Even/odd-number field identification input in external synchronization mode |

| GV       | Output        | Graphics/video select signal                                                                                            |

| VREF     | Analog output | Reference voltage input pin                                                                                             |

| ACOMPR   | Analog output | R-signal compensation pin                                                                                               |

| ACOMPG   | Analog output | G-signal compensation pin                                                                                               |

| ACOMPB   | Analog output | B-signal compensation pin                                                                                               |

| VRO      | Analog output | Reference current setting pin                                                                                           |

<sup>\*:</sup> Input voltage level: 5 V tolerant

Notes: • The video interface contains an 8-bit D/A converter to output analog RGB signals.

- Using an additional external circuit, the video interface can use CSYNC signals to generate composite video signals.

- The video interface can output analog RGB signals synchronized with external video signals. The mode for synchronization with the DCLKI signal can be selected as well as the mode for synchronization with a set dot clock as for normal display.

- The HSYNC and VSYNC signals must be pulled up outside the LSI as they enter the input state upon reset.

- Terminate the AOUTR, AOUTG, and AOUTB pins with a resistance of 75  $\Omega$ .

- Input 1.1 V to the VREF pin. Between this pin and analog ground, insert a bypass capacitor (one with a superior high-frequency characteristic such as a laminated ceramic capacitor).

- Connect the ACOMPR, ACOMPG, and ACOMPB pins to the 0.1μF ceramic capacitor ahead of the analog power supply.

- Connect the VRO pin to the analog ground with a 2.7 k $\Omega$  resistor.

- The input voltage levels of the HSYNC, VSYNC, and EO signals are 5 V tolerant. Do not input 5 V to these pins with the power supply off. (See ABSOLUTE MAXIMUM RATINGS.)

- For noninterlaced display in external synchronization mode, input "0" to the EO pin, for example, using a pull-down resistor.

- The GV signal serves to switch between graphics and video for chroma keying. The pin outputs a low level signal to select video.

• Graphics Memory Interface Pins

| Pin Name       | Input/output | Function                     |

|----------------|--------------|------------------------------|

| MD0 to MD63    | Input/output | Graphics memory bus data     |

| MA0 to MA13    | Output       | Graphics memory bus data     |

| CKE            | Output       | Clock enable                 |

| MRAS           | Output       | Row address strobe           |

| MCAS           | Output       | Column address strobe        |

| MWE            | Output       | Write enable                 |

| MDQM0 to MDQM7 | Output       | Data mask                    |

| MCLKO          | Output       | Graphics memory clock output |

| MCLKI          | Input        | Graphics memory clock input  |

- Notes: The graphics memory interface connects the MB86290A to the external memory used for graphical image data. The interface can directly accept 64 Mbit SDRAM (with a 16-bit or 32-bit data bus) without any external circuit.

- The data signal can be selected between 64 bits and 32 bits. To use the 32-bit signal, leave the MD32 to MD63 and MDQM4 to MDQM7 pins open.

- Connect the MCLKI pin to the MCLKO pin.

#### Clock Input Pins

| Pin Name | Input/output | Function           |

|----------|--------------|--------------------|

| CLK      | Input        | Clock input signal |

| S        | Input        | PLL reset signal   |

| CKM      | Input        | Clock mode signal  |

- Notes: The clock input block inputs the clock signal that serves as the basis for the reference clock for the internal operating clock and display dot clock. Usually input 4 Fsc (= 14.31818 MHz). The internal PLL generates the internal operating clock signal of 100.22726 MHz and the display reference clock signal of 200.45452 MHz.

- The internal operating clock signal to be used can be selected between the clock signal (CLK input multiplied by 7) generated by the internal PLL and the bus clock BCLKI input to the host CPU interface. Select the BCLKI input to use the host CPU bus at 100 MHz.

| СКМ | Clock Mode                          |  |  |

|-----|-------------------------------------|--|--|

| L   | Select internal PLL output.         |  |  |

| Н   | Select host CPU bus clock (BCLKI) . |  |  |

Note: Immediately after turning the power supply on, input a pulse whose low level <u>period</u> is 500 ns or more to the S pin before setting it to high level. After the S signal goes high, input the <u>RESET</u> signal at low level for 300 μs or more.

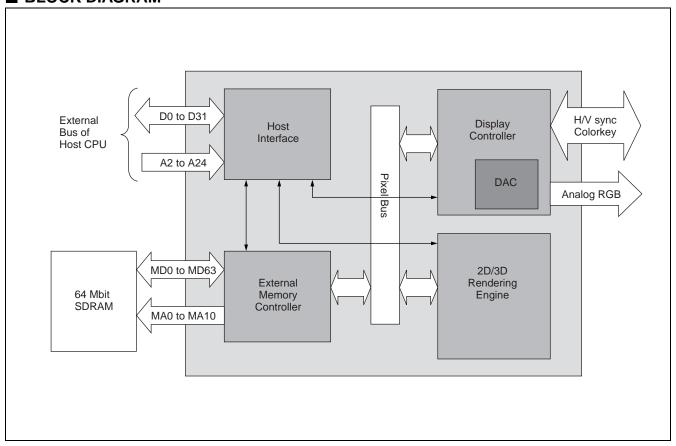

### **■ BLOCK DIAGRAM**

#### **■ FUNCTION BLOCKS**

#### Host Interface

This block allows the MB86290A to be connected to the SH3 or SH4 microprocessor manufactured by Hitachi Ltd. without any external circuit in between. The block provides an interface to transfer display list and texture pattern data directly from main memory to the CREMSON graphics memory or internal register using the external DMA controller.

#### • External Memory Controller

This block controls the external synchronous DRAM connected as graphics memory. The 64-bit or 32-bit data bus is selected and the maximum operating frequency is 100 MHz.

#### • Display Controller

This block contains a three-channel D/A converter supporting XGA (1024x768 pixels) display and outputs analog RGB signals. The block enables superimposing using the external synchronization mode. It can divide the screen into the left and right parts to display different contents and to scroll them separately. It can also display animations smoothly using double buffering. In addition, it can overlay up to four screens, where the image color blending function can be used to display maps through the console screen as a transparency.

#### • 2D/3D Rendering Engine

This block draws images in two or three dimensions.

#### 2D drawing

The block provides the anti-aliasing and alpha blending functions to display high-quality images even on a low-resolution LCD.

#### • 3D drawing

The block provides true 3D drawing functions such as perspective texture mapping and Gouraud shading.

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol              | Ra                        | Unit               |       |  |

|-------------------------------|---------------------|---------------------------|--------------------|-------|--|

| rarameter                     | Symbol              | Min                       | Max                | Oilit |  |

| Dower aupply voltage          | V <sub>DDL</sub> *1 | - 0.5                     | + 3.0              | V     |  |

| Power-supply voltage          | V <sub>DDH</sub>    | - 0.5                     | + 4.0              | V     |  |

| Input voltage                 | Vı                  |                           | VDDH + 0.5 (< 4.0) | V     |  |

| Input voltage                 | V <sub>IV</sub> *2  | - 0.5                     | VDDH + 4.0 (< 6.0) | V     |  |

| Output current                | lo                  | <b>– 13</b>               | + 13               | mA    |  |

| Power pin current             | <b>I</b> POW        | _                         | 60                 | mA    |  |

| Ambient energting temperature | TA                  | 0                         | 70                 | °C    |  |

| Ambient operating temperature | I A                 | - <b>40*</b> <sup>3</sup> | + 85*3             |       |  |

| Ambient storage temperature   | Tstg                | <b>– 55</b>               | + 125              | °C    |  |

<sup>\*1 :</sup> The analog and PLL power supplies are included.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

<sup>\*2 :</sup> The HSYNC, VSYNC, and EO signals are input.

<sup>\*3 :</sup> Model supporting a wider range of temperatures

#### ■ RECOMMENDED OPERATING CONDITIONS

| Dorometer                      | Symbol              |              | Value |            | Unit |

|--------------------------------|---------------------|--------------|-------|------------|------|

| Parameter                      | Symbol              | Min          | Тур   | Max        | Unit |

|                                | V <sub>DDL</sub> *1 | 2.3          | 0.5   |            |      |

| Power supply voltage           | V <sub>DDL</sub> *2 | 2.6*6        | 2.5   | 2.7        | V    |

| Power-supply voltage           | V <sub>DDH</sub>    | 3.0          | 3.3   | 2.6        | V    |

|                                | V DDH               | 3.5*6        | 3.3   | 3.6        |      |

| Input voltage (High Iovel)     | ViH                 | 2.0          | _     | VDDH + 0.3 | V    |

| Input voltage (High level)     | V <sub>IHV</sub> *3 | 2.0          | _     | 5.5        | V    |

| Input voltage (Levy level)     | VıL                 | - 0.3        | _     | + 0.8      | V    |

| Input voltage (Low level)      | V <sub>ILV</sub> *3 | - 0.3        | _     | + 0.8      | V    |

| VREF pin input voltage         | Vref                | 1.05         | 1.10  | 1.15       | V    |

| VRO pin external resistor      | Rvro                | _            | 2.7   | _          | kΩ   |

| AOUT pin external resistor*4   | RAOUT               | _            | 75    | _          | Ω    |

| ACOMP pin external capacitor*5 | Сасомр              | _            | 0.1   | _          | μF   |

| Ambient energting temperature  | т.                  | 40           |       | + 85       | °C   |

| Ambient operating temperature  | TA                  | - <b>4</b> 0 | _     | + 70*6     |      |

<sup>\*1 :</sup> The analog and PLL power supplies are included.

Notes: • The VDDL and VDDH power supplies can be turned on or off in either order.

Note, however, that the VDDH voltage must not be applied alone continuously for several seconds.

- Do not input the HSYNC, VSYNC or signal with the power-supply voltage not applied. (See "Input voltage" in "■ ABSOLUTE MAXIMUM RATINGS".)

- After turning the power on, input a pulse remaining at low level for at least 500 ns to the S pin. Then, set the S pin to high level and input the RESET signal held at low level for at least 300 μs.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

<sup>\*2 :</sup> The HSYNC, VSYNC, and EO signals are input.

<sup>\*3:</sup> AOUTR, AOUTG, and AOUTB pins

<sup>\*4 :</sup> AOUTR, AOUTG, AOUTB pins

<sup>\*5 :</sup> ACOMPR, ACOMPG, ACOMPB pins

<sup>\*6:</sup> Using BCLKI at 90 MHz or more

#### **■ ELECTRICAL CHARACTERISTICS**

#### 1. DC Characteristics

$(V_{DDL} = 2.5 \text{ V} \pm 0.2 \text{ V}, V_{DDH} = 3.3 \text{ V} \pm 0.3, V_{SS} = 0.0 \text{ V}, T_{A} = 0 ^{\circ}\text{C to } +70 ^{\circ}\text{C})$

| Parameter             |                             | Symbol              |                        | Value |                  |      |

|-----------------------|-----------------------------|---------------------|------------------------|-------|------------------|------|

|                       |                             | Symbol              | Min                    | Тур   | Max              | Unit |

| Output voltage (High  | level) *1                   | Vон                 | V <sub>DDH</sub> - 0.2 | _     | V <sub>DDH</sub> | V    |

| Output voltage (Low   | level) *2                   | Vol                 | 0.0                    | _     | 0.2              | V    |

|                       |                             | IOH1*3              | - 2.0                  | _     | _                |      |

| Output current (High  | Output current (High level) |                     | - 4.0                  | _     | _                | mA   |

|                       |                             |                     | - 8.0                  | _     | _                | 7    |

|                       |                             |                     | 2.0                    | _     | _                |      |

| Output current (Low   | level)                      | <b>l</b> 0L2*4      | 4.0                    | _     | _                | mA   |

|                       |                             | lo <sub>L3</sub> *5 | 8.0                    | _     | _                |      |

| AOUT voltage*6        | Full scale                  | - Ідоит             | 9.90                   | 10.42 | 10.94            | mA   |

| AOO1 Vollage *        | Zero scale                  | IAOUT               | 0                      | 2     | 20               | μΑ   |

| AOUT voltage*7        |                             | Vaout               | - 0.1                  | _     | + 1.1            | V    |

| Input leakage current |                             | lι                  |                        | _     | ± 5              | μΑ   |

| Pin capacitance       |                             | С                   | _                      | _     | 16               | pF   |

<sup>\*1 :</sup> Value when  $-100 \,\mu\text{A}$  current flows into output pins.

<sup>\*2 :</sup> Value when 100  $\mu A$  current flows into output pins.

<sup>\*3 :</sup> Output characteristics of the MD0 to MD63, MDQM0 to MDQM7 pins

<sup>\*4:</sup> Output characteristics of the signals (excluding analog signals) other than those in \*3 and \*5

<sup>\*5 :</sup> MCLKO pin output characteristics

<sup>\*6 :</sup> AOUTR, AOUTG, and AOUTB pin output current. Conditions  $V_{REF} = 1.10 \text{ V}$ ,  $R_{VRO} = 2.7 \text{ k}\Omega$  (The full-scale output current calculation expression is  $(V_{REF}/R_{VRO}) \times 25.575$ )

<sup>\*7:</sup> AOUTR, AOUTG and AOUTB pins

#### 2. AC Characteristics

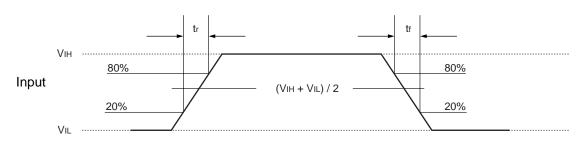

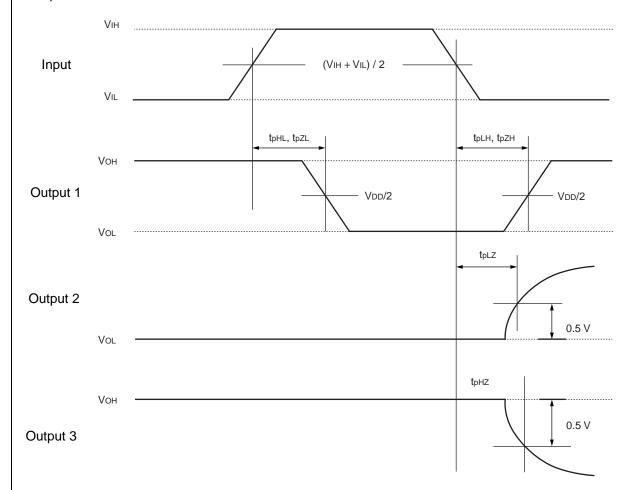

$(V_{IH} = 2.0 \text{ V}, V_{IL} = 0.8 \text{ V})$

• Input measurement conditions

- $t_r$ ,  $t_f \le 5 \text{ ns}$

- Input measurement standard : (VIH + VIL) / 2

• Output measurement conditions

• Output measurement standard : tpLz : VoL + 0.5 V

$t_{\text{pHZ}}$ :  $V_{\text{OH}} - 0.5 \text{ V}$  Else :  $V_{\text{DD}}/2$

### (1) Host Interface

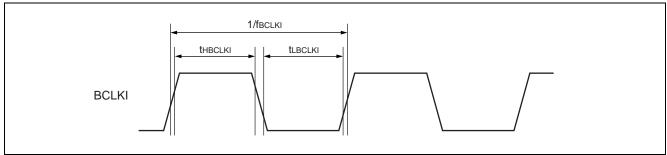

### • Clock

| Parameter       | Symbol Condition |           | Val | Unit |      |  |

|-----------------|------------------|-----------|-----|------|------|--|

| Farameter       | Symbol           | Condition | Min | Max  | Onit |  |

| BCLKI frequency | fвські           | _         | _   | 100  | MHz  |  |

| BCLKI H period  | <b>t</b> нвські  | _         | 3.5 | _    | ns   |  |

| BCLKI L period  | <b>t</b> lbclki  | _         | 3.5 |      | ns   |  |

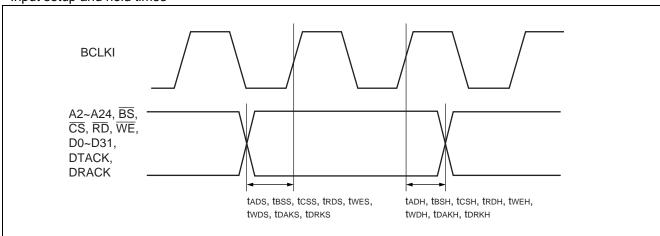

### • Host interface signals

(Recommended operating conditions A, External load of 20 pF)

| Paramatar.                                 | Cumb al          | Condition | Va    | Unit  |      |

|--------------------------------------------|------------------|-----------|-------|-------|------|

| Parameter                                  | Symbol           | Condition | Min   | Max   | Unit |

| Address setup time                         | <b>t</b> ADS     |           | 3.0   | _     | ns   |

| Address hold time                          | <b>t</b> adh     | _         | 1.0   | _     | ns   |

| DC cotup time                              | t                |           | 3.5   |       | no   |

| BS setup time                              | t <sub>BSS</sub> | _         | 3.0*3 | _     | ns   |

| BS hold time                               | <b>t</b> BSH     | _         | 0.0   | _     | ns   |

| CS setup time                              | tono             |           | 3.5   |       | no   |

| C5 setup time                              | tcss             | _         | 3.0*3 | _     | ns   |

| CS hold time                               | <b>t</b> csH     | _         | 0.0   | _     | ns   |

| RD setup time                              | trds             | _         | 3.0   | _     | ns   |

| RD hold time                               | <b>t</b> RDH     |           | 1.0   | _     | ns   |

| WE setup time                              | twes             | _         | 3.0   | _     | ns   |

| WE hold time                               | tweh             | _         | 1.0   | _     | ns   |

| Write data actus time                      | 4                | _         | 5.0   | _     | no   |

| Write data setup time                      | twos             |           | 4.0*3 |       | ns   |

| Write data hold time                       | <b>t</b> wdh     |           | 1.0   | _     | ns   |

| DTACK setup time                           | <b>t</b> daks    | _         | 3.0   |       | ns   |

| DTACK hold time                            | <b>t</b> dakh    | _         | 1.0   | _     | ns   |

| DRACK setup time                           | <b>t</b> drks    | _         | 3.0   | _     | ns   |

| DRACK hold time                            | <b>t</b> drkh    | _         | 1.0   |       | ns   |

| Bood data dalay time (to BD)               | 4                |           | 4.0   | 8.5   | ns   |

| Read data delay time (to $\overline{RD}$ ) | <b>t</b> RDDZ    | _         | _     | 7.5*3 | ns   |

| Dood data dalay tima                       | 4                | *1        | 4.0   | 9.5   | ns   |

| Read data delay time                       | t <sub>RDD</sub> | ^1        | _     | 6.0*3 | ns   |

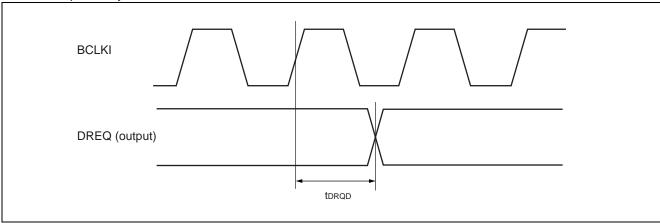

| DDV dalou time (to CC) CU                  | _                |           | 3.0   | 9.0   | ns   |

| RDY delay time (to CS) SH                  | <b>t</b> RDYDZ   |           | _     | 7.5*3 | ns   |

(Continued)

### (Continued)

| Parameter                   | Cumbal         | Condition | Va  | Unit   |       |  |

|-----------------------------|----------------|-----------|-----|--------|-------|--|

| Parameter                   | Symbol         | Condition | Min | Max    | Oilit |  |

| RDY delay time (to CS) V832 | <b>t</b> RDYDZ | _         | 3.0 | 13.0   | ns    |  |

|                             |                |           |     | 10.5*³ | ns    |  |

| RDY delay time              | <b>t</b> RDYD  | _         | 3.5 | 8.5    | ns    |  |

|                             |                |           |     | 7.0*3  | ns    |  |

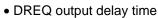

| DREQ delay time             | <b>t</b> drqd  |           | 3.5 | 7.5    | ns    |  |

|                             |                |           |     | 6.5*3  | ns    |  |

| MODE hold time              | tмодн          | *2        |     | 20.0   | ns    |  |

<sup>\*1 :</sup> Read data is output one cycle before the CPU samples it.

Note: The INT signal is output in synchronization with the internal operating clock. As a host interface signal, it is an asynchronous signal.

<sup>\*2 :</sup> Hold time for reset cancellation

<sup>\*3:</sup> Using BCLKI at 90 MHz or more

• Input setup and hold times

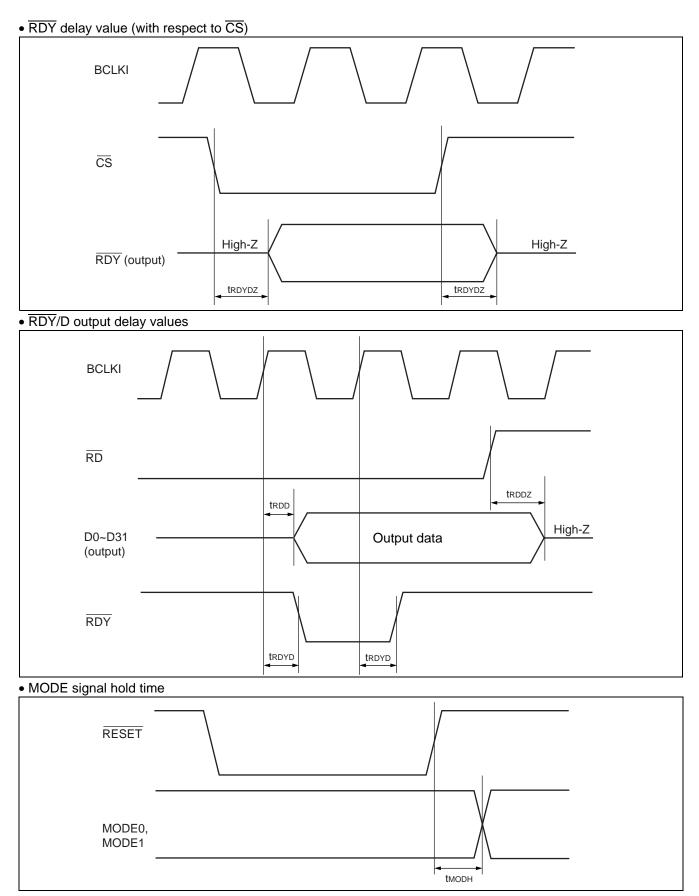

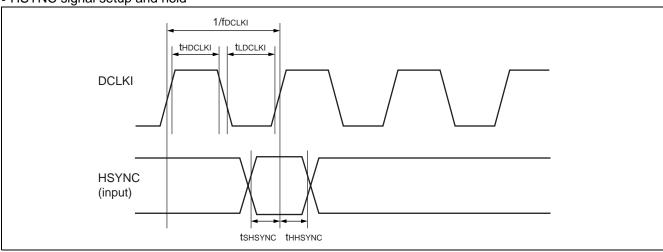

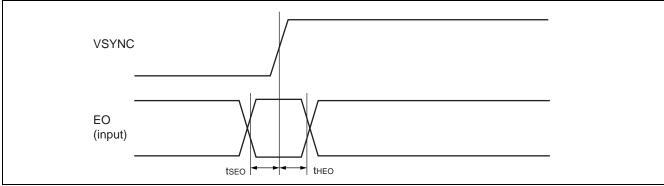

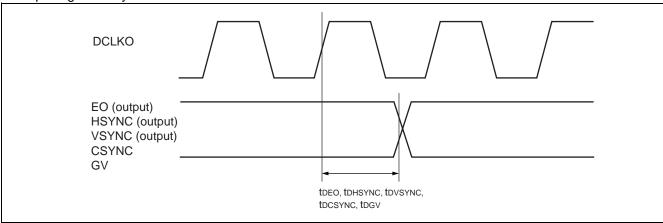

#### (2) Video Interface

#### Clock

| Parameter       | Symbol          | Condition | Value |       |     | Unit |

|-----------------|-----------------|-----------|-------|-------|-----|------|

|                 |                 |           | Min   | Тур   | Max | Onit |

| CLK frequency   | fськ            | _         |       | 14.32 | _   | MHz  |

| CLK H period    | <b>t</b> HCLK   | _         | 25    |       | _   | ns   |

| CLK L period    | <b>t</b> LCLK   | _         | 25    | _     | _   | ns   |

| DCLKI frequency | fdclki          | _         | _     | _     | 67  | MHz  |

| DCLKI H period  | <b>t</b> HDCLKI | _         | 5     | _     | _   | ns   |

| DCLKI L period  | <b>t</b> ldclki | _         | 5     | _     | _   | ns   |

| DCLKO frequency | fdclko          | _         | _     | _     | 67  | MHz  |

• Input signals

| Parameter               | Symbol       | Condition | Value |     |     | Unit             |

|-------------------------|--------------|-----------|-------|-----|-----|------------------|

|                         | Symbol       |           | Min   | Тур | Max | Unit             |

| HSYNC input pulse width | twnsynco     | *1        | 3     | _   | _   | clock            |

|                         | twnsync1     | *2        | 3     | _   | _   | clock            |

| HSYNC input setup time  | tshsync      | *2        | 10    | _   | _   | ns               |

| HSYNC input hold time   | thhsync      | *2        | 10    | _   | _   | ns               |

| VSYNC input pulse width | twnsync1     | _         | 1     | _   | _   | HSYNC<br>1 cycle |

| EO input setup time     | tseo         | *3        | 10    | _   | _   | ns               |

| EO input hold time      | <b>t</b> HEO | *3        | 10    | _   | _   | ns               |

<sup>\*1 :</sup> Applied only in PLL synchronization mode (CKS = 0) . The reference clock is the internal PLL's output with Cycle = 1/(14 fcLK).

### • Output signals

| Parameter               | Symbol       | Condition | Value |     |     | Unit  |

|-------------------------|--------------|-----------|-------|-----|-----|-------|

| raiailletei             | Symbol       |           | Min   | Тур | Max | Offic |

| EO output delay time    | <b>t</b> deo | *         | _     | _   | 10  | ns    |

| HSYNC output delay time | tohsync      | _         |       | _   | 10  | ns    |

| VSYNC output delay time | tovsync      | _         |       | _   | 10  | ns    |

| CSYNC output delay time | tdcsync      | _         |       | _   | 10  | ns    |

| GV output delay time    | <b>t</b> DGV |           | _     | _   | 10  | ns    |

<sup>\*:</sup> The EO output varies at the same time as VSYNC is asserted.

$<sup>^*2</sup>$ : Applied only in DCLKI synchronization mode (CKS = 1) . The reference clock is DCLKI.

<sup>\*3 :</sup> Based on the edge with VSYNC negated.

• HSYNC signal setup and hold

• EO signal setup and hold

Output signal delay

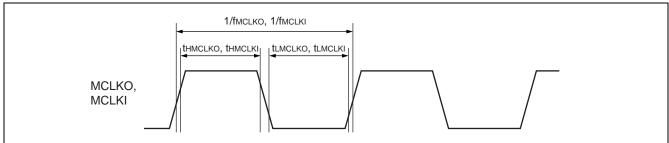

# (3) Graphics Memory Interface • Clock

| Parameter            | Symbol          | Condition | Value |     |     | Unit  |

|----------------------|-----------------|-----------|-------|-----|-----|-------|

|                      |                 |           | Min   | Тур | Max | Oilit |

| MCLKO frequency      | fмсько          | _         | _     | _   | 100 | MHz   |

| MCLKO H period       | tнмсько         | _         | 1     | _   | _   | ns    |

| MCLKO L period       | <b>t</b> LMCLKO | _         | 1     | _   | _   | ns    |

| MCLKI frequency      | <b>f</b> MCLKI  | _         |       | _   | 100 | MHz   |

| MCLKI H period       | <b>t</b> HMCLKI | _         | 1     | _   | _   | ns    |

| MCLKI L period       | <b>t</b> lmclki | _         | 1     | _   | _   | ns    |

| MCLKI delay to MCLKO | toid            | _         | 1     | _   | 4   | ns    |

• I/O signals

| Parameter                              | Cumbal          | Condition | Value |     |     | l lm:4 |

|----------------------------------------|-----------------|-----------|-------|-----|-----|--------|

|                                        | Symbol          | Condition | Min   | Тур | Max | Unit   |

| MA, MRAS, MCAS, MWE, CKE<br>Setup time | <b>t</b> MADS   | *1        | 3.5   | _   | _   | ns     |

| MA, MRAS, MCAS, MWE, CKE<br>Hold time  | <b>t</b> madh   | *1        | 1     | _   | _   | ns     |

| MDQM data setup time                   | <b>t</b> MDQMDS | *1        | 3.5   | _   | _   | ns     |

| MDQM data hold time                    | tмdqмdн         | *1        | 1     | _   | _   | ns     |

| MD output data setup time              | tmdods          | *1        | 3.5   | _   |     | ns     |

| MD output data hold time               | tмдодн          | *1        | 1     |     |     | ns     |

| MD input data setup time               | tmdids          | *2        | 3     | _   | _   | ns     |

| MD input data hold time                | <b>t</b> MDIDH  | *2        | 1     | _   | _   | ns     |

<sup>\*1 :</sup> Setup/hold time with respect to MCLKO.

<sup>\*2 :</sup> Setup/hold time with respect to MCLKI.

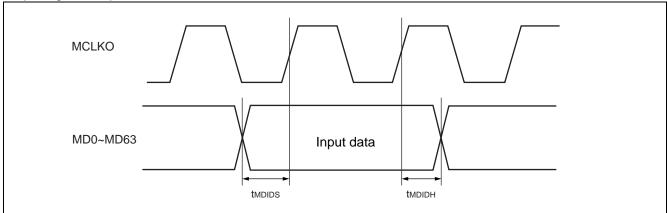

• Input signal setup and hold times

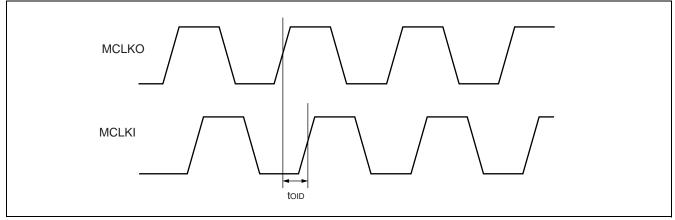

• MCLKI signal delay

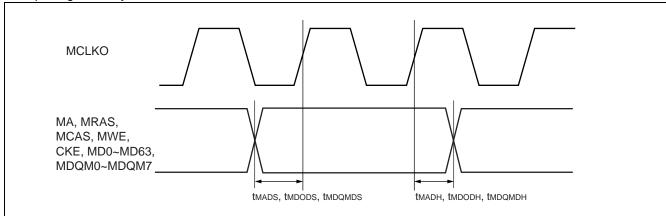

Output signal delay

### (4) PLL Standards

| Doromotor                 | Value Unit |          | l lmi4    | Description |                                                 |

|---------------------------|------------|----------|-----------|-------------|-------------------------------------------------|

| Parameter                 | Min        | Тур      | Max       | Onit        | Description                                     |

| Input frequency (Typical) | _          | 14.31818 | _         | MHz         |                                                 |

| Output frequency          | _          | _        | 200.45452 | MHz         | Multiplied by 14                                |

| Duty ratio                | 93.1       | _        | 101.3     | %           | PLL output clock H/L pulse width ratio          |

| Jitter                    | - 150      | _        | + 180     | ps          | Cycle difference between two consecutive cycles |

### **■** ORDERING INFORMATION

| Part Number  | Package                               | Remarks |

|--------------|---------------------------------------|---------|

| MB86290APFVS | 240-pin plastic QFP<br>(FPT-240P-M03) |         |

#### **■ PACKAGE DIMENSION**

### **FUJITSU LIMITED**

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

F0203

© FUJITSU LIMITED Printed in Japan