EVALUATOR BOARD PMC-1991237 PMC PMC-Sierra, Inc.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

PM4354

# **COMET-QUAD**

# COMET-QUAD EVALUATOR BOARD DESIGN

PRELIMINARY

**ISSUE 2: JANUARY 2001**

PMC-Sierra, Inc.

PM4354 COMET-QUAD

EVALUATOR BOARD PMC-1991237

ISSUE 2

COMET-QUAD EVALUATOR BOARD

# PUBLIC REVISION HISTORY

| lssue<br>No. | lssue<br>Date | Details of Change        |

|--------------|---------------|--------------------------|

| 1            | Feb 2000      | Document created.        |

| 2 January    |               | Revised Line Protection. |

|              | 2001          | Updated Schematics.      |

|              |               | Updated Layout.          |

|              |               | Updated BOM.             |

EVALUATOR BOARD PMC-1991237 PMC-Sierra, Inc.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

# **CONTENTS**

| 1 | INTR | ODUCTION 1                                         |

|---|------|----------------------------------------------------|

|   | 1.1  | PURPOSE 1                                          |

|   | 1.2  | SCOPE1                                             |

|   | 1.3  | APPLICATION 1                                      |

| 2 | FEAT | URES                                               |

| 3 | GENE | ERAL DESCRIPTION OF THE COMET-QUAD EVALUATOR KIT 5 |

|   | 3.1  | THE COMET-QUAD EVALUATOR KIT 5                     |

|   | 3.2  | HARDWARE 5                                         |

|   | 3.3  | SOFTWARE5                                          |

| 4 | BLOC | CK DESCRIPTION 6                                   |

|   | BLOC | CK DIAGRAM 6                                       |

|   | 4.2  | COMET-QUAD 6                                       |

|   | 4.3  | PCI BRIDGE9                                        |

|   | 4.4  | SEEP                                               |

|   | 4.5  | OSCILLATORS 10                                     |

|   | 4.6  | TRANSMIT AND RECEIVE LINE INTERFACE                |

|   | 4.7  | LINE TERMINATION11                                 |

|   | 4.8  | PROTECTION CIRCUITRY11                             |

|   | 4.9  | POWER SUPPLY 13                                    |

|   | 4.10 | PCI EDGE CONNECTOR 14                              |

|   | 4.11 | BACKPLANE BUS CONNECTOR 14                         |

| 5 | DESI | GN ISSUES 16                                       |

| EVALUATOR BOARI<br>PMC-1991237 | 0    | ISSUE 2                                         | COMET-QUAD EVALUATOR BOARD |

|--------------------------------|------|-------------------------------------------------|----------------------------|

|                                | 5.1  | COMET-QUAD DESIGN CONSIDERATIO                  | NS 16                      |

|                                |      | 5.1.1 POWER SUPPLY                              |                            |

|                                |      | 5.1.2 DECOUPLING                                |                            |

|                                |      | 5.1.3 INTERNAL FDL TRANSMITTER                  | 16                         |

|                                |      | 5.1.4 INTERNAL DATA LINK RECEIVER               | 17                         |

|                                |      | 5.1.5 PER-CHANNEL SERIAL CONTRO                 | LLERS 17                   |

|                                |      | 5.1.6 T1/E1 FRAMER LOOPBACK MOD                 | ES 17                      |

|                                | 5.2  | PCI BRIDGE                                      | 18                         |

|                                |      | 5.2.1 DUAL ENVIRONMENT COMPLIAN                 | ICE 18                     |

|                                |      | 5.2.2 PCI 9050 INITIALIZATION                   | 18                         |

|                                |      | 5.2.3 INTERNAL REGISTER ACCESS                  | 19                         |

|                                |      | 5.2.4 DIRECT DATA TRANSFER MODES                | S 19                       |

|                                | 5.3  | LINE PROTECTION                                 | 19                         |

|                                | 5.4  | JUMPER CONFIGURATION                            |                            |

|                                | 5.5  | POWER ESTIMATES                                 | 20                         |

|                                | 5.6  | VOLTAGE REGULATORS - CURRENT AN<br>CALCULATIONS |                            |

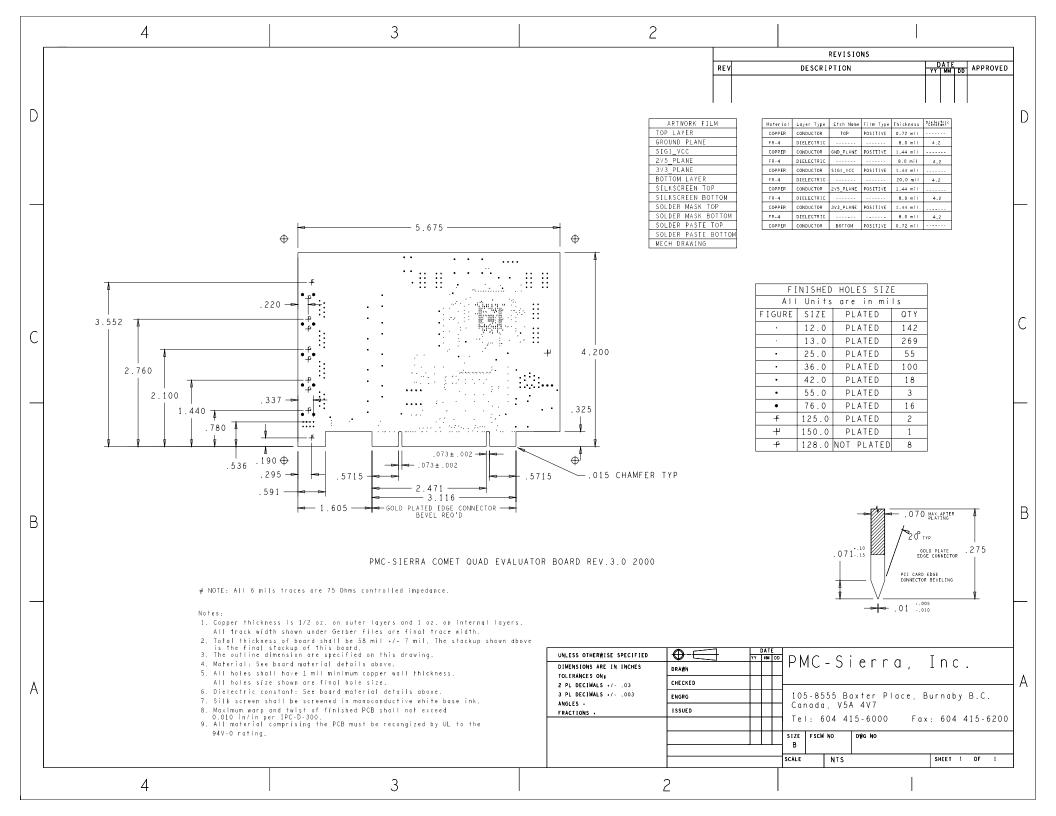

| 6                              | PHYS | CAL AND MECHANICAL DESCRIPTIONS                 | S 24                       |

|                                | 6.1  | FORM FACTOR                                     |                            |

|                                |      | 6.1.1 FACE PLATE                                |                            |

|                                | 6.2  | CONNECTORS                                      |                            |

|                                |      | 6.2.1 LINE INTERFACE CONNECTORS                 |                            |

|                                |      | 6.2.2 SYSTEM BUS CONNECTOR                      |                            |

|                                |      | 6.2.3 PCI EDGE CONNECTOR                        |                            |

EVALUATOR BOARD PMC-1991237

| COMET-QUAD EVALUATOR BOARD | COMET-QUAD | EVALU | UATOR | BOARD |

|----------------------------|------------|-------|-------|-------|

|----------------------------|------------|-------|-------|-------|

| 1237 |      | ISSUE 2                        | COMET-QUAD EVALUATOR BOARD |

|------|------|--------------------------------|----------------------------|

|      | 6.3  | LEDS                           |                            |

|      |      | 6.3.1 COMET-QUAD INTERRUPT LED |                            |

|      |      | 6.3.2 POWER STATUS LEDS        |                            |

| 7    | SOF  | TWARE INTERFACES               |                            |

|      | 7.1  | MEMORY MAP                     |                            |

|      | 7.2  | PCI 9050 CONFIGURATION         |                            |

| 8    | CON  | FORMANCE SPECIFICATION         |                            |

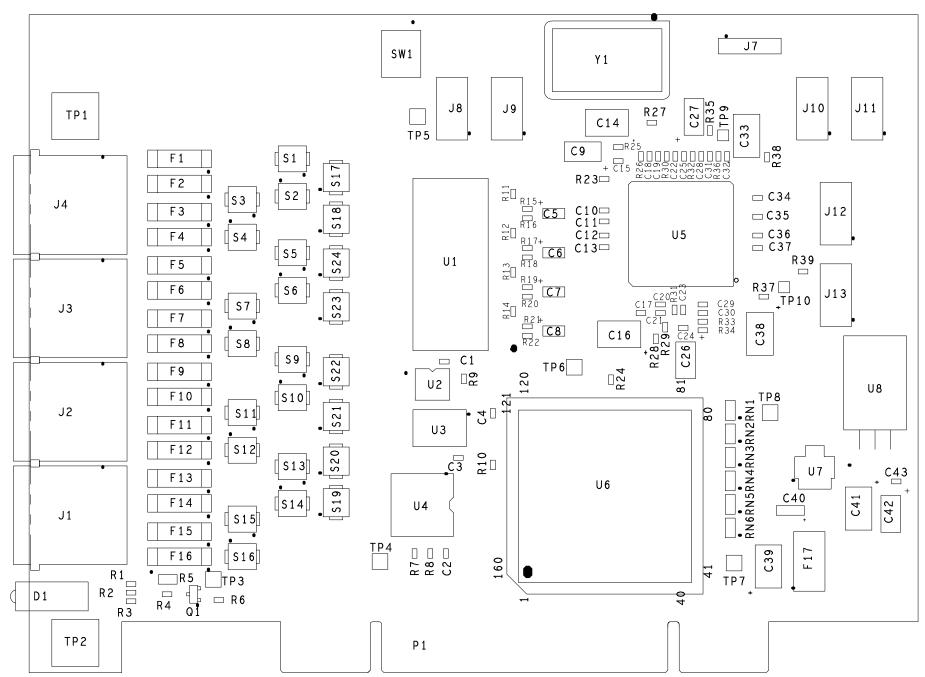

| 9    | LAYC | OUT DESCRIPTION                |                            |

|      | 9.1  | COMPONENT PLACEMENT            |                            |

|      | 9.2  | LAYER STACKING AND TRANSMISSIO |                            |

|      | 9.3  | POWER AND GROUND               |                            |

|      | 9.4  | PCI BUS SIGNAL SPECIFICATION   |                            |

|      | 9.5  | ROUTING                        |                            |

| 10   | GLO  | SSARY                          |                            |

| 11   | REF  | ERENCES                        |                            |

| 12   | DISC | LAIMER                         |                            |

| 13   | APP  | ENDIX A: BILL OF MATERIALS     |                            |

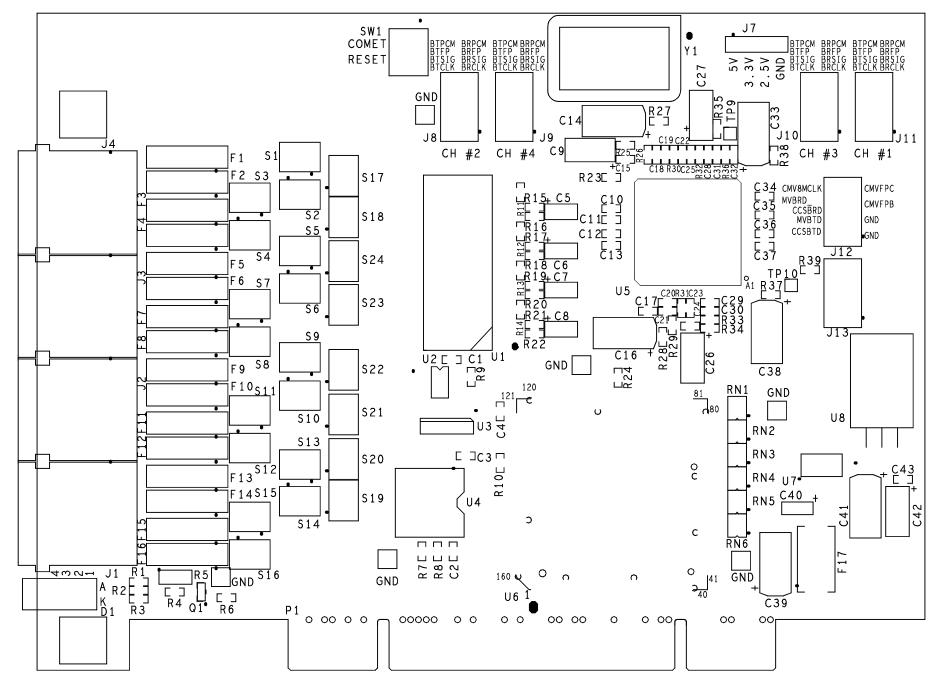

| 14   | APP  | ENDIX B: SCHEMATICS            |                            |

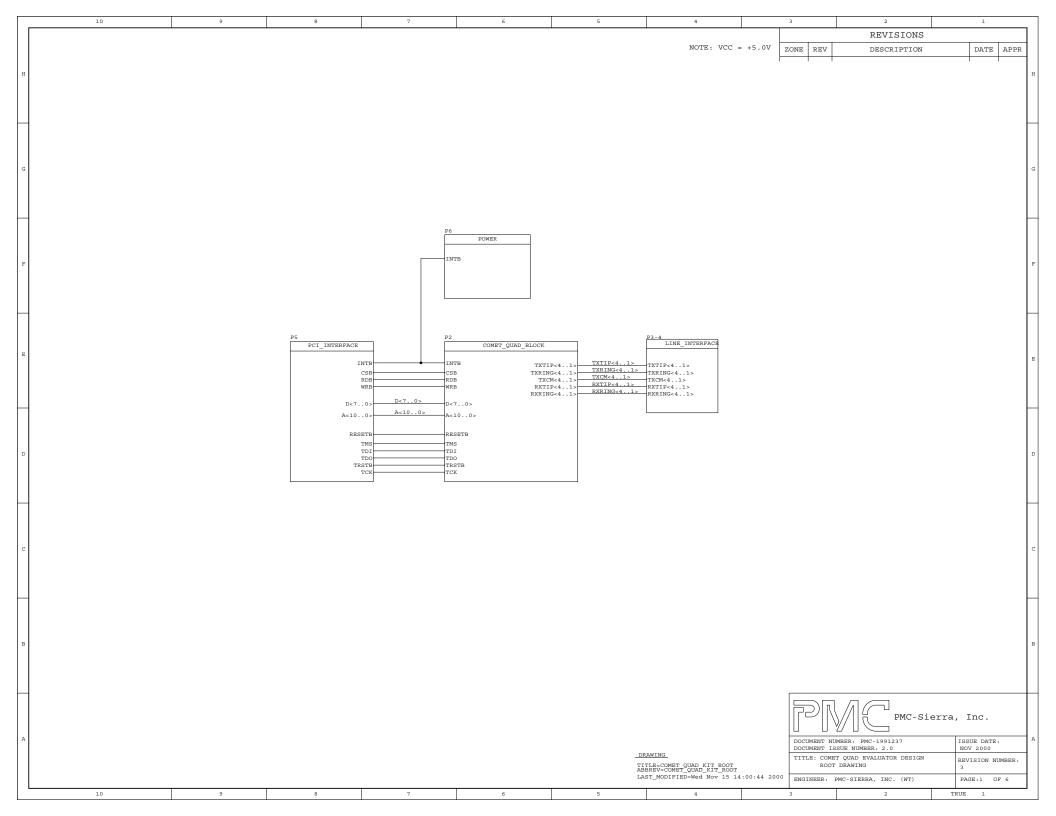

|      | 14.1 | ROOT DRAWING, SHEET 1          |                            |

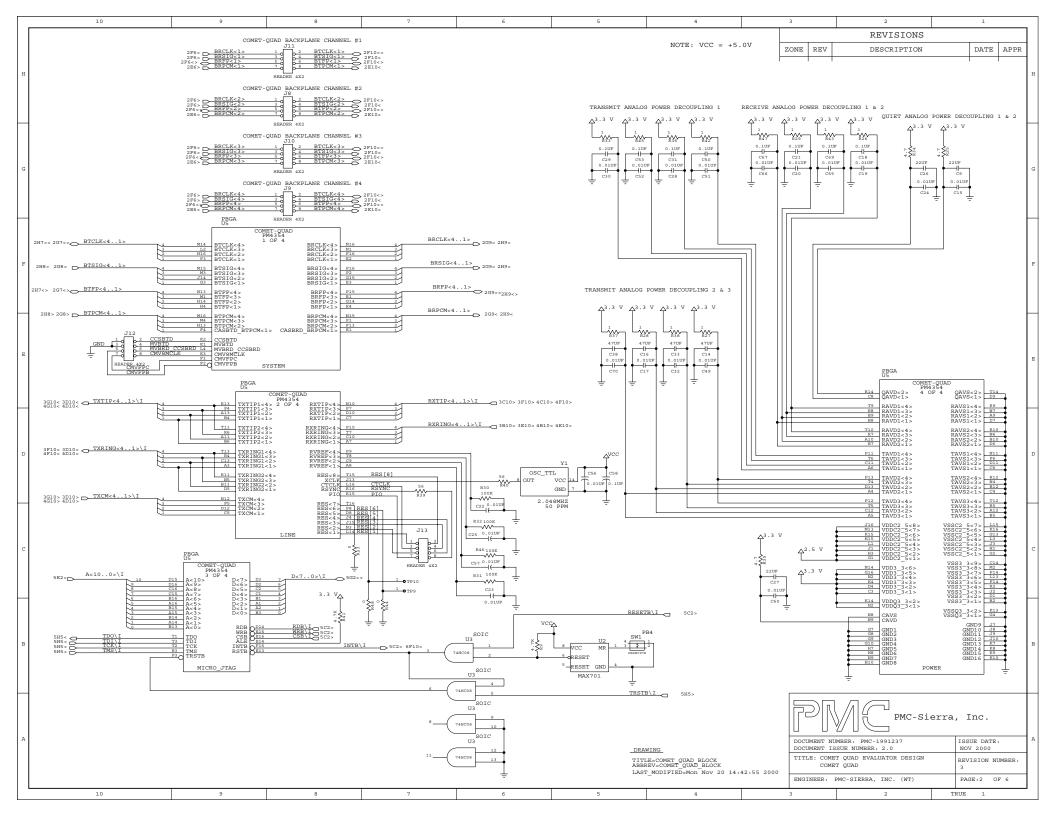

|      | 14.2 | COMET-QUAD BLOCK, SHEET 2      |                            |

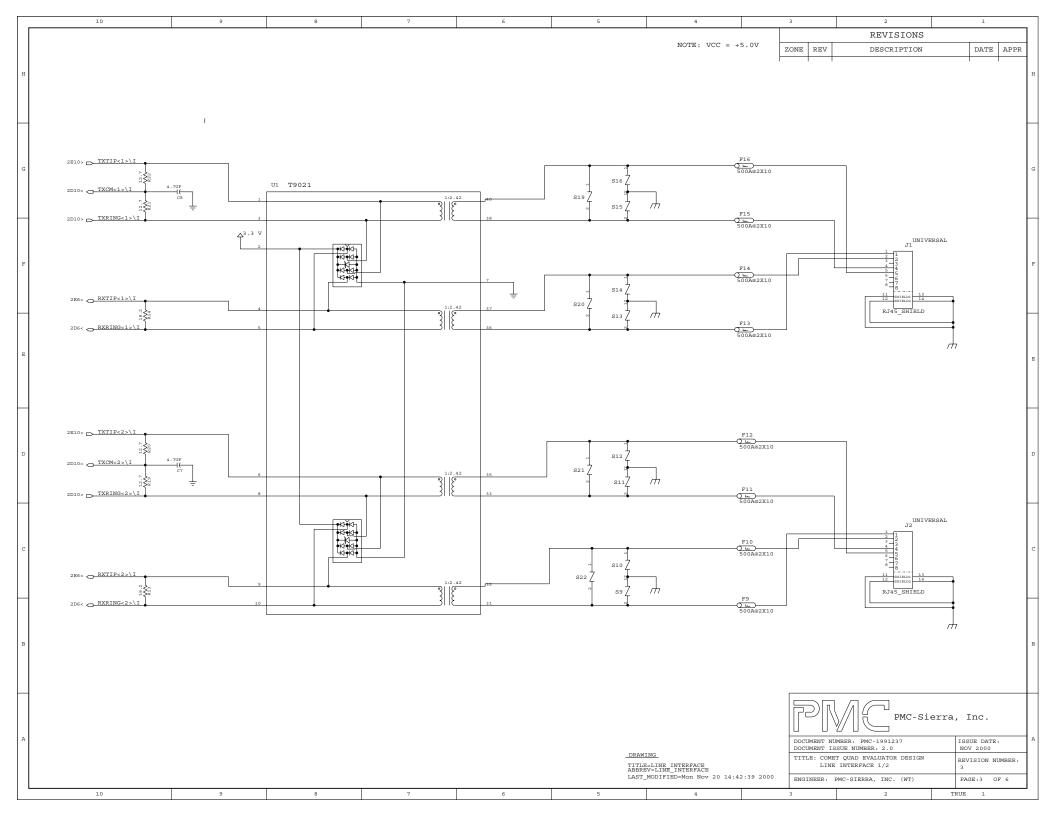

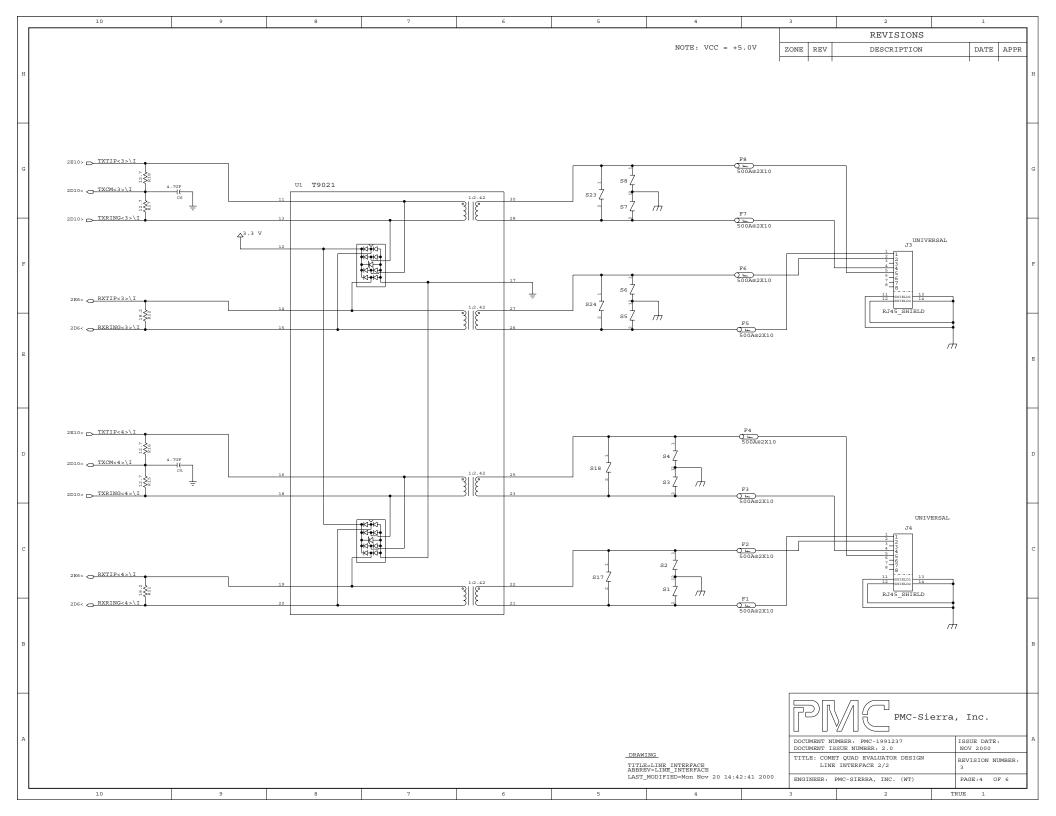

|      | 14.3 | LINE INTERFACE, SHEET 3 AND 4  |                            |

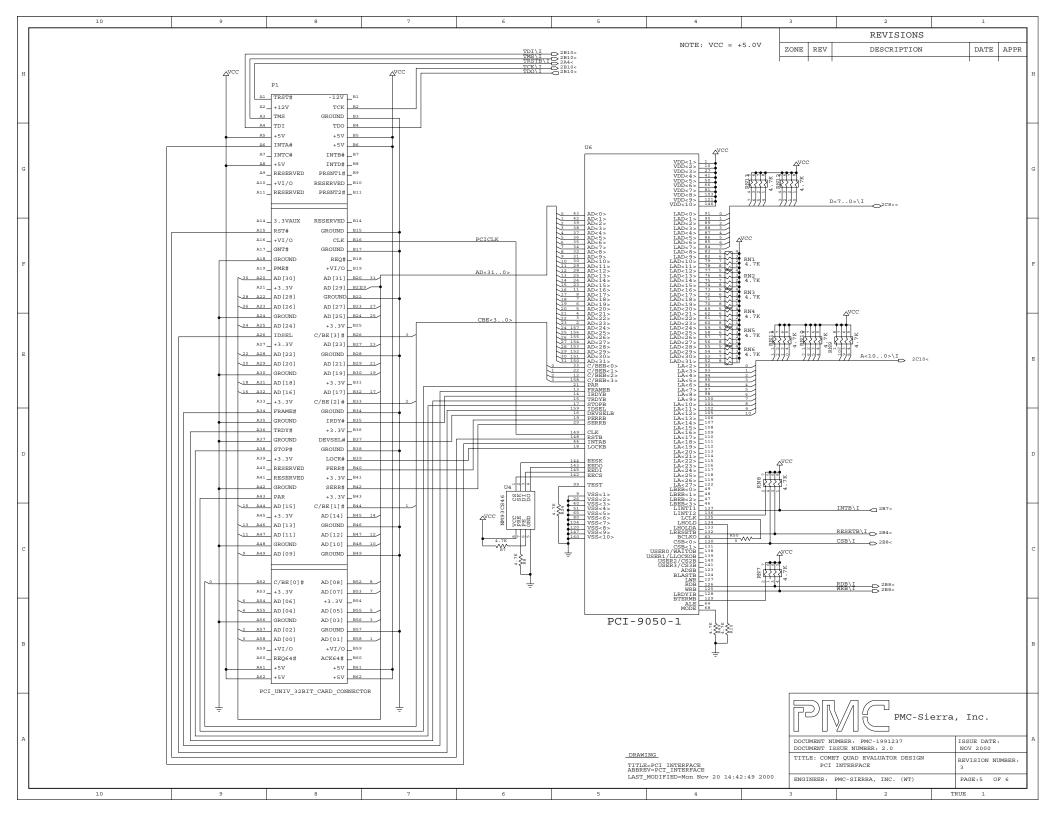

|      | 14.4 | PCI INTERFACE, SHEET 5         |                            |

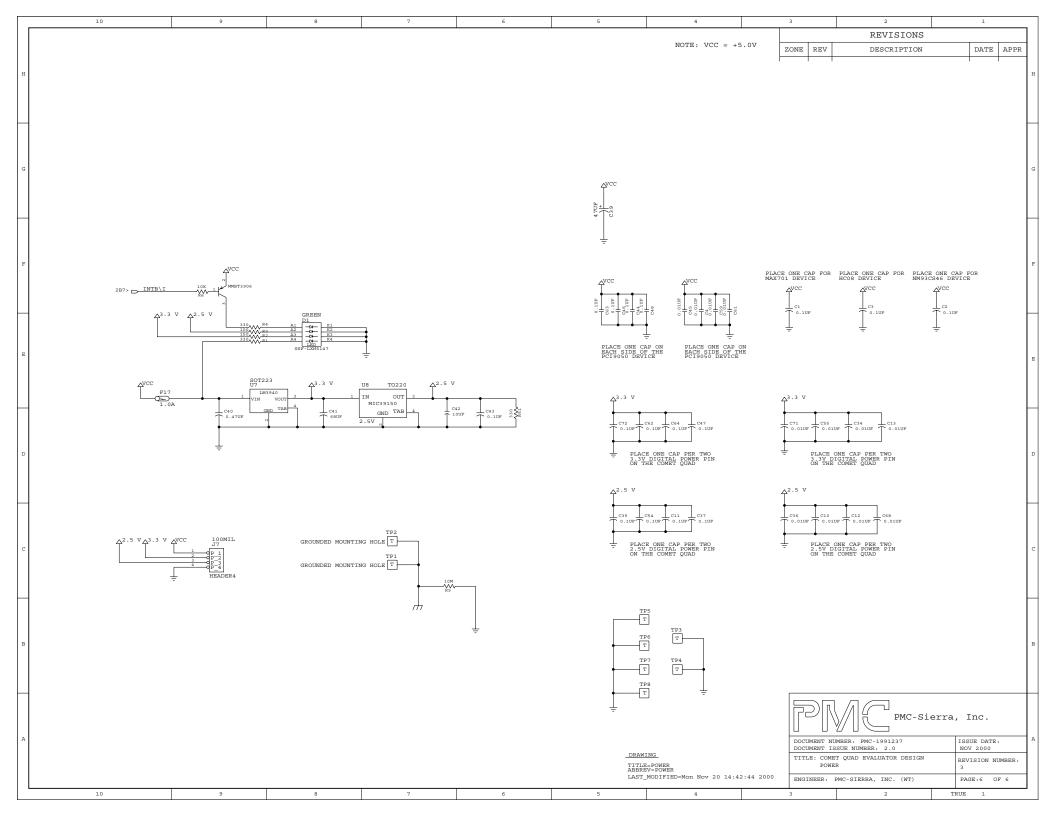

|      | 14.5 | POWER, SHEET 6                 |                            |

PM4354 COMET-QUAD

EVALUATOR BOARD PMC-1991237

ISSUE 2

COMET-QUAD EVALUATOR BOARD

| 15 | APPENDIX C: LAYOUT | <br>18  |

|----|--------------------|---------|

|    |                    | <br>••• |

EVALUATOR BOARD PMC-1991237

ISSUE 2

COMET-QUAD EVALUATOR BOARD

# LIST OF FIGURES

| FIGURE 1: WIRELESS BASE STATION APPLICATION                                     |

|---------------------------------------------------------------------------------|

| FIGURE 2: V5.2 INTERFACE APPLICATION                                            |

| FIGURE 3: BLOCK DIAGRAM 6                                                       |

| FIGURE 6: EXTERNAL ANALOG INTERFACE CIRCUIT FOR ONE CHANNEL 12                  |

| FIGURE 7: SYSTEM BUS CONNECTORS 15                                              |

| FIGURE 8: PCI UNIVERSAL 32-BIT CARD MECHANICAL OUTLINE                          |

| FIGURE 9: PCI UNIVERSAL 32-BIT CARD EDGE CONNECTOR DIMENSIONS<br>AND TOLERANCES |

| FIGURE 10- FACE PLATE                                                           |

| FIGURE 12: MAIN COMPONENT PLACEMENT DIAGRAM                                     |

| FIGURE 13: LAYER STACK                                                          |

| FIGURE 14: PCB CROSS SECTION                                                    |

| FIGURE 15: GND PLANE                                                            |

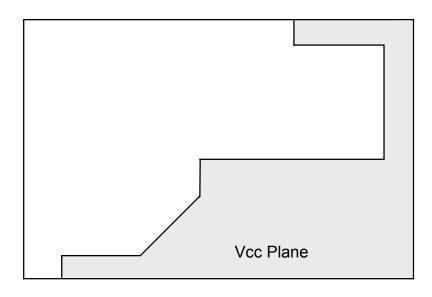

| FIGURE 16: VCC PLANE                                                            |

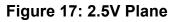

| FIGURE 17: 2.5V PLANE                                                           |

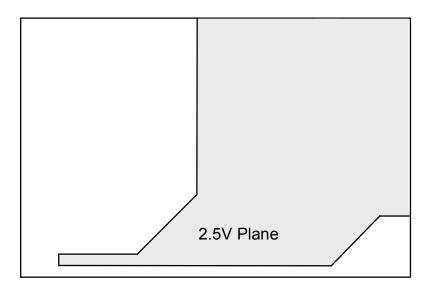

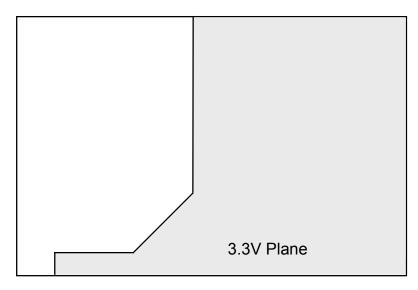

| FIGURE 18: 3.3V PLANE                                                           |

EVALUATOR BOARD PMC-1991237 PMC-Sierra, Inc.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

# LIST OF TABLES

| TABLE 1 PCI9050 LOCAL ADDRESS SPACE ALLOCATION       | 9 |

|------------------------------------------------------|---|

| TABLE 2: RJ-48C PINOUT 10                            | ) |

| TABLE 5: EXTERNAL COMPONENTS DESCRIPTION             | 3 |

| TABLE 6: COMET-QUAD LOOPBACK MODES 18                | 3 |

| TABLE 7: POWER ESTIMATES                             | ) |

| TABLE 8: SYSTEM MEMORY MAP 28                        | 3 |

| TABLE 9: PCI LOCAL ADDRESS SPACE REGISTER            | 3 |

| TABLE 10: PCI LOCAL ADDRESS SPACE                    | 3 |

| TABLE 11: PCI LOCAL ADDRESS SPACE RE-MAP             | 9 |

| TABLE 12: PCI LOCAL ADDRESS SPACE REGION DESCRIPTORS | 9 |

| TABLE 13: PCI CHIP SELECT BASE                       | Э |

| TABLE 14: PCI LOCAL ADDRESS SPACE REGISTERS          | ) |

| TABLE 15: PCB PARAMETERS                             | 5 |

| TABLE 16: MAJOR COMPONENTS LIST                      | 3 |

| TABLE 17: BILL OF MATERIALS                          | 3 |

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

# 1 INTRODUCTION

The COMET-QUAD Evaluator Board is part of the COMET-QUAD Evaluator Kit and allows for the evaluation and demonstration of PMC-Sierra's PM4354 COMET-QUAD device. It also provides a platform for the development and integration of software.

The COMET-QUAD Evaluator Board is configured, monitored, and powered through the PCI edge connector. Software drivers are available from PMC-Sierra, Inc. to fully control and utilize the COMET-QUAD Evaluator Board.

#### 1.1 Purpose

The COMET-QUAD Evaluator Board is designed to assist engineers in designing their products using PMC-Sierra's COMET-QUAD device. The purpose of this document, hence, is to provide a detailed hardware specification for the COMET-QUAD Evaluator Board. The specification detailed here is sufficient to allow design implementation and verification.

#### 1.2 Scope

This document describes the design for the COMET-QUAD Evaluator Board. A general description of the device is given, along with a block diagram for the design. A description for each of the functional blocks of the design is given followed by a detailed account of design issues, including physical and mechanical descriptions, implementation descriptions and layout.

#### 1.3 Application

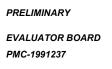

The COMET-QUAD device is suitable in the following applications:

- T1/E1 Wireless Digital Loop Carriers (DLC's) and Cellular Base Stations

- T1/E1 Internet Access Equipment

- T1/E1 Channel Service Units (CSU)

- T1/E1 Frame Relay Interfaces

- T1/E1 ATM Interfaces

- T1/E1 Multiplexers (CPE MUX)

COMET-QUAD EVALUATOR BOARD

- Digital Private Branch Exchanges (PBX)

- Digital Access Cross-Connect Systems (DACS) and Electronic DSX Cross-Connect Systems (EDSX)

- ISDN Primary Rate Interfaces (PRI)

- Test Equipment

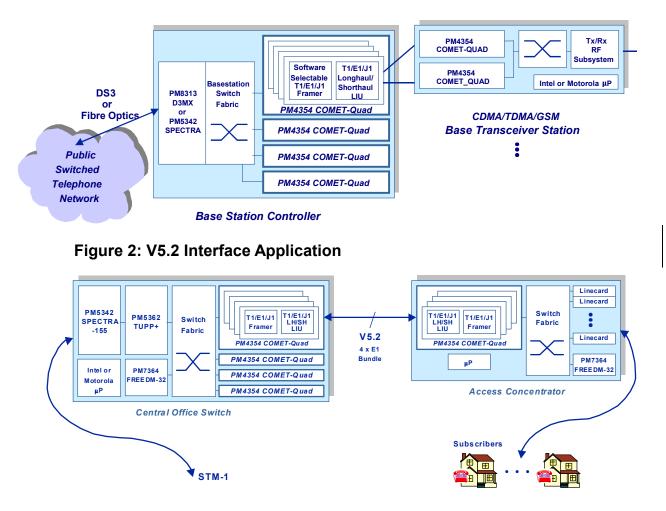

Figure 1 illustrates the COMET-QUAD device in a wireless base transceiver station (BTS) application and Figure 2 illustrates the device in a V5.2 Interface Application.

# Figure 1: Wireless Base Station Application

ISSUE 2

COMET-QUAD EVALUATOR BOARD

#### 2 FEATURES

#### General

- PCI Interface allows for microprocessor access to the COMET-QUAD via a host PC

- Provides a platform for the demonstration of the COMET-QUAD's functions and performance.

- Provides software-selectable E1, T1, J1 rate selection.

#### T1 Mode

- Interface to 4 short haul and long haul T1 lines

- Frames to ESF and SF formats

- Integral HDLC controller for Facilities Data Link Support

- Serial PCM interfaces to each framer to support 1.544 Mbit/s ingress/egress system interfaces

- Detect loss of signal, pulse density violation, Red alarm, Yellow alarm, and AIS alarm

- Performance monitoring with accumulation of CRC-6 errors, framing bit errors, line code violations, and loss of frame events

- Provides synchronous backplane systems 8Mbit/s H-MVIP interfaces for access channel associated signaling (CAS) and common channel signaling (CCS) for each line

- Per channel payload loopback

- Automatic gain control to accommodate distances with up to 36 dB of cable attenuation at nominal conditions using PIC 22 gauge cable emulation

- Programmable Line build outs of DSX-1 as well as CSU of –7.5dB, -15dB and –22dB

- Line interface capable of generating G.703 wave shapes for  $100\Omega$  T1 lines

COMET-QUAD EVALUATOR BOARD

Provides a programmable PRBS test pattern generator, receiver and analyzer.

#### E1 Mode

• Interface to 4 short haul and long haul E1 lines

**ISSUE 2**

- Frames to FAS, CAS and CRC-4 formats

- Integral HDLC controller for Facilities Data Link Support

- Detect loss of signal, loss of frame, loss of signaling multiframe and loss of CRC

- Performance monitoring with accumulation of CRC-4 errors, far end block errors, framing bit errors, and line code violation

- Provides synchronous backplane systems 8Mbit/s H-MVIP interfaces for access channel associated signaling (CAS) and common channel signaling (CCS) for each line

- Per channel payload loopback

- Automatic gain control to accommodate distances with up to 36 dB of cable attenuation at nominal conditions using PIC 22 gauge cable emulation

- Line interface capable of generating G.703 wave shapes for  $120\Omega$  E1 lines

- Provides a programmable PRBS test pattern generator, receiver and analyzer.

COMET-QUAD EVALUATOR BOARD

# 3 GENERAL DESCRIPTION OF THE COMET-QUAD EVALUATOR KIT

**ISSUE 2**

#### 3.1 The COMET-QUAD Evaluator Kit

The COMET-QUAD Evaluator Kit is a self-contained hardware and software reference design tool, designed to operate on a Pentium-based PC running Windows 95/98/2000/NT. The kit provides a platform for the engineers to develop and integrate software with a state-of-the-art T1/E1/J1 design.

#### 3.2 Hardware

The kit is supplied with a 4 channel COMET-QUAD Evaluator Board that has been developed to fit into a PCI-based desktop computer. This board consists of a PM4354 COMET-QUAD device, the necessary interface circuitry, magnetics, and line protection for long haul and short haul operation in either T1 or E1 mode. The board is configured, monitored, and powered through the PC's motherboard.

#### 3.3 Software

The kit contains an interactive program, complete with a graphical user interface (GUI), and a set of scripts to configure the COMET-QUAD device. The software, installed from the kit's CD-ROM, provides a visual interface to control and monitor the COMET-QUAD functions. Direct access to the COMET-QUAD device is provided to read or write any of the COMET-QUAD registers, perform a hardware reset of the COMET-QUAD, and observe the status of the hardware interrupt pin of the COMET-QUAD.

**ISSUE 2**

COMET-QUAD EVALUATOR BOARD

#### **BLOCK DESCRIPTION** 4

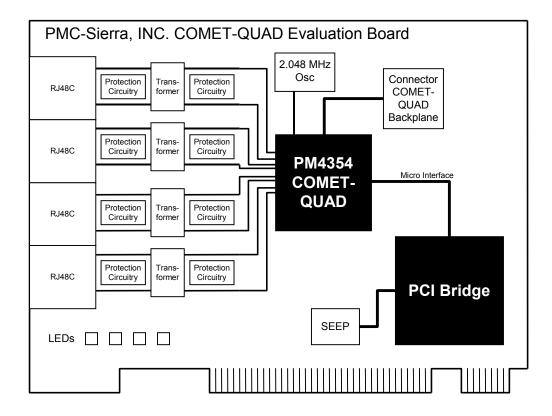

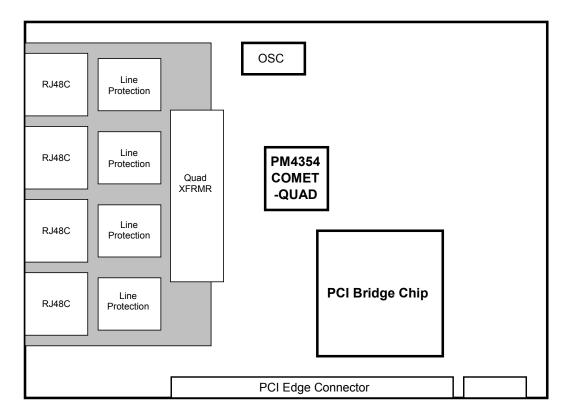

#### 4.1 **Block Diagram**

The following section describes in detail the function of each hardware block shown in Figure 3.

### Figure 3: Block Diagram

#### 4.2 COMET-QUAD

The PM4354 Four Channel Combined E1/T1/J1 Transceiver and Framer (COMET-QUAD) is a feature-rich monolithic integrated circuit suitable for use in long haul and short haul T1, J1 and E1 systems with a minimum of external circuitry. The COMET-QUAD is software configurable, allowing feature selection without changes to external wiring.

Analog circuitry is provided to allow direct reception of long haul E1 and T1 compatible signals with up to 36 dB cable loss (at 1.024 MHz in E1 mode) or up

ISSUE 2

COMET-QUAD EVALUATOR BOARD

to 36 dB cable loss (at 772 kHz in T1 mode) using a minimum of external components. Typically, only line protection, a transformer and a line termination resistor are required.

The COMET-QUAD recovers clock and data from the line and frames to incoming data. In T1 mode, it can frame to SF and ESF signal formats. In E1 mode, the COMET-QUAD frames to basic G.704 E1 signals and CRC-4 multiframe alignment signals, and automatically performs the G.706 interworking procedure. AMI, HDB3 and B8ZS line codes are supported.

The COMET-QUAD supports detection of various alarm conditions such as loss of signal, pulse density violation, Red alarm, Yellow alarm, and AIS alarm in T1 mode and loss of signal, loss of frame, loss of signaling multiframe and loss of CRC multiframe in E1 mode. The COMET-QUAD also supports reception of remote alarm signal, remote multiframe alarm signal, and alarm indication signal in E1 mode. The presence of Yellow and AIS patterns in T1 mode and remote alarm and AIS patterns in E1 mode is detected and indicated. In T1 mode, the COMET-QUAD integrates Yellow, Red, and AIS alarms as per industry specifications. In E1 mode, the COMET-QUAD integrates Red and AIS alarms.

Performance monitoring with accumulation of CRC-6 errors, framing bit errors, line code violations, and loss of frame events are provided in T1 mode. In E1 mode, CRC-4 errors, far end block errors, framing bit errors, and line code violation are monitored and accumulated.

The COMET-QUAD provides one receive HDLC controller per channel for the detection and termination of messages in the ESF facility data link (T1), national use bits (E1), or in any arbitrary timeslot (T1 or E1). In T1 mode, the COMET-QUAD also detects the presence of in-band loop back codes and ESF bit oriented codes. Detection and optional debouncing of the 4-bit Sa-bit codewords defined in ITU-T G.704 and ETSI 300-233 is supported. An interrupt may be generated on any change of state of the Sa codewords.

Dual (transmit and receive) elastic stores for slip buffering and rate adaptation to backplane timing are provided, as is a signaling extractor that supports signaling debounce, signaling freezing, idle code substitution, digital milliwatt tone substitution, data inversion, and signaling bit fixing on a per-channel basis. Receive side data and signaling trunk conditioning is also provided.

In T1 mode, the COMET-QUAD generates framing for SF and ESF formats. In E1 mode, the COMET-QUAD generates framing for a basic G.704 E1 signal. The signaling multiframe alignment structure and the CRC multiframe structure may be optionally inserted. Framing can be optionally disabled.

Internal analog circuitry allows direct transmission of long haul and short haul T1 and E1 compatible signals using a minimum of external components. Typically,

EVALUATOR BOARD PMC-1991237

ISSUE 2

COMET-QUAD EVALUATOR BOARD

only line protection, a transformer and an optional line termination resistor are required. Digitally programmable pulse shaping allows transmission of DSX-1 compatible signals up to 655 feet from the cross-connect, E1 short haul pulses into 120 ohm twisted pair or 75 ohm coaxial cable, E1 long haul pulses into 120 ohm twisted pair as well as long haul DS-1 pulses into 100 ohm twisted pair with integrated support for LBO filtering as required by the FCC rules. In addition, the programmable pulse shape extending over 5-bit periods allows customization of short haul and long haul line interface circuits to application requirements.

In the transmit path, the COMET-QUAD supports signaling insertion, idle code substitution, digital milliwatt tone substitution, data inversion, and zero code suppression on a per-channel basis. Zero code suppression may be configured to Bell (bit 7), GTE, or DDS standards, and can also be disabled. Transmit side data and signaling trunk conditioning is also provided. Signaling bit transparency from the backplane may be enabled.

The COMET-QUAD provides one transmit HDLC controller per channel. These controllers may be used for the transmission of messages in the ESF data link (T1), national use bits (E1), or in any timeslot (T1 or E1). In T1 mode, the COMET-QUAD can be configured to generate in-band loop back codes and ESF bit oriented codes. In E1 mode, transmission of the 4-bit Sa codewords defined in ITU-T G.704 and ETSI 300-233 is supported.

To provide for V5 applications where up to three HDLC channels are contained in each E1, the COMET-QUAD provides a CCS H-MVIP interface. This interface allows the HDLC channels to be inserted or extracted for external processing.

Each channel of the COMET-QUAD can generate a low jitter transmit clock from a variety of clock references, and also provides jitter attenuation in the receive path. A low jitter recovered T1 clock can be routed outside the COMET-QUAD for network timing applications.

Serial PCM interfaces to each T1/E1 framer allow 1.544 Mbit/s or 2.048 Mbit/s backplane receive/backplane transmit system interfaces to be directly supported. Tolerance of gapped clocks allows other backplane rates to be supported with a minimum of external logic.

For synchronous backplane systems, 8.192 Mbit/s H-MVIP interfaces are provided for access to PCM data, channel associated signaling (CAS) and common channel signaling (CCS) for each T1 or E1. The CCS signaling H-MVIP interface is independent of the 64 Kbit/s PCM and CAS H-MVIP access. The use of the H-MVIP interface requires that common clocks and frame pulse be used along with T1/E1 elastic stores.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

The COMET-QUAD is configured, controlled and monitored via a generic 8-bit microprocessor bus through which all internal registers are accessed. All sources of interrupts can be masked and acknowledged through the microprocessor interface.

For a complete description of the COMET-QUAD, please refer to PMC-Sierra's COMET-QUAD data sheet, PMC-1990315 [1].

### 4.3 PCI Bridge

The PCI Bridge used is PLX Technology's PCI9050 PCI Bus Target Interface Chip. The PCI9050 provides a target only interface, and as such does not initiate PCI bus transactions.

The PCI9050 has a 16 long word write FIFO and 8 long word read FIFO allowing the PCI bus to burst data to and from the COMET-QUAD. The local address space is configured to be 32-bit non-multiplexed, big endian, non-burst, and non-prefetchable. Even though the COMET-QUAD has only an 8-bit data bus, the PCI9050 is configured as a 32-bit data bus. This was done to simplify the hardware design. Prefetching is not possible in this application because the COMET-QUAD has a number of registers with read side affects (e.g. interrupt status registers).

The local bus is clocked at 33MHz by looping the buffered PCI clock output (BCLKO) available from the PCI9050 back to the local bus clock input.

The local address spaces are allocated in the following fashion:

| Address Space | Function             |

|---------------|----------------------|

| 0             | COMET-QUAD Registers |

| 1             | unused               |

| 2             | unused               |

| 3             | unused               |

#### Table 1 PCI9050 Local Address Space Allocation

Please refer to the PCI9050 datasheet [5] for more information.

#### <u>4.4 SEEP</u>

The NM93CS46 Serial EEPROM from National Semiconductor is used to store configuration information for the PCI9050 bridge. This specific SEEP (or

ISSUE 2

COMET-QUAD EVALUATOR BOARD

equivalent) is required by PCI9050 because it supports sequential read operations.

The SEEP is 1Kbit deep, 800 bits of which are occupied by the PCI9050 configuration data, leaving 224 bits (28 bytes) unused.

Refer to the PCI9050 datasheet [5] for information on the format of the configuration data stored in the SEEP.

### 4.5 Oscillators

The COMET-QUAD can run in either T1 or E1 mode. In T1 mode, oscillator Y1 should be populated with a 1.544 MHz oscillator. In E1 mode, oscillator Y1 should be populated with a 2.048 MHz oscillator. The COMET-QUAD can also optionally run in T1 mode with a 2.048 MHz oscillator.

#### 4.6 Transmit and Receive Line Interface

A transmit and receive line interface is required for each of the 4 channels.

Each transmit and receive line interface consists of line connectors, line protection circuitry and magnetics.

The magnetics used on this design is a quad package that contains both a receive and transmit transformer. Both the receive and transmit transformers have a 1:2.42 turns ratio with the "1" always on the chip side. Please refer to Table 16 for a list of manufacturers.

The evaluator board provides one set of line interface connectors, a RJ-48C, for the receive and transmit of T1/E1 signals to and from the COMET-QUAD device for each channel. The RJ48C has been provided according to the ANSI T1.403 standard for a Universal Service Ordering Code (USOC) connector. Table 2 below details the pinout for the RJ-48C connector.

| Pin | Signal |

|-----|--------|

| 1   | RXRING |

| 2   | RXTIP  |

| 3   | N.C.   |

| 4   | TXRING |

| 5   | TXTIP  |

#### Table 2: RJ-48C Pinout

EVALUATOR BOARD PMC-1991237 PMC PMC-Sierra, Inc.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

| 6 | N.C. |

|---|------|

| 7 | N.C. |

| 8 | N.C. |

#### 4.7 Line Termination

The line interface provides one termination scheme for both T1 and E1 rates. A termination of  $110\Omega$  is used to allow the interface to be compatible with both  $100\Omega$  T1 and  $120\Omega$  E1. This provides a software switchable reference board for both T1 and E1 by simply configuring the COMET-QUAD device.

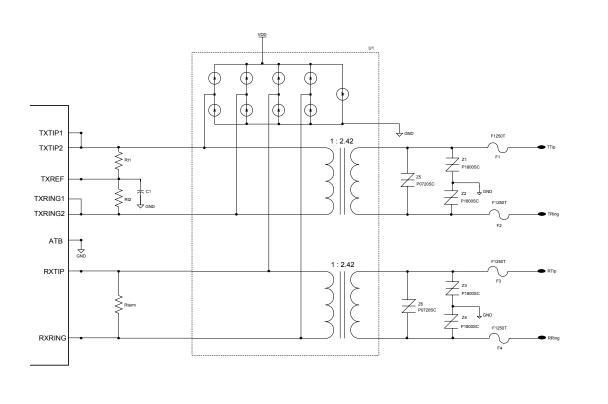

#### 4.8 Protection Circuitry

The protection circuitry prevents damage to telecommunications equipment caused by over-voltage and over-current power surges due to lightning strikes and AC power cross disturbances.

The circuit is composed of two sections. The primary circuit protection consists of circuit protection for digital transmission equipment. The circuit is a proven solution that is currently used in the industry today. The configuration has passed Bellcore GR 1089-CORE, FCC Part 68 and UL 1459 & 1950.

The TECCOR F1250T Telelink Fuse used in combination with the TECCOR P1800SC SIDACtor and P0720SC SIDACtor provide a solution for the regulatory requirements without the use of any additional series resistance. The two fuses provide over current protection and the three SIDACtors provide over voltage protection.

The SIDACtors provide transient over voltage protection. In the standby mode, the device exhibits high off-state impedance eliminating excessive leakage currents and appears transparent to the circuits they protect. When the voltage across the device exceeds the switching voltage, SIDACtors will crowbar and simulate a short circuit. During this state, current gets driven into the ground, thereby reducing some of the voltage that shows across the transformer and eventually at the equipment. The device stays in this state until the current flowing through the SIDACtor falls below the holding current of the device. When this occurs, the device resets and returns to its' high off-state impedance.

Secondary protection is provided using a combination of transformers and a diode array. The quad transformer with diode array module from Pulse further clamps any voltages.

EVALUATOR BOARD PMC-1991237

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

The transformers provide 1500Vrms line isolation and serves to impedance match the lines to the transceiver line interface. Any remaining high positive or high negative voltage signals are further clamped by the diode array configuration. If the positive voltage signal is larger than the reference voltage plus the diode voltage, then the top diode becomes forward biased and steers the excess voltage into the power supply. If the negative voltage signal exceeds the diode voltage, then the bottom diode becomes forward biased and directs the excess negative voltage signals to ground. The transformer with diode array module chosen for this application is a quad package that contains one set of receive and transmit transformer and diode array for each of the four channels.

Figure 6 shows an external protection circuit for designs required to meet major surge immunity and electrical safety standards including Bellcore GR 1089-CORE, FCC Part 68 and UL 1459 & 1950. This circuit uses a part from Pulse that combines eight transformers (4 transmit and 4 receive) and the diode array module (equivalent to the diode array provided by Semtech) into a single module. This is an alternative way of implementing the circuit while reducing the number of required components.

# Figure 6: External Analog Interface Circuit for One Channel

PM4354 COMET-QUAD

**ISSUE 2**

COMET-QUAD EVALUATOR BOARD

# Table 5: External Components Description

| Component                               | Description                                                                                                                     | Part Number           | Source  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------|

| Rt1 & Rt2                               | Typically 12.7 $\Omega \pm 1\%$ Resistors                                                                                       |                       |         |

| Rterm                                   | 18.2 $\Omega$ ±1% Resistor for T1 & 120 $\Omega$ E1 13 $\Omega$ ±1% Resistor for 75 $\Omega$ E1 (assuming a 1:2.42 transformer) |                       |         |

| C1                                      | 4.7µF±10% Capacitor                                                                                                             |                       |         |

| F1 – F4                                 | Surge Resistant, Time Lag<br>Fuse                                                                                               | F1250T Telelink       | Teccor  |

| Z1 – Z4                                 | Bi-directional Transient Surge<br>Protectors                                                                                    | P1800SC               | Teccor  |

| Z5, Z6                                  | Bi-directional Transient Surge<br>Protectors                                                                                    | P0720SC               | Teccor  |

| D1                                      | Surge Protector Diode Array                                                                                                     | SRDA3.3-4             | Semtech |

| T1&T2                                   | Generally 1:2.42CT                                                                                                              | 50436 (single)        | Midcom  |

|                                         | Transformers                                                                                                                    | T1137                 | Pulse   |

|                                         |                                                                                                                                 | TG23-1505NS           | Halo    |

|                                         |                                                                                                                                 | (single)              | Halo    |

|                                         |                                                                                                                                 | TG23-1505N1<br>(dual) |         |

| U1 (replaces<br>both D1 and<br>T1 & T2) | Combined 1:2.42CT Transmit<br>(quantity=4) and Receive<br>(quantity=4) Transformers and<br>Surge Protector Diode Array          | T9021                 | Pulse   |

# 4.9 Power Supply

The COMET-QUAD evaluator design contains components that operate at 2.5V, 3.3V, or 5V, referenced to ground. The 5V supply is provided to the board through the PCI connector. The 2.5V and 3.3V supply is generated on the board via DC-DC voltage regulators.

**ISSUE 2**

PM4354 COMET-QUAD

COMET-QUAD EVALUATOR BOARD

It is recommended that 5V power is provided before both 2.5V and 3.3V power to avoid device latchup. Please refer to the COMET-QUAD datasheet [1] for further details of powering up the COMET-QUAD device.

# 4.10 PCI Edge Connector

The PCI Edge Connector has been implemented as a standard Universal, 32 bit PCI connector. The system board designer must leave all reserved and Vio pins unconnected as voltage rail safety precautions. The universal expansion board is capable of detecting the signaling environment in use, and adapting itself to that environment accordingly. It can be plugged into either 3.3V or 5.0V connector type.

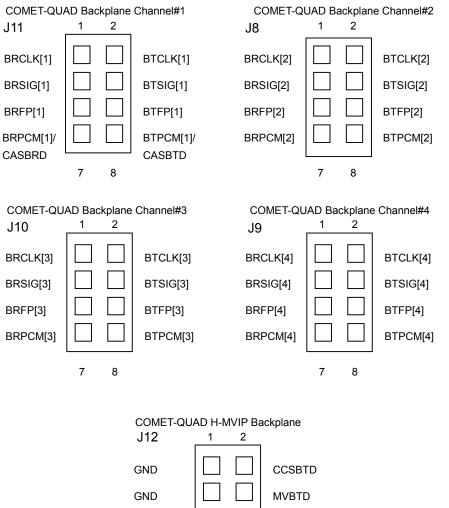

# 4.11 Backplane Bus Connector

The Backplane bus connectors, as shown in Figure 7, provide system side serial clock and data access as well as H-MVIP access for up to four T1 or E1 streams to the COMET-QUAD. This is provided to allow for easy access to the backplane signals. By simply connecting across the jumpers(connecting pins 1 to 2, 3 to 4, etc), the backplane channel connectors also allow for easy configuration of external payload loopback. The H-MVIP backplane connectors, on the other hand, provide useful input/output test ports for testing the system signals.

Note that when in H-MVIP mode, BTPCM[1] and BRPCM[1] act as CASBTD and CASBRD respectively.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

#### Figure 7: System Bus Connectors

MVBRD\_CCSBRD

CMV8MCLK

8

7

CMVFPB

CMVFPC

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

### 5 DESIGN ISSUES

The following sections describe design considerations of the evaluator board.

#### 5.1 COMET-QUAD Design Considerations

#### 5.1.1 Power Supply

Analog power pins must be applied after VDD or they must be current limited to the maximum latch-up current of 100mA. A simple solution is to use a small filtering network between the VDD and the analog power pins to delay power to each AVD pin.

#### 5.1.2 Decoupling

A 0.01 $\mu$ F capacitor is required for every two digital power pins, placed between alternating power and ground. A 0.1 $\mu$ F capacitor required for every two digital power pins, placed between alternating power and ground. The capacitors should be placed as close to the actual pin as possible.

The AVD pins require a filtering network between the GND plane and the 3.3V plane. The network is a single RC network with the resistor between the 3.3V plane and the AVD pin and the capacitor from the AVD pin to the GND plane. Please refer to the schematics and bill of materials for component values.

#### 5.1.3 Internal FDL Transmitter

It is important to note that access rate to the TDPR registers is limited by the rate of the XCLK crystal clock input. Consecutive accesses to the TDPR Configuration, TDPR Interrupt Status/UDR Clear, and TDPR Transmit Data register should be accessed (with respect to WRB rising edge and RDB falling edge) at a rate no faster than the XCLK clock rate. (In T1 mode with a 2.048 MHz XCLK reference, accesses should be no faster than XCLK x 193/256.) This time is used by XCLK to sample the event, write the FIFO, and update the FIFO status. Instantaneous variations in the XCLK clock frequency (e.g. jitter in XCLK) must be considered when determining the procedure used to read and write the TDPR registers.

Upon reset of the COMET-QUAD, the TDPR should be disabled by setting the EN bit in the TDPR Configuration Register to logic 0 (default value). An HDLC all-ones idle signal will be sent while in this state. The TDPR is enabled by setting the EN bit to logic 1. The FIFOCLR bit should be set and then cleared to initialize the TDPR FIFO before the TDPR is ready to transmit.

COMET-QUAD EVALUATOR BOARD

# 5.1.4 Internal Data Link Receiver

It is important to note that the access rate to the RDLC registers is limited by the rate of the XCLK crystal clock input. Consecutive accesses to the RDLC Status and RDLC Data registers should be accessed (with respect to WRB rising edge and RDB falling edge) at a rate no faster than 8/10 that of the XCLK clock rate. (In T1 mode with a 2.048 MHz XCLK reference, accesses should be no faster than XCLK x (193 x 8)/2560.) This time is used by XCLK to sample the event and update the FIFO status. Instantaneous variations in the XCLK clock frequency (e.g. jitter in XCLK) must be considered when determining the procedure used to read RDLC registers.

On power up of the system, the RDLC should be disabled by setting the EN bit in the Configuration Register to logic 0 (default value). The RDLC Interrupt Control register should then be initialized to enable the INTB output and to select the FIFO buffer fill level at which an interrupt will be generated. If the INTE bit is not set to logic 1, the RDLC Status register must be continuously polled to check the interrupt status (INTR) bit.

# 5.1.5 Per-Channel Serial Controllers

Proper initialization of the internal registers must be performed to eliminate erroneous control data from being produced on the outputs of the TPSC (RPSC) block. The output control streams should be disabled by setting the PCCE bit in the TPSC (RPSC) Configuration Register to logic 0. Then, all 96 locations of the TPSC (RPSC) must be filled with valid data. Finally the output streams can be enabled by setting the PCCE bit in the TPSC (RPSC) Configuration Register to 1.

Direct access mode to the TPSC or RPSC is not used in the COMET-QUAD. However, direct access mode is selected by default whenever the COMET-QUAD is reset. The IND bit within the TPSC and RPSC Configuration Registers must be set to logic 1 after a reset is applied.

# 5.1.6 T1/E1 Framer Loopback Modes

The COMET-QUAD provides four loopback modes to aid in network and system diagnostics. The network loopbacks (Payload and Line) can be initiated at any time via the  $\mu$ P interface, but are usually initiated once an inband loopback activate code is detected. The system Diagnostic Digital loopback can be initiated at any time by the system via the  $\mu$ P interface to check the path of system data through the framer. The Per-DS0 loopback permits the payload to be looped-back on a per-DS0 basis to allow network testing without taking an entire link off-line. Please refer to Table 6 for a summary of the loopback

ISSUE 2

COMET-QUAD EVALUATOR BOARD

operations. Note that only one of Payload Loopback, Line Loopback and Diagnostic Digital Loopback can be enabled at any one time.

## Table 6: COMET-QUAD Loopback Modes

| Loopback Mode                  | Addr                    | Register                       | Bit    | Set     |

|--------------------------------|-------------------------|--------------------------------|--------|---------|

| Line Loopback                  | 00AH,10AH,<br>20AH,30AH | Master Diagnostics<br>Register | LINELB | Logic 1 |

| Payload Loopback               | 00AH,10AH,<br>20AH,30AH | Master Diagnostics<br>Register | PAYLB  | Logic 1 |

| Per-Channel Loopback           | 06FH,16FH,<br>26FH,36FH | TPSC Internal Register         | LOOP   | Logic 1 |

| Per-Channel Loopback           | 06CH,16CH,<br>26CH,36CH | TPSC Configuration<br>Register | PCCE   | Logic 1 |

| Diagnostic Digital<br>Loopback | 00AH,10AH,<br>20AH,30AH | Master Diagnostics<br>Register | DDLB   | Logic 1 |

# 5.2 PCI Bridge

# 5.2.1 Dual Environment Compliance

The PCI-9050 must use I/O buffers that can be compliant with either the 5.0V or 3.3V signaling environment. While there are multiple buffer implementations that can achieve this dual environment compliance, it is intended that they be dual voltage buffers – i.e. capable of operating from either power rail. They should be powered from "I/O" designated power pins on PCI connectors that will always be connected to the power rail associated with the signaling environment in use. This means that in the 5.0V signaling environment, these buffers are powered on the 5.0V rail. When the board is plugged into a 3.3V connector, these buffers are powered on the 3.3V rail. This enables the COMET-QUAD Evaluator Board to be compliant with either signaling environment.

# 5.2.2 PCI 9050 Initialization

The PCI-9050 is used in the Evaluator Board to provide a compact high performance PCI bus target (slave) interface to the PCI bus.

During power up, the PCI RST# signal resets the default values of the PCI 9050-1 internal registers. In return, the PCI 9050 outputs the local reset signal (LRESET#) and checks for the existence of the serial EEPROM. If a serial EPROM is installed, and the first 16-bit word is not FFFF, the PCI 9050 loads the

**ISSUE 2**

PM4354 COMET-QUAD

COMET-QUAD EVALUATOR BOARD

internal registers from the serial EEPROM. Otherwise, default values are used. The PCI 9050 configuration registers can be written only by the optional serial EEPROM or the PCI host processor. During the serial EEPROM initialization, the PCI 9050 response to PCI target accesses is RETRYs.

### 5.2.3 Internal Register Access

The PCI 9050 chip provides several internal registers, allowing maximum flexibility in bus interface design and performance. All of the PCI and the local configuration registers are accessible from the PCI bus and EEPROM.

### 5.2.4 Direct Data Transfer Modes

The PCI host processor can directly access devices on the local bus for reads and writes. Configuration registers within the PCI 9050 control decoding and remapping of these accesses to local address space.

### 5.3 Line Protection

Line protection circuitry is implemented to protect the Evaluator Board from damage caused by over-voltage and over-current power surges due to lightning strikes and power cross disturbances.

Using the combination of the F1250T Telelink fuse, the P1800SC SIDACtor and the P0720SC SIDACtor eliminates the need for additional series line resistance. The elimination of the additional resistance allows the signal to maintain its' integrity. The resistance of the F1250T Telelink fuse is  $0.109\Omega \pm 15\%$ . The low resistance results in negligible signal degradation, which allows the signal to remain within the required pulse shape template. Another advantage resulting from the removal of additional series line resistance is that it enables longer loop lengths. Adding the F1250T fuse is an economical solution. The fuse eliminates the need for costly power resistors and PTCs.

Adding the P1800SC and P0720SC SIDACtors results in absolute surge protection regardless of the available surge current and the rate of applied voltage (dV/dt). The SIDACtor also can not be damaged by voltage, eliminates hysteresis and heat dissipation typically found with a clamping device, eliminates voltage overshoot caused by fast rising transients, and has negligible capacitance. The fuse is robust enough to live through lightning surges without causing unwanted openings, but interrupts correctly during situations involving power cross. The P1800SC SIDACtors are chosen because of the switching voltage of 220V.

ISSUE 2

COMET-QUAD EVALUATOR BOARD

The diode array protects high-speed data interfaces from over voltages caused by ESD (electrostatic discharge), EFT (electrical fast transients), and lightning. During transient conditions, the diodes steer the transient to either the positive side of the power supply line or to the ground. The TVS diode used in the array is very important because it prevents over voltage on the power line, thereby protecting components that exist further down the line. Also, the capacitance of the diode array from Semtech has a very low capacitance (<15pF). Since the driving capacity of the transmitter can not handle a large load, this diode array is very suitable. The combination of the transformers and a built in diode array from Pulse was chosen because they have made a diode array obtaining low capacitance.

#### 5.4 Jumper Configuration

Jumpers are used at the system bus connector to manually configure external payload loopback of the Evaluator Board.

#### 5.5 Power Estimates

|                   | Power (Watts) | Current (mA) |

|-------------------|---------------|--------------|

| +2.5V             |               |              |

| COMET-QUAD        | 0.300         | 120          |

| +3.3V             |               |              |

| COMET-QUAD        | 1.7           | 500          |

| 2.5V Regulator    | 1.5           | 160          |

| +5V               |               |              |

| PLX 9050          | 0.650         | 130          |

| MAX 701           | 0.005         | 1            |

| 74HC08            | 0.005         | 1            |

| NM93CS46 (EEPROM) | 0.005         | 1            |

| Misc              | 1             | 200          |

#### Table 7: Power Estimates

PM4354 COMET-QUAD

EVALUATOR BOARD PMC-1991237

ISSUE 2

COMET-QUAD EVALUATOR BOARD

| TOTAL 1.665 333 |

|-----------------|

|-----------------|

# 5.6 Voltage Regulators - Current and Thermal Calculations

Power Dissipation in the Regulators:

For 2.5V Regulator:

Using worst case,

$$V_{out} = 2.5 - 2\% = 2.45V$$

I<sub>out</sub> = 160mA x 100% (for safety) = 320mA

Therefore, the dissipated power at the junction is,

$$P_{j} = (V_{in} - V_{out}) (I_{out}) + (V_{in}) (I_{gnd})$$

$$= (3.465 - 2.45) (320) + (3.465) (2)$$

$$= 0.3248 + 0.0069$$

= 0.332 W

Assumptions:

- maximum junction temperature = 125°C

- ambient temperature (no airflow) = 70°C

Therefore,

$$T_{jmax} - T_{ja} = P_d \times \phi$$

$$125 - 70 = 0.332 \times \phi$$

$$\phi = 166 \text{ °C/W}$$

for a 500 mm<sup>2</sup> of copper,  $\phi \cong 60 \text{ °C/W}$

$$P_d x \phi = 0.332 x 60 = 19.9^{\circ}C$$

EVALUATOR BOARD PMC-1991237 PMC PMC-Sierra, Inc.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

$$T_{jmax} = T_{ja} + (P_d \times \phi)$$

= 90°C

Therefore, a 500 mm<sup>2</sup> area of copper is sufficient to dissipate the heat.

In the 3.3V Regulator:

Using worst case,

Vin =

$$5 + 10\% = 5.5V$$

Vout =  $3.3 - 5\% = 3.135V$

lout =  $460mA \times 100\%$  (for safety) =  $920mA$

Therefore, the dissipated power at the junction is,

$$P_{j} = (V_{in} - V_{out}) (I_{out}) + (V_{in}) (I_{gnd})$$

= (5.5 - 3.135) (920mA) + (5.5) (2509mA)

= 2.176 + 1.375

= 3.6 W

Assumptions:

- maximum junction temperature = 125°C

- ambient temperature (no airflow) = 70°C

Therefore,

$$T_{jmax} - T_{ja} = P_d \ge \phi$$

$125 - 70 = 3.6 \ge \phi$

$\phi = 15.28 \text{ °C/W}$

for a 5000 mm<sup>2</sup> of copper,  $\phi \cong 15$

$P_d \ge \phi = 3.7 \ge 15 = 55 \text{ °C}$

$$T_{jmax} = T_{ja} + (P_d \times \phi)$$

°C/W

EVALUATOR BOARD PMC-1991237

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

= 70 + 55

= 125°C

Therefore, a 5000 mm<sup>2</sup> area of copper is sufficient to dissipate the heat.

Therefore, the total copper needed is  $5000 \text{ mm}^2 + 500 \text{ mm}^2 = 5500 \text{ mm}^2$ . Note that the area of copper on the ground and power planes is more than the required amount.

ISSUE 2

#### 6 PHYSICAL AND MECHANICAL DESCRIPTIONS

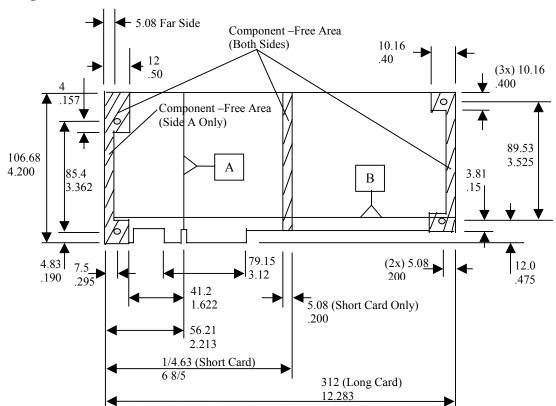

#### 6.1 Form Factor

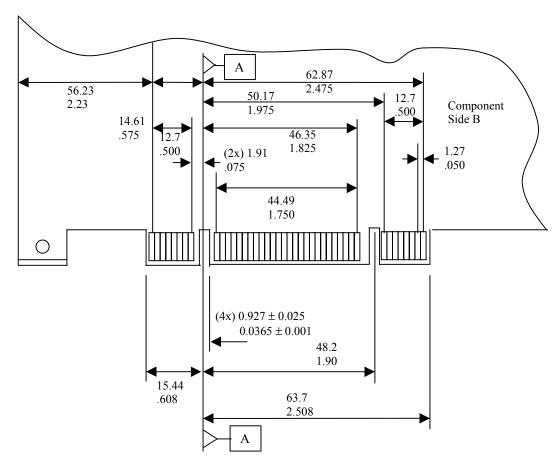

The following figures show the mechanical outline and dimensions of the COMET-QUAD Evaluator Board design.

Figure 8: PCI Universal 32-bit Card Mechanical Outline

EVALUATOR BOARD PMC-1991237

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

EVALUATOR BOARD PMC-1991237

PM4354 COMET-QUAD

COMET-QUAD EVALUATOR BOARD

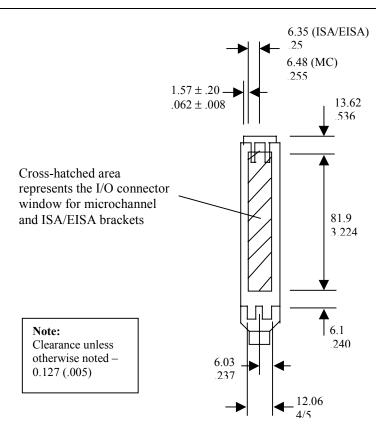

# Figure 9: PCI Universal 32-bit Card Edge Connector Dimensions and Tolerances

**ISSUE 2**

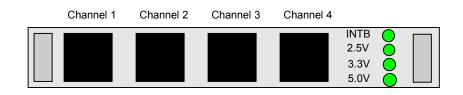

# 6.1.1 Face Plate

The following figure shows the proposed faceplate for the COMET-QUAD Evaluator Board design.

# Figure 10 - Face Plate

ISSUE 2

COMET-QUAD EVALUATOR BOARD

#### 6.2 Connectors

#### 6.2.1 Line Interface Connectors

Only one set of line interface connectors is provided with the evaluator board. These are the RJ48C connectors. Shielded jacks are used to help reduce EMI radiation and increase EMI tolerance.

#### 6.2.2 System Bus Connector

The System Bus Connector allows access to configure the COMET-QUAD and control the external payload loopback.

#### 6.2.3 PCI Edge Connector

The PCI Edge Connector is a standard Universal, 32 bit PCI connector.

#### <u>6.3 LEDs</u>

#### 6.3.1 COMET-QUAD Interrupt LED

A PCB mounted LED is connected to the INTB pin to allow for visual indication of interrupts being generated by the COMET-QUAD.

• INTB, green – indicates presence of interrupts

#### 6.3.2 Power Status LEDs

Three LEDs are provided to display the status of power to the COMET-QUAD board, one for 5.0V, one for 3.3V, and one for 2.5V.

- +5V, green indicates presence of +5V

- +3.3V, green indicates presence of +3.3V

- +2.5V; green indicates presence of +2.5V

ISSUE 2

COMET-QUAD EVALUATOR BOARD

# 7 SOFTWARE INTERFACES

#### 7.1 Memory Map

#### Table 8: System Memory Map

| PCI9050 Local<br>Address Space | Address   | Device                | R/W | Description             |

|--------------------------------|-----------|-----------------------|-----|-------------------------|

| CS_0                           | 0000-00FF | PM4354 COMET-<br>QUAD | R/W | COMET-QUAD<br>Registers |

#### 7.2 PCI 9050 Configuration

The following sets of tables specify the values that should be programmed into the SEEP. These values will be loaded into the PCI9050 registers on power-up. Please refer to the PCI9050 datasheet [5] for further details.

NOTE: The checksum of the SEEP is 0x230D.

#### Table 9: PCI Local Address Space Register

| Register | Address | Description                                    | Value      |

|----------|---------|------------------------------------------------|------------|

| PCIIDR   | 0x000   | Device_ID/Vendor_ID                            | 0x905010B5 |

| PCIREV   | 0x004   | Class_Code                                     | 0x06800000 |

| PCISVID  | 0x008   | Subsystem_ID/Subsystem_Vendor_ID               | 0x000311F8 |

| PCIILAR  | 0x00C   | Maximum Latency MinimumGrant<br>IntPin Routing | 0x00000000 |

#### Table 10: PCI Local Address Space

| Register | Address | Description                 | Value      |

|----------|---------|-----------------------------|------------|

| LAS0RR   | 0x010   | Local_Address_Space_0_Range | 0x0FFFFC00 |

| LAS1RR   | 0x014   | Local_Address_Space_1_Range | 0x00000000 |

| LAS2RR   | 0x018   | Local_Address_Space_2_Range | 0x00000000 |

| LAS3RR   | 0x01C   | Local_Address_Space_3_      | 0x00000000 |

| EROMRR   | 0x020   | Expansion_ROM_Range         | 0x00000000 |

ISSUE 2

COMET-QUAD EVALUATOR BOARD

# Table 11: PCI Local Address Space Re-Map

| Register | Address | Description                                  | Value      |

|----------|---------|----------------------------------------------|------------|

| LAS0BA   | 0x024   | LocalAddressSpace_0_Base_Addr<br>ess(Re-Map) | 0x00000001 |

| LAS1BA   | 0x028   | LocalAddressSpace_1_Base_Addr<br>ess(Re-Map) | 0x00000000 |

| LAS2BA   | 0x02C   | LocalAddressSpace_2_Base_Addr<br>ess(Re-Map) | 0x00000000 |

| LAS3BA   | 0x030   | LocalAddressSpace_3_Base_Addr<br>ess(Re-Map) | 0x00000000 |

| EROMBA   | 0x034   | Expansion_ROM_Base_Address(<br>Re-Map)       | 0x0000000  |

### Table 12: PCI Local Address Space Region Descriptors

| Register    | Address | Description                                   | Value      |

|-------------|---------|-----------------------------------------------|------------|

| LAS0BRD     | 0x038   | LocalAddressSpace0_Bus_Region<br>_Descriptors | 0x1681A1A0 |

| LAS1BRD     | 0x03C   | LocalAddressSpace1_Bus_Region<br>_Descriptors | 0x0000000  |

| LAS2BRD     | 0x040   | LocalAddressSpace2-<br>Bus_Region_Descriptors | 0x00000000 |

| LAS3BRD     | 0x044   | LocalAddressSpace3_Bus_Region<br>-Descriptors | 0x00000000 |

| EROMBR<br>D | 0x048   | Expansion_ROM_Bus_Region_De scriptors         | 0x0000000  |

### Table 13: PCI Chip Select Base

| Register | Address | Description        | Value      |

|----------|---------|--------------------|------------|

| CS0BASE  | 0x04C   | Chip_Select_0_Base | 0x00010001 |

| CS1BASE  | 0x050   | Chip_Select_1_Base | 0x0000000  |

| CS2BASE  | 0x054   | Chip_Select_2_Base | 0x0000000  |

| CS3BASE  | 0x058   | Chip_Select_3_Base | 0x0000000  |

ISSUE 2

COMET-QUAD EVALUATOR BOARD

# Table 14: PCI Local Address Space Registers

| Register | Address | Description                   | Value      |

|----------|---------|-------------------------------|------------|

| INTCSR   | 0x05C   | Interrupt_Control/Status      | 0x00000041 |

| CNTRL    | 0x060   | User_I/O  EEPROM Init_Control | 0x00024492 |

| NULL     | 0x064   | Null_data                     | 0xFFFFFFFF |

| NULL     | 0x068   | Null_data                     | 0xFFFFFFFF |

| NULL     | 0x06C   | Null_data                     | 0xFFFFFFFF |

| NULL     | 0x070   | Null_data                     | 0xFFFFFFFF |

| NULL     | 0x074   | Null_data                     | 0xFFFFFFFF |

| NULL     | 0x078   | Null_data                     | 0xFFFFFFFF |

| NULL     | 0x07C   | Null_data                     | 0xFFFFFFF  |

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

### 8 CONFORMANCE SPECIFICATION

The Evaluator Board utilizes PCI 9050-1, which is compliant with PCI Local Bus Specification 2.1 [6], supporting low cost slave adapters. The chip allows simple conversion of ISA adapters to PCI.

The design of the Evaluator Board, including the external protection circuitry, are designed to meet the major surge immunity and electrical safety standards including FCC Part 68, UL1459 and 1950, and Bellcore TR-NWT-001089. Note that this board has not been tested yet.

EVALUATOR BOARD PMC-1991237

ISSUE 2

COMET-QUAD EVALUATOR BOARD

# 9 LAYOUT DESCRIPTION

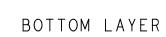

#### 9.1 Component Placement

The overall placement strategies of the components are:

- Place the analog circuitry away from the digital circuitry.

- Keep analog transmit side components separate from the analog receive side components.

- The PCI Bridge device is placed such that all the PCI interface traces are within the specified length limits of the PCI Rev. 2.1 Specification.

- The oscillator is placed in a quiet digital section as noise on its power supply will cause jitter on the output, and the oscillator itself generates noise that may affect sensitive analog circuits.

- All source termination resistors are placed near the outputs and load termination resistors are placed near the inputs.

- All pull up/down resistors are placed near the output pins.

- All decoupling capacitors are placed near the power supply pins.

The overall placement is as follows:

EVALUATOR BOARD PMC-1991237 PMC PMC-Sierra, Inc.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

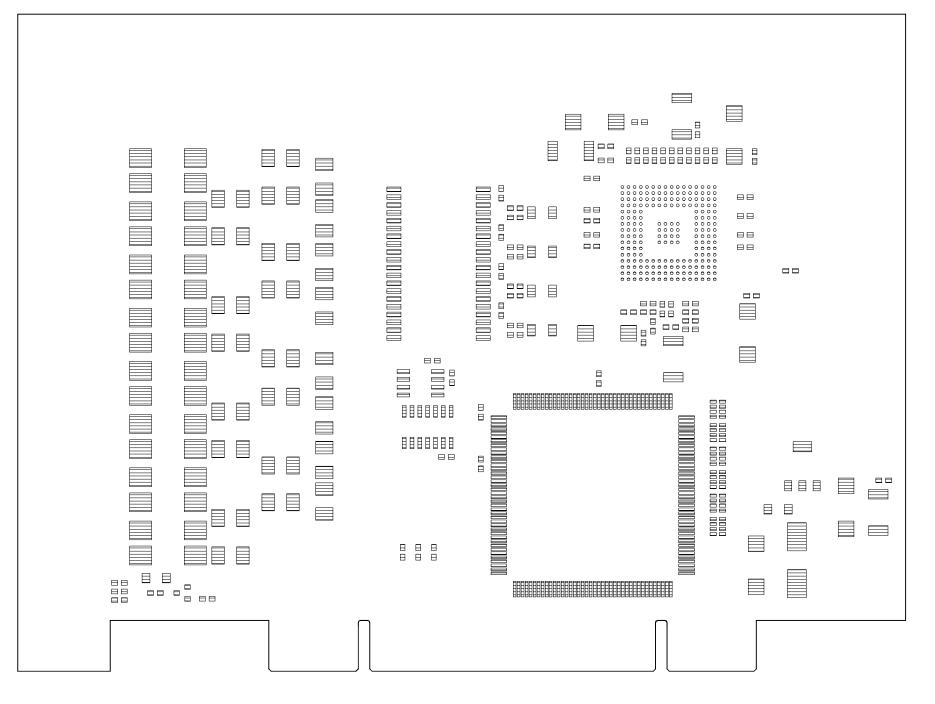

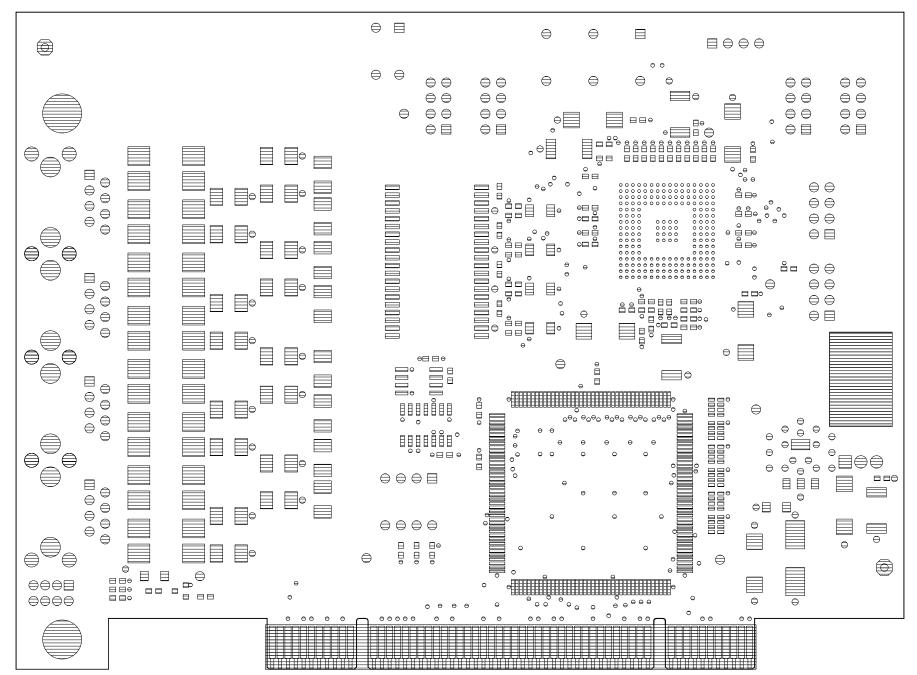

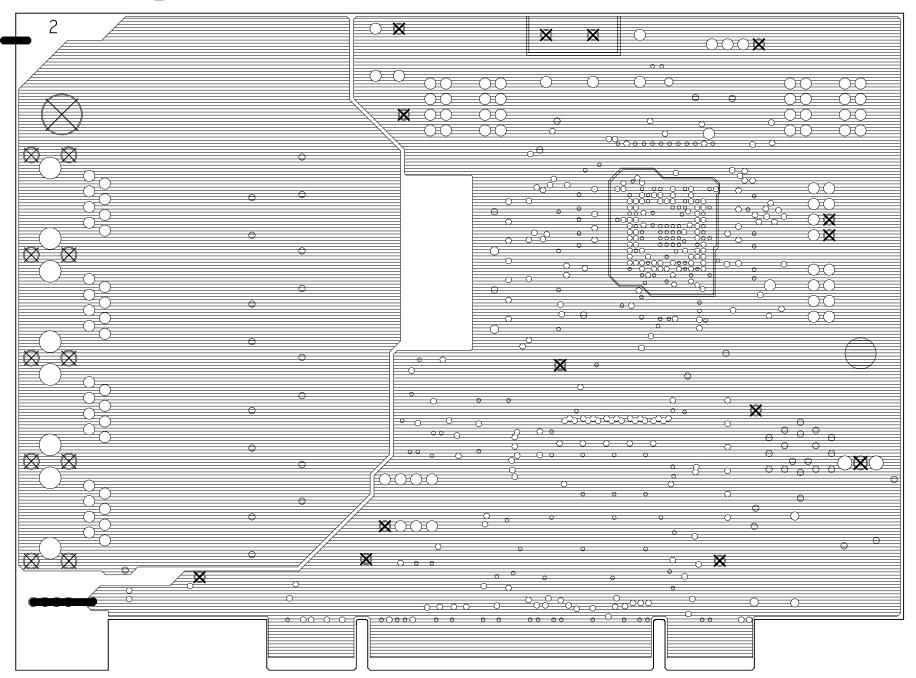

### Figure 12: Main Component Placement Diagram

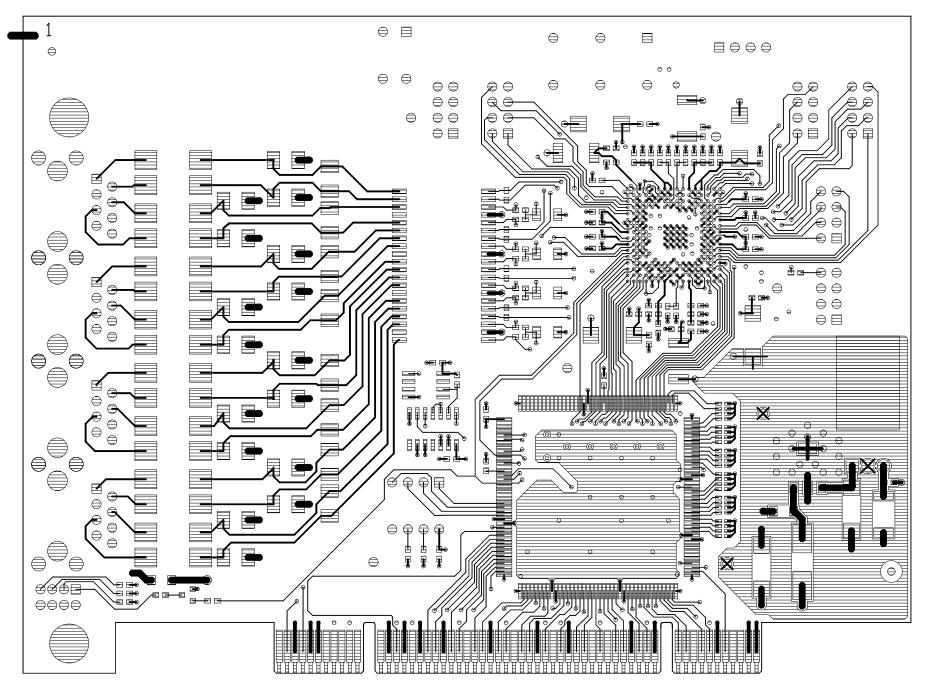

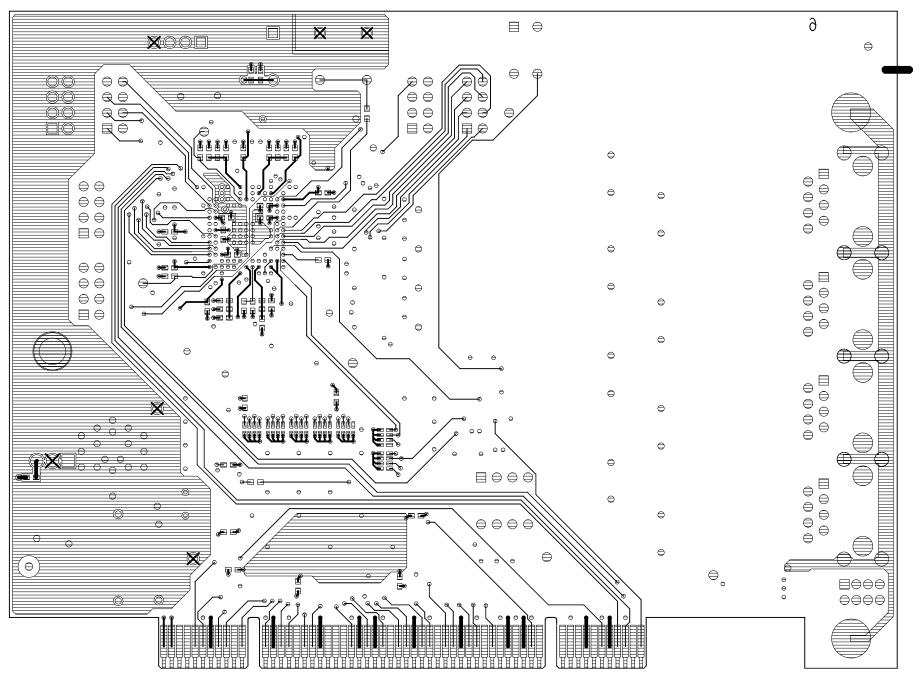

### 9.2 Layer Stacking and Transmission Line Impedance Control

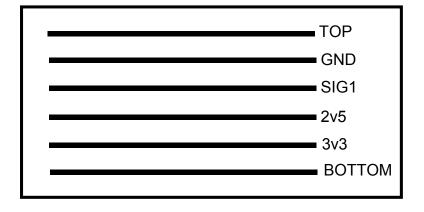

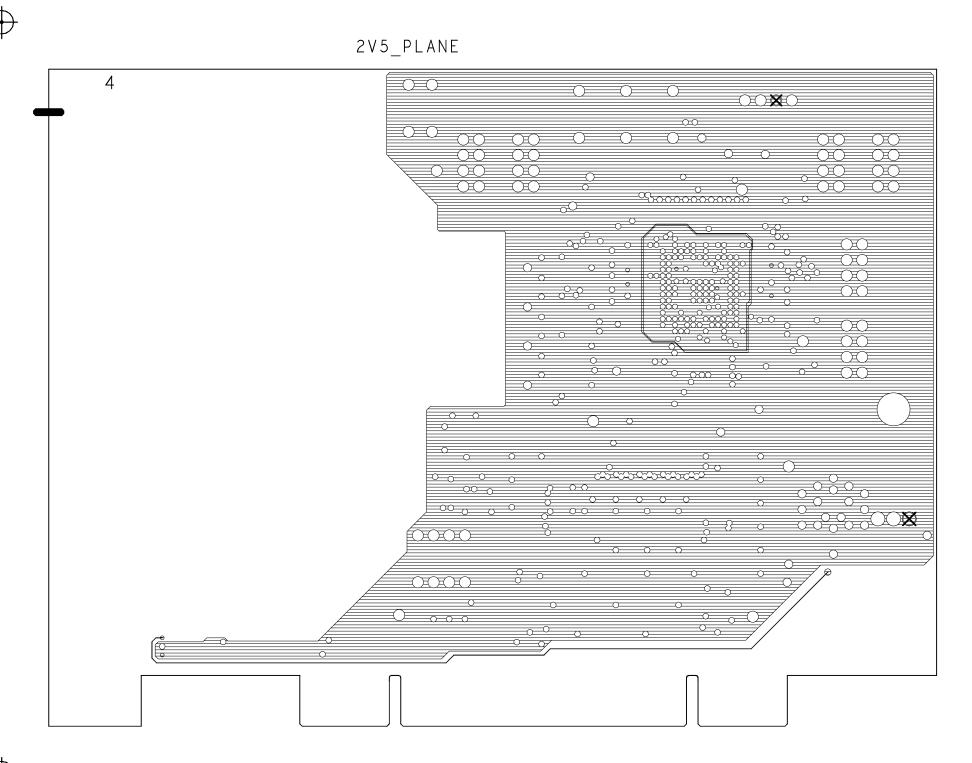

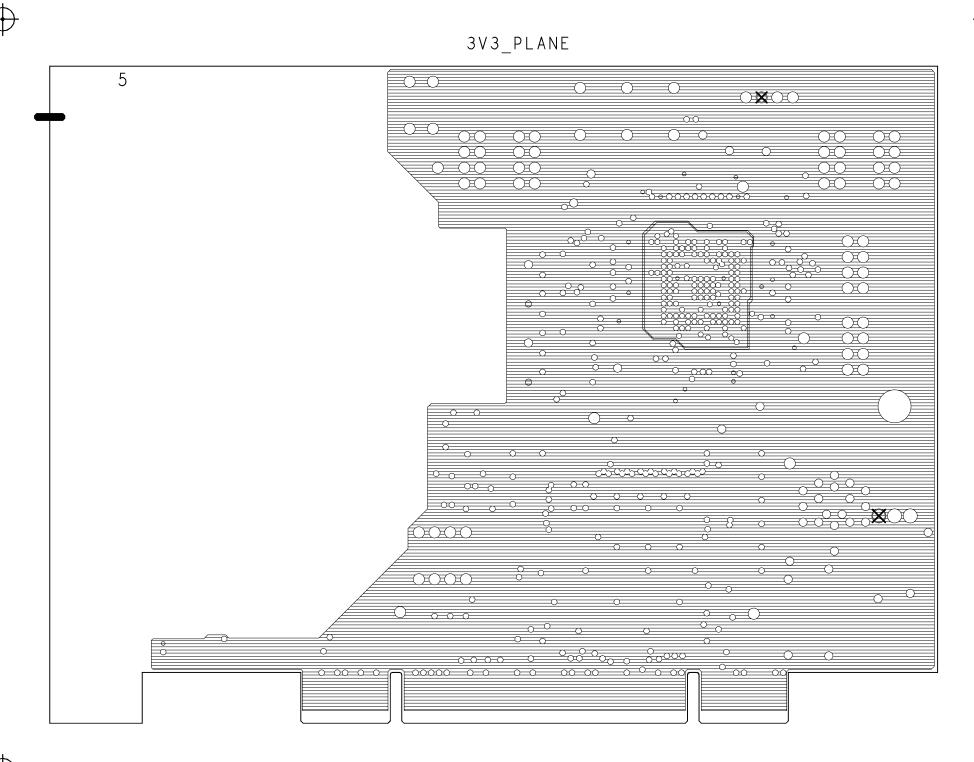

The COMET-QUAD Evaluator card has six layers: (from the top down) layer 1 is the top layer for signals, layer 2 for ground, layer 3 for Vcc signals, layer 4 for the 2.5V power plane, layer 5 for the 3.3V power plane and layer 6 is the bottom layer for signals. The dimension of the card conforms to the 5V PCI Raw Short Card, with custom mounting hole locations. The layer configurations are shown below:

EVALUATOR BOARD PMC-1991237 PMC PMC-Sierra, Inc.

PM4354 COMET-QUAD

**ISSUE 2**

COMET-QUAD EVALUATOR BOARD

# Figure 13: Layer Stack

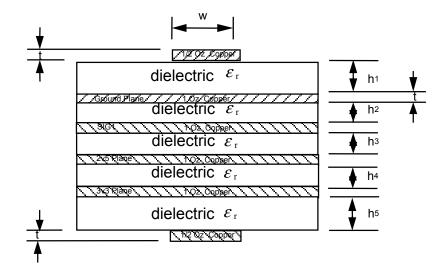

### Figure 14: PCB Cross Section

where

- $\epsilon_t$  = relative dielectric constant, nominally 5.0 for G –10 fibre –glass epoxy

- t = thickness of the copper, fixed according to the weight of copper selected.

For 1 oz copper, the thickness is 1.44 mil. For ½ oz copper, the thickness is 0.72 mil. This thickness can be ignored if w is large enough.

- h1, h2, h3, h4, h5 = thickness of dielectric.

- w = width of copper

ISSUE 2

COMET-QUAD EVALUATOR BOARD

The PCB related parameters are shown in Table 15:

### Table 15: PCB parameters

| Parameters                                             | Nominal                         |

|--------------------------------------------------------|---------------------------------|

| Board Thickness (mil)                                  | 62 (including copper thickness) |

| dielectric thickness between layers 1 and 2 (mil) (h1) | 7                               |

| dielectric thickness between layers 2 and 3 (mil) (h2) | 8                               |

| dielectric thickness between layers 3 and 4 (mil) (h3) | 24                              |

| dielectric thickness between layers 4 and 5 (mil) (h4) | 8                               |

| dielectric thickness between layers 5 and 6 (mil) (h5) | 7                               |

| Relative dielectric constant                           | 4.2                             |

To reduce signal degradation due to reflection and radiation, the traces that carry high speed signals should be treated as micro strip transmission lines with controlled impedance and matched resistive termination. The trace impedance is calculated using the formula:

$$Z_{\rm o} = \frac{87}{\sqrt{\varepsilon_{\rm r} + 1.41}} \times \ln\left(\frac{5.98 \times \rm h}{0.8 \times \rm w + t}\right)$$

| Parameter                  | Data |

|----------------------------|------|

| $\mathcal{E}_{\mathrm{r}}$ | 4.2  |

| h1 (mil)                   | 7    |

| t (mil) (2 Oz              | 2.88 |

| copper)                    |      |

| Zo (Ohm)                   | 50   |

| W (mil)                    | 10   |

Given characteristic impedance Zo, the dielectric thickness h1 is proportional to trace width. A small h1 will result in the traces being too thin to be accurately fabricated. Wider traces can be more precisely manufactured, but they take up too much board space. Therefore, the thickness of the board for a given trace impedance and adequate trace width should be chosen so that the traces take up as little board space as possible yet still leaving enough margin to allow accurate fabrication.

COMET-QUAD EVALUATOR BOARD

Using the same h1, thickness of copper, and dielectric constant, a 10 mil traces has a characteristic impedance of approximately 50 Ohms while an 3 mil trace has a characteristic impedance of 75 Ohms. We are using controlled impedance of 75 Ohms on this Evaluator Board.

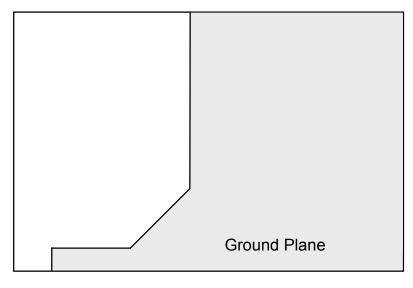

### 9.3 Power and Ground

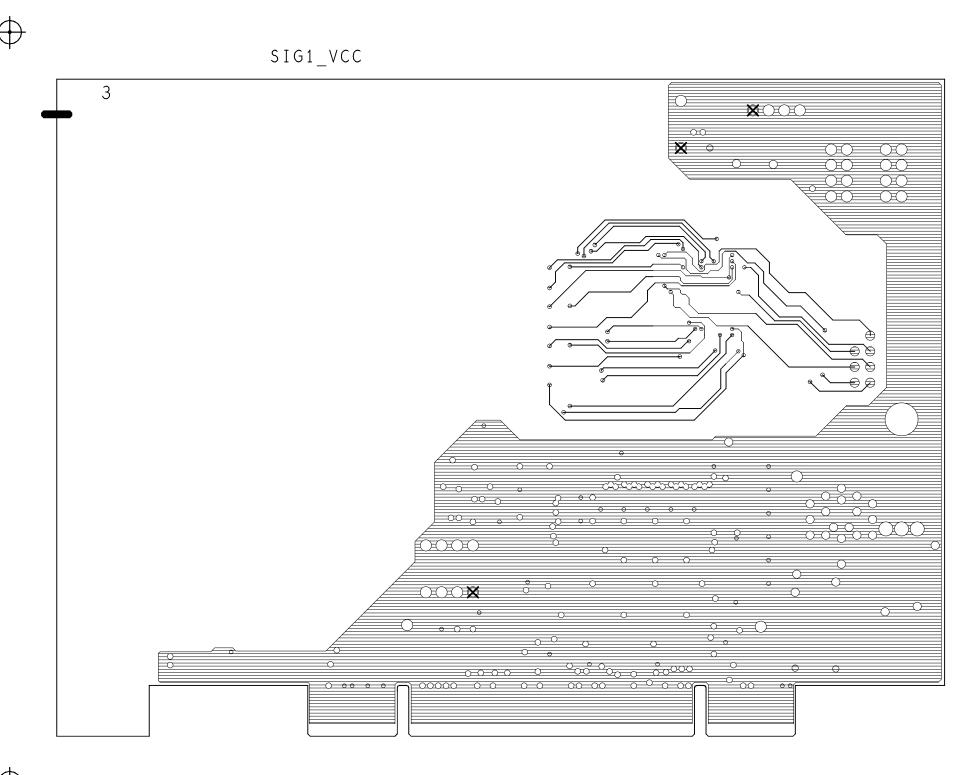

The following diagrams illustrates the power and ground plane distribution:

EVALUATOR BOARD PMC-1991237 PMC PMC-Sierra, Inc.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

Figure 18: 3.3V Plane

The introduction of ground slots within the ground plane must be avoided as they will increase trace inductance and increase crosstalk. Making clear-out holes too large can accidentally create these slots.

### 9.4 PCI Bus Signal Specification

This layout follows the PCI Rev. 2.1 Specification layout restrictions. The PCI SIG specification has stringent and detailed rules on decoupling, power consumption, trace length limits, routing, trace impedance, as well as signal

ISSUE 2

COMET-QUAD EVALUATOR BOARD

loading. Therefore, it is essential to check the latest PCI specification before proceeding with new designs and layouts.

The COMET-QUAD Evaluator design board conforms to the following PCI Specification/Recommendations:

- Component height on the component side does not exceed 0.570 inches, and on the solder side does not exceed 0.105 inches.

- PCI CLK signal trace is 2.5 inches +/- 0.1 inches and is connected to only one load.

- All 32-bit interface signals have the maximum trace length of 1.5 inches.

- Trace impedance for shared PCI signals are within 60 100 Ohm range, and trace velocity is between 150 and 190 ps/inch.

- 20 mil wide traces are used to connect the power and ground pins on PCI connector to their respective planes and the trace lengths are limited to 250 mil.

### 9.5 Routing

- All power and ground traces are as wide and short as possible to minimize trace inductance.

- All high speed traces are routed over continuous image planes (power or ground planes).

- All traces carrying transmit and receive line rate data should be routed on the same side and kept as short as possible.

- Both signals of a differential pair are of equal length and routed close to each other.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

### 10 GLOSSARY

| CompactPCI | Compact Peripheral Component Interconnect. A bus standard based on the PCI standard that defines a more rugged mechanical form factor for industrial use.                                                                                                                                                                                                                                                                                                                                       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSU        | Channel Service Unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DS1        | Off-premise T1 interface level provided by CSU.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DSX-1      | Digital Cross-connect T1 interface level.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| E1         | European First Order transmission format. This is the standardized (ITU-T G.704) base format of the European Pleisosynchronous Digital Hierarchy. It operates at 2.048Mbps. The E1 format consists of frames consisting of 32 octets, or timeslots (numbered 0 to 31). Timeslot 0 alternates between containing an FAS and containing the National Use bits (Sa[8:4]) and an A-bit for RAI. Timeslot 0 also contains an International Use Bit (Si) which can be used to support CRC Multiframe. |

| HDLC       | High Level Data Link Control. A family of bit-oriented protocols providing frames of information with address, control and frame check sequence fields.                                                                                                                                                                                                                                                                                                                                         |

| H-MVIP     | High Capacity MVIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MVIP       | Multi-Vendor Integration Protocol. A TDM bus standard that<br>is an extension of Mitel's ST-BUS. The MVIP bus is used in<br>computer telephony integration applications.                                                                                                                                                                                                                                                                                                                        |

| PCI        | Peripheral Component Interconnect – A bus standard that defines 32 bit transfers over a defined electrical interface.                                                                                                                                                                                                                                                                                                                                                                           |

| PCI Host   | An adapter board for a PCI system which acts as a PCI<br>Master and performs the additional functions of clock<br>distribution and bus arbitration.                                                                                                                                                                                                                                                                                                                                             |

| PCI Target | An adapter board for a PCI system which does not initiate bus transactions. Also known as a slave.                                                                                                                                                                                                                                                                                                                                                                                              |

| ESF        | Extended Super Frame format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PRELIMINARY                    | PMC                                    | PMC-Sierra, Inc.                                                       | PM4354 COMET-QUAD                                                  |

|--------------------------------|----------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------|

| EVALUATOR BOARD<br>PMC-1991237 | ISSUE 2                                |                                                                        | COMET-QUAD EVALUATOR BOARD                                         |

| RJ-48C                         |                                        | odular connector wi<br>00 ohm T1 and 120                               |                                                                    |

| SEEP                           | Only Memory) – A                       | Electrically Erasable<br>type of non-volatile<br>read using a serial i |                                                                    |

| T1                             | popular in North A                     |                                                                        | 44 Mbit/s that is<br>It is made up of 193<br>d by 24 DS-0 channels |

| T1.403                         | •                                      | interface (NI), betwo                                                  | allic interface, referred<br>een the network and a                 |

| TDM                            | channels of data<br>that a byte (or wo | •                                                                      |                                                                    |

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

#### 11 REFERENCES

- 1. PMC-Sierra, Inc., PMC-1990315, "COMET-QUAD Data Sheet", Issue 5, December 2000.

- 2. PMC-Sierra, Inc., PMC-1970624, "Combined E1/T1 Transceiver Standard Product Datasheet", Issue 9, September 2000.

- 3. PMC-Sierra, Inc., PMC-1981210, "COMET Reference Design Rev. 2.0", Issue 1, November 1998.

- 4. PMC-Sierra, Inc., PMC-1980815, "COMET Evaluation Board Rev. 2.0", Issue 4, June 2000.

- 5. PLX Technology, PCI 9050-1 Data Book, Version 1.01, April 17, 1997.

- 6. PCI Local Bus Specification Revision 2.1s, June 1, 1995.

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

### 12 DISCLAIMER

This document is a paper reference design, and as such, has not been built or tested as of this date.

Note that the protection circuitry provided in this document has not been tested to date. Therefore, there are no guarantees that it meets FCC Part 68, UL 1459 and 1950, and Bellcore TR-NWT-001089.

Please check the PMC-Sierra website regularly for updates to this document.

ISSUE 2

COMET-QUAD EVALUATOR BOARD

# 13 APPENDIX A: BILL OF MATERIALS

#### Table 16: Major Components List

| Ref. No | Component     | Manufacturer            | Package Type | Quantity |

|---------|---------------|-------------------------|--------------|----------|

| S1-S16  | P1800SC       | Teccor Electronics      | DO-214 SMB   | 16       |

|         | SIDACtor      | 972-580-7777            |              |          |

| S17-    | P0720SC       | Teccor Electronics      | DO-214 SMB   | 8        |

| S24     | SIDACtor      | 972-580-7777            |              |          |

| U1      | T9021         | Pulse Inc.              |              | 1        |

|         |               | 619-674-8100            |              |          |

| F1-F16  | F1250T        | Teccor Electronics      | SMD          | 16       |

|         | Telelink Fuse | 972-580-7777            |              |          |

| U7      | LM3940        | National Semiconductor  | SOT-223      | 1        |

|         |               | 408-721-5000            |              |          |

| U4      | NM93CS46E     | Fairchild Semiconductor | 8-pin DIP    | 1        |

|         | N             | 1-800-364-3577          |              |          |

| U6      | PCI-9050      | PLX Technology          | 160 pin PQFP | 1        |

|         |               | 800-759-3735            |              |          |

#### Table 17: Bill of Materials

|   | Part Name - Value                    | Part Number                             | Ref Des                                                                                                                            | Qty |

|---|--------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1 | 74HC08_SOIC-<br>BASE                 | Fairchild<br>Semiconductor<br>MM74HC08M | U3                                                                                                                                 | 1   |

| 2 | CAPACITOR-<br>0.01UF,<br>50V,X7R_603 | Various                                 | C4,C10,C12,C13,C15,C17,<br>C19,C20,C22-<br>C25,C28,C30,C32,C34,C36,<br>C45,C49,C51,C52,C55-<br>C57,C59-<br>C61,C65,C66,C68,C70,C71 | 32  |

EVALUATOR BOARD PMC-1991237

PM4354 COMET-QUAD

ISSUE 2

COMET-QUAD EVALUATOR BOARD

| 3  | CAPACITOR-<br>0.1UF,16V,<br>X7R_603                                      | Various                            | C1-<br>C3,C11,C18,C21,C29,C31,<br>C35,C37,C43,C44,C46-<br>C48,C50,C53,C54,C58,C62<br>-C64,C67,C69,C72 | 25 |

|----|--------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------|----|

| 4  | CAPACITOR-<br>0.47UF, 25V,TANT<br>THE                                    | Various                            | C40                                                                                                   | 1  |

| 5  | CAPACITOR-<br>10UF,10V,TANT<br>THE                                       | Various                            | C42                                                                                                   | 1  |

| 6  | CAPACITOR-<br>22UF,6.3V,TANT<br>THE                                      | Various                            | C9,C26,C27                                                                                            | 3  |

| 7  | CAPACITOR-<br>4.7UF,10V,TANT<br>THE                                      | Various                            | C5-C8                                                                                                 | 4  |

| 8  | CAPACITOR-<br>47UF,6.3V,TANT<br>THE                                      | Various                            | C14,C16,C33,C38,C39                                                                                   | 5  |

| 9  | CAPACITOR-<br>68UF,6.3V,TANT<br>THE                                      | Various                            | C41                                                                                                   | 1  |

| 10 | COMET-<br>QUAD_PBGA-<br>BASE                                             | PMC PM4354-PI                      | U5                                                                                                    | 1  |

| 11 | FUSE SMD – 500A<br>@<br>2X10 <u>mailto:FUSE_S</u><br><u>MD-500A@2X10</u> | Teccor Electronics –<br>F1250T     | F1-F16                                                                                                | 16 |

| 12 | FUSESMD_SOC<br>KET-1.000A,SLO-<br>BLO                                    | DIGI-KEY<br>F1303CT-ND             | F17                                                                                                   | 1  |

| 13 | HEADER4_100MIL-<br>BASE                                                  | Sullins Electronics –<br>PZC36SAAN | J7                                                                                                    | 1  |

| 14 | HEADER_4X2_SMT<br>_2MM-BASE                                              | 87267-0850                         | J8-J13                                                                                                | 6  |