# **OKI** semiconductor

# **MSM5219B**

## **48-DOT STATIC LCD DRIVER**

# **GENERAL DESCRIPTION**

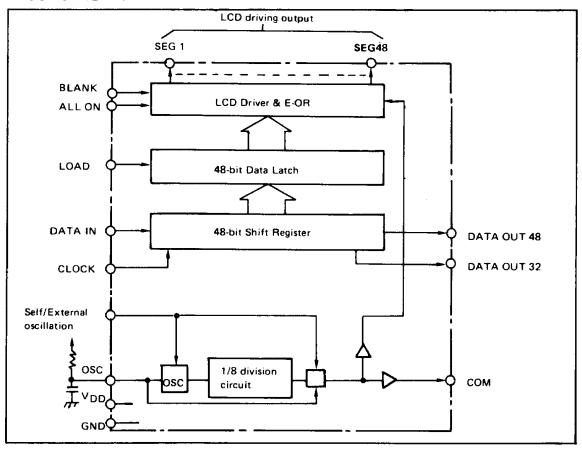

The OKI MSM5219BGS is a 48 dot static LCD driver which is fabricated by low power CMOS metal gate technology. This LSI consists of 48-bit shift register, 48-bit latch and 48-bit LCD driver. The display data, which was input to the 48-bit shift register, is shifted to the 48-bit latch by the LOAD signal. Then the data is output to the LCD panel through the 48-bit LCD driver.

## **FEATURES**

- 48 dots static LCD driving capability

- Simple interface with microcomputer chip (controlled by three input signals)

- Bit-to-bit correspondence between the input and the output

- Cascade connection capability

- LCD driving AC frequency is directly input externally

- Applicable as an output expander

- Supply voltage: 3 ~ 7 V

- 60 pin plastic QFP (QFP60-P-1519-K)

- 60 pin -V plastic QFP (QFP60-P-1519-VK)

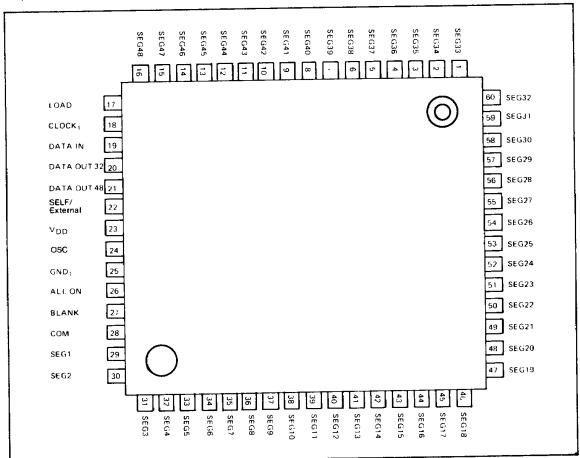

## PIN CONFIGURATION

(Top view) 60 pin plastic QFP

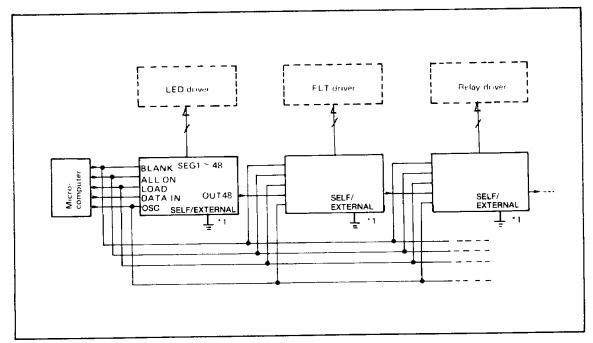

## **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol                            | Condition             | Limits                           | Unit |  |

|---------------------|-----------------------------------|-----------------------|----------------------------------|------|--|

| Supply voltage      | V <sub>DD</sub> – V <sub>SS</sub> | T <sub>a</sub> = 25°C | -0.3 ~+7                         | V    |  |

| input voltage       | V <sub>I</sub>                    | T <sub>a</sub> = 25°C | $V_{SS} - 0.3 \sim V_{DD} + 0.3$ | V    |  |

| Storage temperature | T <sub>stg</sub>                  | _                     | -55 ~+150                        | °c   |  |

# **OPERATING RANGE**

| Parameter             | Symbol                            | Condition                | Limits           | Unit |  |

|-----------------------|-----------------------------------|--------------------------|------------------|------|--|

| Supply voltage        | V <sub>DD</sub> – V <sub>SS</sub> | Self-Oscillation circuit | 4~7              | V    |  |

|                       |                                   | External oscillation     | 3~7              |      |  |

| Operating temperature | Тор                               | <u> </u>                 | <b>−40 ~ +85</b> | °c   |  |

# **DC CHARACTERISTICS**

$(V_{DD} - V_{SS} = 5V, T_a = -40 \sim +85^{\circ}C)$

| Parameter                           | Symbol            | Condition                                                                    | MIN          | TYP | MAX  | Unit |

|-------------------------------------|-------------------|------------------------------------------------------------------------------|--------------|-----|------|------|

| "H" Input voltage*1                 | ViH               |                                                                              | 3.6          | -   | _    | V    |

| "L" Input voltage*1                 | VIL               | _                                                                            |              |     | 1.0  | ٧    |

| Input leakage current*1             | TIH/TIL           | V <sub>I</sub> = 5V/V <sub>I</sub> = 0V                                      | _            | _   | 1/-1 | μΑ   |

| SEG "H" Output voltage VOHS         |                   | ΙΟ = -30μΑ                                                                   | 4.8          |     | _    |      |

| SEG "L" Output voltage              | Vols              | 1Ο = 30μΑ                                                                    | _            |     | 0.2  |      |

| COM "H" Output voltage              | Voнc              | I <sub>O</sub> = -150μΑ                                                      | 4.8          |     |      | V    |

| COM "L" Output voltage              | VOLC              | I <sub>O</sub> = 150μΑ                                                       |              |     | 0.2  | ٧    |

| SEG Output current 1                | OHS1/IOLS1        | V <sub>OH</sub> = 4.5V/V <sub>OL</sub> = 0.5V                                | -100/<br>100 | _   | _    | μΑ   |

| SEG Output current 2                | OHS2/IOLS2        | V <sub>OH</sub> = 1V/V <sub>OL</sub> = 4V                                    | -400/<br>400 | _   | -    | μΔ   |

| COM Output current 1                | IOHC1/IOLC1       | V <sub>OH</sub> = 4.5V/V <sub>OL</sub> = 0.5V                                | -500/<br>500 | _   | -    | μΑ   |

| COM Output current 2                | OHC2/IOLC2        | V <sub>OH</sub> = 1V/V <sub>OL</sub> = 4V                                    | -2/2         | _   |      | m/   |

| "H" Output voltage*2                | Voн               | ΙΟ = -40μΑ                                                                   | 4.2          | -   | _    | ٧    |

| "L" Output voltage*2                | VOL               | I <sub>O</sub> = 1.6mA                                                       | _            |     | 0.4  | V    |

| Output current*2                    |                   | $V_0 = 2.5V/V_0 = 0.4V$                                                      | -0.2/<br>1.6 | -   | _    | ٧    |

| -                                   | twφ               | *3                                                                           | 5            |     | _    | μs   |

| Clock pulse width                   |                   | *4                                                                           | 0.5          | -   |      |      |

| Max. clock pulse frequency          | <sup>f</sup> φMAX | *3                                                                           | 0.1          |     |      | мн   |

|                                     |                   | *4                                                                           | 1            | _   |      |      |

| Input signal rising/falling time    | trφ, tfφ          | *5                                                                           | _            | _   | 5    | μ    |

| Static current consumption          | I <sub>DD1</sub>  | _                                                                            | _            |     | 100  | μ    |

| Active current consumption IDD2     |                   | No load when $R_{OSC} = 150 \text{ k}\Omega$ , $C_{OSC} = 0.015 \mu\text{F}$ | _            | _   | 2    | m    |

| COM Frequency<br>(Self oscillation) | fcom              | No load when V <sub>DD</sub> = 5V                                            | 25           | -   | 300  | н    |

<sup>\*1:</sup> Applicable to all terminals except OSC. This condition is applied to OSC in the external oscillation mode.

<sup>\*2:</sup> Applicable to DATA OUT 32, DATA OUT 48.

<sup>\*3:</sup> Applicable to OSC.

<sup>\*4:</sup> Applicable to CLOCK.

<sup>\*5:</sup> Applicable to all terminals except OSC terminal.

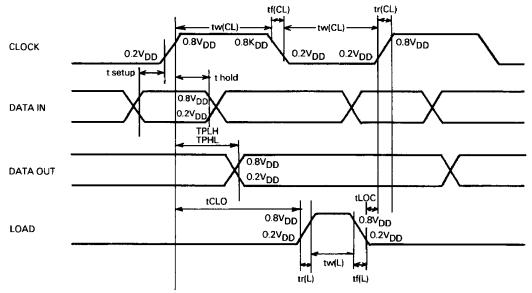

# **Switching Characteristisc**

$(V_{DD} = 5V \pm 10\% \text{ Ta} = 25^{\circ}\text{C})$

|                         |                  |              | , 00 |     |     |      |  |

|-------------------------|------------------|--------------|------|-----|-----|------|--|

| Parameter               | Symbol           | Conditions   | MIN  | TYP | MAX | Unit |  |

| Propagation delay time  | tP HL            |              | _    | _   | 600 | ns   |  |

| Data out delay time     | tP LH            | <del>-</del> |      | _   | 600 | ns   |  |

| Maximum clock frequency | fCL              | DUTY = 50%   | 1    | _   | -   | MHz  |  |

| Clock width             | tw (CL)          | _            | 400  | _   | _   | ns   |  |

| Load width              | tw (L)           |              | 400  |     | _   | ns   |  |

| Data setup time         | t setup          | _            | 300  | _   | _   | ns   |  |

| Data hold time          | t hold           | _            | 300  | _   | _   | ns   |  |

| Clock-to-load time      | t CLO            | _            | 500  | _   |     | ns   |  |

| Load-to-clock time      | t LOC            | AMERICA .    | 0    |     | _   | ns   |  |

| Clock rise/fall time    | tr (CL), td (CL) | _            | 50   | _   |     | ns   |  |

| Load rise/fall time     | tr (L), tf (L)   | <del></del>  | 1    | -   | _   | ns   |  |

# **FUNCTIONAL DESCRIPTION**

### Operational Description

The display data is input to the shift register by the DATA IN signal and CLOCK signal. It is transferred

to the 48-bit latch by the LOAD signal and it is output to the LCD panel through 48-bit LCD driver.

#### osc

The clock, which is used to generate the COM signal and the LCD driving signal, is input to this pin.

#### OSC Terminal

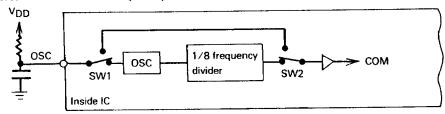

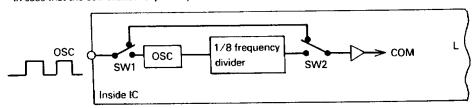

This terminal is used to generate COM signal. When the self-excited/separately-excited terminal is set

to "H" level, the oscillation circuit is formed by connecting the resistor and capacitor to this terminal, and the 1/8 divided frequency of the oscillation frequency is output as COM signal. When the self-excited/separately-excited terminal is set to "L" level, the logical level of the OSC terminal is used as COM signal without change. This is used for cascaded connection in the IC.

In case that the self-excited/separately-excited terminal is at "H" level.

In case that the self-excited/separately-excited terminal is at "L" level.

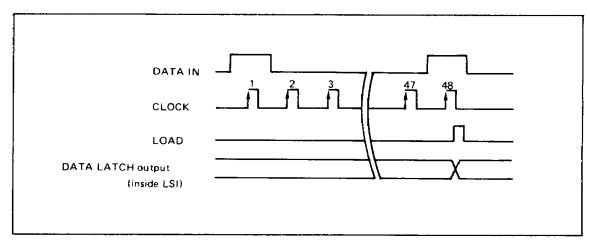

## ● DATA IN CLOCK<sub>1</sub>

DATA IN is a data input pin which enables the LCD to display when DATA IN pin is at high level. The 48-bit shift register is shifted at the rising edge of the CLOCK signal. Initially, the first bit of the shift register contains the current logic level of the DATA IN pin, and the bit N (N = 2  $\sim$  48) contains the data which was in bit N - 1 (N = 2  $\sim$  48) before the start of the operation. The data which was in bit 48 before the operation start is considered invalid.

#### LOAD

The data in the 48-bit shift register is shifted to the 48-bit latch when the LOAD pin set at high level, while the last data which was transferred to the latch when the LOAD pin was set at high level is constantly output when the LOAD pin is set at low level.

#### ALL SEG ON

When this pin is set at high level, all segments display turn on. This pin has the priority to the BLANK pin described as below.

#### BLANK

When this pin is set at high level, all segments display turn off. The ALL SEG ON pin has the priority over this pin.

#### ● SEG1 ~ SEG48

LCD driving output pins. The reversed phase of the COM signal, which is used to display the data, is output from these pins when SEG1 ~ SEG48 are set at high level, while there is no display on the LCD when these pins are set at low level. The data which was input from the DATA IN pin is output from these pins to the LCD panel. The SEG N pin corresponds to the bit N of the shift register.

#### COM

Output terminal for the LCD. It is connected to the common side of the LCD.

## DATA OUT 32, DATA OUT 48

Output pin of the shift register. It is used when the MSM5219BGS is connected in a series (cascade connection). It is connected to next MSM5219BGS's DATA IN terminal.

#### SELF/EXTERNAL

When this pin is set at high level, OSC is self mode. At low level, OSC is external mode.

#### Self-excited/separately-excited terminal

This terminal is used to switch over functions of OSC terminal. When "H" level is set, OSC terminal forms an oscillation circuit, and the 1/8 divided frequency is output as COM signal.

When "L" level is set, the OSC terminal is separated from the oscillation circuit, and its input logical level is used as COM signal without change. When cascade-connecting the IC, the terminal is to be set "H" level at the master and "L" level at the slave.

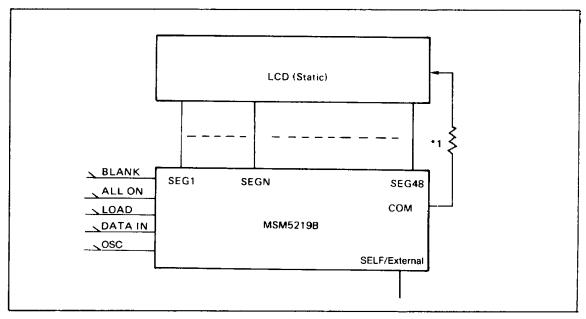

## **APPLICATION CIRCUIT**

## • Single MSM5219BGS

\*1: When this IC is used under a strong external noise or large-capacity LCD load, this resistor prevents latch-up to be caused by a low output impedance of the COM pin. The resistance is about  $100\Omega$ .

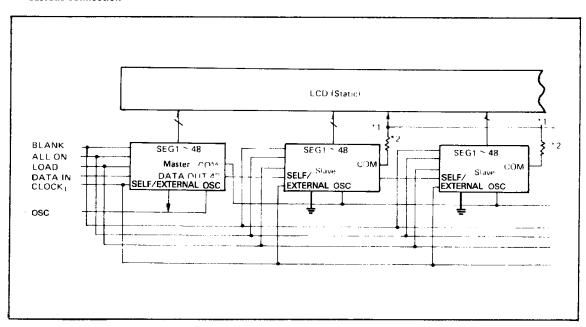

### Cascade connection

- \*1: The COM pin of the slave MSM5219BGS can be WIRED OR.

- \*2: When this IC is used under a strong external noise or large-capacity LCD load, this resistor prevents latch-up to be caused by a low output impedance of the COM pin.

The resistance is about 100Ω.

#### Output Expander

As explained above, this IC can drive the static LCD with the COM pin. In addition, it can also be

used as an output pin expander for a microcomputer with the following connections:

\*1: In this example, "H" is output by the positive logic, that is, when "H" is written from DATA IN, "H" is output with a LOAD signal. If the OSC pin is connected to VDD, the output has the negative logic, that is, the logic level input from the DATA IN pin is inverted and output.

43