# CXA3268AR

# **Driver/Timing Generator for Color LCD Panels**

# **Description**

The CXA3268AR is an IC designed to drive the color LCD panels ACX300, ACX301, ACX302 and ACX703.

This IC greatly reduces the number of peripheral circuits and parts by incorporating a RGB driver and timing generator for video signals onto a single chip. This chip has a built-in serial interface circuit and electronic attenuators which allow various settings to be performed by microcomputer control, etc.

#### **Features**

- Color LCD panel ACX300, ACX301, ACX302 and ACX703 driver

- Supports NTSC and PAL systems

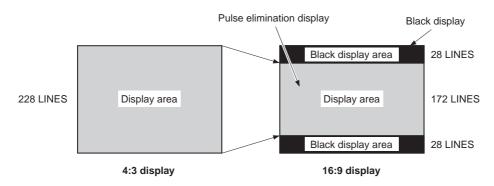

- Supports 16:9 wide display (letter box and pulse elimination display)

- Supports Y/color difference and RGB inputs

- Supports OSD input (digital input)

- Power saving function

- Serial interface circuit

- Electronic attenuators (D/A converter)

- Trap and LPF (f0, fc variable)

- COMMON and PSIG output circuits

- Sharpness function

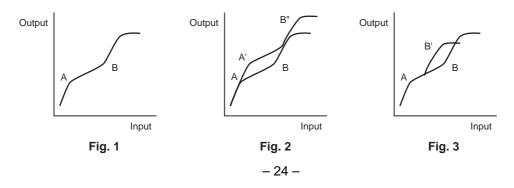

- 2-point γ correction circuit

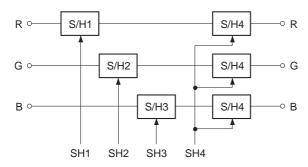

- R, G, B signal delay time adjustment circuit

- D/A output pin (0 to 3V, 8 level output)

- Output polarity inversion circuit

- Supports AC drive for LCD panel during no signal

## **Applications**

Compact LCD monitors, etc.

#### **Absolute Maximum Ratings** (Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul> | Vcc1 | 6   | V  |

|------------------------------------|------|-----|----|

|                                    | Vcc2 | 15  | V  |

|                                    | Vcc3 | 15  | V  |

|                                    | VDD  | 5.5 | \/ |

Analog input pin voltage VINA (Pins 57, 58 and 59)

|                    | GND - 0.3 to $Vcc1 + 0.3$ |      |  |  |  |

|--------------------|---------------------------|------|--|--|--|

| VINA (Pins 3, 69)  | Vcc1                      | V    |  |  |  |

| VINA (Pin 30)      | 1.5 to Vcc2 - 4           | V    |  |  |  |

| VINA (Pin 71)      | 0.9                       | Vp-p |  |  |  |

| VINA (Pins 70, 72) | 0.8                       | Vp-p |  |  |  |

• Digital input pin voltage

VIND (other than Pins 5, 10, 14, 15 and 16)

Vss - 0.3 to Vdd + 0.3 V

VIND (Pins 5, 10) Vss – 0.3 to +5.5

Common input pin voltage

VINAD (Pins 14, 15 and 16)

GND, Vss - 0.3 to +5.5 V

Operating temperature

Topr -15 to +75 °C

Storage temperature

Tstg -55 to +150 °C

Allowable power dissipation

P<sub>D</sub> (Ta  $\leq 25$ °C) 737 mW

## Operating conditions

Supply voltage

| Vcc1 – GND1 | 2.7 to 3.6   | V |

|-------------|--------------|---|

| Vcc2 – GND2 | 11.0 to 14.0 | V |

| Vcc3 – GND3 | 11.0 to 14.0 | V |

| Vpp - Vss   | 2.7 to 3.6   | V |

Input voltage

SIG.C voltage

VSIG.C 5.0 to 6.5 \

RGB input signal voltage (Pins 70, 71 and 72)\*1

VRGB 0 to 0.7 (0.5 typ.)

Y input signal voltage (Pin 71)\*2

VY

0 to 0.5 (0.35 typ.) Vp-p

R-Y input voltage (Pin 72)\*2

VR-Y 0 to 0.49 (0.245 typ.) Vp-p

B-Y input voltage (Pin 70)\*2

VB-Y 0 to 0.622 (0.311 typ.) Vp-p

\*1 During RGB input

\*2 During Y/color difference input

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

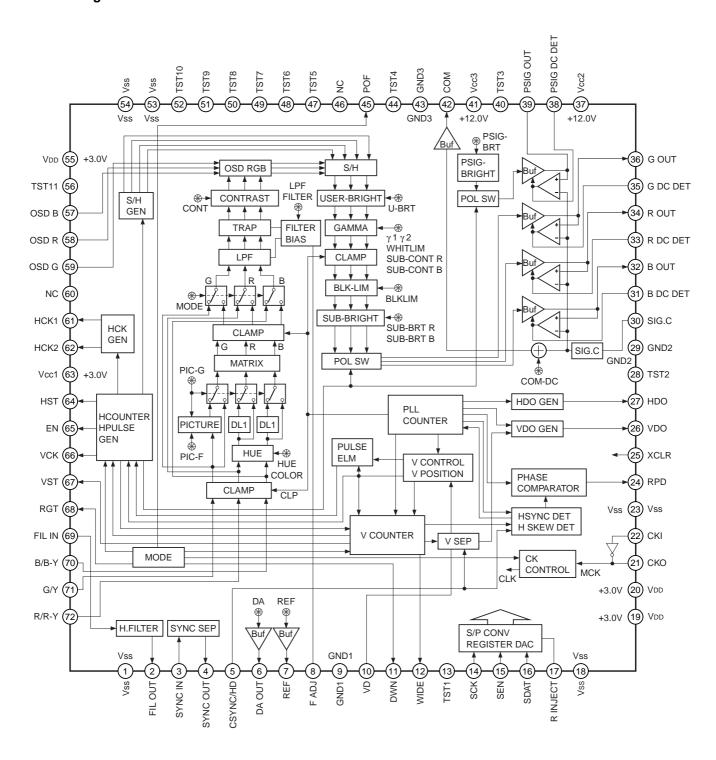

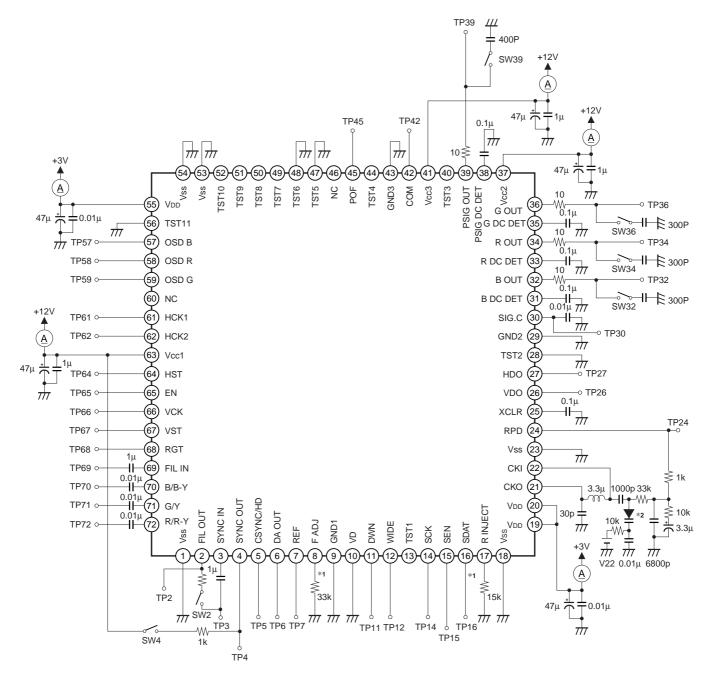

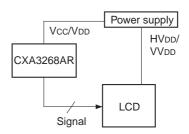

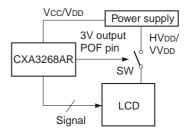

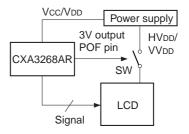

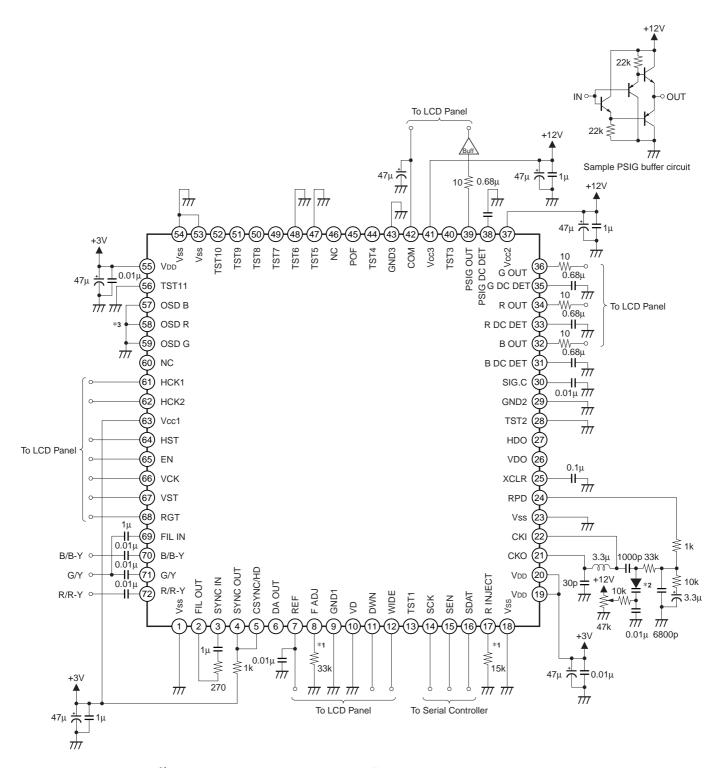

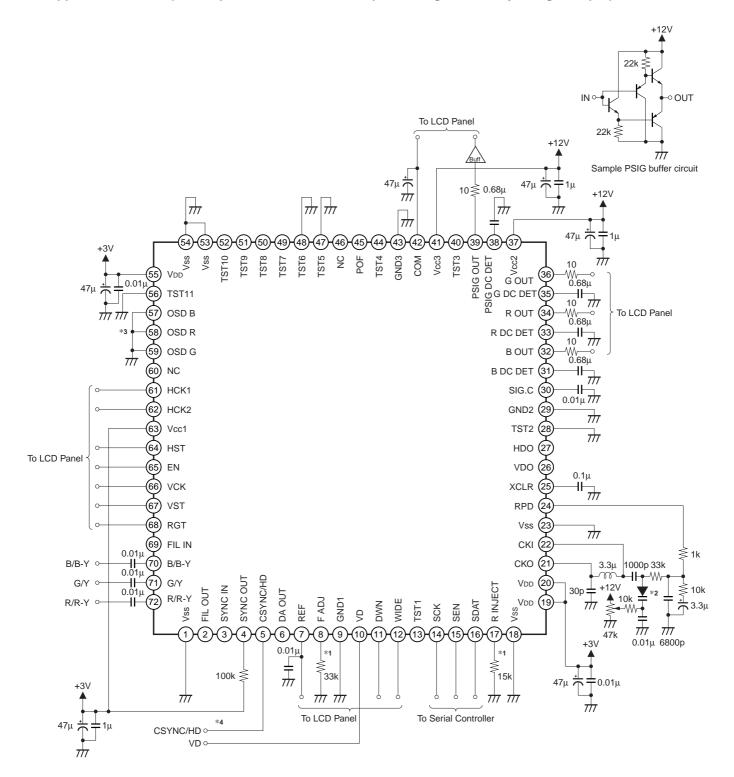

#### **Block Diagram**

# **Pin Description**

| Pin<br>No. | Symbol   | I/O | Description                                                         | Input pin for open status |

|------------|----------|-----|---------------------------------------------------------------------|---------------------------|

| 1          | Vss      |     | Digital 3.0V GND                                                    | '                         |

| 2          | FIL OUT  | 0   | H filter output (for using internal sync separation)                |                           |

| 3          | SYNC IN  | ı   | Sync separation circuit input (for using internal sync separation)  |                           |

| 4          | SYNC OUT | 0   | Sync separation circuit output (for using internal sync separation) |                           |

| 5          | CSYNC/HD | ı   | CSYNC/horizontal sync signal input                                  |                           |

| 6          | DA OUT   | 0   | DAC output                                                          |                           |

| 7          | REF      | 0   | Level shifter circuit REF voltage output for LCD panel              |                           |

| 8          | F ADJ    | 0   | Trap f0 adjusting resistor connection                               |                           |

| 9          | GND1     | _   | Analog 3.0V GND                                                     |                           |

| 10         | VD       | ı   | Vertical sync signal input                                          | L                         |

| 11         | DWN      | 0   | Up/down inversion switching signal output                           |                           |

| 12         | WIDE     | 0   | 16:9 wide display switching pulse output                            |                           |

| 13         | TST1     | _   | Test (Leave this pin open.)                                         |                           |

| 14         | SCK      | ı   | Serial clock input                                                  |                           |

| 15         | SEN      | I   | Serial load input                                                   |                           |

| 16         | SDAT     | I   | Serial data input                                                   |                           |

| 17         | R INJECT | 0   | Serial block current controlling resistor connection                |                           |

| 18         | Vss      | _   | Digital 3.0V GND                                                    |                           |

| 19         | VDD      | _   | Digital 3.0V power supply                                           |                           |

| 20         | VDD      | _   | Digital 3.0V power supply                                           |                           |

| 21         | СКО      | 0   | Oscillation cell output                                             |                           |

| 22         | CKI      | I   | Oscillation cell input                                              |                           |

| 23         | Vss      | _   | Digital 3.0V GND                                                    |                           |

| 24         | RPD      | 0   | Phase comparator output                                             |                           |

| 25         | XCLR     | I   | Power-on reset capacitor connection (timing generator block)        | Н                         |

| 26         | VDO      | 0   | VDO pulse output                                                    |                           |

| 27         | HDO      | 0   | HDO pulse output                                                    |                           |

| 28         | TST2     | _   | Test (Connect to GND.)                                              |                           |

| 29         | GND2     | _   | Analog 12.0V GND                                                    |                           |

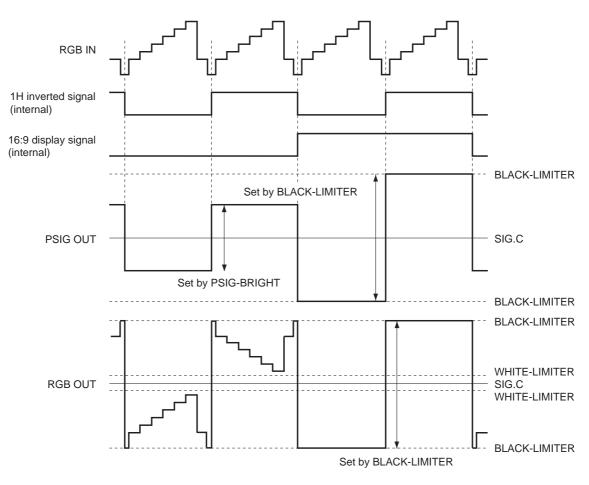

| 30         | SIG.C    | ı   | R, G, B and PSIG output DC voltage adjustment                       |                           |

| 31         | B DC DET | 0   | B signal DC voltage feedback circuit capacitor connection           |                           |

| 32         | B OUT    | 0   | B signal output                                                     |                           |

| 33         | R DC DET | 0   | R signal DC voltage feedback circuit capacitor connection           |                           |

| 34         | R OUT    | 0   | R signal output                                                     |                           |

| 35         | G DC DET | 0   | G signal DC voltage feedback circuit capacitor connection           |                           |

| 36         | G OUT    | 0   | G signal output                                                     |                           |

| 37         | Vcc2     |     | Analog 12.0V power supply                                           |                           |

| Pin<br>No. | Symbol      | I/O | Description                                                                       | Input pin for open status |

|------------|-------------|-----|-----------------------------------------------------------------------------------|---------------------------|

| 38         | PSIG DC DET | 0   | PSIG signal DC voltage feedback circuit capacitor connection                      |                           |

| 39         | PSIG OUT    | 0   | PSIG output                                                                       |                           |

| 40         | TST3        | _   | Test (Leave this pin open.)                                                       |                           |

| 41         | Vcc3        | _   | Analog 12.0V COM (CS) power supply                                                |                           |

| 42         | СОМ         | 0   | Common pad voltage for LCD panel output (CS)                                      |                           |

| 43         | GND3        | _   | Analog 12.0V COM (CS) GND                                                         |                           |

| 44         | TST4        | _   | Test (Leave this pin open.)                                                       |                           |

| 45         | POF         | 0   | LCD panel power supply on/off (Leave this pin open when not using this function.) |                           |

| 46         | NC          |     |                                                                                   |                           |

| 47         | TST5        | _   | Test (Connect to GND.)                                                            |                           |

| 48         | TST6        | _   | Test (Connect to GND.)                                                            |                           |

| 49         | TST7        | _   | Test (Leave this pin open.)                                                       |                           |

| 50         | TST8        | _   | Test (Leave this pin open.)                                                       |                           |

| 51         | TST9        | _   | Test (Leave this pin open.)                                                       |                           |

| 52         | TST10       | _   | Test (Leave this pin open.)                                                       |                           |

| 53         | Vss         | _   | Digital 3.0V GND                                                                  |                           |

| 54         | Vss         | _   | Digital 3.0V GND                                                                  |                           |

| 55         | VDD         | _   | Digital 3.0V power supply                                                         |                           |

| 56         | TST11       | _   | Test (Connect to GND.)                                                            |                           |

| 57         | OSD B       | I   | OSD B input                                                                       |                           |

| 58         | OSD R       | I   | OSD R input                                                                       |                           |

| 59         | OSD G       | I   | OSD G input                                                                       |                           |

| 60         | NC          |     |                                                                                   |                           |

| 61         | HCK1        | 0   | H clock pulse 1 output                                                            |                           |

| 62         | HCK2        | 0   | H clock pulse 2 output                                                            |                           |

| 63         | Vcc1        | _   | Analog 3.0V power supply                                                          |                           |

| 64         | HST         | 0   | H start pulse output                                                              |                           |

| 65         | EN          | 0   | EN pulse output                                                                   |                           |

| 66         | VCK         | 0   | V clock pulse output                                                              |                           |

| 67         | VST         | 0   | V start pulse output                                                              |                           |

| 68         | RGT         | 0   | Right/left inversion switching signal output                                      |                           |

| 69         | FIL IN      | I   | H filter input (for using internal sync separation)                               |                           |

| 70         | B/B-Y       | I   | B/B-Y signal input                                                                |                           |

| 71         | G/Y         | I   | G/Y signal input                                                                  |                           |

| 72         | R/R-Y       | I   | R/R-Y signal input                                                                |                           |

<sup>\*</sup> DWN: <u>DOWN</u> SCAN and UP SCAN, RGT: <u>RIGH</u>T SCAN and LEFT SCAN H: pull-up processing, L: pull-down processing

# **Analog Block Pin Description**

| Pin<br>No. | Symbol   | Pin<br>voltage | Equivalent circuit    | Description                                                                                                        |

|------------|----------|----------------|-----------------------|--------------------------------------------------------------------------------------------------------------------|

| 2          | FIL OUT  | 2.15V          | Vcc1 23k  200 4  GND1 | Amplifies and outputs the sync portion of the video signal input to FIL IN (Pin 69).                               |

| 3          | SYNC IN  | 1.1V           | 3<br>200<br>GND1      | Sync separation circuit input. Inputs the FIL OUT (Pin 2) output signal via a capacitor.                           |

| 4          | SYNC OUT | _              | Vcc1  GND1            | Sync separation output. Positive polarity output in open collector format.                                         |

| 6          | DA OUT   | _              | Vcc1 50 W 50 H 50 H   | DA output. Outputs the serial data converted to DC voltage. The current driving capacity is ±1.0mA (max.).         |

| 7          | REF      | _              | Vcc1                  | REF output. Outputs the serial data converted to DC voltage. The current driving capacity (sink) is ±1.5mA (max.). |

| Pin<br>No.     | Symbol             | Pin<br>voltage                                        | Equivalent circuit           | Description                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|--------------------|-------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8              | F ADJ              | 1.1V                                                  | 8<br>6.5k<br>8<br>GND1       | Connect a resistor between this pin and GND1 to control the internal LPF and trap frequencies. Connect a 33kΩ resistor (tolerance ±2%, temperature characteristics ±200ppm or less). This pin is easily affected by external noise, so make the connection between the pin and external resistor, and between the GND side of the external resistor and the GND1 pin as close as possible. |

| 9              | GND1               | _                                                     |                              | Analog 3.0V GND.                                                                                                                                                                                                                                                                                                                                                                           |

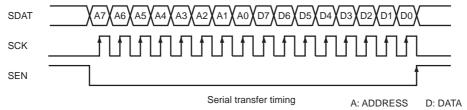

| 14<br>15<br>16 | SCK<br>SEN<br>SDAT | _                                                     | Vcc1  (14) (15) (200) (GND1) | Serial clock, serial load and serial data inputs for serial communication.                                                                                                                                                                                                                                                                                                                 |

| 17             | R INJECT           | 0.7V                                                  | Vcc1 200 GND1                | Connect a resistor for setting the injector current of the IIL logic circuit. Connect a $15k\Omega$ resistor between this pin and GND1. Use a resistor with a deviation of $\pm 2\%$ and temperature characteristics of $\pm 200$ ppm or less.                                                                                                                                             |

| 29             | GND2               | _                                                     |                              | Analog 12.0V GND.<br>(for the RGB and PSIG output<br>circuits)                                                                                                                                                                                                                                                                                                                             |

| 30             | SIG.C              | Preset<br>Vcc2/2<br>Variable<br>range:<br>5.0 to 6.5V | 30 140k 10p GND1 140k 10p    | R, G, B and PSIG output DC voltage setting. Connect a 0.01µF capacitor between this pin and GND1. When using a SIG.C of other than Vcc2/2, input the SIG.C voltage from an external source.                                                                                                                                                                                                |

| Pin<br>No.           | Symbol                                          | Pin<br>voltage                      | Equivalent circuit                            | Description                                                                                                                                                                                                               |

|----------------------|-------------------------------------------------|-------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31<br>33<br>35<br>38 | B DC DET<br>R DC DET<br>G DC DET<br>PSIG DC DET | 1.8V                                | Vcc2 Vcc1  31)  33)  35)  38)  GND1           | Smoothing capacitor connection for the feedback circuit of R, G, B and PSIG output DC level control. Connect a low-leakage capacitor.                                                                                     |

| 32<br>34<br>36<br>39 | B OUT<br>R OUT<br>G OUT<br>PSIG OUT             | Vcc2/2<br>(SIG.C = preset)          | 32<br>34<br>36<br>39<br>GND2                  | R, G, B and PSIG signal outputs. The DC level is controlled to match the SIG.C pin voltage. Low output in power saving mode. Vcc2/2V output when preset.                                                                  |

| 37                   | Vcc2                                            | 12.0V                               |                                               | Analog 12.0V power supply. (for the RGB and PSIG output circuits)                                                                                                                                                         |

| 41                   | Vcc3                                            | 12.0V                               |                                               | Analog 12.0V power supply.<br>(for COM (CS) output)                                                                                                                                                                       |

| 42                   | СОМ                                             | _                                   | Vcc3 200 90k W                                | COMMON voltage output. The output voltage is controlled by serial communication.                                                                                                                                          |

| 43                   | GND3                                            | _                                   |                                               | Analog 12.0V GND.<br>(for COM (CS) output)                                                                                                                                                                                |

| 57<br>58<br>59       | OSD B<br>OSD R<br>OSD G                         | Vth1 = Vcc1 × 1/3 Vth2 = Vcc1 × 2/3 | Vcc1<br>57<br>50k<br>58<br>W<br>50k ≥<br>GND1 | OSD pulse inputs. When one of these input pins exceeds the Vth1 level, all of the outputs go to black limiter level; when an input pin exceeds the Vth2 level, only the corresponding output goes to white limiter level. |

| Pin<br>No.     | Symbol                | Pin<br>voltage                                              | Equivalent circuit            | Description                                                                                                                                                                                                                                                                              |

|----------------|-----------------------|-------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63             | Vcc1                  | _                                                           |                               | Analog 3.0V power supply.                                                                                                                                                                                                                                                                |

| 69             | FIL IN                | 1.2V                                                        | GND1                          | H filter input. Input the video signal via a capacitor.                                                                                                                                                                                                                                  |

| 70<br>71<br>72 | B/B-Y<br>G/Y<br>R/R-Y | G/Y 1.8V  R/R-Y, B/B-Y, RGB: 1.8V  Y/color difference: 2.0V | 70<br>200<br>71<br>72<br>GND1 | In Y/color difference input mode, input the Y signal to Pin 71, the B-Y signal to Pin 70, and the R-Y signal to Pin 72. In RGB input mode, input the B signal to Pin 70, the G signal to Pin 71 and the R signal to Pin 72. Pedestal clamp these pins with external coupling capacitors. |

# **Digital Block Pin Description**

| Pin<br>No.                                                           | Symbol                                            | Pin<br>voltage | Equivalent circuit                                                          | Description                                                                                                                 |

|----------------------------------------------------------------------|---------------------------------------------------|----------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1<br>18<br>23<br>53<br>54                                            | Vss                                               | _              |                                                                             | Digital 3.0V GND.                                                                                                           |

| 19<br>20<br>55                                                       | Vdd                                               | _              |                                                                             | Digital 3.0V power supply.                                                                                                  |

| 5<br>14<br>15<br>16                                                  | CSYNC/HD<br>SCK<br>SEN<br>SDAT                    | _              | 5 15<br>14 16<br>Vss                                                        | Composite sync/horizontal sync signal input, and serial clock, serial load and serial data inputs for serial communication. |

| 10                                                                   | VD                                                | _              | 10<br>Vss                                                                   | Vertical sync signal input.                                                                                                 |

| 21                                                                   | СКО                                               | _              |                                                                             | Oscillation circuit output.                                                                                                 |

| 22                                                                   | CKI                                               | _              |                                                                             | Oscillation circuit input.                                                                                                  |

| 24                                                                   | RPD                                               | _              |                                                                             | Phase comparator output.                                                                                                    |

| 25                                                                   | XCLR                                              | _              | VDD (25) VSS                                                                | Digital block system reset.                                                                                                 |

| 11<br>12<br>26<br>27<br>45<br>61<br>62<br>64<br>65<br>66<br>67<br>68 | DWN WIDE VDO HDO POF HCK1 HCK2 HST EN VCK VST RGT | _              | VDD<br>11 (27) (62) (66)<br>12 (45) (64) (67)<br>(26) (61) (65) (68)<br>VSS | Digital block outputs.                                                                                                      |

# **Test Pin Description**

| Pin<br>No.                             | Symbol                                                | Pin<br>voltage | Equivalent circuit | Description                     |

|----------------------------------------|-------------------------------------------------------|----------------|--------------------|---------------------------------|

| 13<br>40<br>44<br>49<br>50<br>51<br>52 | TST1<br>TST3<br>TST4<br>TST7<br>TST8<br>TST9<br>TST10 | _              |                    | Test.<br>Leave these pins open. |

| 28<br>47<br>48<br>56                   | TST2<br>TST5<br>TST6<br>TST11                         | _              |                    | Test. Connect to GND.           |

## **Setting Conditions for Measuring Electrical Characteristics**

Use the Electrical Characteristics Measurement Circuit on page 22 when measuring electrical characteristics. For measurement, the digital block must be initialized and power saving must be canceled by performing Settings 1 and 2 below. In addition, the serial data must be set to the initial settings shown in the table below.

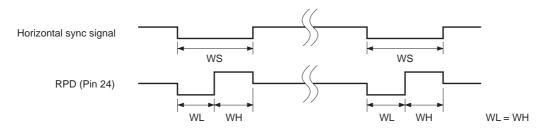

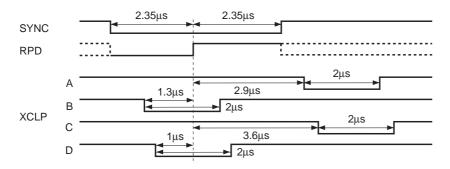

#### **Setting 1. Horizontal AFC adjustment**

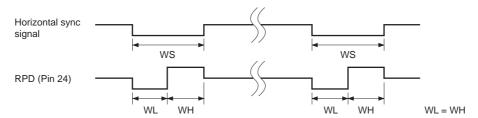

Input a signal and adjust the VCO using V22 so that WL and WH of the TP24 output waveform are the same.

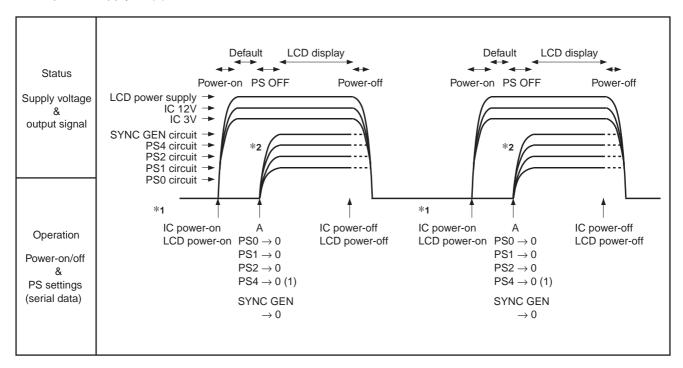

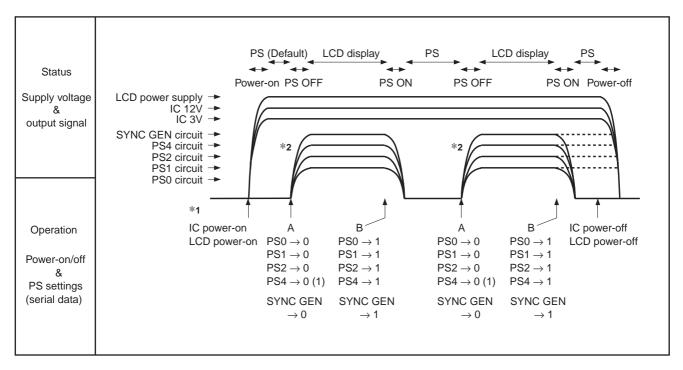

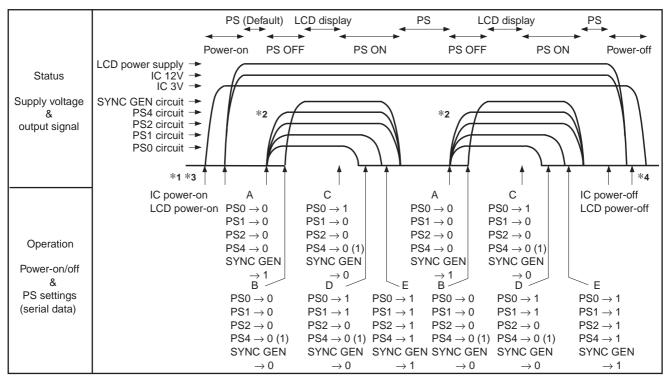

## Setting 2. Canceling power saving mode

The power-on default is power saving mode, so clear (set all "0") serial data PS0, PS1, PS2, PS4 and SYNC GEN.

Fig. 1. Horizontal AFC adjustment

# Serial data initial settings

| MS<br><b>M</b> S | SB  |     | ADDF | RESS |     | L  | SB - | MSB DATA                                                            |            |                 |             | LSB        |             |           |               |

|------------------|-----|-----|------|------|-----|----|------|---------------------------------------------------------------------|------------|-----------------|-------------|------------|-------------|-----------|---------------|

| D15              | D14 | D13 | D12  | D11  | D10 | D9 | D8   | D7                                                                  | D6         | D5              | D4          | D3         | D2          | D1        | D0            |

| 0                | 0   | 0   | 0    | 0    | 0   | 0  | 0    |                                                                     |            |                 | USER-       | BRIGHT     | (0          | 1000110   | /LSB)         |

| 0                | 0   | 0   | 0    | 0    | 0   | 0  | 1    |                                                                     |            |                 | SUB-BF      | RIGHT R    | . (10       | 0001010   | )/LSB)        |

| 0                | 0   | 0   | 0    | 0    | 0   | 1  | 0    |                                                                     |            |                 | SUB-BF      | RIGHT B    | (10         | 0001010   | )/LSB)        |

| 0                | 0   | 0   | 0    | 0    | 0   | 1  | 1    |                                                                     |            |                 | CONT        | RAST       | (00         | 0111111   | /LSB)         |

| 0                | 0   | 0   | 0    | 0    | 1   | 0  | 0    |                                                                     |            | S               | UB-CON      | ITRAST     | R (10       | 0011111   | /LSB)         |

| 0                | 0   | 0   | 0    | 0    | 1   | 0  | 1    |                                                                     |            | S               | UB-CON      | ITRAST     | B (10       | 0011111   | /LSB)         |

| 0                | 0   | 0   | 0    | 0    | 1   | 1  | 0    |                                                                     |            |                 | γ-          | -2         | (1          | 1111111   | /LSB)         |

| 0                | 0   | 0   | 0    | 0    | 1   | 1  | 1    |                                                                     |            |                 | γ-          | -1         | (1          | 1111111   | /LSB)         |

| 0                | 0   | 0   | 0    | 1    | 0   | 0  | 0    | 0                                                                   |            |                 | PSIG-E      | BRIGHT     | (10         | 011111/   | LSB)          |

| 0                | 0   | 0   | 0    | 1    | 0   | 0  | 1    |                                                                     |            |                 | CON         | /I-DC      | (10         | 0000000   | )/LSB)        |

| 0                | 0   | 0   | 0    | 1    | 0   | 1  | 0    |                                                                     |            |                 | COI         | LOR        | (00         | 0000000   | )/LSB)        |

| 0                | 0   | 0   | 0    | 1    | 0   | 1  | 1    |                                                                     |            |                 | Н           | JE         | (10         | 0000000   | )/LSB)        |

| 0                | 0   | 0   | 0    | 1    | 1   | 0  | 0    | 0                                                                   |            | LIMITER<br>LSB) | BL          | ACK-LIN    | /IITER (1   | 1111/LS   | SB)           |

| 0                | 0   | 0   | 0    | 1    | 1   | 0  | 1    | FILTER                                                              | (00/LSB)   | RE              | F (000/L    | SB)        | LPF         | = (000/L  | SB)           |

| 0                | 0   | 0   | 0    | 1    | 1   | 1  | 0    | PI                                                                  | CTURE-     | ·GAIN (0        | 0000/LS     | SB)        | 0           |           | RE-F0<br>LSB) |

| 0                | 0   | 0   | 0    | 1    | 1   | 1  | 1    | 0                                                                   | 0          | 0               | 0           | MODE (1)   | DA          | (000/L    | SB)           |

| 0                | 0   | 0   | 1    | 0    | 0   | 0  | 0    | 0                                                                   | 0          | SYNC GEN<br>(O) | PS 4<br>(0) | 0          | PS 2<br>(0) | PS 1 (0)  | PS 0<br>(0)   |

| 0                | 0   | 1   | 0    | 0    | 0   | 0  | 0    | SLSYP (1)                                                           | SLEXVD (0) | SLDWN (0)       | SLRGT (0)   | SLSH2 (1)  | SLSH1 (1)   | SLWD (0)  | SLPL (0)      |

| 0                | 0   | 1   | 0    | 0    | 0   | 0  | 1    | 0                                                                   | SLFL (0)   | SLFR (0)        | SL4096 (0)  | SLCLP2 (0) | SLCLP1 (0)  | SLVDP (0) | SLHDP (0)     |

| 0                | 0   | 1   | 0    | 0    | 0   | 1  | 0    | O O SLTST4 (0) SLTST3 (0) SLSH0 (1) SLTST2 (0) SLTST1 (0) SLTST0 (0 |            |                 |             |            | SLTST0 (0)  |           |               |

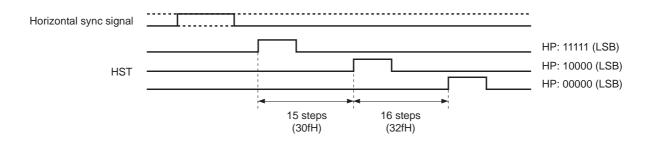

| 0                | 0   | 1   | 0    | 0    | 0   | 1  | 1    | 0                                                                   | 0          | 0               |             | H-POS      | SITION (    | 10000)    |               |

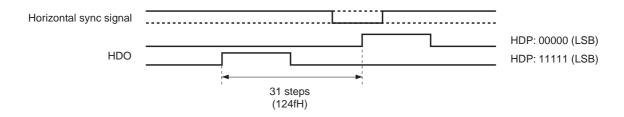

| 0                | 0   | 1   | 0    | 0    | 1   | 0  | 0    | 0                                                                   | 0          | 0               |             | HD-PO      | SITION      | (00000)   |               |

Note) If there is the possibility that data may be set at other than the above-noted addresses, set these data to "0".

# **Electrical Characteristics — DC Characteristics**

**Analog Block**

Unless otherwise specified, Ta = 25°C, Vcc1 = Vdd = 3.0V, Vcc2/Vcc3 = 12.0V, SW4 = off for the current consumption measurement, see page 11 for the DAC.

| Item                                             | Symbol            | Measurement conditions                | Min. | Тур. |      |    |

|--------------------------------------------------|-------------------|---------------------------------------|------|------|------|----|

| Current consumption 1 (Y/color difference input) | I1                | Measure the inflow current to Pin 63. |      | 27.0 | 37.0 | mA |

| Current consumption 2 (Y/color difference input) | 12                | Measure the inflow current to Pin 37. |      | 3.8  | 5.0  | mA |

| Current consumption 3 (Y/color difference input) | 13                | Measure the inflow current to Pin 41. |      | 0.90 | 1.3  | mA |

| Current consumption 1 (RGB input)                | IRGB1             | Measure the inflow current to Pin 63. |      | 23.0 | 30.0 | mA |

| Current consumption 2 (RGB input)                | IRGB2             | Measure the inflow current to Pin 37. |      | 3.8  | 5.0  | mA |

| Current consumption 3 (RGB input)                | IRGB3             | Measure the inflow current to Pin 41. |      | 0.90 | 1.3  | mA |

| Current consumption 1 (PS0 = 1)                  | IPS01             | Measure the inflow current to Pin 63. |      | 7.5  | 10.0 | mA |

| Current consumption 2 (PS0 = 1)                  | IPS02             | Measure the inflow current to Pin 37. |      | 0.18 | 0.35 | mA |

| Current consumption 3 (PS0 = 1)                  | IPS03             | Measure the inflow current to Pin 41. |      |      | 1.00 | μA |

| Current consumption 1 (PS2 = 1)                  | IPS21             | Measure the inflow current to Pin 63. |      | 26.5 | 36.5 | mA |

| Current consumption 1 (PS4 = 1)                  | IPS41             | Measure the inflow current to Pin 63. |      | 26.5 | 36.5 | mA |

| Current consumption 1 (SYNC GEN = 1)             | ISG1              | Measure the inflow current to Pin 63. |      | 7.0  | 9.5  | mA |

| Current consumption 2 (SYNC GEN = 1)             | ISG2              | Measure the inflow current to Pin 37. |      | 0.18 | 0.35 | mA |

| Current consumption 3 (SYNC GEN = 1)             | ISG3              | Measure the inflow current to Pin 41. |      |      | 1.00 | μA |

| FIL OUT pin voltage                              | V2                | During no input                       | 1.8  | 2.1  | 2.4  | V  |

| SYNC IN pin voltage                              | V3                | During no input                       | 1.8  | 1.1  | 1.4  | V  |

| SYNC OUT pin voltage                             | V4                | During no input                       |      | 0.2  | 0.4  | V  |

| F ADJ pin voltage                                | V8                |                                       | 0.8  | 1.1  | 1.4  | V  |

| R INJECT pin voltage                             | V17               |                                       | 0.4  | 0.7  | 1.0  | V  |

| SIG.C pin voltage                                | V30               |                                       | 5.8  | 6.0  | 6.2  | V  |

| B DC DET pin voltage                             | V31               |                                       | 1.5  | 1.8  | 2.1  | V  |

| R DC DET pin voltage                             | V33               |                                       | 1.5  | 1.8  | 2.1  | V  |

| G DC DET pin voltage                             | V35               |                                       | 1.5  | 1.8  | 2.1  | V  |

| PSIG DC DET pin voltage                          | V38               |                                       | 1.5  | 1.8  | 2.1  | V  |

| FIL IN pin voltage                               | V69               |                                       | 0.9  | 1.2  | 1.5  | V  |

| B/B-Y pin voltage 1                              | V70               | During Y/color difference input       | 1.7  | 2.0  | 2.3  | V  |

| B/B-Y pin voltage 2                              | V70               | During RGB input                      | 1.5  | 1.8  | 2.1  | V  |

| G/Y pin voltage                                  | V71               |                                       | 1.5  | 1.8  | 2.1  | V  |

| R/R-Y pin voltage 1                              | V70               | During Y/color difference input       | 1.7  | 2.0  | 2.3  | V  |

| R/R-Y pin voltage 2                              | V70               | During RGB input                      | 1.5  | 1.8  | 2.1  | V  |

| REF pin voltage (power saving mode)              | V7                | I7 = 1.5mA                            |      |      | 0.3  | V  |

| OSD input resistance                             | V57<br>V58<br>V59 | 12                                    | 80   | 100  | 120  | kΩ |

# Digital Block (including some analog block)

$(Ta = -15 \text{ to } +75^{\circ}\text{C}, V_{DD} = V_{CC}1 = 3.7 \text{ to } 3.6\text{V})$

| Item                           | Symbol                                | Measurement conditions | Min.                | Тур. | Max.                | Unit | Applicable pins |

|--------------------------------|---------------------------------------|------------------------|---------------------|------|---------------------|------|-----------------|

| High level input voltage       | VIH                                   |                        | $V_{DD} \times 0.7$ |      |                     | V    | *1              |

| Low level input voltage        | VIL                                   |                        |                     |      | $V_{DD} \times 0.3$ | V    |                 |

| High level threshold voltage   | V <sub>T+</sub> 1                     |                        |                     |      | 2.6                 | V    |                 |

| Low level threshold voltage    | VT-1                                  |                        | 0.6                 |      |                     | V    | *2              |

| Hysteresis voltage             | V <sub>T+</sub> 1 – V <sub>T</sub> –1 | Schmitt buffer         | 0.4                 |      |                     | V    |                 |

| High level threshold voltage   | VT+2                                  | Schmill buller         |                     |      | 2.6                 | V    |                 |

| Low level threshold voltage    | VT-2                                  |                        | 0.6                 |      |                     | V    | *3              |

| Hysteresis voltage             | VT+2 - VT-2                           |                        | 0.2                 |      |                     | V    |                 |

| High level input current       | <b>I</b> IH1                          | VI = VDD               |                     |      | 1.0                 | μΑ   | *4              |

| Low level input current        | <b> </b>                              | Vı = 0V                |                     |      | 1.0                 | μΑ   | •               |

| High level input current       | <b> </b>                              | VI = VDD               |                     |      | 3.0                 | μΑ   | *5              |

| Low level input current        | <b> </b> IL2                          | Vı = 0V                | 10                  | 40   | 100                 | μΑ   |                 |

| High level input current       | Іінз                                  | VI = VDD               | 10                  | 40   | 100                 | μΑ   | *6              |

| Low level input current        | lil3                                  | Vı = 0V                |                     |      | 3.0                 | μΑ   |                 |

| High level input current       | <b> </b>                              | VI = VDD               |                     |      | 1.0                 | μΑ   | *7              |

| Low level input current        | <b> </b>                              | Vı = 0V                |                     |      | 2.0                 | μΑ   |                 |

| Low level output voltage       | Vol1                                  | IoL = 1mA              |                     |      | 0.3                 | V    | *8              |

| High level output voltage      | Voн1                                  | Iон = −0.25mA          | 2.6                 |      |                     | V    |                 |

| Low level output voltage       | Vol2                                  | IoL = 2mA              |                     |      | 0.3                 | V    | *9              |

| High level output voltage      | Voн2                                  | Iон = −0.5mA           | 2.6                 |      |                     | V    |                 |

| Low level output voltage       | Vol3                                  | IoL = 4mA              |                     |      | 0.3                 | V    | *10             |

| High level output voltage      | gh level output voltage Vонз          |                        | 2.6                 |      |                     | V    |                 |

| Low level output voltage       | ow level output voltage Vol4          |                        |                     |      | 0.4                 | V    | *11             |

| High level output voltage VOH4 |                                       | Iон = −1.25mA          | VDD - 0.5           |      |                     | V    |                 |

| Output leak current            | loz                                   | High impedance status  |                     |      | 1.0                 | μΑ   | *12             |

<sup>\*1</sup> XCLR (Pin 25), CKI (Pin 22)

<sup>\*2</sup> CSYNC/HD (Pin 5), VD (Pin 10)

<sup>\*3</sup> SCK (Pin 14), SEN (Pin 15), SDAT (Pin 16)

<sup>\*4</sup> CSYNC/HD (Pin 5), CKI (Pin 22)

<sup>\*5</sup> XCLR (Pin 25)

<sup>\*6</sup> VD (Pin 10)

<sup>\*7</sup> SCK (Pin 14), SEN (Pin 15), SDAT (Pin 16)

<sup>\*8</sup> DWN (Pin 11), WIDE (Pin 12), VCK (Pin 66), VST (Pin 67), RGT (Pin 68)

<sup>\*9</sup> RPD (Pin 24), VDO (Pin 26), HDO (Pin 27), POF (Pin 45), HST (Pin 64), EN (Pin 65)

<sup>\*10</sup> HCK1 (Pin 61), HCK2 (Pin 62)

<sup>\*11</sup> CKO (Pin 21). However, when measuring the output pin (CKO), the input level of the input pin (CKI) should be 0V or VDD.

<sup>\*12</sup> RPD (Pin 24)

# **Electrical Characteristics**

## **AC Characteristics**

Unless otherwise specified, Settings 1 and 2, the serial data initial settings, and the following setting conditions are required.

Ta = 25°C, Vcc1 = 3.0V, Vcc2 = Vcc3 = 12V, GND1/2/3 = 0V, Vss = 0V, SW2 = ON, SW4 = ON, SW32/34/36 = OFF, no video input, SG1 input to TP5

Note: Serial data values in the table are HEX notation.

| Item                                                          | Symbol                                                                                                             | Serial data setting (HEX)                                                                                                   | Measurement conditions                                                                                                                                                 | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

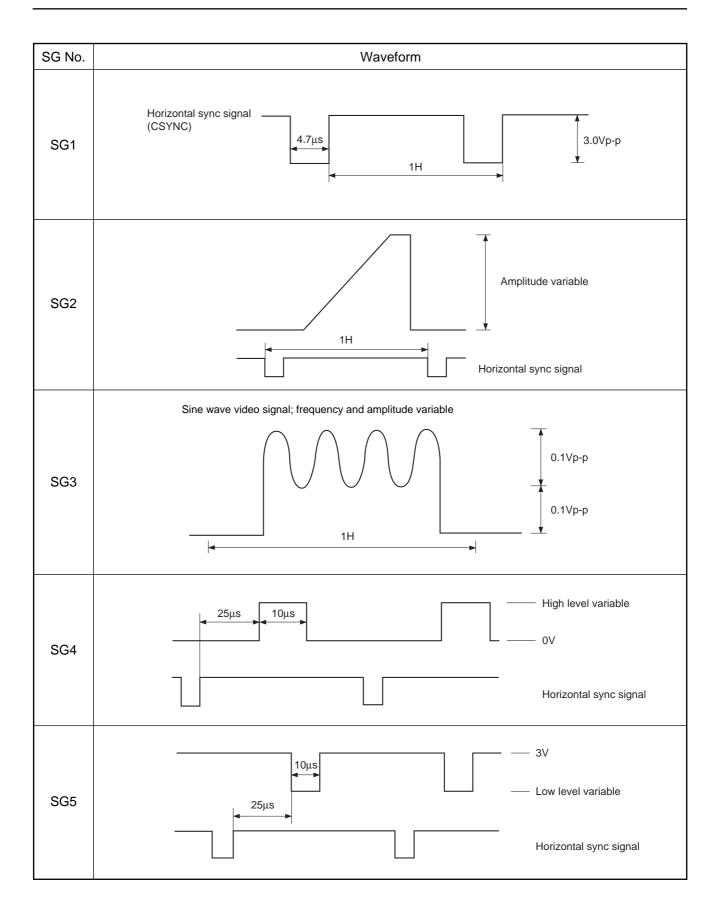

| Maximum gain between input and output Y/color difference      | Gмах                                                                                                               | CONT FFh                                                                                                                    | nput SG2 (50mVp-p) to TP71 and measure the output amplitude at TP36.                                                                                                   |      | 32   | 34   | dB   |

| Maximum gain<br>between input and<br>output<br>RGB            | GRGBMAX                                                                                                            | CONT FFh<br>MODE 00h                                                                                                        |                                                                                                                                                                        | 26   | 29   | 31   | dB   |

| Amount of contrast attenuation                                | Gcon                                                                                                               | CONT 00h                                                                                                                    | Assume the output amplitude at TP36 when SG2 (0.5Vp-p) is input to TP71 as GMIN.<br>$\Delta$ gcon = GMAX – GMIN                                                        | 25   | 30   |      | dB   |

| Inverted and non-inverted gain difference                     | ΔGΙΝΥ                                                                                                              | CONT 2Fh                                                                                                                    | Assume the inverted output amplitude at TP36 when SG2 (0.35Vp-p) is input to TP71 as Vinv, and the non-inverted output amplitude as Vninv. Δginv = 20 log (Vninv/Vinv) |      |      | ±0.3 | dB   |

| Gain difference                                               | in difference ΔGRGB1 CONT 2Fh Input SG2 (0.35Vp-p) to TP71 (TP70, TP72), measure the non-inverted output amplitude |                                                                                                                             |                                                                                                                                                                        |      | 0.6  | dB   |      |

| between R, G and B                                            | $\Delta G$ RGB $2$                                                                                                 | MODE 00h<br>CONT 2Fh                                                                                                        | at TP32, TP34 and TP36, and obtain the maximum and minimum difference between these values.                                                                            |      |      | 0.6  | uБ   |

| Sub-contrast                                                  | ΔGsc1                                                                                                              | SUB-CONT<br>00h                                                                                                             | Set CONT = 26h, input SG2 (0.35Vp-p) to TP71, and assume the non-inverted output amplitude at TP32 and TP34 when SUB-CONT R/B = 9Ah, 00h and FFh as V1, V2             |      | -5.5 | -4.5 | dB   |

| variable amount                                               | ΔGsc2                                                                                                              | SUB-CONT<br>FFh                                                                                                             | and V3, respectively.<br>$\Delta$ Gsc1 = 20 log (V3/V1)<br>$\Delta$ Gsc2 = 20 log (V2/V1)                                                                              | 2.0  | 2.7  |      | GD   |

| Sub-bright                                                    | ΔVsв1                                                                                                              | SUB-BRT<br>R, B 00h                                                                                                         | Set U-BRT = 1Ah and measure the non-<br>inverted level at TP32 and TP34 relative to                                                                                    |      | -1.5 | -1.0 | V    |

| variable amount                                               | ΔVsв2                                                                                                              | SUB-BRT<br>R, B FFh                                                                                                         | the non-inverted black level at TP36 when SUB-BRT R/B = FFh and 00h.                                                                                                   |      | 1.2  |      | V    |

| Black limiter  VBL1  O0h  RI K-I IM = 00h and 15h, and assure |                                                                                                                    | Set U-BRT = FFh, measure the inverted and non-inverted black limit level at TP36 when BLK-LIM = 00h and 1Fh, and assume the | ±1.6                                                                                                                                                                   | ±2.1 | ±2.7 | V    |      |

| variable amount                                               | V <sub>B</sub> L2                                                                                                  | BLK-LIM<br>1Fh                                                                                                              | difference from the output DC voltage as V <sub>BL</sub> 1 and V <sub>BL</sub> 2, respectively.                                                                        | ±4.7 | ±5.1 | ±5.4 | V    |

| Item                                                | Symbol                                 | Serial data setting (HEX)                                                                      | Measurement conditions                                                                                                                                                                                     | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| White limiter                                       | VwL1                                   | WHITE-LIM<br>00h                                                                               | Set CONT = FFh, input SG2 (0.35Vp-p) to TP71, measure the inverted and non-inverted white limit level when WHITE-LIM = 00h and                                                                             |      | ±0.6 | ±0   | V    |

| variable amount                                     | VwL2                                   | WHITE-LIM 03h, and assume the difference from output DC voltage as Vwl1 and Vwl2 respectively. |                                                                                                                                                                                                            | ±0.6 | ±1.2 | ±1.8 | V    |

| Black level<br>difference between<br>R, G and B     | ΔVв                                    |                                                                                                | Measure the non-inverted black level at TP32, TP34 and TP36, and obtain the maximum and minimum difference between these values.                                                                           |      |      | 300  | mV   |

| RGB and PSIG output DC voltage                      | Vc                                     |                                                                                                | Measure the output DC level (average voltage) at TP32, TP34, TP36 and TP39.                                                                                                                                | 5.8  | 6.0  | 6.2  | ٧    |

| DC voltage<br>difference between<br>RGB and PSIG    | ΔVc                                    |                                                                                                | Measure the output average voltage difference at TP32, TP34 and TP39 relative to the output average voltage at TP36.                                                                                       |      |      | ±200 | mV   |

| PSIG-BRT                                            | VPB1                                   | PSIG-BRT<br>01h                                                                                | Measure the inverted and non-inverted black level when PSIG-BRT = 01h and 7Fh and                                                                                                                          |      |      | ±0.7 | V    |

| variable amount                                     | VPB2                                   | PSIG-BRT<br>7Fh                                                                                | ssume the difference from the average DC oltage Vc as VPB1 and VPB2, respectively.                                                                                                                         |      |      |      | V    |

| USER-BRT                                            | ΔUB1                                   | U-BRT<br>00h                                                                                   | Measure the inverted and non-inverted black level at TP36 when U-BRT = 00h and 7Ah                                                                                                                         |      | ±0.8 | ±1.5 | V    |

| variable amount                                     | ΔUB2                                   | U-BRT<br>7Ah                                                                                   | and assume the difference from the average voltage as $\Delta$ UB1 and $\Delta$ UB2, respectively.                                                                                                         | ±4.5 | ±4.9 |      |      |

| Level difference<br>between PSIG-BLK<br>and BLK-LIM | ΔVBB                                   | SLWD<br>1                                                                                      | Set BLK-LIM = 00h and measure the difference between the inverted and non-inverted black level at TP36 and TP39.                                                                                           |      |      | 350  | mV   |

| Hue                                                 | θ1                                     | HUE 00h                                                                                        | Set U-BRT = 23h, CONT = 80h, COLOR = 40h, and assume the amplitude at TP32 when SG4 (56mVp-p) is input to TP72 as V1. Similarly, assume the amplitude at TP34 when SG4 (100mVp-p) is input to TP70 as V2.  | -20  | -25  |      | deg  |

| variable amount                                     | θ2                                     | HUE FFh                                                                                        | $\theta = \tan - 1$ (V1/V2). Assume the $\theta$ when HUE = 00h, 80h and FFh as $\theta a$ , $\theta b$ and $\theta c$ , respectively. $\theta 1 = \theta a - \theta b$ , $\theta 2 = \theta c - \theta b$ | 20   | 25   |      | deg  |

| Picture                                             | GP1                                    | PIC-G<br>01h                                                                                   | Set CONT = 2Fh, input SG3 to TP71, and measure the TP36 amplitude at f0 relative to the TP36 amplitude at 100kHz when PIC-G                                                                                | -1.5 | 0    | 1.5  | ٦D   |

| variable amount                                     | GP2                                    | PIC-G<br>1Fh                                                                                   | = 01h and 1Fh. f0 at PIC-f0 = 00h, 01h, 02h and 03h is 2MHz, 2.2MHz, 2.6MHz and 2.9MHz, respectively.                                                                                                      |      | 12   |      | dB   |

| Color                                               | GC1                                    | COLOR<br>00h                                                                                   | Input SG4 (50mVp-p) to TP70 and TP72, and assume the output amplitude at TP32 and TP34 when COLOR = 00h, 80h and FFh                                                                                       |      | -30  | -20  | ΑĐ   |

| variable amount                                     | and TP34 when COLOR = 00h, 80h and FFh |                                                                                                | 5.0                                                                                                                                                                                                        | 6.0  |      | dB   |      |

| Item                                                | Symbol      | Serial data setting (HEX) | Measurement co                                                                                                                                                | onditions                                                                                                                                                       | Min. | Тур. | Max. | Unit    |

|-----------------------------------------------------|-------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---------|

|                                                     | B-Y/<br>R-Y |                           | Assume the TP34 output w<br>is input to TP72 as RR, the<br>when SG4 (0.1Vp-p) is inp                                                                          | TP32 amplitude                                                                                                                                                  | 0.85 | 1.00 | 1.15 |         |

| Matrix amplitude ratio                              | G-Y/<br>R-Y | CONT 63h<br>COLOR<br>6Fh  | color input to TP72 as RG, and the TP32 amplitude 0                                                                                                           |                                                                                                                                                                 | 0.41 | 0.51 | 0.61 |         |

|                                                     | G-Y/<br>B-Y |                           | B-Y/R-Y = RR/BB,<br>G-Y/R-Y = RG/RR,<br>G-Y/B-Y = BG/BB                                                                                                       | 0.15                                                                                                                                                            | 0.19 | 0.23 |      |         |

| LPF characteristics                                 | fc1         | LPF 01h<br>MODE 00h       | •                                                                                                                                                             | Input SG3 to TP71 and measure the frequency which results in –3dB relative to                                                                                   |      |      | 2.5  | MHz     |

| LFF Characteristics                                 | fc2         | LPF 07h<br>MODE 00h       | the TP36 amplitude at 100 01h and 07h.                                                                                                                        | )kHz when LPF =                                                                                                                                                 | 5.0  | 6.4  |      | IVII IZ |

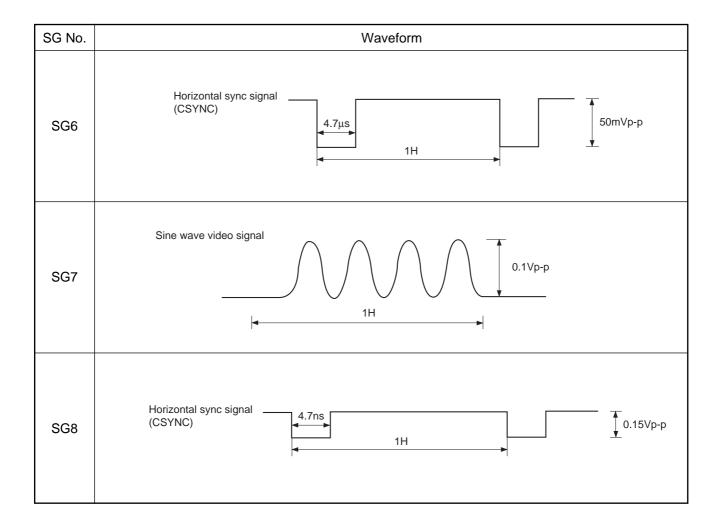

| Trap                                                | fo1         | MODE 00h                  | (13.5MHz) to TP70, TP71 ameasure the amount by wh                                                                                                             | Set U-BRT = 30h, CONT = DFh, input SG7 (13.5MHz) to TP70, TP71 and TP72, and measure the amount by which the output is attenuated when FILTER = 01h relative to |      |      |      | · dB    |

| characteristics                                     | fo2         | MODE 00h                  | to TP70, TP71 and TP72, a amount by which the output                                                                                                          | FILTER = 00h. Similarly, input SG7 (14.5MHz) to TP70, TP71 and TP72, and measure the amount by which the output is attenuated when FILTER = 00h.                |      |      |      | ub      |

| Frequency response                                  | f RGB       | MODE 00h                  | Set SW32, SW34 and SW3 to TP70, TP71 and TP72, a frequency which results in TP32, TP34 and TP36 amp                                                           | 5.5                                                                                                                                                             |      |      | MHz  |         |

| REF adjustment                                      | VREF1       | REF 00h                   | Measure the REF pin output voltage when                                                                                                                       | Output current                                                                                                                                                  | 1.20 | 1.35 | 1.50 | V       |

| range                                               | VREF2       | REF 07h                   | REF = 00h and 07h.                                                                                                                                            | 1.5mA, sink only                                                                                                                                                | 1.90 | 2.05 | 2.20 | V       |

| DA adjustment                                       | VDA1        | DA 00h                    | Measure the DA output                                                                                                                                         | Output current<br>1.0mA                                                                                                                                         |      |      | 0.3  | V       |

| range                                               | VDA2        | DA 07h                    | voltage when DA = 00h and 07h.                                                                                                                                | Output current<br>-1.0mA                                                                                                                                        | 2.7  |      |      | V       |

| Internal DAC<br>differential<br>non-linearity error | SDL         |                           | Measure under the measure for each adjustment range                                                                                                           |                                                                                                                                                                 | -1.5 |      | 1.5  | LSB     |

| Internal DAC non-linearity error                    | SL          |                           | Measure under the measure for each adjustment range                                                                                                           |                                                                                                                                                                 | -2.0 |      | 2.0  | LSB     |

| Gamma                                               | Δγ1         | CONT 41h                  | Input SG2 (0.35mVp-p) to TP71 and measure the amplitude at TP32, TP34 and TP36. Assume the output amplitude when GAMMA1 = FFh as V1, when GAMMA1 = 3Fh as V2, |                                                                                                                                                                 | 12   | 14   | 16   | dB      |

| characteristics                                     | Δγ2         | JON 4111                  | and when GAMMA1 = GAM<br>$\Delta \gamma 1$ = 20 log (V1/V2)<br>$\Delta \gamma 2$ = 20 log (V3/V2)                                                             | 12                                                                                                                                                              | 14   | 16   | ub   |         |

| H FIL gain                                          | Ghfil       |                           | Input SG6 to TP69 and mo amplitude at TP2.                                                                                                                    | easure the output                                                                                                                                               | 15.0 | 17.0 |      | dB      |

| Item                                 | Symbol      | Serial data setting (HEX) | Measurement conditions                                                                                                                                                                                      | Min. | Тур. | Max. | Unit |

|--------------------------------------|-------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| COMMON control range                 | COMpc       |                           | Measure the COM output DC voltage when COM-DC = 00h and FFh, and measure the difference from the COM output DC voltage when COM-DC = 80h.                                                                   | ±1.0 | ±1.3 |      | V    |

| SYNC IN sensitivity current          | ISYNC       |                           | Gradually increase the SYNC IN outflow current and measure the current at which SYNC OUT switches to high.                                                                                                  | 20   | 31   |      | μA   |

| SYNC OUT on voltage                  | VOsync      |                           | Measure the SYNC OUT pin voltage during SYNC IN no input.                                                                                                                                                   |      | 0.2  | 0.4  | V    |

| OSD threshold                        | Vth1<br>OSD |                           | Input SG4 to TP57, TP58 and TP59, gradually raise the high level from 0V, and assume the high level voltage at which the output level goes to BLK-LIM level as                                              | 0.8  | 1.0  | 1.2  | V    |

| value                                | Vth2<br>OSD |                           | Vth1OSD, and the high level voltage at which the output level goes to WHITE-LIM level as Vth2OSD.                                                                                                           | 1.8  | 2.0  | 2.2  | V    |

| Propagation delay time between input | tLH1        |                           | Set SW32, SW34 and SW36 = ON, input SG4 (0.35Vp-p) to TP71, and measure                                                                                                                                     | 70   | 120  | 170  |      |

| and output Y/color difference 1      | tHL1        |                           | the propagation delay time of the non-<br>inverted output rise and fall at TP32, TP34<br>and TP36 from TP71.                                                                                                | 80   | 130  | 180  | ns   |

| Propagation delay time between input | tLH2        | MODE                      | Set SW32, SW34 and SW36 = ON, input SG4 (0.35Vp-p) to TP70, TP71 and TP72, and measure the propagation delay time of the non-inverted output rise and fall at TP32, TP34 and TP36 from TP70, TP71 and TP72. |      | 110  | 160  | ns   |

| and output<br>RGB input              | tHL2        | 00h                       |                                                                                                                                                                                                             |      | 110  | 160  | 113  |

| Propagation delay time between input | tLH3        | PIC-G                     | Set SW32, SW34 and SW36 = ON, input SG4 (0.35Vp-p) to TP71, and measure the propagation delay time of the non-                                                                                              | 270  | 330  | 390  | ne   |

| and output<br>Y/color difference 2   | tHL3        | 01h                       | inverted output rise and fall at TP32, TP34 and TP36 from TP71.                                                                                                                                             | 270  | 330  | 390  | ns   |

| Propagation delay                    | tLH4        |                           | Set SW32, SW34 and SW36 = ON, input SG4 (3Vp-p) to TP57, TP58 and TP59,                                                                                                                                     | 90   | 130  | 170  |      |

| time between OSD input and output    | tHL4        |                           | and measure the propagation delay time of<br>the non-inverted rise and fall at TP70, TP71<br>and TP72 from TP57, TP58 and TP59.                                                                             | 170  | 210  | 250  | ns   |

| Propagation delay time between H FIL | tLH7        |                           | Input SG6 to TP69 and measure the                                                                                                                                                                           | 500  | 700  | 900  | no   |

| and FIL OUT                          | tHL7        |                           | propagation delay time of the rise and fall at TP2 from TP69.                                                                                                                                               |      | 300  | 500  | ns   |

| Propagation delay time between       | tLH8        |                           | Set SW2 = OFF, input SG8 to TP3, and                                                                                                                                                                        | 140  | 200  | 260  | ns   |

| SYNC IN and<br>SYNC OUT              | tHL8        |                           | measure the propagation delay time of the rise and fall at TP4 from TP3.                                                                                                                                    |      | 100  | 160  | 113  |

| Item                        | Symbol | Serial data setting (HEX) | Measurement conditions                                                                         | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|---------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

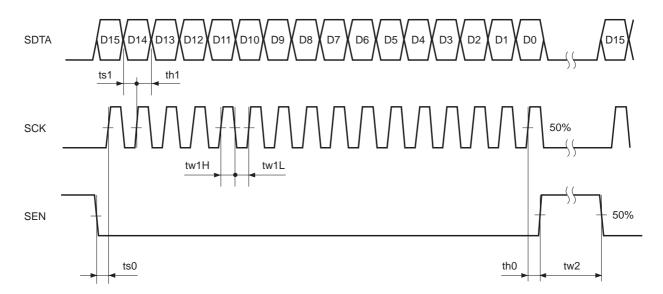

| Data setup time             | ts0    |                           | SEN setup time, activated by the rising edge of SCK. (See Fig. 4.)                             | 150  |      |      | ns   |

| Data setup time             | ts1    |                           | SDAT setup time, activated by the rising edge of SCK. (See Fig. 4.)                            |      |      |      | 113  |

| Data hold time              | th0    |                           | SEN hold time, activated by the rising edge of SCK. (See Fig. 4.)                              | 150  |      |      | nc   |

| Data Hold time              | th1    |                           | SDAT hold time, activated by the rising edge of SCK. (See Fig. 4.)                             | 150  |      |      | ns   |