# mos digital integrated circuit $\mu PD1703C-011$

# PHASE LOCKED LOOP FREQUENCY SYNTHESIZER FM/AM DIGITAL TUNING SYSTEM CONTROLLER CMOS LSI

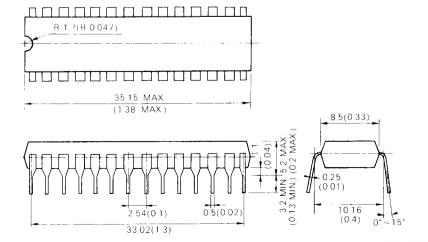

The  $\mu$ PD1703C-011 is a CMOS LSI designed for using as a PLL Frequency Synthesizer Digital Tuning System Controller. The  $\mu$ PD1703C 011 provides a set of fluorescent indicator panel (FIP) segment drivers, a clock generator and a power-on clear circuit. The  $\mu$ PD1703C-011 is packaged in a 28 pin slim dual in-line package (DIP).

#### **FEATURES**

- PLL, swallow counter and system controller are realized in a single chip.

- Fluorescent indicator panel driver incorporated (segment outputs)

- Internal display decorder for 4.5 digit multiplexed display

- Very low stand-by current···less than 10 μA

- High speed and low power consumption due to CMOS

- High reference frequency due to pulse swallowing (FM band: 25 kHz)

It results in a high carrier-to-noise ratio.

- Internal clock oscillator and divider circuit.

- Automatic power-on clear without any external components.

- Preset memory address display (External latch/decorder is required.)

- Display brightness control (DIMMER) · · · · · Duty ratio 1:4

- FM/AM tuner · · · · · U.S., Europe and Japan bands

- External programmable IF offset for FM band (10.650 MHz, 10.675 MHz, 10.700 MHz, 10.725 MHz)

#### **FUNCTION OF TUNER**

- Automatic up or down search (SEEK)

- Manual up or down search

- Preset station memory call

Preset station memory . . . . . . . FM: 6 stations, AM: 6 stations

• Last station memory . . . . . . FM: 1 station, AM: 1 station

#### PACKAGE DIMENSIONS Unit: mm (inches)

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage             | $V_{DD}$  | -0.3 to +6.0                          | V  |

|----------------------------|-----------|---------------------------------------|----|

| Input Voltage              | ٧ı        | $-0.3$ to $V_{\mbox{DD}}$             | V  |

| Output Voltage             | $v_0$     | $-0.3$ to $V_{\mbox{\scriptsize DD}}$ | V  |

| Output Breakdown Voltage * | $V_{BDS}$ | <b>-35</b>                            | V  |

| Output Current             | ЮН        | -10                                   | mΑ |

| Storage Temperature        | Tstg      | -55 to +125                           | °C |

| Operating Temperature      | Topt      | -35 to +75                            | °C |

<sup>\* :</sup> Segment Output Terminals (P-ch open drain)

# ELECTRICAL CHARACTERISTICS (Ta=-35 to +75 $^{\circ}$ C, V<sub>DD</sub>=4.5 to 5.5 V)

| CHARACTERISTIC            | SYMBOL                        | MIN.               | TYP. | MAX.               | UNIT | TEST CONDITIONS                           |

|---------------------------|-------------------------------|--------------------|------|--------------------|------|-------------------------------------------|

|                           | V <sub>I</sub> H1             | 0.8V <sub>DD</sub> |      | V <sub>DD</sub>    | V    | SD terminal                               |

| High Level Input Voltage  | V <sub>1H2</sub>              | 0.7V <sub>DD</sub> |      | V <sub>DD</sub>    | V    | CE terminal                               |

|                           | V <sub>1</sub> H3             | 0.6V <sub>DD</sub> |      | V <sub>DD</sub>    | V    | K0 to K3 terminals                        |

|                           | V <sub>IL1</sub>              | 0                  |      | 0.3V <sub>DD</sub> | ٧    | CE terminal                               |

| Low Level Input Voltage   | V <sub>1</sub> L <sub>2</sub> | 0                  |      | 0.2V <sub>DD</sub> | V    | SD, K0 to K3 terminals                    |

|                           | V <sub>OH1</sub>              | 4.0                |      |                    | V    | EO, D, MUTE: I <sub>OH</sub> =-0.5 mA     |

| High Level Output Voltage | V <sub>OH2</sub>              | 3.0                |      |                    | V    | SEG: I <sub>OH</sub> =-0.5 mA             |

|                           | V <sub>OH3</sub>              | 4.0                |      |                    | V    | PSC: I <sub>OH</sub> =-0.2 mA             |

|                           | V <sub>OL1</sub>              |                    |      | 0.5                | V    | EO: IOL=0.5 mA                            |

| Low Level Output Voltage  | V <sub>OL2</sub>              |                    |      | 0.5                | V    | D, MUTE, PSC: I <sub>OL</sub> =0.2 mA     |

| High Level Input Current  | ΙΉ                            | 5.0                | 25   | 100                | μΑ   | K: V <sub>I</sub> =V <sub>DD</sub> =5.0 V |

|                           | fin1                          | 0.5                |      | 2.5                | MHz  | AM: vi=1.0Vp-p, DC cut sine wave          |

| Frequency Response        | fin2                          | 0.5                |      | 8.8                | MHz  | FM: vi=0.8Vp-p, DC cut<br>square wave     |

| Supply Voltage Rise Time  | Tr                            |                    |      | 0.5                | s    | V <sub>DD</sub> : 0 → 4.5 V               |

| Supply Current            | <sup>1</sup> DD               |                    |      | 10                 | μА   | CE: Low Level                             |

| Output Off Leak Current   | IOFF                          |                    |      | -5.0               | μА   | SEG: V <sub>DS</sub> =-30 V               |

#### SYSTEM DESCRIPTION

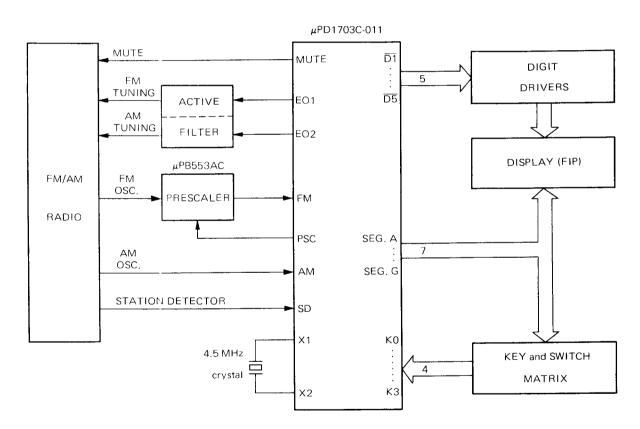

NEC's Digital Tuning System provides full electronic control of a vari-cap tuned FM/AM radio receiver and stereo. The block diagram of the system is shown in Fig. 1. This is a Phase Locked Loop Digital Tuning System which consists of two integrated circuits; controller plus PLL in a single chip, and two-modulus prescaler.

The controller chip (µP:D1703C-011) provides Phase Locked Loop capability with on-chip frequency division, a reference oscillator whose frequency is controlled by an external crystal of 4.5 MHz, and phase comparator circuitry. It accepts directly an AM local oscillator signal and an FM signal from two-modulus prescaler (µPB553AC), and outputs control signals for closed loop operation of these oscillators. The outputs drives filters for supplying analog voltages to the vari-cap tuners. The controller also provides the signals to drive the display. The frequency of the tuned station is displayed on a 4.5 digit multiplexed display. Six favorite stations on each band can be stored as well as "last stations tuned" information.

The two-modulus prescaler (µPB553AC) is suitable for pulse swallowing in this system.

Fig. 1 BLOCK DIAGRAM

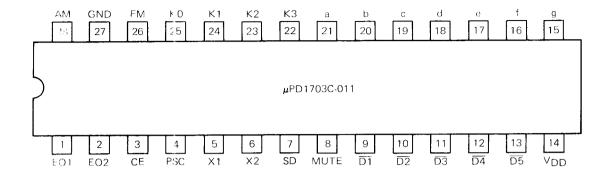

### PIN CONNECTION (Top View)

#### **EXPLANATION OF INPUT AND OUTPUT TERMINALS**

| E01<br>E02      | These three-state outputs are used (via active filters) to supply analog voltages to the tuner vari-cap for controlling the local oscillators.                |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CE              | This input is used to designate the stand-by mode to the chip.  It is low to designate the stand-by mode. (PLL: disable, display: off, clock generator: stop) |  |  |  |

| PSC             | This output is used to control the division ratio of the FM two-modulus prescaler (µPB553AC).                                                                 |  |  |  |

| X1, X2          | These inputs are for connection to a 4.5 MHz crystal.                                                                                                         |  |  |  |

| SD              | This input is used to control the station searching operation (AU/AD). It is high to indicate the presence of a station and the operation is terminated.      |  |  |  |

| MUTE            | This output line is high to mute the radio in the case of station change, band change, and so on.                                                             |  |  |  |

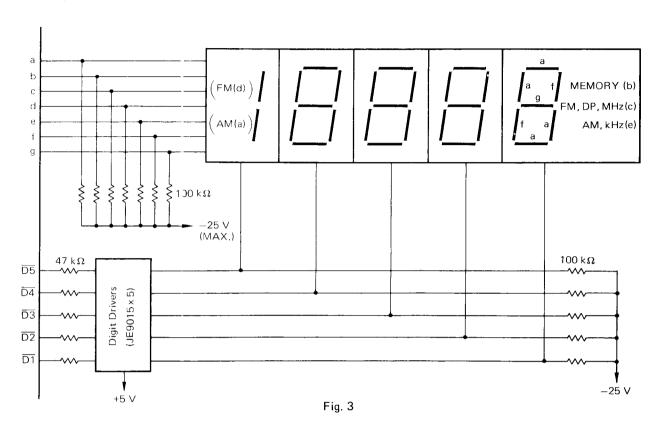

| D1 to D5        | These outputs are used as digit drivers for the display. (Active low)                                                                                         |  |  |  |

| V <sub>DD</sub> | This is a 4.5 to 5.5 volt supply for the chip.                                                                                                                |  |  |  |

| a to g          | These outputs are p-ch open drain used as segment drivers for the display. They are also used as vertical drive for the control key and mode switch matrix.   |  |  |  |

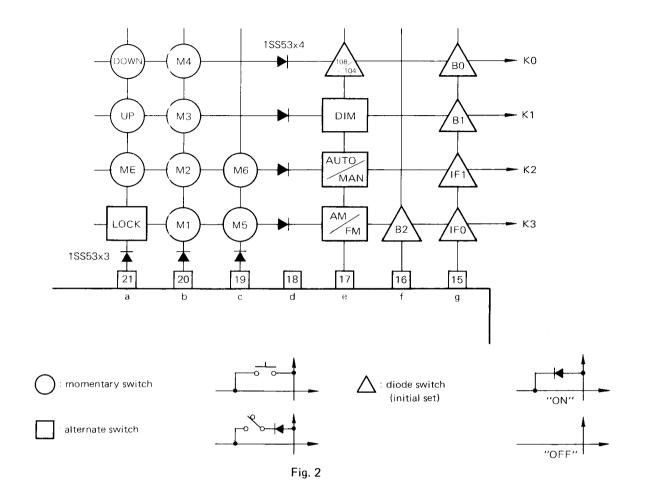

| K0 to K3        | These inputs are from seven by four matrix. Various functions are entered through the matrix. See Fig. 2 for the matrix assignments.                          |  |  |  |

| FM              | This is the FM band local oscillator input. The frequency is divided by 16/17 using a two-modulus prescaler (µPB553AC).                                       |  |  |  |

| GND             | System ground.                                                                                                                                                |  |  |  |

| AM              | This is the AM band local oscillator input.                                                                                                                   |  |  |  |

#### CONTROL KEY AND MODE SWITCH MATRIX

#### • Searching of the station

UP, DOWN

\* AUTO/MANUAL switch: ON (SEEK)

A momentary depression causes automatic up or down searching by the speed of 80 ms/ch until SD terminal is activated (active high) or any key is depressed.

\* AUTO/MANUAL switch: OFF (Manual searching)

A momentary depression will tune to next channel, and continuous depression more than 0.5 second allows traversing up or down the entire band by the speed of 80 ms until the key is released.

#### Preset of the station

ME The tuning information is stored into internal RAM by depressing ME key and then desired memory key within 5 seconds from the time ME key was initially depressed. If any key is depressed in this period, the ME function is cancelled.

M1 to M6 Six favorite stations can be recalled from internal RAM for each band. When it is switched from one band to the other band, it will tune to "Last-tuned to station" on that band. Each time a station is changed, the controller provides a signal to mute the tuner.

#### • Selection of the radio band

B0, B1

These switches are for selection of the district.

AM/FM

This switch is for selection of the radio band.

B2

This switch is for selection of the receiving band and channel spacing of AM radio for U.S.

band.

|     |                |       |          | Selected Band       |                      |         |         |  |  |  |

|-----|----------------|-------|----------|---------------------|----------------------|---------|---------|--|--|--|

| B0  | BO B1 B2 AM/FM | AM/FM | District | Receiving Frequency | Channel Spacing      | IF      |         |  |  |  |

|     |                |       | off      | FM Japan            | 76.1 to 89.9 MHz     | 100 kHz | *1      |  |  |  |

| off | off            | X     | on       | AM Japan            | 522 to 1611 kHz      | 9 kHz   | 450 kHz |  |  |  |

|     |                |       | off      | FM Europe           | 87.5 to 108.0 MHz *2 | 50 kHz  | *1      |  |  |  |

| on  | off            | X     | on       | AM Europe           | 522 to 1611 kHz      | 9 kHz   | 450 kHz |  |  |  |

|     |                | Х     | off      | FM U.S.             | 87.9 to 107.9 MHz    | 200 kHz | *1      |  |  |  |

| off | on             | on    | on       | AM U.S.             | 522 to 1611 kHz      | 9 kHz   | 450 kHz |  |  |  |

|     |                | off   | on       | AM U.S.             | 530 to 1620 kHz      | 10 kHz  | 450 kHz |  |  |  |

X : Don't care.

Table 1.

#### \*1 FM band IF offset

IFO, IF1 These switches program the chip to accept 4 different intermediate frequencies for each band in 25 kHz steps.

| 150 | 150 151 | Intermediate Frequency (MHz) |        |        |  |  |

|-----|---------|------------------------------|--------|--------|--|--|

| IF0 | IF1     | Japan                        | U.S.   | Europe |  |  |

| off | on      | 10.750                       | 10.650 | 10.650 |  |  |

| on  | on      | 10.725                       | 10.675 | 10.675 |  |  |

| off | off     | 10.700                       | 10.700 | 10.700 |  |  |

| on  | off     | 10.675                       | 10.725 | 10.725 |  |  |

Table 2.

\*2 108/104 This switch is for selection of receiving frequency of FM radio for Europe band.

| 108/104 | Receiving Frequency |  |  |  |

|---------|---------------------|--|--|--|

| on      | 87.50 to 108.00 MHz |  |  |  |

| off     | 87.50 to 104.00 MHz |  |  |  |

Table 3.

#### • Display interface

The center frequency of tuned station is displayed on a 4.5 digit FIP. The  $\mu$ PD1703C-011 provides direct interface to the FIP. The  $\mu$ PD1703C-011 interfaces with all the devices requiring up to 30 V levels. The segment outputs go directly to the segments (anodes) of the multi-digit 7 segment FIP. The digit outputs go to PNP transistor array to drive the digits (grids) of the FIP. The LED display can be driven by using appropriate interface circuits.

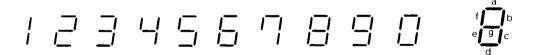

#### Display format

O Segment Pattern

#### Display brightness control (DIMMER)

DIM This switch is for selection of display brightness.

ON . . . . Display brightness is reduced. (Duty factor: 1/28) OFF . . . . Display brightness is ordinary. (Duty factor: 1/7)

#### • Protection from the miss key input

LOCK This switch is for protection from miss key input.

ON . . . . All of the momentary keys input are disabled. OFF . . . . All of the momentary keys input are enabled.

#### Protection of the key chattering

\* Key make time . . . . . . less than 15 ms

\* Key break time ..... less than 15 ms

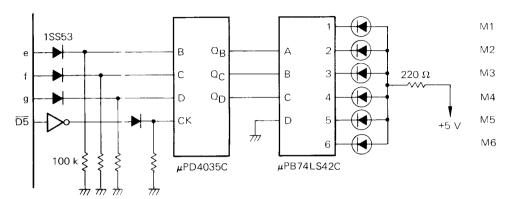

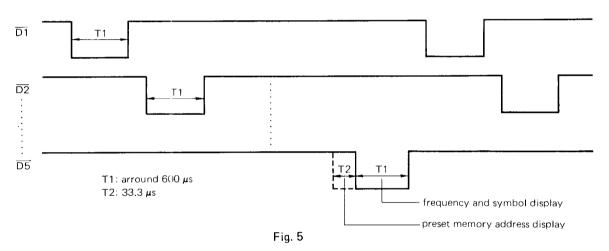

#### • Preset memory address display

In the case of memorizing the displayed frequency or recalling a preset memory, the chip provides the data to display preset memory address corresponded to the disired memory key.

At the timing T2 of digit output D5, the data of memory address are provided segment output e, f and g. The data are binary coded decimal (BCD).

Fig. 4

\* The segment output at the timing T1, T2 of digit output  $\overline{D5}$  is as follows.

| Segment<br>Timing | а     | b   | С   | d       | е         | f     | g |

|-------------------|-------|-----|-----|---------|-----------|-------|---|

| T1                | (AM)  | (1) | (1) | (FM/DP) | 1         | blank |   |

| T2                | blank |     |     | E       | 3CD outpu | t     |   |

Table 4.

\* Segment output and preset memory address.

| g | f | e | Address |

|---|---|---|---------|

| 0 | 0 | 1 | M1      |

| 0 | 1 | 0 | M2      |

| 0 | 1 | 1 | М3      |

| 1 | 0 | 0 | M4      |

| 1 | 0 | 1 | M5      |

| 1 | 1 | 0 | M6      |

Table 5.

### (center tap: -21 V) MEMORY FIP 7D8 2.3 V<sub>ac</sub> FM MHz KHz ΑM 18853 . 220 a +5 v 100 kΩ BITIES A 3 ZIT µPB74LS42C μPD4035C JE9015 100 kΩ § -25 V 100 kΩ Ş ± 0.022 µF 7 x2 SD MUTE 51 52 53 54 55 VDD 100 kΩ § −25 V 📥 µPD1703C-011 MUTE -γνν-47 kΩ 15553 10.022 F 33 KG Station Detector 18853 🛊 🙀 🙀 \*TOYOCOM TQC-231A-8C (4.5 MHz) 0.022 µF ] 2.2 ks (momentary switch) 18853 (alternate switch) 0.033 µF 2.2 µF back-up capacitor # (diode matrix) JE9014x2 to FM VCO (Vtun) 2.2 μF B 7 6 5 NC NC PSC OUT MPB553AC VCC IN CHK GND 10kឆ**>** main switch 0.022 µF 0.022 µF 🛨 0.022 µF 10 kΩ§ to AM VCO (Vtun) from AM VCO from FM VCO +5.7 V

APPLICATION CIRCUIT