CMOS LSI

## **Overview**

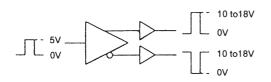

The LC4105V is a level shifter driver that converts 5-V signals into signals with amplitudes between 10 and 18 V.

### **Features**

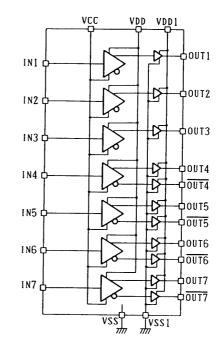

- · Seven inputs and eleven outputs IN1 to IN3 produce only true outputs. IN4 to IN7 produce both true and inverted outputs.

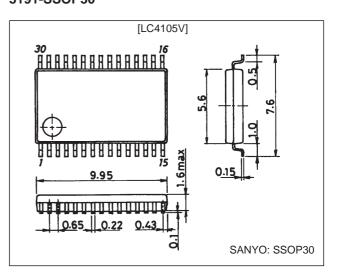

- Slim SSOP-30 package

# **Package Dimensions**

unit: mm 3191-SSOP30

### **Specifications** Absolute Maximum Ratings at Ta = $25^{\circ}C \pm 2^{\circ}C$ , all voltages are relative to V<sub>SS</sub>, unless otherwise specified

| Parameter            | Symbol            | Conditions |      | Unit |                      |      |

|----------------------|-------------------|------------|------|------|----------------------|------|

|                      |                   |            | min  | typ  | max                  | Unit |

| Power supply voltage | V <sub>DD</sub>   |            | -0.3 |      | 20                   | V    |

|                      | V <sub>DD</sub> 1 |            | -0.3 |      | 20                   | V    |

|                      | V <sub>CC</sub>   |            | -0.3 |      | 7                    | V    |

|                      | V <sub>SS</sub> 1 |            | -0.3 |      | +0.3                 | V    |

| Input voltage        | V <sub>IN</sub>   | IN1 to IN7 | -0.5 |      | V <sub>CC</sub> +0.5 | V    |

| Power dissipation    | Pd                | Ta ≤ 75°C  |      |      | 200                  | mW   |

| Storage temperature  | Tstg              |            | -55  |      | +125                 | °C   |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

## Allowable Operating Ranges at voltages relative to $V_{\mbox{\scriptsize SS}}$

| Parameter                | Symbol             | Conditions                            | Ratings             |                 |                     | Unit |

|--------------------------|--------------------|---------------------------------------|---------------------|-----------------|---------------------|------|

|                          |                    |                                       | min                 | typ             | max                 |      |

| Power supply voltage     | V <sub>DD</sub>    | *                                     | 10                  |                 | 18                  | V    |

|                          | V <sub>DD</sub> 1  | *                                     |                     | V <sub>DD</sub> |                     | V    |

|                          | V <sub>cc</sub>    | *                                     | 3.0                 |                 | 5.5                 | V    |

|                          | V <sub>SS</sub> 1  | *                                     |                     | V <sub>SS</sub> |                     | V    |

| High-level input voltage | V <sub>IN</sub> -H | IN1 to IN7 ( $V_{CC}$ = 4.5 to 5.5 V) | 2.4                 |                 | V <sub>cc</sub>     | N    |

|                          |                    | (V <sub>CC</sub> = 3.0 to 4.5 V)      | 0.7 V <sub>CC</sub> |                 | V <sub>cc</sub>     | V    |

| Low-level input voltage  |                    | IN1 to IN7 ( $V_{CC}$ = 4.5 to 5.5 V) | 0                   |                 | 0.8                 |      |

|                          | V <sub>IN</sub> -L | (V <sub>CC</sub> = 3.0 to 4.5 V)      | 0                   |                 | 0.1 V <sub>CC</sub> | V    |

| Operating temperature    | Topr               |                                       | -10                 |                 | +75                 | °C   |

Note: \* Applications must observe the directions in the note on page 5 at power on and at power off.

### **Electrical Characteristics**

### at Ta = $25^{\circ}C \pm 2^{\circ}C$ , $V_{CC} = 5$ V, and $V_{DD} = 16$ V, all voltages are relative to $V_{SS}$ , unless othrewise specified

| Parameter                      | Symbol             | Conditions                                                          |                    | Ratings |                    |      |

|--------------------------------|--------------------|---------------------------------------------------------------------|--------------------|---------|--------------------|------|

|                                | Symbol             | Conditions                                                          | min                | typ     | max                | Unit |

| High-level input current       | l <sub>ih</sub>    | $Vin = V_{CC}$ IN1 to IN7                                           |                    |         | 1                  | μA   |

| Low-evel input current         | l <sub>ii</sub>    | Vin = V <sub>SS</sub> IN1 to IN7                                    | -1                 |         |                    | μA   |

| High-level output voltage      | V <sub>oh</sub>    | lo = 1 mA                                                           | V <sub>DD</sub> -1 |         | V <sub>DD</sub>    | V    |

| Low-level output voltage       | V <sub>ol</sub>    | lo = -1 mA                                                          | V <sub>SS</sub>    |         | V <sub>SS</sub> +1 | V    |

| Output on resistance           | Rout               | $V_{DD} = V_{DD}1 = 10 \text{ V}$ Io = ±1 mA                        |                    | 60      |                    | Ω    |

| Current drain while idling     | I <sub>CCI</sub>   | $V_{DD} = V_{DD}1 = 18 \text{ V}, V_{CC} = 5.5 \text{ V}$           |                    | 0.01    | 10                 | μA   |

|                                | I <sub>DDI</sub> ∗ | IN1 to IN7 = 0 V<br>All outputs open.                               |                    | 0.10    | 10                 | μA   |

| Current drain during operation | I <sub>CCa</sub>   | V <sub>DD</sub> = V <sub>DD</sub> 1 = 15 V, V <sub>CC</sub> = 5.5 V |                    | 16      |                    | μA   |

|                                | I <sub>DDa</sub> * | IN0 to IN6 = 0 V<br>IN7 = 0 to 5.5 V/2 MHz<br>Load 1                |                    | 10      |                    | mA   |

Note: \*  $I_{DD}I$  and  $I_{DD}a$  are the total currents flowing into power supply pins  $V_{DD}$  and  $V_{DD}1$ .

## Pin Assignment

|    |                  |                  | 1    |

|----|------------------|------------------|------|

| 1  | v <sub>DD</sub>  | V <sub>DD1</sub> | 30   |

| 2  | V <sub>CC</sub>  | NC               | 29   |

| 3  | NC               | 0UT1             | 28   |

| 4  | NC               | 0UT2             | 27   |

| 5  | IN1              | 0UT 3            | 26   |

| 6  | 1N2              | OUT4             | 25   |

| 7  | 1N3              | OUT4             | 24   |

| 8  | I N 4            | 0UT5             | 23   |

| 9  | 1N5              | 0UT5             | 22   |

| 10 | 1N6              | 0UT6             | 21   |

| Ξ  | IN7              | OUT6             | 20   |

| 12 | NC               | 0UT7             | 19   |

| 13 | NC               | OUT7             | 18   |

| 14 | V <sub>SS</sub>  | NC               | 17   |

| 15 | V <sub>SS1</sub> | V <sub>SS1</sub> | 16   |

|    |                  | Тор              | view |

Block Diagram

## **Pin Descriptions**

|                   |     | <b>D</b> : <b>N</b> : <b>1</b> | <b>–</b>                                |

|-------------------|-----|--------------------------------|-----------------------------------------|

| Pin Name          | I/O | Pin Number                     | Function                                |

| OUT1              |     | 28                             |                                         |

| OUT2              |     | 27                             |                                         |

| OUT3              |     | 26                             |                                         |

| OUT4              |     | 25                             |                                         |

| OUT4*             |     | 24                             |                                         |

| OUT5              | 0   | 23                             | Level shifter outputs                   |

| OUT5*             |     | 22                             |                                         |

| OUT6              |     | 21                             |                                         |

| OUT6*             |     | 20                             |                                         |

| OUT7              |     | 19                             |                                         |

| OUT7*             |     | 18                             |                                         |

| IN1               |     | 5                              |                                         |

| IN2               |     | 6                              |                                         |

| IN3               |     | 7                              |                                         |

| IN4               | I   | 8                              | Level shifter inputs                    |

| IN5               |     | 9                              |                                         |

| IN6               |     | 10                             |                                         |

| IN7               |     | 11                             |                                         |

| V <sub>DD</sub>   | —   | 1                              | Level shifter high-voltage power supply |

| V <sub>DD</sub> 1 | —   | 30                             | Buffer high-voltage power supply        |

| V <sub>CC</sub>   | _   | 2                              | Level shifter low-voltage power supply  |

| V <sub>SS</sub> 1 | —   | 15, 16                         | Buffer ground                           |

| V <sub>SS</sub>   | —   | 14                             | Level shifter ground                    |

| NC                |     | 3, 4, 12, 13, 17, 29           | Do not connect anything to these pins.  |

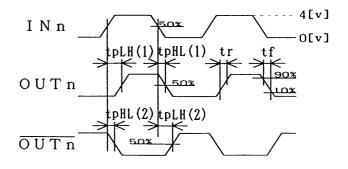

| Parameter         | Symbol  | Conditions |            | Unit |            |      |

|-------------------|---------|------------|------------|------|------------|------|

|                   |         |            | min        | typ  | max        | Unit |

| Propagation delay | tpLH(1) |            |            | 33   | 60         | ns   |

|                   | tpHL(1) |            |            | 35   | 60         | ns   |

|                   | tpLH(2) |            | tpHL(1)-10 | 36   | tpHL(1)+20 | ns   |

|                   | tpHL(2) |            | tpLH(1)-20 | 20   | tpLH(1)+10 | ns   |

| Rising time       | tr      | Load 1     |            | 24   | 50         | ns   |

| Falling time      | tf      | Load 1     |            | 24   | 50         | ns   |

## Switching Characteristics at Ta = 25°C $\pm 2^{\circ}C,$ $V_{CC}$ = 5 V $\pm 10\%,$ $V_{DD}$ = 10 to 18 V

### at Ta = 25°C $\pm 2^{\circ}$ C, V\_{CC} = 3.0 to 4.5 V, V\_{DD} = 10 to 18 V

| Parameter         | Symbol  | Conditions |     | Unit |     |    |

|-------------------|---------|------------|-----|------|-----|----|

|                   |         |            | min | typ  | max |    |

| Propagation delay | tpLH(1) | Load 1     |     |      | 100 | ns |

|                   | tpHL(1) |            |     |      | 120 | ns |

|                   | tpLH(2) |            |     |      | 120 | ns |

|                   | tpHL(2) |            |     |      | 100 | ns |

| Rising time       | tr      | Load 1     |     |      | 50  | ns |

| Falling time      | tf      | Load 1     |     |      | 50  | ns |

Note: The typical values are measured for OUT1 output with  $V_{CC}$  = 5.5 V and  $V_{DD}$  = 15 V.

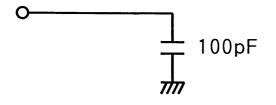

Load 1

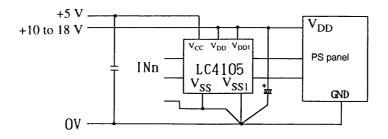

#### **Power Supply Circuits**

Keep the impedance of the  $V_{SS}$  and  $V_{SS}$ 1 lines as low as possible. Connect a large electrolytic capacitor across the  $V_{DD}$ 1 and  $V_{SS}$ 1 pins and close to the IC. Wherever possible, keep the grounds for the power supply circuits and the signal circuits separate and connect the two at a single point.

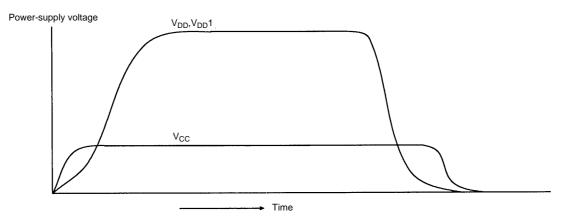

#### **Notes on Power-Supply Voltage Application**

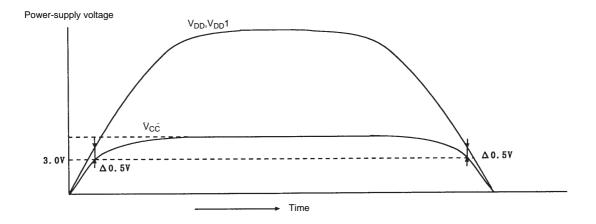

This IC has two power supply systems:  $V_{DD}$  ( $V_{DD}$ 1) and  $V_{CC}$ , and requires that applications observe the notes provided here when applying or removing these voltages. In particular, if the  $V_{DD}$  ( $V_{DD}$ 1) system power-supply voltage becomes higher than the  $V_{CC}$  system voltage while the  $V_{CC}$  system voltage is not yet established (i.e. is less than  $V_{CC}$ min), excessive currents may flow and the IC may be destroyed. To prevent destruction of the IC due to this phenomenon, applications must, basically, follow the sequence described in item 1 below when turning the power supplies on or off.

1. When turning the power on, first apply the  $V_{CC}$  voltage (bring this voltage to a value above  $V_{CC}$ min), and then apply the  $V_{DD}$  voltage. When turning the power off, first drop the  $V_{DD}$  voltage, and, after  $V_{DD}$  is below  $V_{CC}$ min, then drop the  $V_{CC}$  voltage.

However, there are many cases where it is not possible to control the power-supply voltage on/off sequence. This IC is actually capable of supporting the on/off sequence described in item 2 below.

2. If  $V_{DD}$  ( $V_{DD}$ 1) and  $V_{CC}$  are turned on and off at essentially the same time, the difference between  $V_{DD}$  and  $V_{CC}$  (e.g. the distance in the figure marked as  $\Delta 0.5$  V) must be held to be under 0.5 V while  $V_{CC}$  is less than or equal to 3.0 V.

Another point is that a certain amount of time is required to stabilize the  $V_{CC}$  system when  $V_{CC}$  is first applied and the IC is easily destroyed during this period. Inversely, when the power is removed, the  $V_{CC}$  system state is easily retained and as a result the device cannot be destroyed easily. In actual use, one can consider there to be a certain amount of margin for removing the  $V_{DD}$  ( $V_{DD}$ 1) voltage even after  $V_{CC}$  has already been dropped. However, this margin varies with sample-to-sample variations in the IC itself and with the details of the application circuit, and careful analysis and consideration of the actual usage conditions is required to assure that the IC will not be destroyed if the sequences in items 1 or 2 are not observed.

3. Note that when power is turned off and then immediately turned back on again, many circuit designs may fail to meet the conditions for the sequences described in items 1 and 2 above. Be sure to take this into account when designing applications that use this IC.

No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of April, 1998. Specifications and information herein are subject to change without notice.