# 4 1/10 三洋半導体開発ニューズ

**No.** N 6845

D0500

暫定規格

## LC87F52C8A

CMOS LSI - FROM128K バイト,RAM4K バイト内蔵

## 8 ビット1 チップマイクロコンピュータ

#### 概要

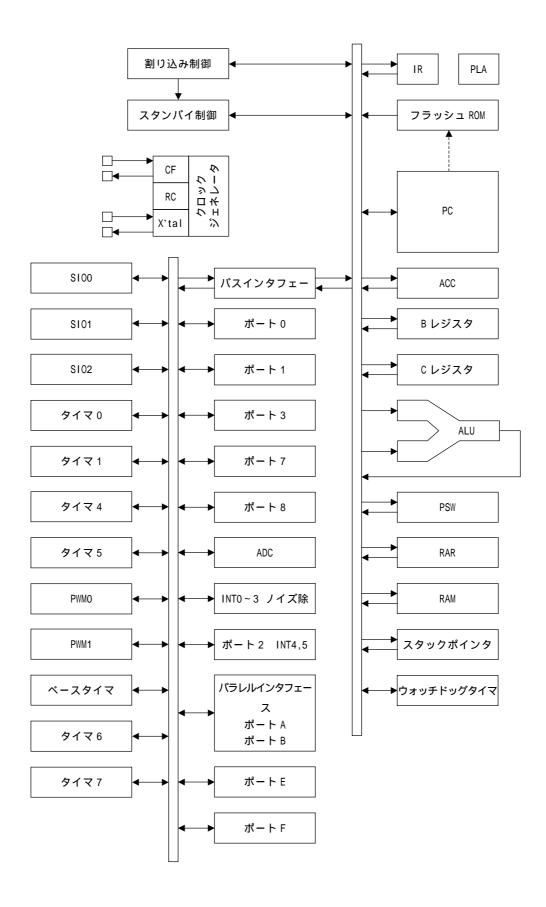

L C 8 7 F 5 2 C 8 A は、最小バスサイクルタイム 1 0 0 n s で動作する C P U 部を中心にして、 1 2 8 K バイトのフラッシュ R O M (オンボード書き換え可能), 4 K バイト R A M , 高機能 1 6 ビットタイマ / カウンタ×2 (8 ビットタイマに分割可), プリスケーラ付き 8 ビットタイマ×4 , 時計用ベースタイマ,自動転送機能付き同期式 S I O × 2 , 非同期 / 同期式 S I O × 1 , 1 2 ビット P W M × 2 , 8 ビット 1 2 チャネル A D コンバータ , 高速 8 ビットパラレルインタフェース , 高速クロックカウンタ , システムクロック分 周機能 , 2 1 要因 1 0 ベクタ割り込み機能等を 1 チップに集積した 8 ビットマイクロコンピュータです。

#### 特長

#### フラッシュROM

- ・5 V単一電源でのオンボード書き込み可能。

- ・128バイト単位でのブロック消去可能。

- ・131071×8ビット(LC87F52C8A)

#### 最小バスサイクルタイム

100ns(10MHz)(注)バスサイクルタイムはROMの読み出し速度を表します。

### 最小命令サイクルタイム

· 3 0 0 n s ( 1 0 M H z )

#### ポート

・ノーマル耐圧入出力ポート

1ビット単位で入出力指定可能2ビット単位で入出力指定可能

4 ビット単位で入出力指定可能

・ノーマル耐圧入力ポート

・ノーマル耐圧出力ポート

・発振専用ポート

・リセット端子

・電源端子

6 1 (P1n, P2n, P3n, P70~P73, P8n, PAn, PBn, PCn, S2Pn)

16 (PEn, PFn)

8 (POn)

2 (XT1, XT2)

2 (PWMO, PWM1)

2 (CF1, CF2)

1 (RES#)

8 (VSS1~4, VDD1~4)

- ■本書記載の製品は、極めて高度の信頼性を要する用途(生命維持装置、航空機のコントロールシステム等、 多大な人的・物的損害を及ぼす恐れのある用途)に対応する仕様にはなっておりません。そのような場合に は、あらかじめ三洋電機販売窓口までご相談下さい。

- ■本書記載の規格値(最大定格、動作条件範囲等)を瞬時たりとも越えて使用し、その結果発生した機器の欠陥について、弊社は責任を負いません。

#### タイマ

・タイマ 0:キャプチャレジスタ付きの 16ビットのタイマ / カウンタ

モード 0 : 8 ビットプログラマブルプリスケーラ付 8 ビットタイマ ( 8 ビットキャプチャレ ジスタ付 ) × 2 チャネル

モード1:8ビットプログラマブルプリスケーラ付8ビットタイマ(8ビットキャプチャレンデスタイン・21/21 カナンタイス (8ビットオンタイス)

ジスタ付)+8ビットカウンタ(8ビットキャプチャレジスタ付)

モード2:8ビットプログラマブルプリスケーラ付16ビットタイマ(16ビットキャプチャレジスタ付)

モード3:16ビットカウンタ(16ビットキャプチャレジスタ付)

・タイマ1: PWM / トグル出力可能な16ビットのタイマ/カウンタ

モード0:8ビットタイマ(トグル出力付)+8ビットタイマ/カウンタ(トグル出力付)

モード1:8ビットPWM×2チャネル

モード2:16ビットタイマ/カウンタ(トグル出力付)(下位8ビットからもトグル出力 可能)

モード3:16ビットタイマ(トグル出力付)(下位8ビットはPWMとして使用可能)

- ・タイマ4:6ビットプリスケーラ付8ビットタイマ

- ・タイマ5:6ビットプリスケーラ付8ビットタイマ

- ・タイマ6:6ビットプリスケーラ付8ビットタイマ

- ・タイマ7:6ビットプリスケーラ付8ビットタイマ

- ・ベースタイマ

クロックは、サブクロック(32.768kHz水晶発振),システムクロック,タイマ0のプリスケーラ出力から選択できる。

5種類の時間での割り込み発生が可能。

#### 高速クロックカウンタ

最高  $2\,0\,M\,H\,z$  のクロックをカウントできる。(メインクロック  $1\,0\,M\,H\,z$  使用時) リアルタイム出力

#### SIO

・SIO0:8ビット同期式シリアルインタフェース

LSB先頭/MSB先頭切り替え可能

8ビットボーレートジェネレータ内蔵(最大転送クロック周期4/3Tcyc)

連続自動データ通信(1~256ビット)

・SIO1:8ビット非同期/同期式シリアルインタフェース

モード0:同期式8ビットシリアルIO(2線式または3線式,転送クロック2~512Tcyc)

モード1:非同期シリアルIO(半二重,データ8ビット,ストップビット1,ボーレート8~204 8

Tcyc)

モード2:バスモード1(スタートビット,データ8ビット,転送クロック2~512Tcyc)

モード3:バスモード2(スタート検出,データ8ビット,ストップ検出)

・SIO2:8ビット同期式シリアルインタフェース

LSB先頭

8ビットボーレートジェネレータ内蔵(最大転送クロック周期4/3Tcyc)

連続自動データ通信(1~32バイト)

A D コンバータ: 8 ビット× 1 2 チャネル

PWM:周期可変12ビットPWM×2チャネル

### パラレルインタフェース

- ・RS, RD#, WR#, CS0#~CS2#出力(極性切替可能)

- 1 T c y c での読み出し/書き込み可能

リモコン受信回路(P73/INT3/T0IN端子と共用)

・ノイズ除去機能(ノイズ除去フィルタの時定数選択1/32/128Tcyc)

### ウォッチドッグタイマ

- ・RC外付けによるウォッチドッグタイマ

- ・割り込み、リセットの選択可能

#### 割り込み

・21要因10ベクタ

割り込みは低レベル(L),高レベル(H),最高レベル(X)の3レベルの多重割り込み制御。割り込み処理中に、同一レベルまたは下位のレベルの割り込み要求が入っても受け付けられません。2つ以上のベクタアドレスへの割り込み要求が同時に発生した場合、レベルの高いものが優先されます。また、同一レベルでは飛び先ベクタアドレスの小さい方の割り込みが優先されます。

| No. | ベクタ    | 選択レベル | 割り込み要因             |

|-----|--------|-------|--------------------|

| 1   | 00003H | ΧまたはL | INTO               |

| 2   | 0000BH | ΧまたはL | INT1               |

| 3   | 00013H | ΗまたはL | INT2/T0L/INT4      |

| 4   | 0001BH | ΗまたはL | INT3/INT5/ベースタイマ   |

| 5   | 00023H | ΗまたはL | ТОН                |

| 6   | 0002BH | ΗまたはL | T1L/T1H            |

| 7   | 00033H | ΗまたはL | \$100              |

| 8   | 0003BH | ΗまたはL | \$101/\$102        |

| 9   | 00043H | ΗまたはL | ADC/T6/T7          |

| 10  | 0004BH | ΗまたはL | ポート 0/T4/T5/PWM0,1 |

- 優先レベル X > H > L

- ・同一レベルではベクタアドレスの小さいものが優先

サブルーチンスタックレベル:最大512レベル(スタックはRAMの中に設定)

#### 高速乗除算命令

・16ビット×8ビット (実行時間: 5Tcyc)

・24ビット×16ビット (実行時間: 12Tcyc)

・16ビット÷8ビット (実行時間: 8Tcyc)

・24ビット÷16ビット (実行時間: 12Tcyc)

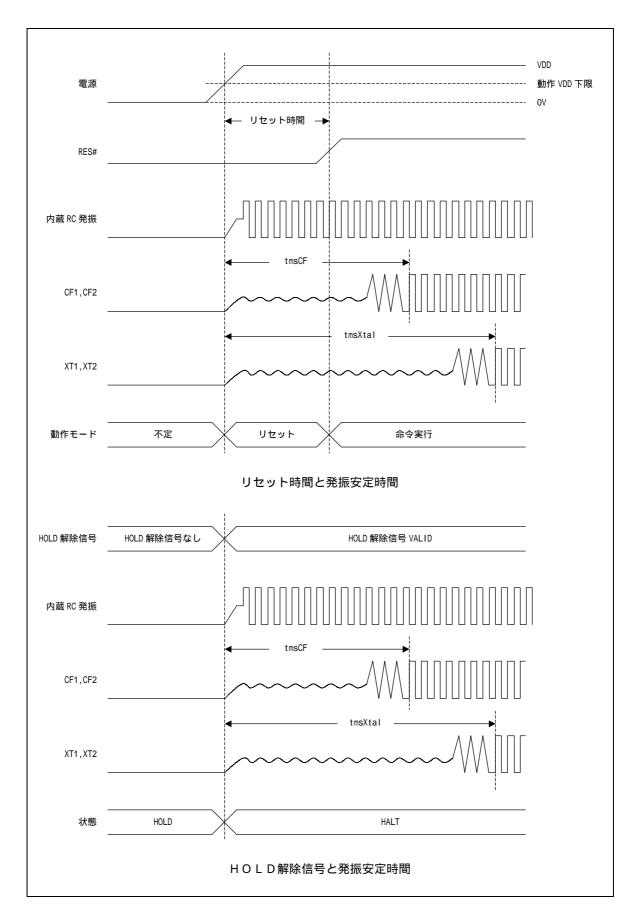

#### 発振回路

・RC発振回路(内蔵) :システムクロック用

・CF発振回路: システムクロック用, Rf内蔵・水晶発振回路: 低速システムクロック用

### システムクロック分周機能

· 低消費電流動作可能

・ 最小命令サイクルで 300ns , 600ns ,  $1.2\mu s$  ,  $2.4\mu s$  ,  $4.8\mu$  s ,  $9.6\mu s$  ,

19.2 μs,38.4 μs,76.8 μsの選択が可能(メインクロック10 M H z 使用時)

#### スタンバイ機能

・HALTモード:命令実行停止,周辺回路動作継続 発振の停止は自動的には行いません。 システムリセットまたは割り込みの発生により解除。

・HOLDモード: 命令実行停止,周辺回路動作停止

CF発振, RC発振, 水晶発振のいずれも自動的に停止します。

- HOLDモードを解除するには次の3つの方法があります。

- (1)リセット端子に「L」レベルを入力する。

- (2) INT 0 , INT 1 , INT 2 , INT 4 , INT 5 の少なくとも 1 つの端子に指定されたレベルを入力する。

- (3)ポート0で割り込み要因が成立する。

- ・X'tal HOLDモード:命令実行停止,ベースタイマ以外の周辺回路動作停止

- CF発振,RC発振は自動的に停止します。

水晶発振は突入時の状態を維持します。

- X'tal HOLDモードを解除するには次の4つの方法があります。

- (1)リセット端子に「L」レベルを入力する。

- (2) INT 0 , INT 1 , INT 2 , INT 4 , INT 5 の少なくとも 1 つの端子に指定されたレベルを入力する。

- (3)ポート0で割り込み要因が成立する。

- (4)ベースタイマ回路で割り込み要因が成立する。

#### 出荷形態

- Q F P 1 0 0 E

- SQFP100

### 開発ツール

・エバチップ : LC876095

・エミュレータ : EVA62S+ECB876500/6600+SUB875200+POD100QFP

or POD100SQFP2

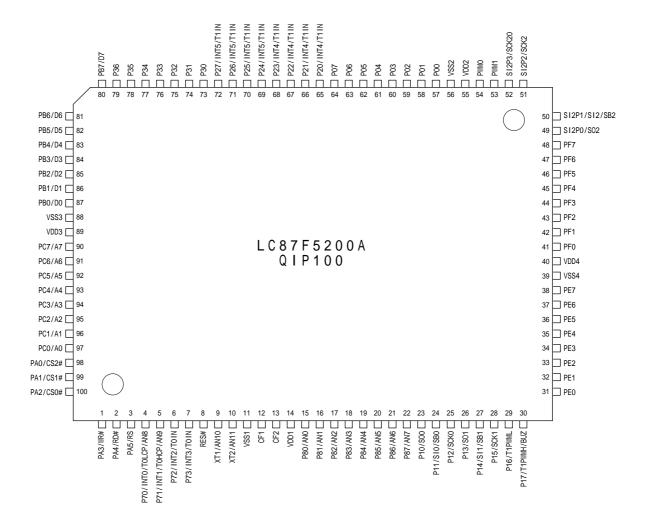

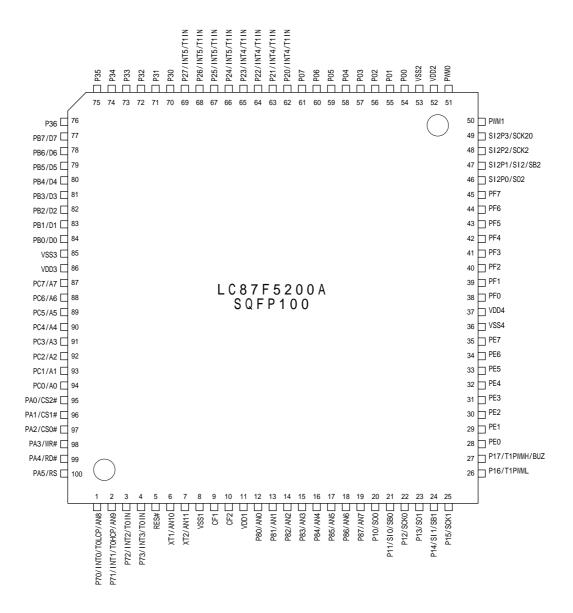

#### ピン配置図

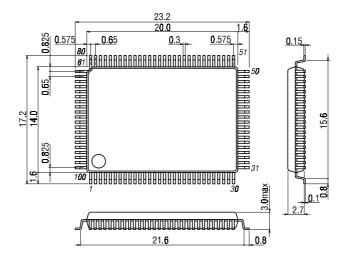

### 外形図 3151 (unit: mm)

SANYO : QIP100E

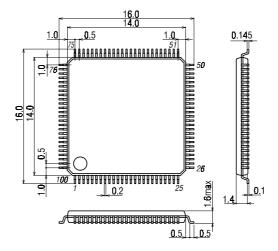

### 外形図 3181B (unit:mm)

SANYO : SQFP100

| QIP | NAME                    | SQFP |

|-----|-------------------------|------|

| 1   | PA3/WR#                 | 98   |

| 2   | PA4/RD#                 | 99   |

| 3   | PA5/RS                  | 100  |

| 4   | P70/INT0/T0LCP/AN8      | 1    |

| 5   | P71/INT1/T0HCP/AN9      | 2    |

| 6   | P72/INT2/T0IN           | 3    |

| 7   | P73/INT3/T0IN           | 4    |

| 8   | RES#                    | 5    |

| 9   | XT1/AN10                | 6    |

| 10  | XT2/AN11                | 7    |

| 11  | VSS1                    | 8    |

| 12  | CF1                     | 9    |

| 13  | CF2                     | 10   |

| 14  | VDD1                    | 11   |

| 15  | P80/AN0                 | 12   |

| 16  | P81/AN1                 | 13   |

| 17  | P82/AN2                 | 14   |

| 18  | P83/AN3                 | 15   |

| 19  | P84/AN4                 | 16   |

| 20  | P85/AN5                 | 17   |

| 21  | P86/AN6                 | 18   |

| 22  | P87/AN7                 | 19   |

| 23  | P10/S00                 | 20   |

| 24  | P11/S10/SB0             | 21   |

| 25  | P12/SCK0                | 22   |

| 26  | P13/S01                 | 23   |

|     |                         |      |

| 27  | P14/SI1/SB1<br>P15/SCK1 | 24   |

| 28  | P16/T1PWML              | 25   |

| 29  | P17/T1PWMH/BUZ          | 26   |

| 30  |                         | 27   |

| 31  | PE0                     | 28   |

| 32  | PE1                     | 29   |

| 33  | PE2                     | 30   |

| 34  | PE3                     | 31   |

| 35  | PE4                     | 32   |

| 36  | PE5                     | 33   |

| 37  | PE6                     | 34   |

| 38  | PE7                     | 35   |

| 39  | VSS4                    | 36   |

| 40  | VDD4                    | 37   |

| 41  | PF0                     | 38   |

| 42  | PF1                     | 39   |

| 43  | PF2                     | 40   |

| 44  | PF3                     | 41   |

| 45  | PF4                     | 42   |

| 46  | PF5                     | 43   |

| 47  | PF6                     | 44   |

| 48  | PF7                     | 45   |

| 49  | S12P0/S02               | 46   |

| 50  | SI2P1/SI2/SB2           | 47   |

| QIP | NAME          | SQFP |

|-----|---------------|------|

| 51  | S12P2/SCK2    | 48   |

| 52  | S12P3/SCK20   | 49   |

| 53  | PWM1          | 50   |

| 54  | PWM0          | 51   |

| 55  | VDD2          | 52   |

| 56  | VSS2          | 53   |

| 57  | P00           | 54   |

| 58  | P01           | 55   |

| 59  | P02           | 56   |

| 60  | P03           | 57   |

| 61  | P04           | 58   |

| 62  | P05           | 59   |

| 63  | P06           | 60   |

| 64  | P07           | 61   |

| 65  | P20/INT4/T1IN | 62   |

| 66  | P21/INT4/T1IN | 63   |

| 67  | P22/INT4/T1IN | 64   |

| 68  | P23/INT4/T1IN | 65   |

| 69  | P24/INT5/T1IN | 66   |

| 70  | P25/INT5/T1IN | 67   |

| 71  | P26/INT5/T1IN | 68   |

| 72  | P27/INT5/T1IN | 69   |

| 73  | P30           | 70   |

| 74  | P31           | 71   |

| 75  | P32           | 72   |

| 76  | P33           | 73   |

| 77  | P34           | 74   |

| 78  | P35           | 75   |

| 79  | P36           | 76   |

| 80  | PB7/D7        | 77   |

| 81  | PB6/D6        | 78   |

| 82  | PB5/D5        |      |

| 83  | PB4/D4        | 79   |

| 84  |               | 80   |

|     | PB3/D3        | 81   |

| 85  | PB2/D2        | 82   |

| 86  | PB1/D1        | 83   |

| 87  | PBO/DO        | 84   |

| 88  | VSS3          | 85   |

| 89  | VDD3          | 86   |

| 90  | PC7/A7        | 87   |

| 91  | PC6/A6        | 88   |

| 92  | PC5/A5        | 89   |

| 93  | PC4/A4        | 90   |

| 94  | PC3/A3        | 91   |

| 95  | PC2/A2        | 92   |

| 96  | PC1/A1        | 93   |

| 97  | PCO/A0        | 94   |

| 98  | PA0/CS2#      | 95   |

| 99  | PA1/CS1#      | 96   |

| 100 | PA2/CS0#      | 97   |

### システムブロック図

### 端子機能表

| 端子名         | 1/0 | 機能説明                                                            | オプション |

|-------------|-----|-----------------------------------------------------------------|-------|

| VSS1, VSS2, | -   | 電源の - 端子                                                        | なし    |

| VSS3, VSS4  |     |                                                                 |       |

| VDD1, VDD2, | -   | 電源の+端子                                                          | なし    |

| VDD3, VDD4  |     |                                                                 |       |

| ポート 0       | 1/0 | ・8 ビットの入出力ポート                                                   | あり    |

| P00 ~ P07   |     | ・4 ビット単位の入出力指定可能                                                |       |

|             |     | ・4 ビット単位のプルアップ抵抗 ON / OFF 可能<br>  ・HOLD 解除入力                    |       |

|             |     | ・ポート0割り込み入力                                                     |       |

| ポート1        | 1/0 | ・8 ビットの入出力ポート                                                   | あり    |

| P10 ~ P17   | 170 | ・1 ビット単位の入出力指定可能                                                | 05.5  |

| 110 117     |     | ・1 ビット単位のプルアップ抵抗 ON / OFF 可能                                    |       |

|             |     | ・端子機能                                                           |       |

|             |     | P10 : SI00 データ出力                                                |       |

|             |     | P11 : SI00 データ入力 / バス入出力                                        |       |

|             |     | P12 : SI00 クロック入出力                                              |       |

|             |     | P13 : SIO1 データ出力                                                |       |

|             |     | P14 : SIO1 データ入力 / バス入出力                                        |       |

|             |     | P15 : SIO1 クロック入出力<br>P16 : タイマ 1PWML 出力                        |       |

|             |     | P10 : ダイマ 1PWMH 出力 / ブザー出力                                      |       |

| ポート2        | 1/0 | ・8 ビットの入出力ポート                                                   | あり    |

| P20 ~ P27   | .,, | ・1 ビット単位の入出力指定可能                                                |       |

| 120 127     |     | ・1 ビット単位のプルアップ抵抗 ON / OFF 可能                                    |       |

|             |     | ・端子機能                                                           |       |

|             |     | P20~P23 : INT4 入力 / HOLD 解除入力 / タイマ 1 イベント入力                    |       |

|             |     | / タイマ OL キャプチャ入力 / タイマ OH キャプチャ入力                               |       |

|             |     | P24~P27 : INT5 入力 / HOLD 解除入力 / タイマ 1 イベント入力                    |       |

|             |     | / タイマ OL キャプチャ入力 / タイマ OH キャプチャ入力<br>インタラプト受付形式                 |       |

|             |     | イフタフフト支刊形式<br>  立ち上がり 立ち下がり 立ち上がり   Hレベル   Lレベル                 |       |

|             |     |                                                                 |       |

|             |     | INT4 × ×                                                        |       |

|             |     | INT5 × ×                                                        |       |

|             |     |                                                                 |       |

| ポート3        | 1/0 | ・7 ビットの入出力ポート<br>・1 ビット単位の入出力指定可能                               | あり    |

| P30 ~ P36   |     | ・1 ビット単位の八山刀指足可能<br>  ・1 ビット単位のプルアップ抵抗 ON / OFF 可能              |       |

| ポート 7       | 1/0 | ・4 ビットの入出力ポート                                                   | なし    |

| P70 ~ P73   | 170 | ・1 ビット単位の入出力指定可能                                                | , & O |

| 170 173     |     | ・1 ビット単位のプルアップ抵抗 ON / OFF 可能                                    |       |

|             |     | ・端子機能                                                           |       |

|             |     | P70 : INTO 入力 / HOLD 解除入力 / タイマ OL キャプチャ入力                      |       |

|             |     | / ウォッチドッグタイマ用出力                                                 |       |

|             |     | P71 : INT1 入力 / HOLD 解除入力 / タイマ OH キャプチャ入力                      |       |

|             |     | P72 : INT2 入力 / HOLD 解除入力 / タイマ 0 イベント入力                        |       |

|             |     | / タイマ OL キャプチャ入力<br>P73 : INT3 入力 ( ノイズフィルタ付入力 ) / タイマ 0 イベント入力 |       |

|             |     | P/3 : INI3 人刀(フィスフィルタ刊 人刀) / タイマ U イベント人刀<br>  / タイマ OH キャプチャ入力 |       |

|             |     | インタラプト受付形式                                                      |       |

|             |     | 立ち上がり   立ち下がり   立ち上がり   Hレベル   L レベル                            |       |

|             |     | 立ち下がり                                                           |       |

|             |     | INTO ×                                                          |       |

|             |     | INT1 X X X                                                      |       |

|             |     | IN12                                                            |       |

|             |     | ・AD 変換入力ポート:AN8(P70), AN9(P71)                                  |       |

| 1           |     | (たる)                                                            |       |

(次ページへ)

| 端子名          | 1/0  | 機能説明                                    | オプション |

|--------------|------|-----------------------------------------|-------|

| ポート8         | 1/0  | ・8 ビットの入出力ポート                           | なし    |

| P80 ~ P87    |      | ・1 ビット単位の入出力指定可能                        |       |

|              |      | ・兼用機能                                   |       |

|              |      | P80~P87 : AD 変換入力ポート                    |       |

| ポートA         | 1/0  | ・6 ビットの入出力ポート                           | あり    |

| PAO ~ PA5    |      | ・1 ビット単位の入出力指定可能                        |       |

|              |      | ・1 ビット単位のプルアップ抵抗 ON / OFF 可能            |       |

|              |      | ・兼用機能                                   |       |

|              |      | PAO : パラレルインタフェースの CS2#出力               |       |

|              |      | PA1 : パラレルインタフェースの CS1#出力               |       |

|              |      | PA2 : パラレルインタフェースの CSO#出力               |       |

|              |      | PA3 : パラレルインタフェースの WR#出力                |       |

|              |      | PA4 : パラレルインタフェースの RD#出力                |       |

|              |      | PA5 : パラレルインタフェースの RS 出力                |       |

| ポートB         | 1/0  | ・8 ビットの入出力ポート                           | あり    |

| PB0 ~ PB7    |      | ・1 ビット単位の入出力指定可能                        |       |

|              |      | ・1 ビット単位のプルアップ抵抗 ON / OFF 可能            |       |

|              |      | ・兼用機能                                   |       |

| <del>1</del> | 1.70 | PB0~PB7 : パラレルインタフェースのデータ入出力 / アドレス出力   | ± 12  |

| ポートC         | 1/0  | ・8 ビットの入出力ポート                           | あり    |

| PC0 ~ PC7    |      | ・1 ビット単位の入出力指定可能                        |       |

|              |      | ・1 ビット単位のプルアップ抵抗 ON / OFF 可能<br>  ・兼用機能 |       |

|              |      | ・                                       |       |

| ポートE         | 1/0  | - 8 ビットの入出力ポート                          | なし    |

|              | 170  | ・0 こットの六山刀が一ト<br>  ・2 ビット単位の入出力指定可能     | 40    |

| PE0 ~ PE7    |      | ・1 ビット単位のプルアップ抵抗 ON / OFF 可能            |       |

| ポートF         | 1/0  | ・8 ビットの入出力ポート                           | なし    |

| PF0 ~ PF7    | 1,0  | ・2 ビット単位の入出力指定可能                        | , & O |

| FIOSFIT      |      | ・1 ビット単位のプルアップ抵抗 ON / OFF 可能            |       |

| S102 ポート     | 1/0  | ・4 ビットの入出力ポート                           | なし    |

| S12P0        |      | ・1 ビット単位の入出力指定可能                        |       |

| ~ S12P3      |      | ・兼用機能                                   |       |

| 0.2.0        |      | SI2PO : SI02 データ出力                      |       |

|              |      | SI2P1 : SI02 データ入力 / バス入出力              |       |

|              |      | SI2P2 : SI02 クロック入出力                    |       |

|              |      | SI2P3 : SI02 クロック出力                     |       |

| PWMO         | 0    | PWMO 出力ポート                              | なし    |

| PWM1         | 0    | PWM1 出力ポート                              | なし    |

| RES          | I    | リセット端子                                  | なし    |

| XT1          | I    | ・32.768kHz 水晶発振子用入力端子                   | なし    |

|              |      | ・兼用機能                                   |       |

|              |      | AN10 : AD 変換入力ポート                       |       |

|              |      | 汎用入力ポート                                 |       |

|              |      | 使用しない場合は VDD1 に接続してください。                |       |

| XT2          | 1/0  | ・32.768kHz 水晶発振子用出力端子                   | なし    |

|              |      | ・兼用機能                                   |       |

|              |      | AN11 : AD 変換入力ポート                       |       |

|              |      | 汎用入力ポート                                 |       |

|              |      | 使用しない場合は発振仕様にして、オープンにしてください。            | 1     |

| CF1          | I    | セラミック発振子用入力端子                           | なし    |

| CF2          | 0    | セラミック発振子用出力端子                           | なし    |

#### ポート出力形態

ポート出力形態とプルアップ抵抗の有無を以下に示します。 なお、入力ポートでのデータの読み込みは、ポートが出力モード時でも可能です。

| ポート名        | オプション<br>切替単位 | オプション<br>種類 | 出力形式               | プルアップ抵抗      |

|-------------|---------------|-------------|--------------------|--------------|

| P00 ~ P07   | 1 ビット単位       | 1           | CMOS               | プログラマブル (注1) |

|             |               | 2           | Nch-オープンドレイン       | なし           |

| P10 ~ P17   | 1 ビット単位       | 1           | CMOS               | プログラマブル      |

| P20 ~ P27   |               | 2           | Nch-オープンドレイン       | プログラマブル      |

| P30 ~ P36   |               |             |                    |              |

| PAO ~ PA5   | 1 ビット単位       | 1           | CMOS               | プログラマブル      |

| PB0~PB7(注)  |               | 2           | Nch-オープンドレイン       | プログラマブル      |

| PC0 ~ PC7   |               |             |                    |              |

| PE0 ~ PE7   | -             | なし          | CMOS               | プログラマブル      |

| PF0~PF7(注)  |               |             |                    |              |

| P70         | •             | なし          | Nch-オープンドレイン       | プログラマブル      |

| P71 ~ P73   | •             | なし          | CMOS               | プログラマブル      |

| P80 ~ P87   | -             | なし          | Nch-オープンドレイン       | なし           |

| S12P0,S12P2 | -             | なし          | CMOS               | なし           |

| SI2P3       |               |             |                    |              |

| PWMO, PWM1  |               |             |                    |              |

| SI2P1       | -             | なし          | CMOS(通常ポート選択時)     | なし           |

|             |               |             | Nch-オープンドレイン       |              |

|             |               |             | (\$102 データ選択時)     |              |

| XT1         | -             | なし          | 入力専用               | なし           |

| XT2         | -             | なし          | 32.768kHz 水晶発振子用出力 | なし           |

- 注 1 ポート 0 のプログラマブルプルアップ抵抗は、 4 ビット単位 ( P 0 0 ~ 0 3 , P 0 4 ~ 0 7 ) の制御になります。

- (注)パラレルインタフェースモードの時、 $PB0 \sim PB7$ はオプションに関係なく、出力形式がCMOSとなります。

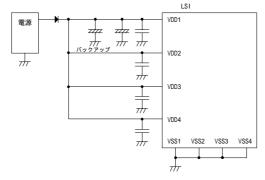

- 1 VDD1端子に入るノイズを小さくし、バックアップ時間を長くするために、次のように接続してください。 VSS1端子とVSS2端子とVSS3端子は必ず電気的にショートしてください。 (例1)HOLDモードでバックアップ時、ポート出力の'H'レベルはバックアップ用コンデンサより供給されます。 \_\_\_\_\_\_

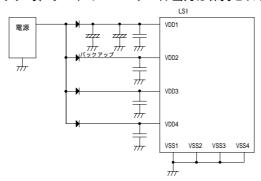

(例2) HOLDモードバックアップ時、ポートの'H'レベル出力は保持されず不定となります。

### 1. 絶対最大定格 / Ta=25 , VSS1=VSS2=VSS3=VSS4=0V

|              | 項目                                        | 記号      | 適用端子・備考                                                           | 条件                      |        | 規格   |      |         |      |

|--------------|-------------------------------------------|---------|-------------------------------------------------------------------|-------------------------|--------|------|------|---------|------|

|              | 切口 ロー・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 此与      | 週份期 1 1 開写                                                        | ѫҥ                      | VDD[V] | min. | typ. | max.    | unit |

| 最            | 大電源電圧                                     | VDDMAX  | VDD1, VDD2,<br>VDD3, VDD4                                         | VDD1=VDD2=VDD3<br>=VDD4 |        | -0.3 | ~    | +6.5    | V    |

| 入.           | 力電圧                                       | VI(1)   | XT1,XT2,CF1                                                       |                         |        | -0.3 | ~    | VDD+0.3 |      |

| 出            | 力電圧                                       | V0(1)   | PWMO, PWM1                                                        |                         |        | -0.3 | ~    | VDD+0.3 |      |

| λ            | 出力電圧                                      | VIO(1)  | ポート0,1,2<br>ポート3,7,8<br>ポートA,B,C,E,F<br>SI2P0~SI2P3<br>PWM0,PWM1  |                         |        | -0.3 | ~    | VDD+0.3 |      |

| 高レベル出力電流     | ピーク出力電流                                   | IOPH(1) | #°-+0,1,2,3<br>#°-+A,B,C,E,F<br>SI2P0~SI2P3<br>PWM0,PWM1          | CMOS 出力選択<br>適用 1 端子当り  |        | -10  |      |         | mA   |

| カ            | A ±1.11.1                                 | 10PH(2) | P71 ~ P73                                                         | 適用1端子当り                 |        | -5   |      |         |      |

| 電流           | 合計出力                                      | IOAH(1) | P71 ~ P73                                                         | 適用全端子合計                 |        | -5   | -    |         |      |

| <i>71</i> 1L | 電流                                        | 10AH(2) | ポート1<br>PWMO,PWM1<br>ポート3<br>SI2PO~SI2P3                          | 適用全端子合計                 |        | -30  |      |         |      |

|              |                                           | IOAH(3) | ポ-ト0,2                                                            | 適用全端子合計                 |        | -20  |      |         |      |

|              |                                           | IOAH(4) | ポ−トB                                                              | 適用全端子合計                 |        | -20  |      |         |      |

|              |                                           | IOAH(5) | ホ°−トA,C                                                           | 適用全端子合計                 |        | -20  |      |         |      |

|              |                                           | IOAH(6) | π° −トΕ                                                            | 適用全端子合計                 |        | -20  |      |         |      |

|              |                                           | IOAH(7) | ポ−ト F                                                             | 適用全端子合計                 |        | -20  |      |         |      |

| 低レベル出力電流     | ピーク出力電流                                   | IOPL(1) | P02~P07<br>ホ°-ト1,2,3<br>ホ°-トA,B,C,E,F<br>S12P0~S12P3<br>PWM0,PWM1 | 適用1端子当り                 |        |      |      | 20      |      |

| 電            |                                           | IOPL(2) | P00, P01                                                          | 適用1端子当り                 |        |      |      | 30      |      |

| 流            |                                           | IOPL(3) | ポ−ト 7,8                                                           | 適用1端子当り                 |        |      |      | 5       |      |

|              | 合計出力                                      | IOAL(1) | <b>ポ−</b> ト 7                                                     | 適用全端子合計                 |        |      |      | 15      |      |

|              | 電流                                        | IOAL(2) | <b>ポ−ト</b> 8                                                      | 適用全端子合計                 |        |      |      | 15      |      |

|              |                                           | 10AL(3) | #°-1-1<br>PWMO,PWM1<br>#°-1-3<br>SI2P0~SI2P3                      | 適用全端子合計                 |        |      |      | 50      |      |

|              |                                           | IOAL(4) | ポート0,2                                                            | 適用全端子合計                 |        |      |      | 70      |      |

|              |                                           | IOAL(5) | ホ° −ト B                                                           | 適用全端子合計                 |        |      |      | 40      |      |

|              |                                           | IOAL(6) | ホ°−トA,C                                                           | 適用全端子合計                 |        |      |      | 40      |      |

|              |                                           | IOAL(7) | ホ°−トΕ                                                             | 適用全端子合計                 |        |      |      | 40      |      |

|              |                                           | IOAL(8) | ホ°−トF                                                             | 適用全端子合計                 |        |      |      | 40      | _    |

| 許            | 容消費電力                                     | Pdmax   | QIP100E<br>SQFP100                                                | Ta=-20 ~ +70            |        |      |      | 350     | mW   |

| 動            | 作周囲温度                                     | Topg    |                                                                   |                         |        | -20  | ~    | 70      |      |

| 保            | 存周囲温度                                     | Tstg    |                                                                   |                         |        | -55  | ~    | 125     |      |

### 2. 許容動作条件 / Ta=-20~+70 , VSS1=VSS2=VSS3=VSS4=0V

| 項目                                            | 記号        | 適用端子・備考                        | 条件                                     |           | 規格             |      |         |      |

|-----------------------------------------------|-----------|--------------------------------|----------------------------------------|-----------|----------------|------|---------|------|

|                                               | 記写        | 週用姉丁・個名                        | <b>新</b> 什                             | VDD[V]    | min.           | typ. | max.    | unit |

| 動作電源電圧                                        | VDD(1)    | VDD1=VDD2=VDD3                 | 0.294μs tCYC 200μs                     |           | 4.5            |      | 5.5     | V    |

|                                               |           | =VDD4                          | 0.588μs tCYC 200μs                     |           | 2.5            |      | 5.5     |      |

|                                               |           |                                | FROM オンボート書き込                          |           |                |      |         |      |

| メモリ保持                                         | VHD       | VDD1=VDD2=VDD3                 | みは除く<br>HOLD モード時                      |           | 2.0            |      | 5.5     |      |

| スモリ保持<br>  電源電圧                               | עחט       | =VDD4                          | RAM,レジスタ保持                             |           | 2.0            |      | 5.5     |      |

| 高レベル                                          | VIH(1)    | ホ°-ト1,2                        | 10 m, 2 2 7 7 pkg g                    | 2.5~5.5   | 0.3VDD         |      | VDD     |      |

| 入力電圧                                          | , ,       | S12P0~3                        |                                        |           | +0.7           |      |         |      |

|                                               |           | P71 ~ P73                      |                                        |           |                |      |         |      |

|                                               |           | P70 のポート入力                     |                                        |           |                |      |         |      |

|                                               |           | /割り込み側                         |                                        |           |                |      |         |      |

|                                               | VIH(2)    | π°-ト0,8,3                      |                                        | 2.5~5.5   | 0.3VDD<br>+0.7 |      | VDD     |      |

|                                               | VIH(3)    |                                |                                        | 2.5~5.5   | 0.9VDD         |      | VDD     |      |

|                                               | VIII(3)   | 」が - ド/ひ ひり<br>  ウォッチト゛ック゛タイマ側 |                                        | 2.5 - 5.5 | 0.500          |      | ۷۵۵     |      |

|                                               | VIH(4)    | XT1,XT2,CF1,RES#               |                                        | 2.5~5.5   | 0.75VDD        |      | VDD     |      |

|                                               | (.)       | ,,,                            |                                        |           |                |      |         |      |

| 低レベル                                          | VIL(1)    | ポ−ト 1,2                        |                                        | 2.5~5.5   | VSS            |      | 0.1VDD  |      |

| 入力電圧                                          |           | S12P0 ~ 3                      |                                        |           |                |      | +0.4    |      |

|                                               |           | P71 ~ P73                      |                                        |           |                |      |         |      |

|                                               |           | P70 のポート入力                     |                                        |           |                |      |         |      |

|                                               | VIL(2)    | /割り込み側<br>ポート0.8.3             |                                        | 2.5~5.5   | VSS            |      | 0.15VDD |      |

|                                               | VIL(Z)    | ホートロ,8,3<br>  ポートA,B,C,E,F     |                                        | 2.5~5.5   | VSS            |      | +0.4    |      |

|                                               | VIL(5)    | ポート 70 の                       |                                        | 2.5~5.5   | VSS            |      | 0.8VDD  |      |

|                                               | ( )       | ウォッチト゛ック゛タイマ側                  |                                        |           |                |      | -1.0    |      |

|                                               | VIL(6)    | XT1,XT2,CF1,RES#               |                                        | 2.5~5.5   | VSS            |      | 0.25VDD |      |

|                                               |           |                                |                                        |           |                |      |         |      |

| 命令サイクル                                        | tCYC      |                                |                                        | 4.5~5.5   | 0.294          |      | 200     | μS   |

| タイム                                           |           |                                | FROM オンボート書き込                          | 2.5~5.5   | 0.588          |      | 200     |      |

| 51 \$17 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | FEVOE (4) | 054                            | みは除く                                   | 4.5.5.5   | 0.4            |      | 40      | MII  |

| 外部システム<br>クロック周波数                             | FEXCF(1)  | CF1                            | ・CF2 端子オープン<br>・システムクロック               | 4.5~5.5   | 0.1            |      | 10      | MHz  |

| プロップ同級奴                                       |           |                                | 分周 1/1                                 |           |                |      |         |      |

|                                               |           |                                | ・外部システムクロック                            |           |                |      |         |      |

|                                               |           |                                | の DUTY50 ± 5%                          |           |                |      |         |      |

|                                               |           |                                | ・CF2 端子オープン                            | 2.5~5.5   | 0.1            |      | 5       |      |

|                                               |           |                                | ・システムクロック                              |           |                |      |         |      |

|                                               |           |                                | 分周 1/1                                 |           |                |      |         |      |

|                                               |           |                                | ・外部システムクロック                            |           |                |      |         |      |

|                                               |           |                                | の DUTY50 ± 5%<br>・CF2 端子オープン           | 4.5~5.5   | 0.2            |      | 20.4    |      |

|                                               |           |                                | ・OF2 姉 <del>」</del> オーフフ<br> ・システムクロック | 7.0 - 0.0 | 0.2            |      | 20.4    |      |

|                                               |           |                                | 分周 1/2                                 |           |                |      |         |      |

|                                               |           |                                | ・CF2 端子オープン                            | 2.5~5.5   | 0.1            |      | 10      |      |

|                                               |           |                                | ・システムクロック                              |           |                |      |         |      |

|                                               |           |                                | 分周 1/2                                 |           |                |      |         |      |

<sup>(</sup>注1)発振定数は表1,2参照のこと。

(注2) フラッシュROMへのオンボード書き込みは、VDD 4.5 Vとすること。

3. 電気的特性 / Ta=-20~+70 , VSS1=VSS2=VSS3=VSS4=0V

| 項目       | 記号     | 適用端子・備考                                                                     | 条件                                                          |         | 規格      |        |      |      |

|----------|--------|-----------------------------------------------------------------------------|-------------------------------------------------------------|---------|---------|--------|------|------|

|          |        |                                                                             |                                                             | VDD[V]  | min.    | typ.   | max. | unit |

| 高レベル入力電流 | IIH(1) | ポートの、1、2<br>ポート3、7、8<br>ポートA、B、C<br>SI2PO~SI2P3<br>RES#<br>PWMO、PWM1        | 出力ディセーブル<br>プルアップ抵抗オフ<br>VIN=VDD<br>(出力 Tr.のオフリーク<br>電流を含む) | 2.5~5.5 |         |        | 1    | μА   |

|          | IIH(2) | XT1,XT2                                                                     | 入力ポート仕様時<br>VIN=VDD                                         | 2.5~5.5 |         |        | 1    |      |

|          | 11H(3) | CF1                                                                         | VIN=VDD                                                     | 2.5~5.5 |         |        | 15   |      |

| 低レベル入力電流 | IIL(1) | ホ°-ト0,1,2<br>ホ°-ト3,7,8<br>ホ°-トA,B,C,E,F<br>S12P0~S12P3<br>RES#<br>PWM0,PWM1 | 出力ディセーブル<br>プルアップ抵抗オフ<br>VIN=VSS<br>(出力 Tr.のオフリーク<br>電流を含む) | 2.5~5.5 | -1      |        |      |      |

|          | 11L(2) | XT1,XT2                                                                     | 入力ポート仕様時<br>VIN=VSS                                         | 2.5~5.5 | -1      |        |      |      |

|          | IIL(3) | CF1                                                                         | VIN=VSS                                                     | 2.5~5.5 | -15     |        |      |      |

| 高レベル出力電圧 | V0H(1) | ポ゚−ト0,1,2,3<br>ポ゚−トB,C,E,F                                                  | IOH=-1.0mA                                                  | 4.5~5.5 | VDD-1   |        |      | V    |

|          | VOH(2) | SI2P0~SI2P3<br>PWM0,PWM1                                                    | IOH=-0.1mA                                                  | 2.5~5.5 | VDD-0.5 |        |      |      |

|          | VOH(3) | π° −ト A                                                                     | IOH=-5.0mA                                                  | 4.5~5.5 | VDD-1   |        |      |      |

|          | VOH(4) |                                                                             | IOH=-0.4mA                                                  | 2.5~5.5 | VDD-0.5 |        |      |      |

|          | V0H(5) | ポート 71,72,73                                                                | IOH=-0.4mA                                                  | 4.5~5.5 | VDD-1   |        |      |      |

| 低レベル出力電圧 | V0L(1) | ポ゚−ト0,1,2,3<br>ポ−トB,C,E,F                                                   | IOL=10mA                                                    | 4.5~5.5 |         |        | 1.5  |      |

|          | V0L(2) | SI2P0~SI2P3<br>PWM0,PWM1                                                    | IOL=1.6mA                                                   | 4.5~5.5 |         |        | 0.4  |      |

|          | V0L(3) |                                                                             | IOL=1mA                                                     | 2.5~5.5 |         |        | 0.4  |      |

|          | VOL(4) | P00,P01                                                                     | IOL=30mA                                                    | 4.5~5.5 |         |        | 1.5  |      |

|          | VOL(5) | ポート7,8                                                                      | IOL=1mA                                                     | 2.5~5.5 |         |        | 0.4  |      |

|          | V0L(6) |                                                                             |                                                             |         |         |        |      |      |

|          | V0L(7) | <b>ポ−ト</b> A                                                                | IOL=15mA                                                    | 4.5~5.5 |         |        | 1.5  |      |

|          | V0L(8) |                                                                             | IOL=2mA                                                     | 2.5~5.5 |         |        | 0.4  |      |

| プルアップ抵抗  | Rpu    | ポート0,1,2,3<br>ポート7<br>ポートA,B,C,E,F                                          | VOH=0.9VDD                                                  | 2.5~5.5 | 15      | 40     | 70   | kΩ   |

| ヒステリシス電圧 | VHIS   | RES#<br>ポート1<br>ポート2<br>ポート7<br>SIP0~SIP3                                   |                                                             | 2.5~5.5 |         | 0.1VDD |      | V    |

| 端子容量     | CP     | 全端子                                                                         | 被測定端子以外<br>VIN=VSS<br>f=1MHz<br>Ta=25                       | 2.5~5.5 |         | 10     |      | pF   |

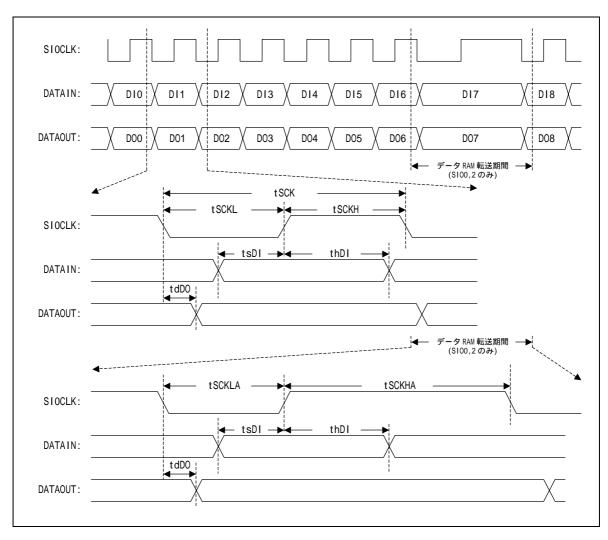

### 4. シリアル入出力特性 / Ta=-20~+70 , VSS1=VSS2=VSS3=VSS4=0V

|        |       | 項目                      | 記号        | 適用端子                                                                | 条件                                                                             |         | 規格                   |      |                  |      |

|--------|-------|-------------------------|-----------|---------------------------------------------------------------------|--------------------------------------------------------------------------------|---------|----------------------|------|------------------|------|

|        |       |                         | 마스        | ・備考                                                                 | ホロ                                                                             | VDD[V]  | min.                 | typ. | max.             | unit |

| シリ     | 入力    | 周期                      | tSCK(1)   | SCKO(P12),<br>SI2P2                                                 | 図 6 参照                                                                         | 2.5~5.5 | 2                    |      |                  | tCYC |

| リアルクロッ | 入力クロッ | 低レベル<br>パルス幅            | tSCKL(1)  |                                                                     |                                                                                |         | 1                    |      |                  |      |

| クロッ    | ク     |                         | tSCKLA(1) |                                                                     |                                                                                |         | 1                    |      |                  |      |

| ク      |       | 高レベル<br>パルス幅            | tSCKH(1)  |                                                                     |                                                                                |         | 1                    |      |                  |      |

|        |       |                         | tSCKHA(1) |                                                                     |                                                                                |         | 3(\$100)<br>5(\$102) |      |                  |      |

|        |       | 周期                      | tSCK(2)   | SCK1 (P15)                                                          | 図 6 参照                                                                         | 2.5~5.5 | 2                    |      |                  |      |

|        |       | 低レベル<br>パルス幅            | tSCKL(2)  |                                                                     |                                                                                |         | 1                    |      |                  |      |

|        |       | 高レベル<br>パルス幅            | tSCKH(2)  |                                                                     |                                                                                |         | 1                    |      |                  |      |

|        | 出     | 出<br>力<br>用期<br>tSCK(3) | tSCK(3)   | SCKO(P12),<br>SI2P2                                                 | ・CMOS 出力選択時<br>・図 6 参照                                                         | 2.5~5.5 | 4/3                  |      |                  |      |

|        | クロ    |                         | tSCKL(3)  | \$12P3                                                              |                                                                                |         |                      | 1/2  |                  | tSCK |

|        | ク     |                         | tSCKLA(2) |                                                                     | SCK0(P12)<br>S100 の場合                                                          |         |                      | 3/4  |                  |      |

|        |       |                         |           |                                                                     | S12P2,S12P3<br>S102 の場合                                                        |         |                      | 1    |                  |      |

|        |       | 高レベル<br>パルス幅            | tSCKH(3)  |                                                                     |                                                                                |         |                      | 1/2  |                  |      |

|        |       |                         | tSCKHA(2) |                                                                     | SCK0(P12)<br>S100 の場合                                                          |         |                      | 2    |                  |      |

|        |       |                         |           |                                                                     | S12P2,S12P3<br>S102 の場合                                                        |         |                      | 7/4  |                  |      |

|        |       | 周期                      | tSCK(4)   | SCK1(P15)                                                           | ・CMOS 出力選択時<br>・図 6 参照                                                         | 2.5~5.5 | 2                    |      |                  | tCYC |

|        |       | 低レベル<br>パルス幅            | tSCKL(4)  |                                                                     |                                                                                |         |                      | 1/2  |                  | tSCK |

|        |       | 高レベル<br>パルス幅            | tSCKH(4)  |                                                                     |                                                                                |         |                      | 1/2  |                  |      |

| シリア    |       | ータセット<br>ップ時間           | tsDI      | SB0(P11),<br>SB1(P14),<br>SI2P1,                                    | ・SIOCLK の立ち上がり<br>に対して規定する<br>・図 6 参照                                          | 2.5~5.5 | 0.03                 |      |                  | μS   |

| ル入力    | ルデー   | ータホールド<br>間             | thDI      | \$10,<br>\$11                                                       |                                                                                |         | 0.03                 |      |                  |      |

| シリアル出力 | 出     | 力遅延時間                   | tdD0      | S00(P10),<br>S01(P13),<br>SB0(011),<br>SB1(P14),<br>S12P0,<br>S12P1 | ・SIOCLK の立ち下がり<br>に対して規定する<br>・オープンドレイン出力<br>時は出力変化開始まで<br>の時間として規定する<br>・図6参照 | 2.5~5.5 |                      |      | 1/3tCYC<br>+0.05 |      |

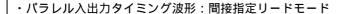

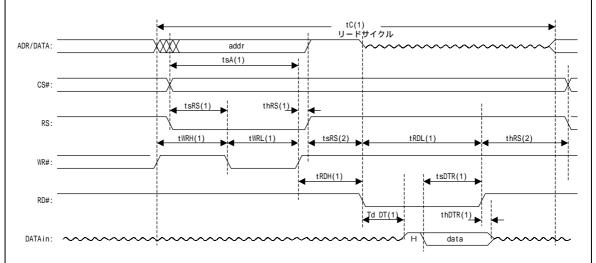

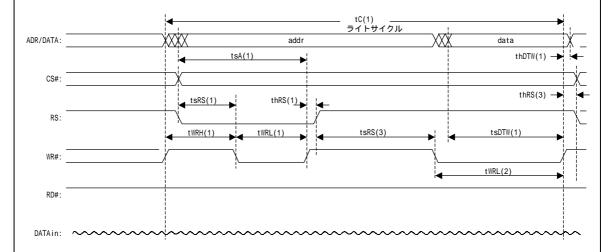

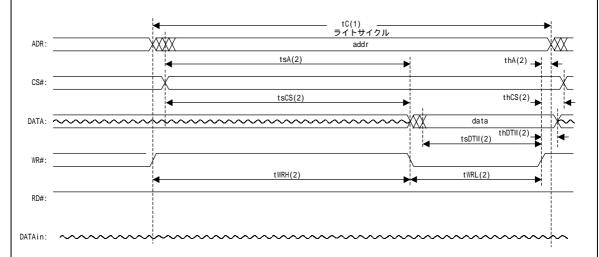

### 5. パラレル入出力特性 / Ta=-20~+70 , VSS1=VSS2=VSS3=VSS4=0V

注意: RS, WR#, RD#, CS#として使用するポートA端子は、オプションでC-MOS形式を選択してください。

パラレル入出力タイミング波形図8,図9を参照してください。

|                      | 記号         | 適用端子・備考                       | 条件                                      | 1       | 規格               |             |                  |              |

|----------------------|------------|-------------------------------|-----------------------------------------|---------|------------------|-------------|------------------|--------------|

|                      |            | 2011 C DIR C112               | 2811                                    | VDD[V]  | min.             | typ.        | max.             | unit         |

| ライトサイクル ,<br>リードサイクル | tC(1)      |                               |                                         | 2.5~5.5 |                  | 1           |                  | tCYC         |

| アドレス                 | tsA(1)     | • WR#(PA3), PB0 ~ PB7         | アドレスの確定から                               | 2.5~5.5 | 1/3tCYC          |             |                  | tCYC         |

| セットアップ時間             |            | • RD#(PA4), PC0 ~ PC7         | 制御信号の変化まで                               |         | -30ns            |             |                  | & ns         |

|                      | tsA(2)     | RD#(PA4),PC0~PC7              |                                         | 2.5~5.5 | 2/3tCYC<br>-30ns |             |                  |              |

| アドレス                 | thA(1)     | RD#(PA4),PC0~PC7              | RD#の変化から                                | 2.5~5.5 | 1/6tCYC          |             |                  |              |

| ホールド時間               |            |                               | アドレスの変化まで                               |         |                  |             |                  |              |

|                      | thA(2)     | WR#(PA3),PC0~PC7              | WR#の変化から<br>アドレスの変化まで                   | 2.5~5.5 | 5                |             |                  | ns           |

| RS<br>セットアップ時間       | tsRS(1)    | WR#(PA3),RS(PA5),<br>CS#(PAX) | RS,CS#の変化から<br>WR#の変化まで                 | 2.5~5.5 | 1/6tCYC<br>-15ns |             |                  | tCYC<br>& ns |

|                      | tsRS(2)    | RD#(PA4),RS(PA5)              | RS の変化から<br>RD#の変化まで                    | 2.5~5.5 | 1/6tCYC<br>-15ns |             |                  |              |

|                      | tsRS(3)    | RD#(PA4),RS(PA5)              | 10,000                                  | 2.5~5.5 | 1/3tCYC<br>-15ns |             |                  |              |

| CS#                  | tsCS(1)    | RD#(PA4),CS#(PAX)             | CS#の変化から                                | 2.5~5.5 | 1/3tCYC          |             |                  |              |

| セットアップ時間             | 1330(1)    | (FAA)                         | RD#の変化まで                                | 2.0 0.0 | -15ns            |             |                  |              |

|                      | tsCS(2)    | WR#(PA3),CS#(PAX)             | CS#の変化から                                | 2.5~5.5 | 2/3tCYC          |             |                  |              |

|                      |            | ·                             | WR#の変化まで                                |         | -15ns            |             |                  |              |

| RS<br>ホールド時間         | thRS(1)    | WR#(PA3),RS(PA5)              | WR#の変化から<br>RS の変化まで                    | 2.5~5.5 | 0                |             |                  | ns           |

|                      | thRS(2)    | RD#(PA4),RS(PA5),<br>CS#(PAX) | RD#の変化から<br>RS,CS#の変化まで                 | 2.5~5.5 | 1/6tCYC          |             |                  | tCYC<br>& ns |

|                      | thRS(3)    | RD#(PA4),RS(PA5),<br>CS#(PAX) |                                         | 2.5~5.5 | 0                |             |                  | ns           |

| CS#<br>ホールド時間        | thCS(1)    | RD#(PA4),RS(PA5)              | RD#の変化から<br>CS#の変化まで                    | 2.5~5.5 | 1/6tCYC          |             |                  | tCYC<br>& ns |

|                      | thCS(2)    | WR#(PA3),RS(PA5)              | WR#の変化から<br>CS#の変化まで                    | 2.5~5.5 | 0                |             |                  | ns           |

| WR#<br>'H'パルス幅       | tWRH(1)    | WR#(PA3)                      |                                         | 2.5~5.5 | 1/6tCYC          | 1/6<br>tCYC |                  | tCYC         |

| 「ハル人帽                | tWRH(2)    | WR#(PA3)                      |                                         | 2.5~5.5 | -5ns<br>2/3tCYC  | 2/3         |                  | & ns         |

|                      | twin(2)    | WK#(FA3)                      |                                         | 2.5~5.5 | -5ns             | tCYC        |                  |              |

| WR#                  | tWRL(1)    | WR#(PA3)                      |                                         | 2.5~5.5 | 1/6tCYC          | 1/6         |                  |              |

| ' L ' パルス幅           | (1117) (0) | WD (( DAG)                    |                                         |         | -5ns             | tCYC        |                  |              |

|                      | tWRL(2)    | WR#(PA3)                      |                                         | 2.5~5.5 | 1/3tCYC<br>-5ns  | 1/3<br>tCYC |                  |              |

| RD#                  | tRDH(1)    | RD#(PA4)                      |                                         | 2.5~5.5 | 1/6tCYC          | 1/6         |                  |              |

| 'H'パルス幅              | . ,        | , ,                           |                                         |         | -5ns             | tCYC        |                  |              |

|                      | tRDH(2)    | RD#(PA4)                      |                                         | 2.5~5.5 | 1/3tCYC<br>-5ns  | 1/3<br>tCYC |                  |              |

| RD#                  | tRDL(1)    | RD#(PA4)                      |                                         | 2.5~5.5 | 1/3tCYC          | 1/3         |                  |              |

| `L'パルス幅              |            |                               |                                         |         | -5ns             | tCYC        |                  |              |

|                      | tRDL(2)    | RD#(PA4)                      |                                         | 2.5~5.5 | 1/2tCYC<br>-5ns  | 1/2<br>tCYC |                  |              |

| ライトデータ<br>許容ディレイ     | tdDT(1)    | RD#(PA4),PB0~PB7              | RD#の立ち下がりから<br>入力データの確定まで               | 2.5~5.5 | -                | -           | 1/6tCYC<br>-15ns | tCYC<br>& ns |

|                      | tdDT(2)    | RD#(PA4),PB0 ~ PB7            | の許容時間<br>注 1                            | 2.5~5.5 |                  |             | 1/3tCYC<br>-15ns |              |

| 入力データ<br>セットアップ時間    | tsDTR(1)   | RD#(PA4),PB0 ~ PB7            | 入力データの確定から<br>RD#の立ち上がりまで<br>の時間<br>注 2 | 2.5~5.5 | 40               |             | 10110            | ns           |

| 入力データ<br>ホールド時間      | thDTR(1)   | RD#(PA4),PB0 ~ PB7            | RD#の立ち上がりから<br>入力データの保持必要<br>時間         | 2.5~5.5 | 0                |             |                  | ns           |

(次ページへ)

| 項目              | 記号       | 適用端子・備考             | 条件                        |         | 規格      |      |      |      |

|-----------------|----------|---------------------|---------------------------|---------|---------|------|------|------|

|                 | 記り       | 旭川州 1、湘石            | ホロ                        | VDD[V]  | min.    | typ. | max. | unit |

| 出力データ           | tsDTW(1) | RD#(PA4),PB0~PB7    | 出力データの確定から                | 2.5~5.5 | 1/3tCYC |      |      | tCYC |

| セットアップ時間        |          |                     | WR#の立ち上がりまで               |         | -30ns   |      |      | & ns |

| 出力データ           | tsDTW(2) | RD#(PA4), PB0 ~ PB7 | の時間                       | 2.5~5.5 | 1/3tCYC |      |      |      |

| セットアップ時間        |          |                     |                           |         | -30ns   |      |      |      |

| 出力データ<br>ホールド時間 | thDTW(1) | RD#(PA4),PB0~PB7    | WR#の立ち上がりから<br>出力データの保持時間 | 2.5~5.5 | 0       |      |      | ns   |

| い 101円          | thDTW(2) |                     | 一四ハン 2の以近時間               | 2.5~5.5 | 0       |      |      |      |

注1:LOWの不正データがなくなるまでの時間

注2: tRDL(1)-tdDT(1)の期間は、LOWの不正データは出力されない。

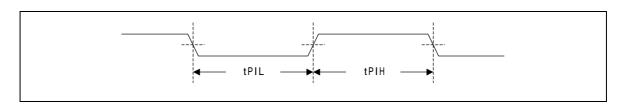

### 6. パルス入力条件 / Ta=-20~+70 , VSS1=VSS2=VSS3=VSS4=0V

| 項目     | 記号      | 適用端子・備考          | 条件              |                       | 規格  |  |  |      |

|--------|---------|------------------|-----------------|-----------------------|-----|--|--|------|

| グロ     | 記ら      | 地方               | <b>ホ</b> ロ      | VDD[V] min. typ. max. |     |  |  |      |

| 高・低レベル | tPIH(1) | INTO(P70),       | ・割り込み要因フラグを     | 2.5~5.5               | 1   |  |  | tCYC |

| パルス幅   | tPIL(1) | INT1(P71),       | セットできる。         |                       |     |  |  |      |

|        |         | INT2(P72),       | ・タイマ 0,1 へのイベント |                       |     |  |  |      |

|        |         | INT4(P20 ~ P23), | 入力ができる。         |                       |     |  |  |      |

|        |         | INT5(P24 ~ P27)  |                 |                       |     |  |  |      |

|        | tPIH(2) | ノイズ除去フィルタ        | ・割り込み要因フラグを     | 2.5~5.5               | 2   |  |  |      |

|        | tPIL(2) | の時定数が 1/1 の      | セットできる。         |                       |     |  |  |      |

|        |         | 場合の INT3(P73)    | ・タイマ 0 へのイベント   |                       |     |  |  |      |

|        |         |                  | 入力ができる。         |                       |     |  |  |      |

|        | tPIH(3) | ノイズ除去フィルタ        | ・割り込み要因フラグを     | 2.5~5.5               | 64  |  |  |      |

|        | tPIL(3) | の時定数が 1/32 の     | セットできる。         |                       |     |  |  |      |

|        |         | 場合の INT3(P73)    | ・タイマ 0 へのイベント   |                       |     |  |  |      |

|        |         |                  | 入力ができる。         |                       |     |  |  |      |

|        | tPIH(4) | ノイズ除去フィルタ        | ・割り込み要因フラグを     | 2.5~5.5               | 256 |  |  |      |

|        | tPIL(4) | の時定数が 1/128 の    | セットできる。         |                       |     |  |  |      |

|        |         | 場合の INT3(P73)    | ・タイマ 0 へのイベント   |                       |     |  |  |      |

|        |         |                  | 入力ができる。         |                       |     |  |  |      |

|        | tPIL(5) | RES#             | リセットできる。        | 2.5~5.5               | 200 |  |  | μS   |

|        |         |                  |                 |                       |     |  |  |      |

### 7. AD 変換特性 / Ta=-20~+70 , VSS1=VSS2=VSS3=VSS4=0V

| 項目             | 記号    | 適用端子                               | 条件                                       |         | 規格                          |      |                            |      |

|----------------|-------|------------------------------------|------------------------------------------|---------|-----------------------------|------|----------------------------|------|

|                | 記与    | ・備考                                | 赤什                                       | VDD[V]  | min.                        | typ. | max.                       | unit |

| 分解能            | N     | ANO(P80)                           |                                          | 3.0~5.5 |                             | 8    |                            | bit  |

| 絶対精度           | ET    | ~ AN8(P70)                         | (注 2)                                    | 3.0~5.5 |                             |      | ±1.5                       | LSB  |

| 変換時間           | TCAD  | AN9(P71)<br>AN10(XT1)<br>AN11(XT2) | AD 変換時間=32 x tCYC<br>(ADCR2=0 の時) (注 3)  | 3.0~5.5 | 15.10<br>(tCYC=<br>0.588μs) |      | 97.92<br>(tCYC=<br>3.06μs) | μS   |

|                |       |                                    | AD 変換時間=64 × t CYC<br>(ADCR2=1 の時) (注 3) | 3.0~5.5 | 15.10<br>(tCYC=<br>0.294μs) |      | 97.92<br>(tCYC=<br>1.53μs) |      |

| アナログ入力<br>電圧範囲 | VAIN  |                                    |                                          | 3.0~5.5 | VSS                         |      | VDD                        | V    |

| アナログポート        | IAINH |                                    | VAIN=VDD                                 | 3.0~5.5 |                             |      | 1                          | μΑ   |

| 入力電流           | IAINL |                                    | VAIN=VSS                                 | 3.0~5.5 | -1                          |      |                            |      |

- (注3)絶対精度は量子化誤差(±1/2LSB)を除く。

- (注4)変換時間は変換をスタートさせる命令が出てからアナログ入力値に対する完全なデジタル変換値がレジスタに設定されるまでの時間をいう。

8. 消費電流特性 / Ta=-20+70 , VSS1=VSS2=VSS3=VSS4=0V

| 項目                                        | 記号         | 適用端子                            | 条件                                                                                                    |         | 規格   |      |      |      |

|-------------------------------------------|------------|---------------------------------|-------------------------------------------------------------------------------------------------------|---------|------|------|------|------|

| 切口 ロー・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 마스         | ・備考                             | 水口                                                                                                    | VDD[V]  | min. | typ. | max. | unit |

| 通常動作時<br>消費電流<br>(注 4)                    | IDDOP(1)   | VDD1<br>=VDD2<br>=VDD3<br>=VDD4 | ・FmCF=10MHz<br>セラミック発振時<br>・FmX'taI=32.768kHz 水晶発振時<br>・システムクロックは 10MHz 側<br>・内蔵 RC 発振は停止<br>・1/1 分周時 | 4.5~5.5 |      | 18   | 35   | mA   |

|                                           | IDDOP(2)   |                                 | ・CF1=20MHz 外部クロック<br>・FmX'taI=32.768kHz 水晶発振時<br>・システムクロックは CF1 側<br>・内蔵 RC 発振は停止<br>・1/2 分周時         | 2.5~5.5 |      | 18   | 35   |      |

|                                           | IDDOP(3)   |                                 | ・FmCF=5MHz セラミック発振時<br>・FmX'tal=32.768kHz 水晶発振時<br>・システムクロックは 5MHz 側                                  | 4.5~5.5 |      | 7    | 15   |      |

|                                           | IDDOP(4)   |                                 | ・内蔵 RC 発振は停止                                                                                          | 2.5~4.5 |      | 6    | 11   |      |

|                                           | IDDOP(5)   |                                 | ・FmCF=0Hz(発振停止)<br>・FmX'tal=32.768kHz 水晶発振時                                                           | 4.5~5.5 |      | 6    | 9    |      |

|                                           | IDDOP(6)   |                                 | ・システムクロックは内蔵 RC 発振                                                                                    | 2.5~4.5 |      | 3    | 6    |      |

|                                           | IDDOP(7)   |                                 | ・FmCF=0Hz (発振停止)<br>・FmX'tal=32.768kHz 水晶発振時<br>・システムクロックは32.768kHz 側                                 | 4.5~6.0 |      | 5    | 7    |      |

|                                           | IDDOP(8)   |                                 | ・内蔵 RC 発振は停止                                                                                          | 2.5~4.5 |      | 3    | 5    |      |

| HALT モード<br>消費電流<br>(注 4)                 | IDDHALT(1) | VDD1<br>=VDD2<br>=VDD3<br>=VDD4 | HALT モード ・FmCF=10MHz セラミック発振時 ・FmX' ta1=32.768kHz 水晶発振時 ・システムクロックは 10MHz 側 ・内蔵 RC 発振は停止 ・1/1 分周時      | 4.5~5.5 |      | 6    | 12   | mA   |

|                                           | IDDHALT(2) |                                 | ・CF1=20MHz 外部クロック<br>・FmX'ta1=32.768kHz 水晶発振時<br>・システムクロックは CF1 側<br>・内蔵 RC 発振は停止<br>・1/2 分周時         | 4.5~5.5 |      | 7    | 14   |      |

|                                           | IDDHALT(3) |                                 | ・HALT モード<br>・FmCF=5MHz セラミック発振時<br>・FmX'tal=32.768kHz 水晶発振時<br>・システムクロックは 5MHz 側                     | 4.5~5.5 |      | 3.3  | 4    |      |

|                                           | IDDHALT(4) |                                 | ・内蔵 RC 発振は停止                                                                                          | 2.5~4.5 |      | 1.2  | 3.2  | _    |

|                                           | IDDHALT(5) |                                 | ・HALT モード<br>・FmCF=0Hz(発振停止)<br>・FmX*ta1=32.768kHz 水晶発振時                                              | 4.5~5.5 |      | 1    | 1.5  |      |

|                                           | IDDHALT(6) |                                 | ・システムクロックは内蔵 RC 発振                                                                                    | 2.5~4.5 |      | 0.4  | 1    |      |

|                                           | IDDHALT(7) |                                 | ・HALT モード<br>・FmCF=0Hz(発振停止)<br>・FmX'tal=32.768kHz 水晶発振時<br>・システムクロックは 32.768kHz 側                    |         |      | 60   | 150  |      |

|                                           | IDDHALT(8) |                                 | ・内蔵 RC 発振は停止                                                                                          | 2.5~4.5 |      | 16   | 72   |      |

| HOLD モード<br>消費電流                          | IDDHOLD(1) | VDD1                            | HOLD モード<br>・CF1=VDD またはオープン<br>(外部クロック時)                                                             | 2.5~5.5 |      | 0.01 | 25   | μА   |

| 時計 HOLD モード<br>消費電流                       | IDDHOLD(2) | VDD1                            | 時計 HOLD モード ・CF1=VDD またはオープン (外部クロック時) ・FmX'tal=32.768kHz 水晶発振時                                       | 2.5~5.5 |      | 35   | 100  | μА   |

(注4)消費電流は出力 Tr. および内蔵プルアップ抵抗に流れる電流を含まない。

9. F-ROM 書き込み特性 / Ta=+10~+55 , VSS1=VSS2=VSS3=VSS4=0V

| 項目     | 記号       | 適用端子 | 条件            | _       | 規格   |      |         |    |  |

|--------|----------|------|---------------|---------|------|------|---------|----|--|

| 75.1   | HO -5    | ・備考  | 3811          | VDD[V]  | min. | typ. | max. un |    |  |

| オンボード  | IDDFW(1) | VDD1 | ・128 バイト書き込み  | 4.5~5.5 |      | 30   | 65      | mA |  |

| 書き込み電流 |          |      | ・消去電流も含む      |         |      |      |         |    |  |

| 書き込み時間 | tFW(1)   |      | ・128 バイト書き込み  | 4.5~5.5 |      | 4.2  | 7.0     | mS |  |

|        |          |      | ・消去動作も含む      |         |      |      |         |    |  |

|        |          |      | ・128 バイトのデータを |         |      |      |         |    |  |

|        |          |      | そろえる時間は除く     |         |      |      |         |    |  |

### メイン・システム・クロック発振回路特性例

メイン・システム・クロック発振回路特性例は、弊社指定の発振特性評価用基板を用いて、発振子メーカによって安定に発振することを確認された回路定数と、この回路定数を外付けしたときの特性例です。

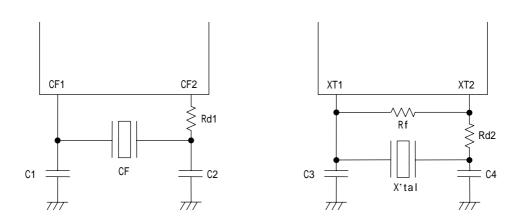

表 1 セラミック発振子を使用したメイン・システム・クロック発振回路特性例

| 公称周波数             | メーカ名                                    | 発振子名       | □      | 路定数    |     | 動作電圧     | 発振安    | 定時間    | 備考        |

|-------------------|-----------------------------------------|------------|--------|--------|-----|----------|--------|--------|-----------|

|                   | / // // // // // // // // // // // // / | 无派」口       | C1     | C2     | Rd1 | 範囲       | typ    | max    | MH '5     |

| 10MHz 村田製作<br>京セラ | 村田制作品                                   | CSA10.OMTZ | 33pF   | 33pF   | 0Ω  | 4.5~6.0V | 0.05ms | 0.50ms |           |

|                   | 11 Ш <del>Ж</del> ГР <i>П</i> Г         | CST10.OMTW | (30pF) | (30pF) | Ω0  | 4.5~6.0V | 0.05ms | 0.50ms | C1,C2 内蔵品 |

|                   | 京セラ                                     | KBR-10.0M  | 33pF   | 33pF   | Ω0  | 4.5~6.0V | 0.05ms | 0.50ms |           |

| 4MHZ              | 村田製作所                                   | CSA4.00MG  | 33pF   | 33pF   | Ω0  | 2.5~6.0V | 0.05ms | 0.50ms |           |

|                   | TI LI XX IF I/I                         | CST4.00MGW | (30pF) | (30pF) | Ω0  | 2.5~6.0V | 0.05ms | 0.50ms | C1,C2 内蔵品 |

|                   | 京セラ                                     | KBR-4.0MSA | 33pF   | 33pF   | 0Ω  | 2.5~6.0V | 0.05ms | 0.50ms |           |

発振安定時間は、VDDが動作電圧下限を上回ってから、発振が安定するまでに必要な時間です。(図4参照)

### サブ・システム・クロック発振回路特性例

サブ・システム・クロック発振回路特性例は、弊社指定の発振特性評価用基板を用いて、発振子メーカによって安定に発振することを確認された回路定数と、この回路定数を外付けしたときの特性例です。

表 2 水晶発振子を使用したサブ・システム・クロック発振回路特性例

| 公称周波数     | メーカ名        | 発振子名    |      | 回路   | 路定数  |       | 動作電圧範囲         | 発振安定 | 官時間     | 備考 |

|-----------|-------------|---------|------|------|------|-------|----------------|------|---------|----|

|           | <b>У</b> ЛЪ | 无弧」口    | C3   | C4   | Rf   | Rd2   | <b>到下电</b> 工电四 | typ  | typ max |    |

| 32.768kHz | セイコーエフ。ソン   | C-002Rx | 12pF | 15pF | OPEN | 360kΩ | 2.5~6.0V       | 1    | 3       |    |

発振安定時間は、サブクロック発振回路を開始させる命令を実行後、発振が安定するまでに必要な時間と、 HOLDモードを解除後、発振が安定するまでに必要な時間です。(図4参照)

(注意) ・ 回路パターンの影響を受けるので、発振に関わる部品はできるだけパターン長を伸ばさないように 近くに配置すること。

図1 CF発振回路

図 2 X T 発振回路

図3 ACタイミング測定点

図4 発振安定時間

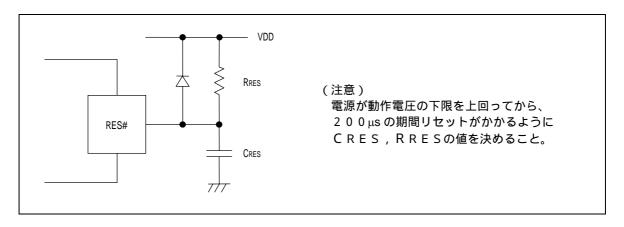

図5 リセット回路

図6 シリアル入出力波形

図7 パルス入力タイミング波形

注意:RS, WR#, RD#, CS#として使用するポートA端子は、オプションでC - MOS形式を選択してください。

・パラレル入出力タイミング波形:間接指定ライトモード

注意:RS,WR#,RD#,CS#として使用するポートA端子は、オプションでC-MOS形式を選択してください。

図8 間接モードパラレル入出力タイミング波形

注意:RS,WR#,RD#,CS#として使用するポートA端子は、オプションでC-MOS形式を 選択してください。

・パラレル入出力タイミング波形:直接指定ライトモード

注意:RS, WR#, RD#, CS#として使用するポートA端子は、オプションでC - MOS形式を選択してください。

図9 直接モードパラレル入出力タイミング波形

- ■本書記載の製品は、定められた条件下において、記載部品単体の性能・特性・機能などを規定するものであり、お客様の製品(機器)での性能・特性・機能などを保証するものではありません。部品単体の評価では予測できない症状・事態を確認するためにも、お客様の製品で必要とされる評価・試験を必ず行って下さい。

- ■弊社は、高品質・高信頼性の製品を供給することに努めております。しかし、半導体製品はある確率で故障が生じてしまいます。この故障が原因となり、人命にかかわる事故、発煙・発火事故、他の物品に損害を与えてしまう事故などを引き起こす可能性があります。機器設計時には、このような事故を起こさないような、保護回路・誤動作防止回路等の安全設計、冗長設計・機構設計等の安全対策を行って下さい。

- ■本書記載の製品が、外国為替及び外国貿易法に定める規制貨物(役務を含む)に該当する場合、輸出する際に同法に基づく輸出許可が必要です。

- ■弊社の承諾なしに、本書の一部または全部を、転載または複製することを禁止します。

- ■本書に記載された内容は、製品改善および技術改良等により将来予告なしに変更することがあります。したがって、ご使用の際には、「納入仕様書」でご確認下さい。

- ■この資料の情報(掲載回路および回路定数を含む)は一例を示すもので、量産セットとしての設計を保証するものではありません。また、この資料は正確かつ信頼すべきものであると確信しておりますが、その使用にあたって第3者の工業所有権その他の権利の実施に対する保証を行うものではありません。