2388

mot

# 4K Bit Static Random Access Memory

The MCM6147A is a 4096-bit static random access memory organized as 4096 words by 1-bit, fabricated using Motorola's high performance CMOS silicon gate technology (HCMOS). It uses a design approach which provides the simple timing features associated with fully static memories and the reduced power associated with CMOS memories. This means low power without the need for clocks, nor reduced data rates due to cycle times that exceed access times.

Chip enable  $(\overline{E})$  controls the power-down feature. It is not a clock, but rather a chip control that affects power consumption. After  $\overline{E}$  goes high, initiating deselect mode, the part automatically reduces its power requirements and remains in this low-power standby mode as long as  $\overline{E}$  remains high.

The MCM6147A is in an 18-pin dual in-line package with the industry standard pin out. It is TTL compatible in all respects. The data out has the same polarity as the input data. A data input and a separate three-state output provide flexibility and allow easy OR-ties.

- Single +5 V Supply

- Fully Static Memory-No Clock or Timing Strobe Required

- Maximum Access Time

MCM6147A-55 and MCM61L47A-55 = 55 ns

MCM6147A-70 and MCM61L47A-70 = 70 ns

- Automatic Power Down

- Low Power Supply Current Drain

35 mA Maximum (Active)

12 mA Maximum (Standby—TTL Levels)

800 μA Maximum (Standby—Full Rail, MCM6147A)

100 μA Maximum (Standby—Full Rail, MCM61L47A)

- Low Standby Power Version Available—MCM61L47A

- Directly TTL Compatible—All Inputs and Output

- Separate Data Input and Three-State Output

- Equal Access and Cycle Time

- High Density 18-Pin Package

- Improved ESD Protection

# **BLOCK DIAGRAM** AΠ PIN 18 = V<sub>CC</sub> PIN 9 = GND MEMORY ARRAY ROW 64 ROWS SELECT 46 64 COLUMNS . . . $D^{\frac{11}{2}}$ COLUMN I/O CIRCUITS COLUMN SELECT 13 A9 A10 A11 Α5

# MCM6147A 040733 MCM61L47A

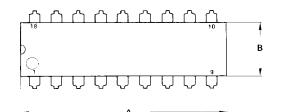

P PACKAGE PLASTIC CASE 707

| PIN               | PIN ASSIGNMENT |                       |   |  |  |  |  |  |

|-------------------|----------------|-----------------------|---|--|--|--|--|--|

| A0 [              | 1 •            | 18 D V <sub>C</sub> ( | 3 |  |  |  |  |  |

| A1 [              | 2              | 17 🗖 🗚 6              |   |  |  |  |  |  |

| A2 [              | 3              | 16 🛮 A7               |   |  |  |  |  |  |

| АЗ [              | 4              | 15 🕽 A8               |   |  |  |  |  |  |

| A4 [              | 5              | 14 🛮 A9               |   |  |  |  |  |  |

| A5 [              | 6              | 13 🛭 A11              | 0 |  |  |  |  |  |

| a <b>C</b>        | 7              | 12 <b>  ]</b> A1      | 1 |  |  |  |  |  |

| ₩d                | 8              | 11 <b>  1</b> D       | • |  |  |  |  |  |

| v <sub>SS</sub> C | 9              | 10 DE                 |   |  |  |  |  |  |

|                   |                |                       |   |  |  |  |  |  |

|                 | PIN NAMES    |  |  |  |  |  |

|-----------------|--------------|--|--|--|--|--|

| A0-A11          | Address      |  |  |  |  |  |

| Ē               | Chip Enable  |  |  |  |  |  |

| D               |              |  |  |  |  |  |

| α               | Data Output  |  |  |  |  |  |

| W               |              |  |  |  |  |  |

| Vcc · · ·       | Power (+5 V) |  |  |  |  |  |

| V <sub>SS</sub> | Ground       |  |  |  |  |  |

|                 |              |  |  |  |  |  |

#### **ABSOLUTE MAXIMUM RATING (See Note)**

| Rating                                             | Value          | Unit |

|----------------------------------------------------|----------------|------|

| Temperature Under Bias                             | - 10 to +85    | °C   |

| Voltage on Any Pin with Respect to V <sub>CC</sub> | -0.5  to  +7.0 | ٧    |

| Power Dissipation                                  | 1.0            | Watt |

| Operating Temperature Range                        | 0 to +70       | °C   |

| Storage Temperature Range                          | 65 to + 150    | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPER-ATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

### DC OPERATING CONDITIONS AND CHARACTERISTICS

(Full Operating Voltage and Temperature Range Unless Otherwise Noted)

### RECOMMENDED OPERATING CONDITIONS

| Parameter                                | Symbol          | Min      | Тур      | Max      | Unit |

|------------------------------------------|-----------------|----------|----------|----------|------|

| Supply Voltage (Operating Voltage Range) | Vcc<br>Vss      | 4.5<br>0 | 5.0<br>0 | 5.5<br>0 | ٧    |

| Input High Voltage, All Inputs           | V <sub>IH</sub> | 2.0      |          | 6.0      | V    |

| Input Low Voltage, All Inputs            | V <sub>IL</sub> | -0.3     | _        | 0.8      | V    |

### DC CHARACTERISTICS

| Parameter                                                                                                        |                       | Symbol           | Min    | Тур*      | Max  | Unit |

|------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|--------|-----------|------|------|

| Input Load Current (All Input Pins, V <sub>in</sub> = 0 to 5.5 V)                                                |                       | IIL              | ı      | 0.01      | 1.0  | μА   |

| Output Leakage Current (E=2.0 V, Vout=0 to 5.5 V)                                                                |                       | I <sub>OL</sub>  | 1      | 0.1       | 1.0  | μА   |

| Power Supply Current (E=V <sub>IL</sub> , Output Open)                                                           |                       | <sup>I</sup> cc  | _      | 15        | (35) | mA   |

| Standby Current ( $\overline{E} = V_{IH}$ )                                                                      |                       | ISB              | _      | 5         | 12   | mA   |

| Standby Current ( $\overline{E} = V_{CC} - 0.2 \text{ V}, 0.2 \text{ V} \ge V_{in} \ge V_{CC} - 0.2 \text{ V}$ ) | MCM6147A<br>MCM61L47A | <sup>I</sup> SB1 | _<br>_ | 200<br>25 | 800  | μΑ   |

| Input Low Voltage                                                                                                |                       | V <sub>IL</sub>  | -0.3   |           | 0.8  | ν    |

| Input High Voltage                                                                                               |                       | V <sub>IH</sub>  | 2.0    | _         | 6.0  | V    |

| Output Low Voltage (I <sub>OL</sub> = 12.0 mA)                                                                   |                       | VOL              | _      | _         | 0.4  | ٧    |

| Output High Voltage** (IOH = -8.0 mA)                                                                            |                       | VOH              | 2.4    |           | _    | V    |

<sup>\*</sup>Typical values are for  $T_A = 25^{\circ}\text{C}$  and  $V_{CC} = 5.0 \text{ V}$ .

### CAPACITANCE

(f = 1.0 MHz, T<sub>A</sub> = 25°C, Periodically Sampled Rather Than 100% Tested)

| Characteristic                            | Symbol           | Max | Unit |

|-------------------------------------------|------------------|-----|------|

| Input Capacitance (V <sub>in</sub> = 0 V) | C <sub>in</sub>  | 5.0 | pF   |

| Output Capacitance (Vout=0 V)             | C <sub>out</sub> | 7.0 | pF   |

Capacitance measured with a Boonton Meter or effective capacitance calculated from the equation:  $C = I\Delta_t/\Delta V$ .

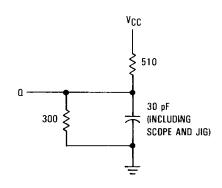

Figure 1. Output Load

<sup>\*\*</sup>Output voltages are compatible with Motorola's High-Speed CMOS Logic Family if the same power supply voltage is used.

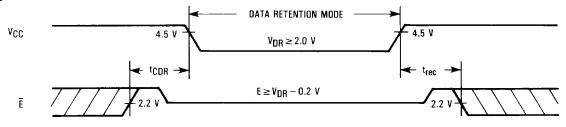

# LOW VCC DATA RETENTION CHARACTERISTICS (T<sub>A</sub> = 0 to +70°C) (MCM61L47A Only)

|                                     |                                                                                                                          |                  |        |     | ,   |      |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------|--------|-----|-----|------|

| Parameter                           | Conditions                                                                                                               | Symbol           | Min    | Тур | Max | Unit |

| V <sub>CC</sub> for Data Retention  | $\overline{E} \ge V_{CC} - 0.2V$<br>$V_{in} \ge V_{CC} - 0.2 \text{ V or } V_{in} \le 0.2 \text{ V}$                     | V <sub>DR</sub>  | 2.0    | _   | _   | V    |

| Data Retention Current              | $V_{CC} = 3.0 \text{ V}, \ \vec{E} \ge 2.8 \text{ V}$<br>$V_{in} \ge 2.8 \text{ V} \text{ or } V_{in} \le 0.2 \text{ V}$ | ICCDR            | _      | _   | 40  | μΑ   |

| Chip Disable to Data Retention Time | See Retention Waveform                                                                                                   | tCDR             | 0      | _   | _   | ns   |

| Operation Recovery Time             |                                                                                                                          | t <sub>rec</sub> | *tAVAX | _   | _   | ns   |

$t_{AVAX} = Read Cycle Time.$

# LOW VCC DATA RETENTION WAVEFORM

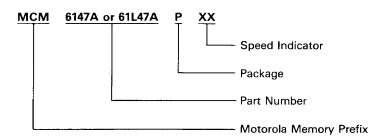

# ORDERING INFORMATION (Order by Full Part Number)

Full Part Numbers — MCM6147AP55 MCM61L47AP55 MCM6147AP70 MCM61L47AP70

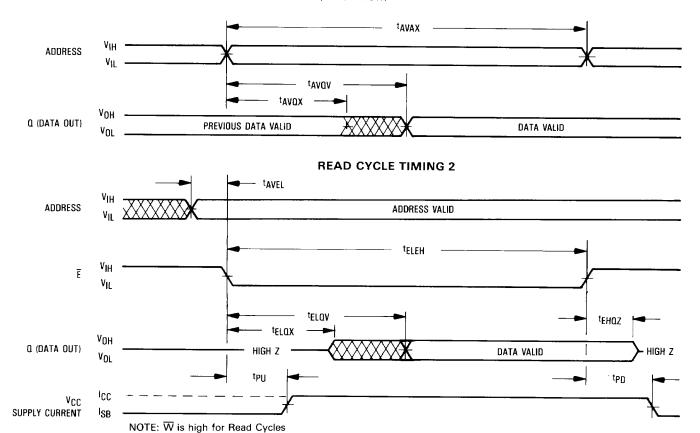

# READ CYCLE TIMING 1

(E Held Low)

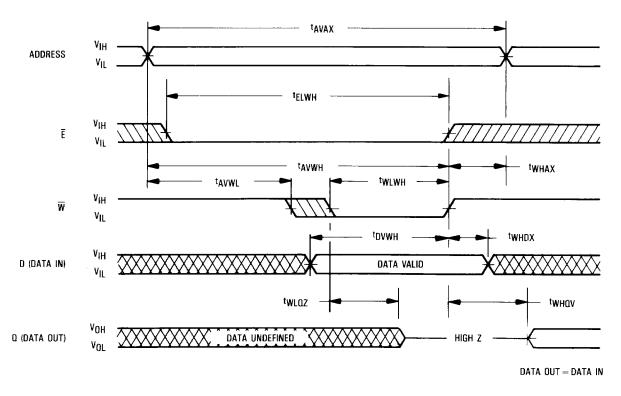

### WRITE CYCLE TIMING

### AC OPERATING CONDITIONS AND CHARACTERISTICS

(Full Operating Voltage and Temperature Unless Otherwise Noted)

| Input Pulse Levels        | . 0 Volt to 3.5 Volts | Input and Output Timing Reference Levels | 1.5 Volts |

|---------------------------|-----------------------|------------------------------------------|-----------|

| Input Rise and Fall Times | 10 ns                 | Output Load                              | Figure 1  |

### **READ, WRITE CYCLES**

| Parameter                                                                           | Symbol            | MCM6147A-55<br>MCM61L47A-55 |          | MCM6147A-70<br>MCM61L47A-70 |     | Unit     |

|-------------------------------------------------------------------------------------|-------------------|-----------------------------|----------|-----------------------------|-----|----------|

|                                                                                     |                   | Min                         | Max      | Min                         | Max | <u> </u> |

| Address Valid to Address Don't Care<br>(Cycle Time when Chip Enable is Held Active) | <sup>†</sup> AVAX | 55                          | _        | 70                          | _   | ns       |

| Chip Enable Low to Chip Enable High                                                 | <sup>†</sup> ELEH | 55                          | <u> </u> | 70                          |     | ns       |

| Address Valid to Output Valid (Access)                                              | tAVQV             | _                           | 55       |                             | 70  | ns       |

| Chip Enable Low to Output Valid (Access)                                            | t <sub>ELQV</sub> | _                           | 55       |                             | 70  | ns       |

| Address Valid to Output Invalid                                                     | tAVQX             | 5                           |          | 5                           | _   | ns       |

| Chip Enable Low to Output Invalid                                                   | tELQX_            | 10                          | _        | 10                          | _   | ns       |

| Chip Enable High to Output High Z                                                   | <sup>‡</sup> EHQZ | 0                           | 40       | 0                           | 40  | ns       |

| Chip Selection to Power-Up Time                                                     | tėu               | 0                           | _        | 0                           | _   | ns       |

| Chip Deselection to Power-Down Time                                                 | tPD               | 0                           | 30       | 0                           | 30  | ns       |

| Address Valid to Chip Enable Low (Address Setup)                                    | †AVEL             | 0                           |          | 0                           |     | ns       |

| Chip Enable Low to Write High                                                       | <sup>t</sup> ELWH | 45                          | _        | 55                          | _   | ns       |

| Address Valid to Write High                                                         | <sup>t</sup> AVWH | 45                          | _        | 55                          | _   | ns       |

| Address Valid to Write Low (Address Setup)                                          | †AVWL             | 0                           |          | 0                           |     | ns       |

| Write Low to Write High (Write Pulse Width)                                         | tWLWH             | 35                          | _        | 40                          | _   | ns       |

| Write High to Address Don't Care                                                    | tWHAX             | 10                          | _        | 15                          | _   | ns       |

| Data Valid to Write High                                                            | tDVWH             | 25                          | _        | 30                          | _   | ns       |

| Write High to Data Don't Care (Data Hold)                                           | tWHDX             | 10                          |          | 10                          | _   | ns       |

| Write Low to Output High Z                                                          | tWLQZ             | 0                           | 30       | 0                           | 35  | ns       |

| Write High to Output Valid                                                          | tWHQV             | 0                           |          | 0                           |     | ns       |

### TIMING PARAMETER ABBREVIATIONS

signal name from which interval is defined \_\_\_\_\_ signal name to which interval is defined \_\_\_\_\_ signal name to which interval is defined \_\_\_\_\_ transition direction for second signal \_\_\_\_\_

The transition definitions used in this data sheet are:

H = transition to high

L = transition to low

V = transition to valid

X = transition to invalid or don't care

Z = transition to off (high impedance)

## **TIMING LIMITS**

The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address setup time is shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time.

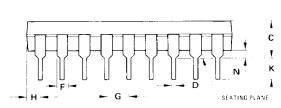

### PACKAGE DIMENSIONS

P PACKAGE PLASTIC CASE 707-02

#### NOTES:

- 1. POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25mm(0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

- 2. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- DIMENSION B DOES NOT INCLUDE MOLD FLASH.

|     | MILLIN   | MILLIMETERS |           | HES             |

|-----|----------|-------------|-----------|-----------------|

| DIM | MIN      | MAX         | MIN       | MAX             |

| Α   | 22.22    | 23.24       | 0.875     | 0.915           |

| В   | 6.10     | 6.60        | 0.240     | 0.260           |

| C   | 3.56     | 4.57        | 0.140     | 0.180           |

| D   | 0.36     | 0.56        | 0.014     | 0.022           |

| F   | 1.27     | 1.78        | 0.050     | 0.070           |

| G   | 2.54 BSC |             | 0.100 BSC |                 |

| Н   | 1.02     | 1.52        | 0.040     | 0.060           |

| J   | 0.20     | 0.30        | 0.008     | 0.012           |

| K   | 2.92     | 3.43        | 0.115     | 0.135           |

| L   | 7.62     | BSC         | 0.300 BSC |                 |

| M   | 00       | 15°         | 00        | 15 <sup>0</sup> |

| N   | 0.51     | 1.02        | 0.020     | 0.040           |

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola and  $\overset{\bigstar}{\mathbf{A}}$  are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity/ Affirmative Action Employer.

### Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. EUROPE: Motorola Ltd.; European Literature Center; 88 Tanners Drive, Blakelands Milton Keynes, MK145BP, England. ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; P.O. Box 80300; Cheung Sha Wan Post Office; Kowloon Hong Kong.

**MOTOROLA**